Изобретение относится к импульсной технике и может быть использовано в измерительных устройствах и электронных часах.

Целью изобретения является повышение быстродействия.

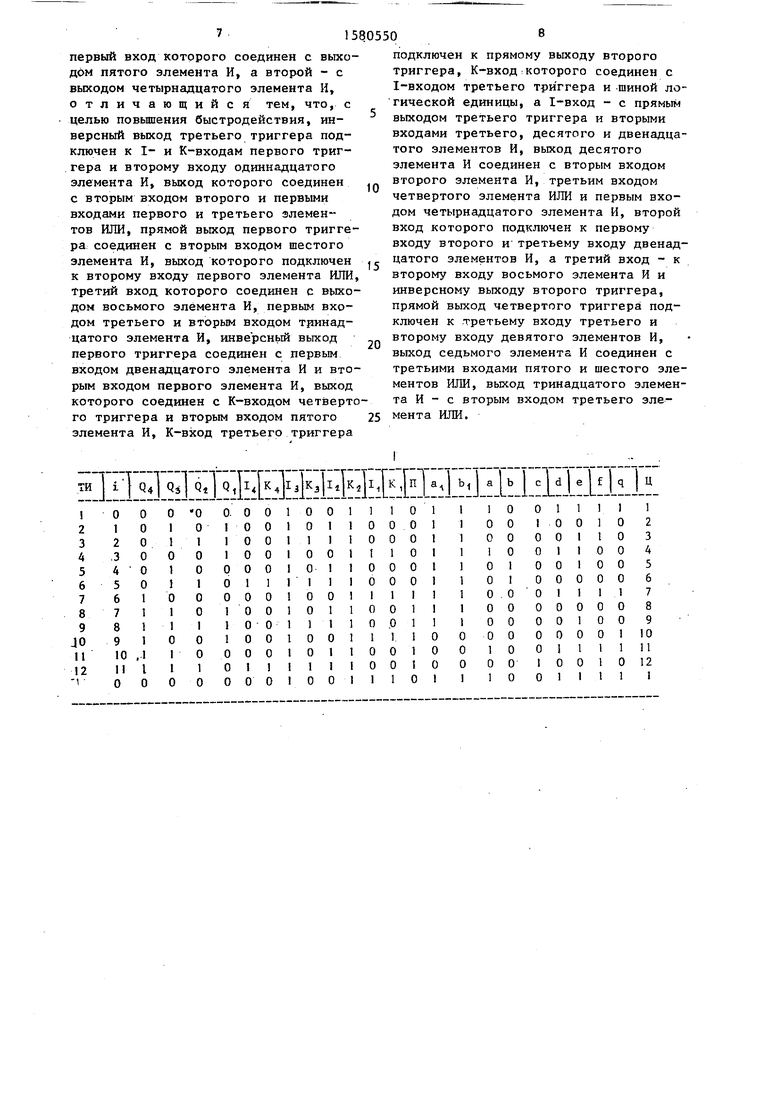

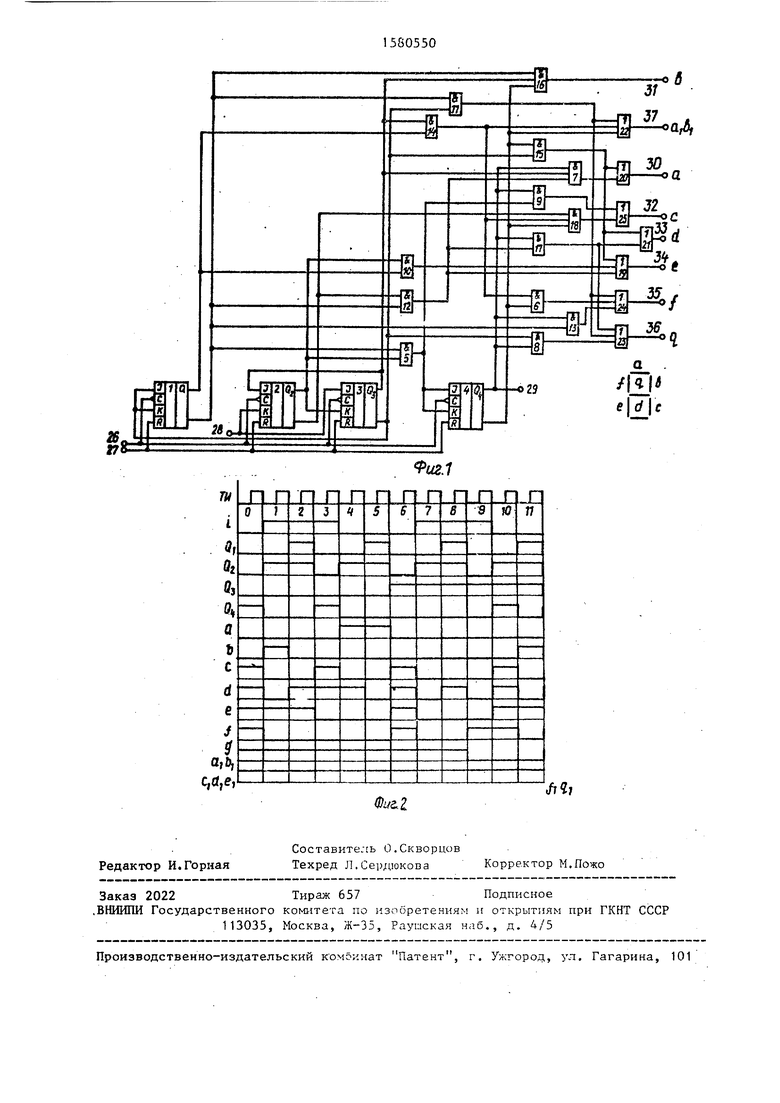

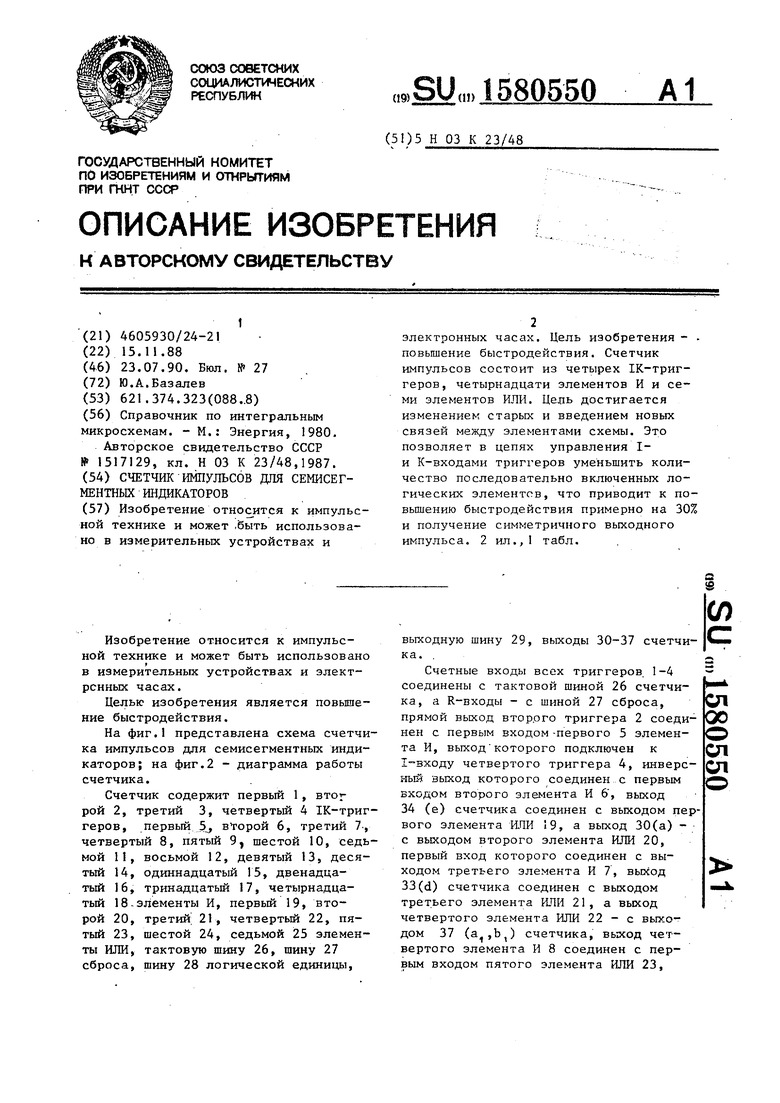

На фиг.1 представлена схема счетчика импульсов для семисегментных индикаторов; на фиг.2 - диаграмма работы счетчика.

Счетчик содержит первый 1, втог рой 2, третий 3, четвертый 4 1К-триг- геров, первый второй 6, третий 7, четвертый 8, пятый 9, шестой 10, седьмой 11, восьмой 12, девятый 13, десятый 14, одиннадцатый 15, двенадцатый 16, тринадцатый 17, четырнадцатый 18 элементы И, первый 19, второй 20, третий 21, четвертый 22, пятый 23, шестой 24, седьмой 25 элементы ИЛИ, тактовую шину 26, шину 27 сброса, шину 28 логической единицы,

выходную шину 29, выходы 30-37 счетчика.

Счетные входы всех триггеров 1-4 соединены с тактовой шиной 26 счетчика, а R-входы - с шиной 27 сброса, прямой выход второго триггера 2 соединен с первым входом первого 5 элемента И, выход которого подключен к I-входу четвертого триггера 4, инверсный выход которого соединен с первым входом второго элемента И 6, выход 34 (е) счетчика соединен с выходом первого элемента ИЛИ 19, а выход 30(а) - с выходом второго элемента ИЛИ 20, первый вход которого соединен с выходом третьего элемента И 7, выход 33(d) счетчика соединен с выходом третьего элемента ИЛИ 21, а выход четвертого элемента ИЛИ 22 - с выходом 37 (а1,Ь1) счетчика, выход четвертого элемента И 8 соединен с первым входом пятого элемента ИЛИ 23,

ел

00

о ел сп

выход которого соединен с выходом 36 (q) счетчика, прямой выход четвертого триггера 4 соединен с выходом 29 счетчика, первыми входами четвертого 8 и пятого 9 элементов И, первый вход шестого элемента И 10 соединен

5, сс

с первым входом первого элемента И первый вход седьмого элемента И 11 единен с вторым входом четвертого элемента И 8 и с инверсным выходом третьего триггера 3,второй вход - с инверсным выходом первого триггера 1 и первым входом восьмого элемента И 12, а выход - с первым входом четвертого элемента ИЛИ 22, первый вход восьмого элемента И 12 соединен с первым входом девятого элемента И 13, выход которого подключен к первому входу шестого элемента ИЛИ 24, выход которого соединен с выходом 35 (f) счетчика, а второй вход - с выходом второго элемента И 6, прямой выход первого триггера 1 подключен к первому входу десятого элемента И )4, первый вход одиннадцатого элемента И 15 соединен с первым входом второго элемента И 6 и вторым входом четвертого элемента ИЛИ 22, выход двенадцатого элемента И 16 подключен к выходу 31 (Ь) счетчика, первый вход пятого элемента И 9 подключен к первому входу тринадцатого элемента И 17, выход которого подключен к второму входу пятого элемента ИЛИ 23, выход 32 (с) счетчика соединен с выходом седьмого элемента ИЛИ 25, первый вход которог соединен с выходом пятого элемента И 9, а второй - с выходом четырнадцатого элемента И 18, инверсный выход третьего триггера 3 подключен к I- и К-входам первого триггера 1 и второму входу одиннадцатого элемента И 15, выход которого соединен с вторым входом второго 20 и первыми входами первого 19 и третьего 21 элементов ИЛИ, прямой выход первого триггера 1 соединен с вторым входом шестого элемента И 10, выход которого подключен к второму входу первого элемента ИЛИ 19, третий вход которого соединен с выходом восьмого элемента И 12, первым входом третьего 7 и вторым входом тринадцатого 17 элементов И, инверсный выход первого триг

гера 1 соединен с первым входом две- надцатого элемента И 16 и вторым входом первого элемента И 5, выход кото- рого соединен с К-входом четвертого

10

15

20

5,Q 05504

триггера 4 и вторым входом пятого элемента И 9, К-в::од третьего триггера 3 подключен к прямому выходу второго триггера 2, К-вход которого соединен с I-входом третьего триггера 3 и шиной 28 логической единицы, а 1-вход - с прямым выходом третьего триггера 3 и вторыми входами третьего 7, десятого 14 и двенадцатого 16 элементов И, выход десятого элемента И 14 соединен с вторым входом второго элемента И 6, третьим входом четвертого элемента ИЛИ 22 и первым входом четырнадцатого элемента И 18, второй вход которого подключен к первому входу второго 6 и третьему входу двенадцатого 16 элементов И, а третий вход - к второму входу восьмого элемента И 12 и инверсному выходу второго триггера 2, прямой выход четвертого триггера 4 подключен к третьему входу третьего 7 и второму входу девятого 13 элементов И, выход седьмого элемента И 11 соединен с третьими входами пятого 23 и шестого 24 элементов ИЛИ, а выход тринадцатого элемента И 17 - с вторым входом третьего элемента ИЛИ 21.

Q

е

J

5

0

5

0

Благодаря такой схеме соединения элементов логические уравнения для I- и К-входов триггеров и всех выходов счетчика следующие: ., Q3,

Кт

Q

з

if Q3;

к.

1 Ч т - 1 Ч

1 Ij- 1

К5 Q7; I QjQj, K Q,Qz, ,

a, b, (1,2,3,4,5,6,7,8,9)

VQ, a (1,4,11) ,о;2(длол

b (5,6) QfQ4Q4, с (2,12) Q2Q4(QiQ3) VQt(Q1Q,z), d (1,4,7, 11) (QiQi), e (1,3,4,5,7, 9,11) Q,Q« vQ,Q4 vq,, f (1,2, 3,7,11,12) Q1Q5V Q1Q4v Q4(Q1Qa), q (1,,11) ,.,), где обозначение 1 показывает, что на данный вход подается уровень логической единицы. Для остальных элементов ,, второго индикатора используется уровень логической единицы, так как они не светятся.

Триггеры 1-4 с элементом И 5 образуют делитель частоты на 12, а элементы 6-25 образуют дешифратор для последовательного включения (можно через соответствующий формирователь) элементов семисегментного индикатора. Триггеры реагируют на изменения тактовых импульсов со значения на .

В исходное состояние все триггеры 1--4 приводятся сигналом Сброс, поступающим в виде импульса по шине 27, при этом 0 О, Q2 О, Q3 О, 0 0 диаграммы на фиг.2 при ).

Пользуясь логическими уравнениями для I- и К-входов триггеров, определим их

состояния: , К 1,

1а- О, К, 1, I,- I, К§ 0, 14- О,

К 0, а по логическим уравнениям выходов дешифратора определим состояния выходов a,b,c,d,e,f,q: a, I, bj 1, а 1, b 0, с 0, d 1, е 1, f q I. На индикаторе светится цифра 1.

Поскольку IK-триггер по входному тактовому импульсу при I 0 и К О не изменяет своего состояния, при I I и К 1 переключается в противоположное состояние, при I 1 и К 0 переключается в состояние логической единицы, а при I 0 и К 1 - в состояние логического нуля, то по первому тактовому импульсу, поступившему по шине 26, триггеры I и 3 переключаются в состояние логической единицы, а триггеры 2 и 4 не изменяют своего состояния (диаграммы на фиг.2 при ). При этом состояния выходов триггеров 1-4 станут равны Q 1, Q4 О, Q 3 1,-Q4 0, изменяются соот- состояния I- и

ветственно

У

1, 0.

о,

о,

4е

К4

1, Кз 1, 13 1,

О, а на выходах деV 0

шифратора появляются сигналы а 1, bf 1, а О, Ъ 0, с 1, d О, , f 1, q 0 и на индикаторе засветится цифра 2.

По второму тактовому импульсу (ди- |аграммы на фиг. 2 при ) состояния выходов и входов станут равны Q 1,

Q QS Ь 4 ° Ii ° K °

, Kj I, If l,Kj 1, Т4 О, , а, 1 , Ь, 1, а О, Ь 0, с О, ,e 1 , f 1, q OnHa семи- сегментном индикаторе засветится

цифра 3.

Анализируя и далее таким же образом работу предлагаемого счетчика для семисегментных индикаторов,получим все значения сигналов на выходах делителя частоты и дешифратора (диаграммы на фиг.2 при всех i), которые сведены в таблицу.

Формула изобретения

Счетчик импульсов для семисегментных индикаторов, содержащий первый,

0

5

0

5

0

5

0

5

0

второй, третий и четвертый 1К-тригге- ры, четырнадцать элементов И и семь элементов ИЛИ и имеющий.выходы а,Ь, c,d,e,f,q для подключения соответствующих элементов семисегментного индикатора, счетные входы всех триггеров которого соединены с тактовой шиной устройства, а R-входы - с шиной сбро- fca, прямой выход второго тригге- 1ра соединен с первым входом первого элемента И, выход которого подключен к I-входу четвертого триггера, инверсный выход которого соединен с первым входом второго элемента И, выход е устройства соединен с выходом первого элемента ИЛИ, а выход а устройства - с выходом второго элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, выход d устройства соединен с выходом третьего элемента ИЛИ, а выход четвертого элемента ИЛИ соединен с выходами а1, Ьи устройства, выход четвертого элемента И соединен с первым входом пятого элемента ИЛИ, выход которого соединен с выходом q устройства, прямой выход четвертого триггера соединен с выходом устройства, первыми входами четвертого и пятого элементов И, первый вход шестого элемента И соединен с первым входом первого элемента И, первый вход седьмого элемента И соединен с вторым входом четвертого элемента И и инверсным выходом третьего триггера, второй вход - с инверсным выходом первого триггера и первым входом восьмого элемента И, а выход - с первым входом четвертого элемента ИЛИ, первый вход восьмого элемента И соединен с первым входом дечятого элемента И, выход которого подключен к первому входу шестого эчемента ИЛИ, выход которого соединен с выходом f устройства, а второй вход - с выходом второго элемента И, прямой выход первого триггера подключен к первому входу десятого элемента И, первый вход одиннадцатого элемента И соединен с первым входом второго элемента I и вторым входом четвертого элемс птл ИЛИ, выход двенадцатого элемента И подключен к выходу b устройства, первый вход пятого элемента И подключен к первому входу тринадцатого элемента II, выход которого подключен к второму входу пятого элемента IL1K, вь:ход с устройства соединен с БЫХОДОМ седьмого элемента ИЛИ,

71580550

вход которого соединен с выховк в в

дом пятого элемента И, а второй - с выходом четырнадцатого элемента И, отличающийся тем, что, с целью повышения быстродействия, инверсный выход третьего триггера подключен к I- и К-входам первого триггера и второму входу одиннадцатого элемента И, выход которого соединен с вторым входом второго и первыми входами первого и третьего элементов ИЛИ, прямой выход первого триггера соединен с вторым входом шестого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий вход которого соединен с выходом восьмого элемента И, первым входом третьего и вторым входом тринадцатого элемента И, инверсный выход первого триггера соединен с первым входом двенадцатого элемента И и вторым входом первого элемента И, выход которого соединен с К-входом четвертого триггера и вторым входом пятого элемента И, К-вход третьего триггера

8

5

5

0

подключен к прямому выходу второго триггера, К-вход которого соединен с I-входом третьего триггера и шиной логической единицы, а 1-вход - с прямым выходом третьего триггера и вторыми входами третьего, десятого и двенадцатого элементов И, выход десятого элемента И соединен с вторым входом второго элемента И, третьим входом четвертого элемента ИЛИ и первым входом четырнадцатого элемента И, второй вход которого подключен к первому входу второго и третьему входу двенадцатого элементов И, а третий вход - к второму входу восьмого элемента И и инверсному выходу второго триггера, прямой выход четвертого триггера подключен к третьему входу третьего и второму входу девятого элементов И, выход седьмого элемента И соединен с третьими входами пятого и шестого элементов ИЛИ, выход тринадцатого элемента И - с вторым входом третьего элемента ИЛИ.

ев

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Декадный счетчик в семисегментном коде | 1987 |

|

SU1432767A1 |

| Декадный счетчик для семисегментных индикаторов | 1983 |

|

SU1172005A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1359906A1 |

| Счетчик импульсов с цифровой индикацией | 1987 |

|

SU1478325A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

Изобретение относится к импульсной технике и может быть использовано в измерительных устройствах и электронных часах. Цель изобретения - повышение быстродействия. Счетчик импульсов состоит из четырех IK-триггеров, четырнадцати элементов И и семи элементов ИЛИ. Цель достигается изменением старых и введением новых связей между элементами схемы. Это позволяет в цепях управления I- и K-входами триггеров уменьшить количество последовательно включенных логических элементов, что приводит к повышению быстродействия примерно на 30% и получение симметричного выходного импульса. 2 ил., 1 табл.

| Справочник по интегральным микросхемам | |||

| - М.: Энергия, 1980 | |||

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-11-15—Подача