UTFI

ю

J-1

5

1,

6

FI

15

-Jgb®

ел

30

И:)пбретен1и относится к телевиэи- 1И11ой тех)ике и может быть использо- цано в телевизионных передаюищх уст- poFJcTiuix повышенной разрешающей споСО()НОСТИ .

Цель изобретения - поньш ение раз- ре111аю1цей способности.

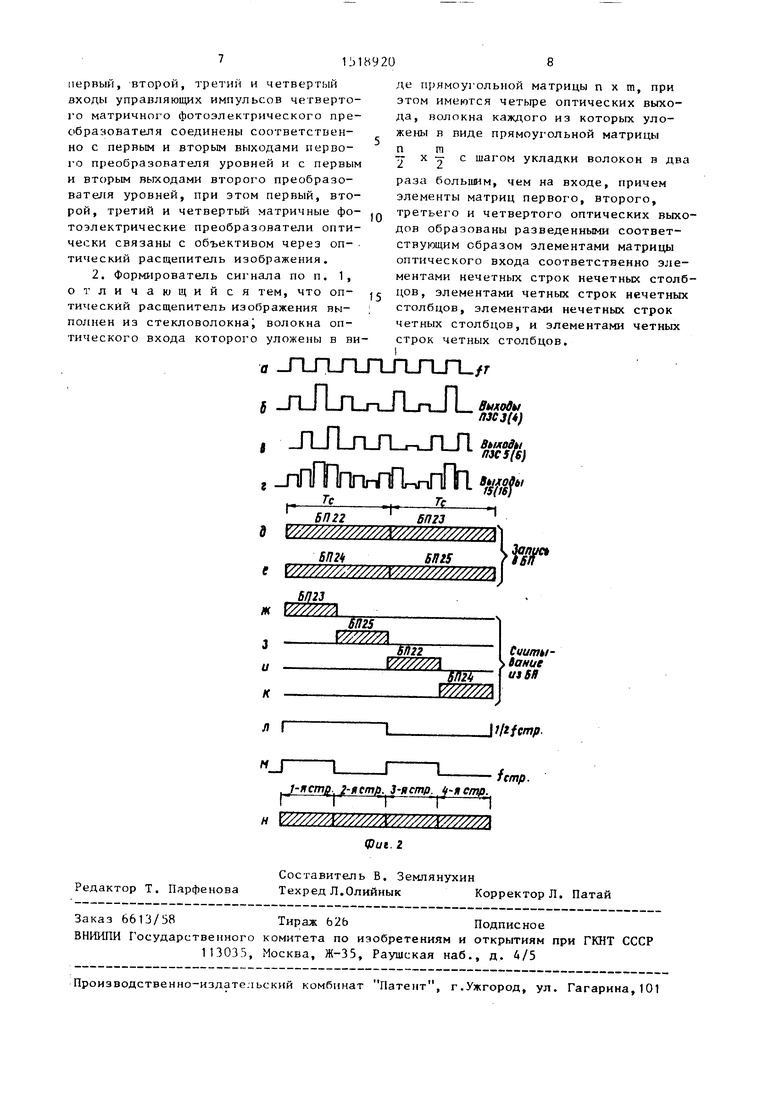

На фиг. 1 представлена структурная оптико-электрическая схема формиро- вателя сигнала изображения; на фиг.2 временные диаграммы, поясняющие его работу.

Формирователь содержит объектив 1 , оптический расщепитель 2 изображения, первый, второй, третий и четвертый матричные фотоэлектрические преобразователи (МФЭП) 3-6, первый и второй преобразователи уровней 7 и 8, .блок 9 эадержки, первый, второй, тре- тий, четвертый и пятый видеоусилители 10 - 14, первый и второй переключатели 1Ь и 16 сигналов, инвертор 17, первый, второй, третий и четвертый электронные ключи 18 - 21, первый, второй, третий и четвертый блоки 22 - 25 памяти, первый, второй, третий и I четвертый формирователи 26 - 29 управляющих импульсов, сумматор 30 и

синхрогенератор 31.

Формирователь сигнала изображения работает следующим образом.

Световой поток, несуп(ий изображение, поступает через объектив 1 на оптической расщепитель 2 изображения, который поэлементно расщепляет изобра жение после объектива на четыре составляющих следующим образом: изобра- же1те, образованное нечетными элемен- тами нечетных строк исходного изображения, подается на оптический вход первого МФЭП 3; четными элементами нечетнь х строк - на третий МФЭП 5; нечетными элементами четных строк - на строй МФЭП 4; четными элементами четных строк - на четвертый МФЭП 6. При этом шаг расположения элементов в составляющих изображения равен шагу светочувствительных элементов МФЭП в данном направлении. Все МФЭП вьтол- нены на матричных ПЗС и работают в типовом режиме. Производится преобразование локальных световых потоков в заряды подвижных носителей, накопление зарядов в элементах секции накопления и перенос зарядов сначала в секцию памяти, а затем в выходной регистр .

о 5

s о З п

(1 кции и;1 ьс)11Л(Ч1Ия н памяти всех МФЭП работают синфаг н) от фааных им- иульсов cHtiXporeiiepaTOpa 31 через пер- Bbrf i преобразователь 7 уровней. Выходные регистры первого н второго МФЭП 3 и 4 синфазно выводят видеосигнал от элементов изображения (фиг. 2б), а третьего и четвертого МФЭП 5 и 6 синфазно между собой, но с задержкой на полпериоца частоты опроса элементов относительно моментов вывода - первый двух МФЭП (фиг. 2в) . Это достиг ается управлением регистров третьего и четвертого МФЭП 5 и 6 регистровыми фазными импульсами синхрогенератора 31, задержанными введеным блоком 9 и усиленными вторым преобразователем 8 уровней.

Видеосигнал от каждого МФЭП усиливается одним из четырех видеоусилителей (10,,11, 13, 14). Усиленные и выравненные по размаху видеосигналы с выходов видеоусилителей подаются соответственно на входы переключателей 15 и 1Ь сигналов таким образом, что на первых входах первого и второго переключателя сигналов 15 и 16 присутствуют сигналы соответственно четных элементов нечетной и четной строк исходного изображения, на вторых входах - нечетных элементов нечетной и четной строк.

Переключатели 15 и 16 сигналов переключаются импульсами типа меандр. тактовой частоты (фиг. 2а) - частоты опроса элементов МФСИ. С выходов первого и второго переключателей 15 и 16 сигналов имеет соответственно видеог- сигналы нечетной и четной строк исходного изображения (фиг. 2г). В четные периоды строчной частоты видеосигналы с выходов первого и второго переключателей 15 и 16 сигналов через открытые управляюпщм импульсом с выхода синхрогенератора 31 через инвертор 17 четные электронные ключи 19 и 21 записываются соответственно во второй и четвертой блоки 23 и 25 памяти (фиг. 2 д, е), в нечетные периоды открыты нечетные электронные ключи 18, 20, и видеосигналы записываются в первый и третий блоки 22 и 24 памяти (фиг. 2 д, е). Управляются электрон- , ные ключи импульсами полустрочной частоты типа меандр с выхода синхрогенератора 31 (фиг. 2л). В срочные периоды (фиг. 2м), когда идет параллельная запись видеосигналов в чет0

IS us 9 2 о

ные блоки памяти, иечетиьи; блоки памяти опраишваются последовательно с улноенион частотой и наоборот. Видеосигналы с выходов всех блоков 22 - 2Ь памяти (фиг. 2, ж, э, и, к) поступают через сумматор 30 на третий ви-; деоусилитель 12, выход которого является выходом устройства (фиг. 2н).

Каждый блок 22 - 25 памяти управ- Q ляется своим формирователем 26 - 29 управляющих импульсов, который генерирует импульсы, определяющие режим работы памяти (запись или считывание), а также импульсы с частотами записи 15 и считывания информации.

Таким образом, за один строчньй период со всех матричньсх ПЗС выводится по одной строке, а на выходе устройства мы имеем две строки с удвоенным 20 числом элементов в каждой (фиг. 2н).

Формула изобретения

1. Формирователь сигнала изображения, содержащий объектив, первый и второй матричные фотоэлектрические преобразователи, информационные выходы которых соединены с входами соответственно первого и второго видеоусилителей, первьй, второй, третий и четвертый электронные ключи, информационные входы которьк объединены, а также последовательно соединенные сумматор и третий видеоусилитель, выход которого является выходом формирователя сигнала изображения, первый второй, третий и четвертый входы сумматора соединены с выходами соответственно первого, второго, третьего и четвертого блоков памяти, управляющие входы которых соединены с выходами соответственно первого, второго, третьего и четвертого формирователей управляющих импульсов, первые и вторые входы которых соответственно объединены, а третьи входы объединены и соединены с выходом строчной частоты синхрогенератора, первый, второй, третий и четвертый выходы управляюпдах импульсов которого соединены соответственно с первым, вторым, третьим и четвертым входами первого преобразователя уровней, первый, второй, третий и четвертый выходы которого соединены соответственно с объединенными первыми, вторыми, третьими и четвертыми входами управляющих импульсов первого и второго матричных фотоэлектриQ5

0

5

0

5

0

5

0

5

ческих преобрлзсшателей, л также ин- , вход KOT(ip)i O объединен с управляю1Ц11ми входами первого и третьего электронных ключей, с четвертыми входами первого и третьего формирователей управляьэщих импульсов li соединен с выходом псшустрочной частоты синхрогенератора, при этом управляющие входы второго и четвертого электронных ключей совместно объединены с четвертыми входами второго и четвертого формирователей управляющих импульсов и соединены с выходом инвертора, информационные входы первого, второго, третьего и четвертого блоков памяти соответственно соединены с выходами первого, второго, третьего и четвертого электронных ключей, а информационные входы первого и второго, третьего и четвертого электронных ключей попарно объединены, о т л и- чающийся тем, что, с целью повышения разрешающей способности, введены четвертый и пятый видеоусилители, первый и второй переключатели сигналов, блок задержки, второй преобразователь уровней, оптический расщепитель изображения, третий и четвертый матричные фотоэлектрические преобразователи, информационные выходы которых соединены соответственно с входами четвертого и пятого видеоусилителей, выходы которых соединены, соответственно с первыми информационными входами первого и второг о переключателей сигналов, вторые информационные входы которых соединены соответственно с выходами первого и второго видеоусилителей, управляюп(ие входы первого и второго переключателей сигналов объединены и соединены с выходом тактовой частоты синхрогенератора, выходы удвоенной и учетверенной тактовой частоты которого соединены соответственно с первым и вторым входами первого формирователя управляющих импульсов, при этом третий и четвертый входы первого преобразователя уровней объединены, соответственно, с первыми и вторыми входами блока задержки, первый и второй выхолт,ы которого соединены соответственно с первым и вторым входами второго преобразонатсля уровней, одноименные первые, Biopbie, третьи и четвертые входы управляющих импульсов третьего и четвертого матричных фотоэлектрических преоОразовате- лей соответственно об1-)е.чине11п1, причем,

первый, второй, третий и четвертый входы управляющих импульсов четвертого матричного фотоэлектрического преобразователя соединены соответствен- но с первым и вторым выходами перво- I o преобразователя уровней и с первым и вторым выходами второго преобразователя уровней, при этом первый, второй, третий и четвертый матричные фо- тоэлектрические преобразователи оптически связаны с объективом через оптический расщепитель изображения.

2. Формирователь сигнала по п. 1, отличающийся тем, что оп- тический расщепитель изображения вы- полнен из стекловолокна; волокна оптического входа которого уложены в виде прямоугольной матрицы п х т, при этом имеются четыре оптических выхода, волокна каждого из которых уложены в виде прямоугольной матрицы

m

п

2 2

с шагом укладки волокон в два

раза большим, чем на входе, причем элементы матриц первого, второго, третьего и четвертого оптических выходов образованы разведенными соответствующим образом элементами матрицы оптического входа соответственно элементами нечетных строк нечетных столбцов, элементами четных строк нечетных столбцов, элементами нечетных строк четных столбцов, и элементами четных

строк четных столбцов.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигнала изображения | 1984 |

|

SU1277427A1 |

| Устройство для пространственной фильтрации изображений | 1988 |

|

SU1622954A1 |

| Телевизионное устройство для обнаружения объектов | 1989 |

|

SU1663779A2 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| Устройство формирования телевизионного сигнала | 1981 |

|

SU1069187A1 |

| Телевизионное устройство для обнаружения объектов | 1987 |

|

SU1533018A1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ | 2010 |

|

RU2426265C1 |

| Устройство для измерения скорости | 1986 |

|

SU1429036A1 |

| Телевизионная система | 1981 |

|

SU1160611A1 |

Изобретение относится к телевизионной технике. Цель изобретения - повышение разрешающей способности. Формирователь содержит объектив 1, оптический расщепитель 2 изображения, матричные фотоэлектрические преобразователи (МФЭП) 3-6, преобразователи 7 и 8 уровней, блок задержки 9, видеоусилители 10-14, переключатели 15 и 16 сигналов, инвертор 17, электронные ключи 18-21, блоки памяти 22-25, формирователи 26-29 управляющих импульсов, сумматор 30 и синхрогенератор 31. Цель достигается тем, что за один строчный период со всех МФЭП 3-6 выводится по одной строке, а на выходе устройства образуются две строки с удвоенным числом элементов в каждой. Формирователь по п.2 ф-лы отличается выполнением расщепителя 2 из стекловолокна, у которого волокна оптического входа уложены в виде прямоугольной матрицы. 1 з.п.ф-лы, 2 ил.

а JlJlJTrLTLTLrU/r в JгЛJl.rJ rJLJ-3 |

, JlJLriJl.JlJl

г jifllTirnriwi

| Формирователь сигнала изображения | 1984 |

|

SU1277427A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-30—Публикация

1987-06-23—Подача