Изобретение относится к вычислительной технике, может быть использовано для контроля и наладки периферийных устройств (ПУ) и является усовершенствованием известного имитатора канала по авт. св. № 1174927.

Целью изобретения является повышение производительности имитатора.

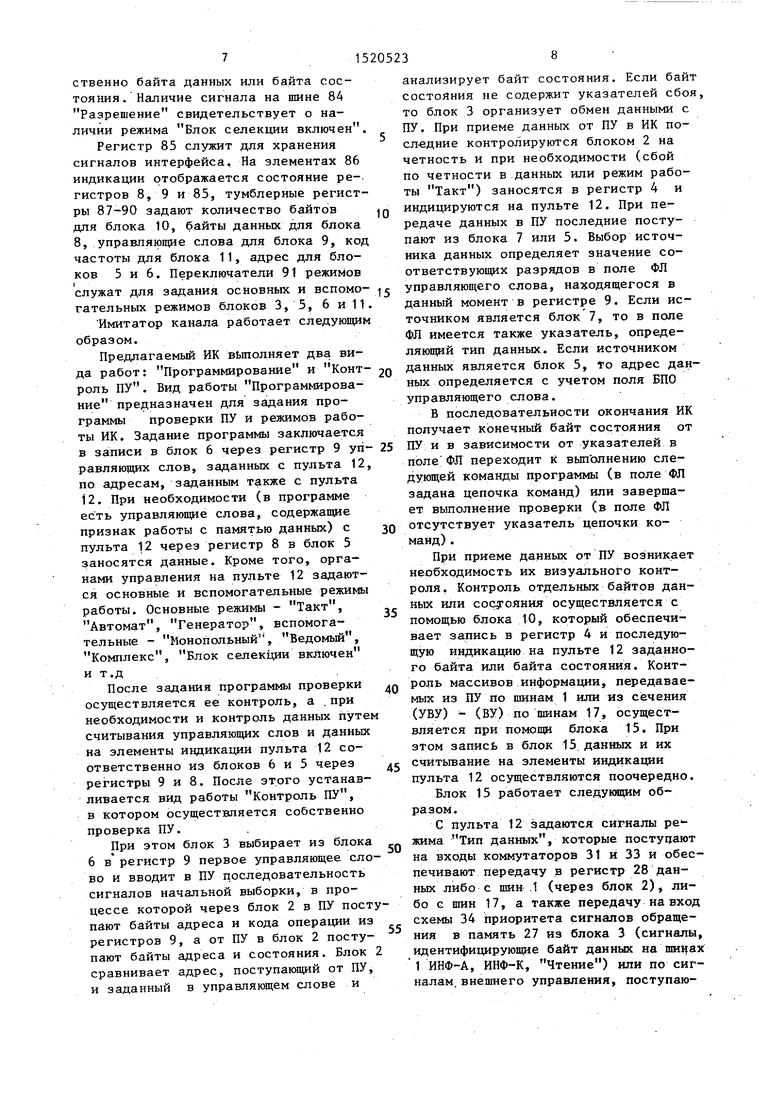

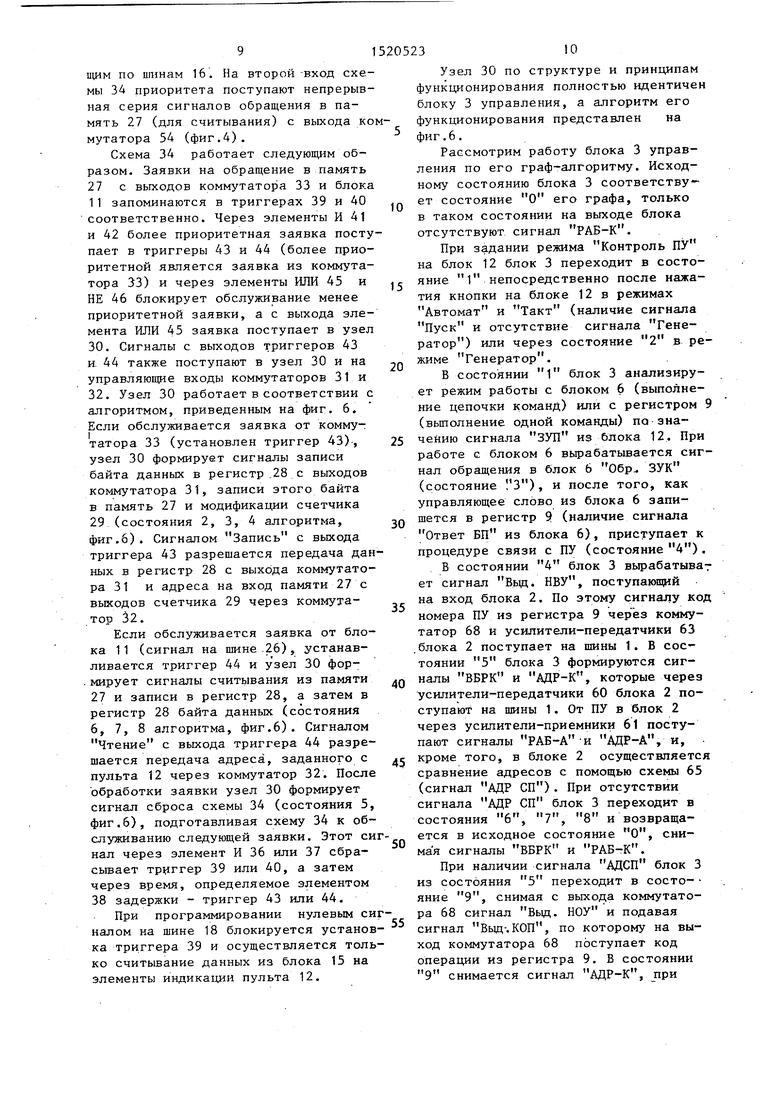

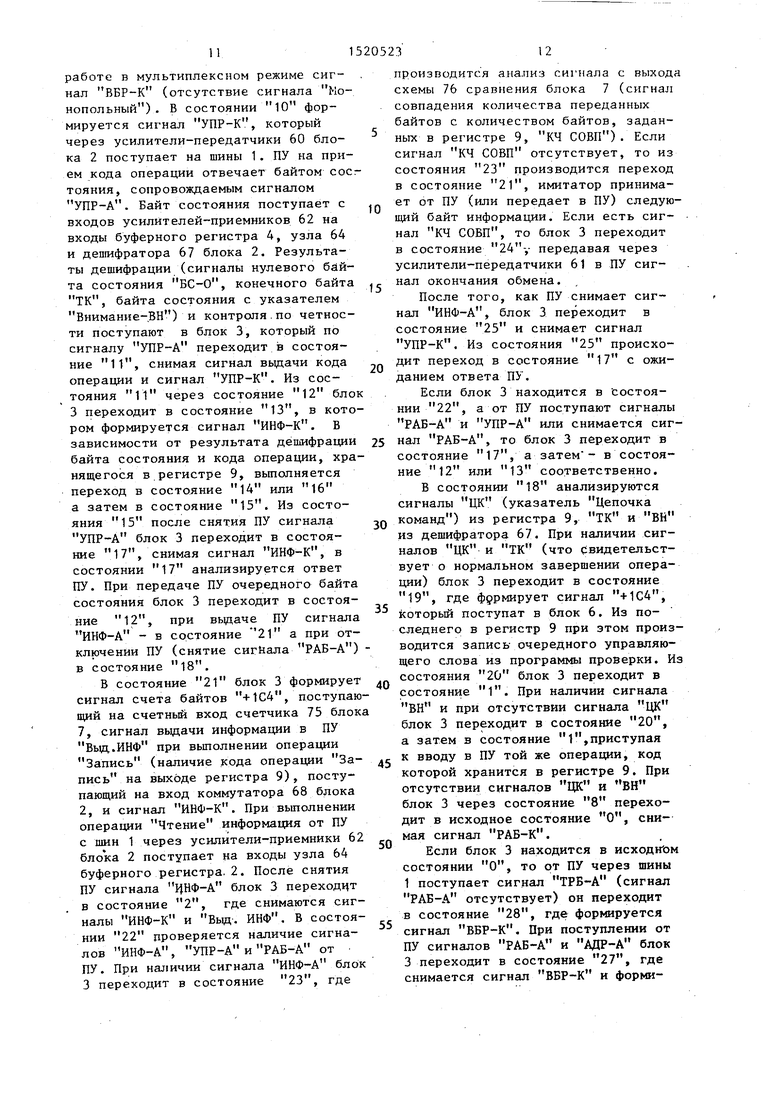

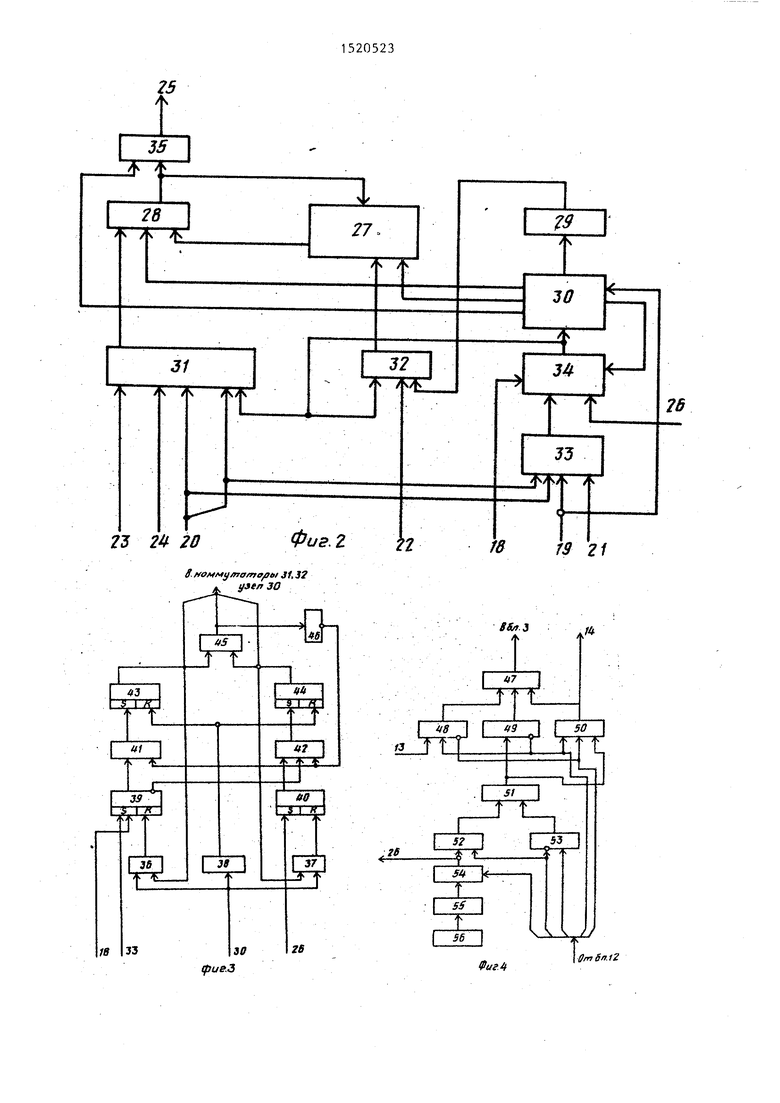

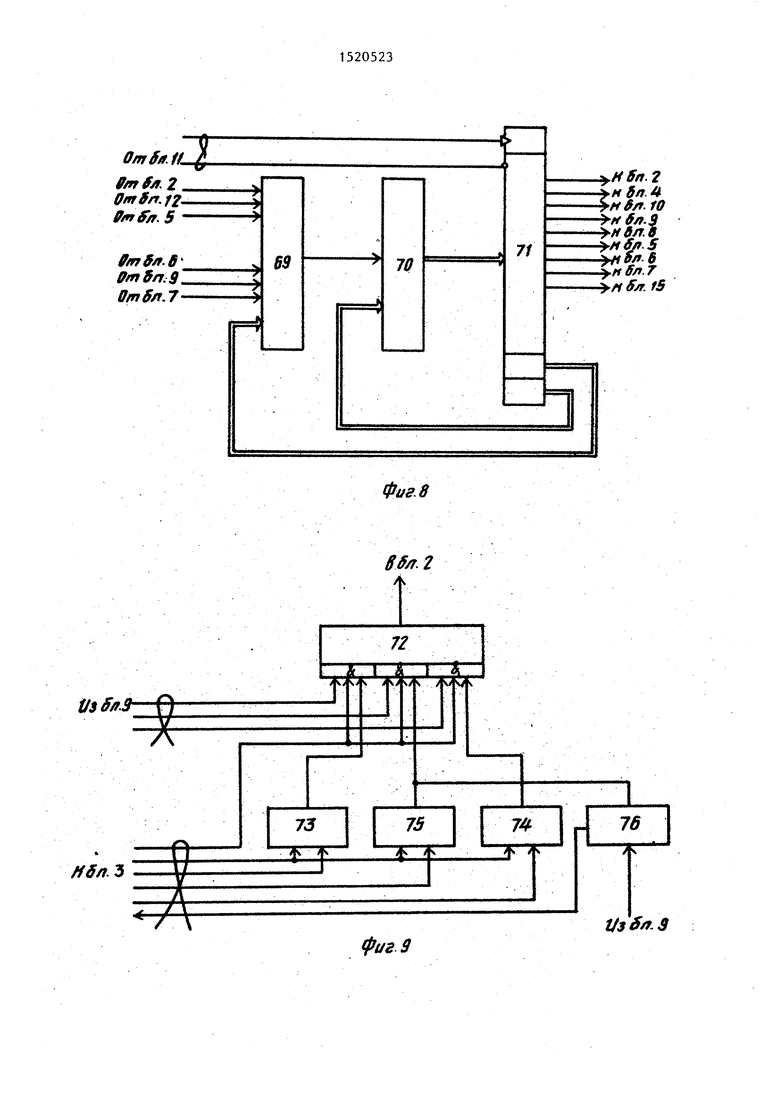

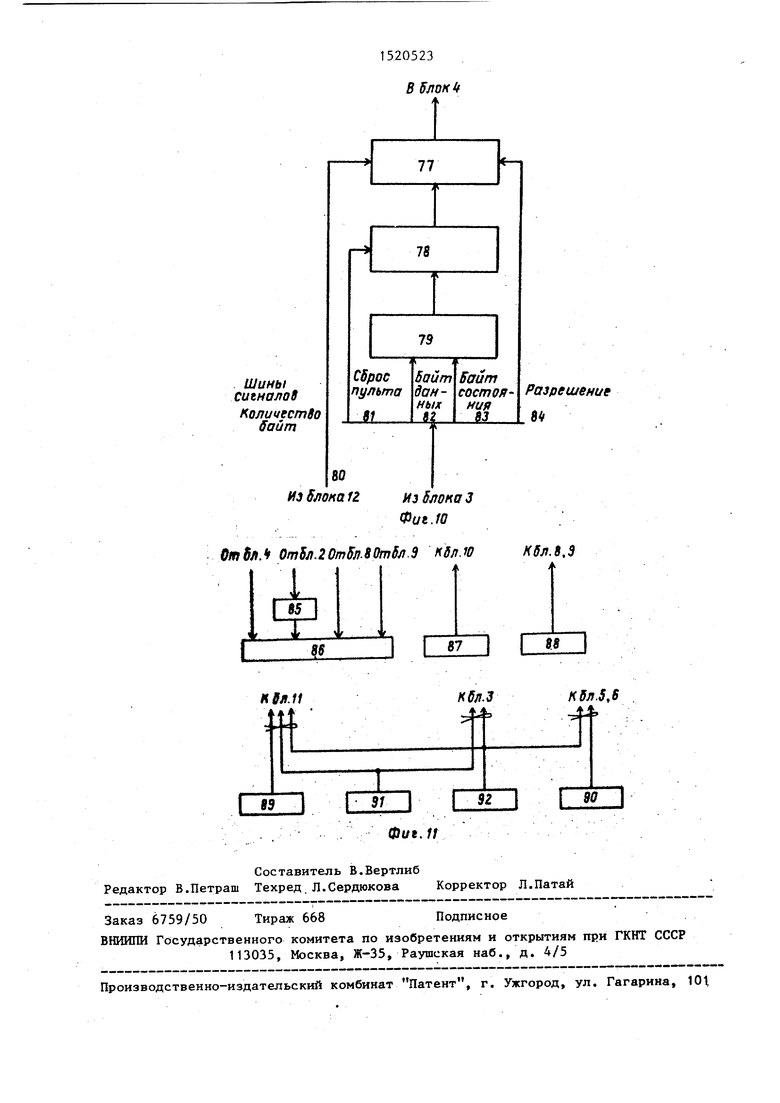

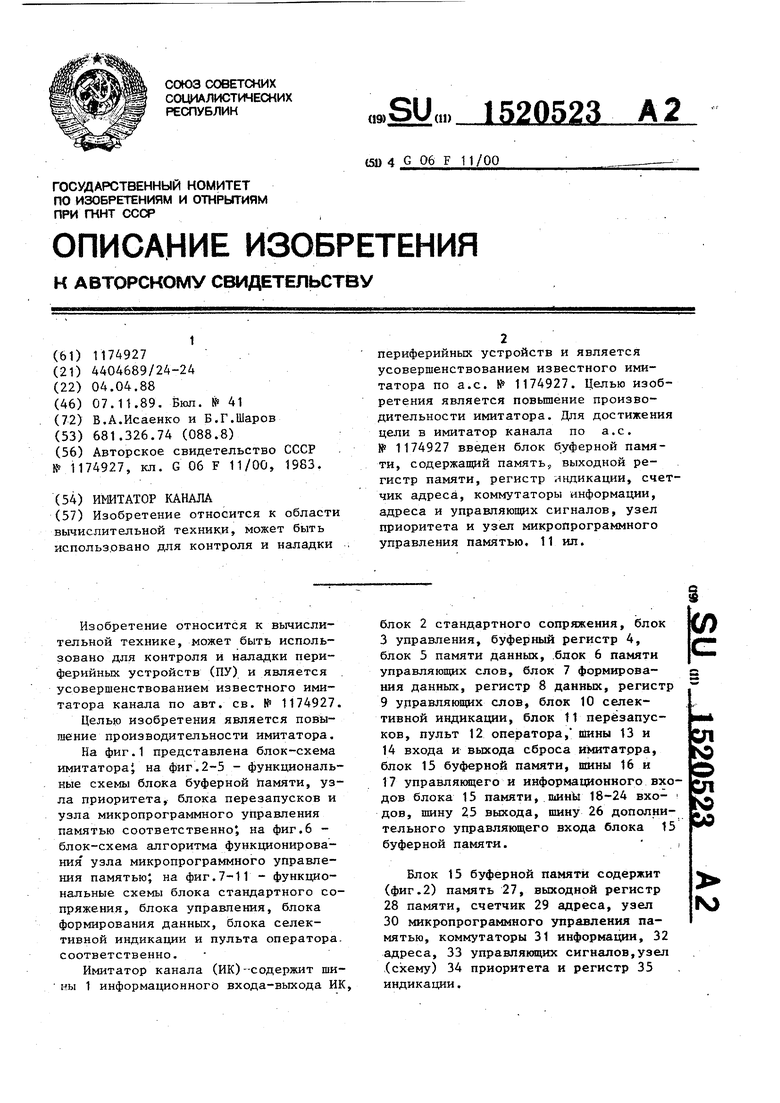

На фиг.1 представлена блок-схема имитатораJ на фиг.2-5 - функциональные схемы блока буферной памяти, узла приоритета, блока перезапусков и узла микропрограммного управления памятью соответственно на фиг.6 - блок-схема алгоритма функционирования узла микропрограммного управления памятью; на фиг.7-11 - функциональные схемы блока стандартного сопряжения, блока управления, блока формирования данных, блока селективной индикации и пульта оператора, соответственно.

Имитатор канала (ИК)-содержит ши- ны 1 информационного входа-выхода ИК,

блок 2 стандартного сопряжения, блок 3 управления, буферный регистр 4, блок 5 памяти данных, .блок 6 памяти управляющих слов, блок 7 формирования данных, регистр 8 данных, регистр 9 управляющих слов, блок 10 селективной индикации, блок 11 перезапусков, пульт 12 оператора, шины 13 и 14 входа и выхода сброса имитатрра, блок 15 буферной памяти, шины 16 и 17 управлякнцего и информационного входов блока 15 памяти, шинЬ: 18-24 вхо- ROB, шину 25 выхода, шину 26 дополнительного управляющего входа блока 15 буферной памяти. ,

Блок 15 буферной памяти содержит (фиг.2) память 27, выходной регистр 28 памяти, счетчик 29 адреса, узел 30 микропрограммного управления памятью, коммутаторы 31 информации, 32 адреса, 33 управлякицих сигналов,узел (схему) 34 приоритета и регистр 35 индикации.

(Л

G

:л

N5

л

N9

:л

1Ч

3

Узел 34 содержит (фиг. 3) элементы И 36 и 37, элемент 38 задержки, триггеры 39 и 40, элементы И 41 и 42,.триггеры 43 и 44, элемент ИЛИ 45 и элемент 46 НЕ.

Блок 11 содержит (фиг. 4) элемент ИЛИ 47, элементы И 48-50, формирователь 51 импульсов, элементы И 52 и 53, коммутатор 54, делитель 55 частоты и генератор 56.

Узел 30 микропрограммного управления памятью содержит (фиг.5) входной мультиплексор 57, постоянную память (ПЗУ) 58 и выходной регистр 59

Блок 2 стандартного сопряжения содержит (фиг.7) усилители-передатчики 60, усилители-приемники 61 сигналов идентификации и управления, усилители-приемники 62 и усилители-передатчики 63 сигналов и ШИН-К, узел 64 контроля четности, схему 65 сравнения адресов, узел 66 формирования контрольного разряда, дешифратор 67 байта состояния, коммутатор 68.

Блок 3 управления содержит (фиг.8 мультиплексор 69, постоянную память (ПЗУ) 70 и выходной регистр 71.

Блок 7 формирования данных содержит (фиг.9) коммутатор 72, регистр

73сдвига, постоянную память (ПЗУ)

74символьных кодов, счетчик 75 и схему 76 сравнения.

Блок 10 селективной индикации со держит (фиг. 10) схему 7.7 сравнения, счетчик 7в, элемент ИЛИ 79, шину 80 сигнала Количество байт первого входа блока, шины 81-84-сигналов

Сброс пульта, Байт данных,Байт состояния, Разрешение второго входа блока.

Пульт 12 оператора содержит (фиг.11) регистр 85, элементы 86 индикации, тумблерные регистры 87- 90, переключатель 91, кнопку 92 сбрса и начальной установки.

Посредством шин 1 имитатор канал подключается к ПУ. Блок 2 осуществляет согласование входных и выходных сигналов интерфейса, дополняет КОДВ1 адресов операций и данных, передаваемых в ПУ по шинам 1 контрольным разрядом, сравнивает адрес, поступивший от ПУ по шинам t, с заданным, контролирует на четность байты адресов, состояний и данных, поступающих от ПУ по ШИН-А, дешифрирует байт состояния. Блок 3 обеспечивает координацию работы всех узлов ИК с

0

5

0

5

помощью управляющих и синхронизирующих сигналов, формируемь1х блоком в соответствии с заданной программой режимами сигналами от ПУ и алгоритмами работы. Буферный регистр 4 служит для запоминания байтов данных, адресов и состояний, поступающих по ШИП-А от ПУ через блок 2, содержимое регистра 4 индицируется на пульте 12 оператора. Блок 5 памяти данных служит для хранения и вьдачи данных в ПУ по ШИН-К через регистр 8 и блок 2, предварительно занесенных в блок 5 с пульта 12 оператора. Эти данные необходимы для разметки носителей задания границ и зон и т.д. при работе с ПУ типа накопителей на лентах, дисках, барабанах (т.е. данные, организованные в произвольные, достаточно структуры) . Блок 6 памяти управляющих слов служит для хранения заданной с пульта 12 оператора программы состояний из управляющих слов следующего формата:

НПУ : КОП : КЧ : ФА : БПД,

где НПУ - поле номера периферийного устройства}

КОП - поле кода операции, КЧ - поле количества чисел

РПД - поле базы памяти данных ,

ФА - поле флажков.

Содержание полей НПУ и КОП передается в ПУ. Со; ержимое поли КЧ определяется количеством передаваемых в ПУ или принимаемых ot ПУ байтов данных. В поле ФЛ содержатся флажки- признаки блокировки счета данных це- цочки данных и команд, работы с тем или другим типом данных и т.п. Поле базы памяти данных предн значе- но дл программного разбиения паия- ти данньпс на зоны путем базирования адреса.

Блок 7 формирует переменный код для передачи в ПУ. Регистры 8 и 9 служат для хранения текупрсс значений соответственно байта данньос и управляющего слова. Запись в регистры 8 и 9 производится из соотйетствую- щего блока 5 или 6 или с пульта 12. Блок 10 селективной индикации управляют записью в буферный регистр 4

заданных с пульта байтов данных или состояний, поступающих от ПУ. Блок 11 перезапусков обеспечивает циклический режим работы ИК при наличии неис

правностей в ПУ, а также совместную работу с другим ИК, который подключается к шинам 13 и 14. Пульт 12 содержит органы управления и индикации и служит для задания режимов работы ИК и контроля работы ПУ.

Блок 15 буферной памяти обеспечивает прием, хранение и вьщачу на элементы индикации пульта 12 массивов информации, поступающих из ПУ по шинам 1 или из сечения управление внешним устройством (УВУ) - внешнее устройство (ВУ). К шинам 16 и 17 подключается сечение УВУ-ВУ. Память 27 обеспечивает накопление массивов поступающей информации.„Выходной регистр 28 служит для хранения текущего информационного слова. Счетчик 29 служит для формирования адреса памяти 27 при записи информации. Узел 30 микропрограммного управления памятью вырабатывает сигналы, управляющие работой памяти 27. Коммутатор 31 служит для передачи информации,на вход регистра 28, коммутатор 32 - для передачи информации на адресный вход памяти 27, коммутатор 33 - для передачи информации на вход схемы 34 приоритета . Схема 34 приоритета является арбитром при одновременном обращении к памяти 27 с выходов коммутатора 3 и блока 11. Регистр 35 индицирует текущее информационное слово. Элемент И 36 обеспечивает передачу сигналов на вход сброса триггера 39. Элемент И 37 обеспечивает передачу сигналов, поступающих на вход сброса триггера 40.

Элемент 38 задерживает сигнал,

поступакнций из узла 30 на входы сброса триггеров 43 и 44.

Триггеры 39 и 40 фиксируют поступление заявок соответственно из коммутатора 30 и с шины 26. Элементы И 41 и 42 обеспечивают пезредачу сигналов на установочные входы триггеров 43 и 44, Триггеры 43 и 44 фиксируют сиг налы, определяющие режим работы памя- ти 27. Элемент ИЛИ 45 служит для передачи сигналов с выходов триггеров 43 и 44 на вход схемы 34 приоритета. Элемент НЕ 43 запрещает передачу сигналов через элементы И 41 и 42 при наличии сигнала на выходе элемента ИЛИ 45.

Входной мультиплексор 57 содержит набор микрокоманд узла 30. Выходной

10

15

20

25

40

Q

30

35

4S

5

регистр 59 обеспечивает хранение текущей микрокоманды ПЗУ 58.

Усилители-передатчики 60 и 63 предназначены для усиления сигналов, передаваемых в ПУ, а усилители-приемники 61 и 62 - для усиления сигналов, принимаемых от ПУ. Контроль по четности байтов, принимаемых от ПУ, осуществляется с помощью узла 64.Схема 65 сравнивает номер ПУ, переданный по ШИН-К, с номером ПУ, принятым по ШИН-А, с вьздачей результата в блок 3. С помощью узла 65 формируется контрольный разряд байта, передаваемого в ПУ, с передачей его в ПУ. Дешифратор 66 определяет тип байта состояния, принимаемого от ПУ.

Через коммутатор 68 поступает информация из регистра 9 (при вьщаче номера ПУ) либо из регистра 8, либо из блока 7 (при передаче данных в ПУ) .

Назначение отдельных узлов блока 3 управления идентично назначению соответствующих узлов узла 30.

Регистр 73, ПЗУ 74 и счетчик 75 блока 7 формируют массивы чисел, передаваемые в ПУ. Коммутатор 72 по указателям, поступающим из регистра 9, выбирает один из трех источников этих чисел - регистр 73, ПЗУ 74 или счетчик 75.

Указатели содержатся в соответствующем поле управляющего слова. Независимо от того, какой из трех источников выбран, счетчик 75 подсчитывает количество переданных байтов, а схема 76 сравнивает с количеством, заданным в соответствунмцем поле управляющего слова. Сигнал сравнения поступает в блок 3.

Схема 77 сравнивает номер поступившего байта данных (состояний) с набранным на блок 12. Счетчик 78 обеспечивает подсчет количества пос тупивших байтов данных (состояния) от ПУ. Элемент ИЛИ 79 обеспечивает передачу сигналов Байт данных с шины 82 или Байт состояния с шины 83 на счетный вход счетчика 78, По шине 80 сигнала Количество байт из блока 12 передается номер требуе мого байта. По сигналу на шине 81 Сброс пульта осуществляется начальный сброс счетчика 78. По шинам 82 и 83 Байт данных л Байт состояния передаются сигналы, свидетельствующие о поступлении из ПУ соответ71520523

ственно байта данных или байта состояния. Наличие сигнала на шине 84 Разрешение свидетельствует о наличии режима Блок селекции включен.

Регистр 85 служит для хранения сигналов интерфейса, На элементах 86 индикации отображается состояние ре-, гистров 8, 9 и 85, тумблерные регистры 87-90 задают количество байтов для блока 10, байты данных для блока 8, управляющие слова для блока 9, код частоты для блока 11, адрес для блоков 5 и 6. Переключатели 91 режимов служат для задания основных и вспомо- i гательных режимов блоков 3, 5, 6 и 11.

Имитатор канала работает следующим образом.

Предлагаемый ИК вьтолняет два ви10

анализирует байт состояния. Если байт состояния не содержит указателей сбоя то блок 3 организует обмен данными с ПУ. При приеме данных от ПУ в ИК последние контролируются блоком 2 на четность и при необходимости (сбой по четности в.данных или режим работы Такт) заносятся в регистр 4 и индицируются на пульте 12. При передаче данных в ПУ последние поступают из блока 7 или 5. Выбор источника данных определяет значение соответствующих разрядов в поле ФЛ управляющего слова, находящегося в данный момент в регистре 9. Если источником является блок 7, то в поле ФЛ имеется также указатель, определяющий тип данных. Если источником

да работ: Программирование и Конт- 2о данных является блок 3, то адрес дан30

роль ПУ. Вид работы Программирование предназначен для задания программы проверки ПУ и режимЬв работы ИК. Задание программы заключается в записи в блок 6 через регистр 9 yri- 25 равляющих слов, заданных с пульта 12, по адресам, заданным также с пульта 12. При необходимости (в программе есть управляющие слова, содержащие признак работы с памятью данных) с пульта 12 через регистр 8 в блок 5 заносятся данные. Кроме того, органами управления на пульте 12 задаются основные и вспомогательные режимы работы. Основные режимы - Такт, Автомат, Генератор, вспомогательные - Монопольный, Ведомый, Комплекс, Блок селекции включен и т.д.

После задания программы проверки осуществляется ее контроль, а .при необходимости и контроль данных путем считывания управляющих слов и данных на элементы индикации пульта 12 соответственно из блоков 6 и 5 через регистры 9 и 8. После этого устанавливается вид работы Контроль ПУ, в котором осуществляется собственно проверка ПУ. .

При этом блок 3 выбирает из блока 6 в регистр 9 первое управляющее слово и вводит в ПУ последовательность сигналов начальной выборки, в процессе которой через блок 2 в ПУ поступают байты адреса и кода операции из регистров 9, а от ПУ в блок 2 поступают байты адреса и состояния. Блок 2 сравнивает адрес, поступающий от ПУ, и заданный в управляющем слове и

35

40

45

50

55

ньгх определяется с учетом поля БПО управляющего слова.

В последовательности окончания ИК получает конечный байт состояния от ПУ и в зависимости от указателей в поле ФЛ переходит к вьт олнению следующей команды программы (в поле ФЛ задана цепочка команд) или завершает выполнение проверки (в поле ФЛ отсутствует указатель цепочки команд) .

При приеме данных от ПУ возникает необходимость их визуального контроля. Контроль отдельных байтов данных или состояния осуществляется с помощью блока 10, который обеспечивает запись в регистр 4 и последующую индикацию на пульте 12 заданного байта или байта состояния. Контроль массивов информации, передаваемых из ПУ ito шинам 1 или из сечения (УВУ) - (ВУ) по шинам 17, осуществляется при помощи блока 15. При этом запись в блок 15 данных и их считывание на элементы индикации пульта 12 осуществляются поочередно.

Блок 15 работает следукшр1м образом.

С пульта 12 задаются сигналы ре-- жима Тип данных, которые постуцают на входы коммутаторов 31 и 33 и обеспечивают передачу в регистр 28 данных либо с шин .1 (через блок 2), либо с шин 17, а также передачу на вход схемы 34 приоритета сигналов обращения в память 27 из блока 3 (сигналы, идентифигщрующие байт данных на 1 ИНФ-А, ИНФ-К, Чтение) или по сигналам, внешнего управления, поступаю

0

анализирует байт состояния. Если байт состояния не содержит указателей сбоя, то блок 3 организует обмен данными с ПУ. При приеме данных от ПУ в ИК последние контролируются блоком 2 на четность и при необходимости (сбой по четности в.данных или режим работы Такт) заносятся в регистр 4 и индицируются на пульте 12. При передаче данных в ПУ последние поступают из блока 7 или 5. Выбор источника данных определяет значение соответствующих разрядов в поле ФЛ управляющего слова, находящегося в данный момент в регистре 9. Если источником является блок 7, то в поле ФЛ имеется также указатель, определяющий тип данных. Если источником

данных является блок 3, то адрес дан0

5

5

0

5

0

5

ньгх определяется с учетом поля БПО управляющего слова.

В последовательности окончания ИК получает конечный байт состояния от ПУ и в зависимости от указателей в поле ФЛ переходит к вьт олнению следующей команды программы (в поле ФЛ задана цепочка команд) или завершает выполнение проверки (в поле ФЛ отсутствует указатель цепочки команд) .

При приеме данных от ПУ возникает необходимость их визуального контроля. Контроль отдельных байтов данных или состояния осуществляется с помощью блока 10, который обеспечивает запись в регистр 4 и последующую индикацию на пульте 12 заданного байта или байта состояния. Контроль массивов информации, передаваемых из ПУ ito шинам 1 или из сечения (УВУ) - (ВУ) по шинам 17, осуществляется при помощи блока 15. При этом запись в блок 15 данных и их считывание на элементы индикации пульта 12 осуществляются поочередно.

Блок 15 работает следукшр1м образом.

С пульта 12 задаются сигналы ре-- жима Тип данных, которые постуцают на входы коммутаторов 31 и 33 и обеспечивают передачу в регистр 28 данных либо с шин .1 (через блок 2), либо с шин 17, а также передачу на вход схемы 34 приоритета сигналов обращения в память 27 из блока 3 (сигналы, идентифигщрующие байт данных на 1 ИНФ-А, ИНФ-К, Чтение) или по сигналам, внешнего управления, поступаю

uydM по шинам 16. На второй вход схемы 34 приоритета поступают непрерывная серия сигналов обращения в память 27 (для считывания) с выхода комутатора 54 (фиг,4),

Схема 34 работает следующим образом. Заявки на обращение в память 27 с выходов коммутатора 33 и блока 11 запоминаются в триггерах 39 и 40 соответственно. Через элементы И 41 и 42 более приоритетная заявка поступает в триггеры 43 и 44 (более приоритетной является заявка из коммутатора ) и через элементы ИЛИ 45 и НЕ 46 блокирует обслуживание менее приоритетной заявки, а с выхода элемента ИЛИ 45 заявка поступает в узел 30, Сигналы с выходов триггеров 43 и. 44 также поступают в узел 30 и на управляющие входы коммутаторов 31 и 32, Узел 30 работает в соответствии с алгоритмом, приведенным на фиг, 6. Если обслуживается заявка от коммутатора 33 (установлен триггер 43), узел 30 формирует сигналы записи байта данных в регистр .28 с выходов коммутатора 31, записи этого байта в память 27 и модификации счетчика 29 (состояния 2, 3, 4 алгоритма, фиг,6), Сигналом Запись с выхода триггера 43 разрешается передача данных в регистр 28 с выхода коммутатора 31 и адреса на вход памяти 27 с выходов счетчика 29 через коммутатор 32,

Если обслуживается заявка от блока 11 (сигнал на шине .26), устанавливается триггер 44 и узел 30 формирует сигналы считывания из памяти 27 и записи в регистр 28, а затем в регистр 28 байта данных (состояния 6, 7, 8 алгоритма, фиг.6), Сигналом Чтение с выхода триггера 44 разрешается передача адреса, заданного с пульта 12 через коммутатор 32. После обработки заявки узел 30 формирует сигнал сброса схемы 34 (состояния 5, фиг.6), подготавливая схему 34 к обслуживанию следующей заявки. Этот синал через элемент И 36 или 37 сбра- сьшает триггер 39 или 40, а затем через время, определяемое элементом 38 задержки - триггер 43 или 44.

При программировании нулевым синалом на шине 18 блокируется установка триггера 39 и осуществляется только считывание данных из блока 15 на элементы индикации пульта 12.

0

5

0

5

0

5

0

5

0

Узел 30 по структуре и принципам функционирования полностью идентичен блоку 3 управления, а алгоритм его функционирования представлен на фиг.6,

Рассмотрим работу блока 3 управления по его граф-алгоритму. Исходному состоянию блока 3 соответствует состояние О его графа, только в таком состоянии на выходе блока отсутствуют сигнал РАБ-К.

При задании режима Контроль ПУ на блок 12 блок 3 переходит в состояние 1 непосредственно после нажатия кнопки на блоке 12 в режимах Автомат и Такт (наличие сигнала Пуск и отсутствие сигнала Генератор) или через состояние 2 в режиме Генератор,

В состоянии 1 блок 3 анализирует режим работы с блоком 6 (выполнение цепочки команд) или с регистром 9 (вьшолнение одной команды) по значению сигнала ЗУП из блока 12. При работе с блоком 6 вырабатьшается сигнал обращения в блок 6 Обр ЗУК (состояние 3), и после того, как управляющее слово из блока 6 запишется в регистр 9 (наличие сигнала Ответ БП из блока 6), приступает к процедуре связи с ПУ (состояние 4) . Б состоянии 4 блок 3 вырабатыват ет сигнал Вьщ. НВУ, поступающий на вход блока 2. По этому сигналу код номера ПУ из регистра 9 через коммутатор 68 и усилители-передатчики 63 .блока 2 поступает на шины 1. В состоянии 5 блока 3 формируются сигналы ВБРК и АДР-К, которые через усилители-передатчики 60 блока 2 поступают на шины 1. От ПУ в блок 2 через усилители-приемники 61 поступают сигналы РАБ-А -и АДР-А, и, кроме того, в блоке 2 осуществляется сравнение адресов с помощью схемы 65 (сигнал АДР СП), При отсутствии сигнала АДР СП блок 3 переходит в состояния 6, 7, 8 и возвращается в исходное состояние О, снимая сигналы ВБРК и РАБ-К.

При наличии сигнала АДСП блок 3 из состояния 5 переходит в состо- яние 9, снимая с выхода коммутатора 68 сигнал Выд. НОУ и подавая сигнал Выд-.КОП, по которому на выход коммутатора 68 поступает код операции из регистра 9. В состоянии 9 снимается сигнал АДР-К, при

работе в мультиплексном режиме сигнал ВБР-К (отсутствие сигнала Монопольный) . В состоянии 10 формируется сигнал УПР-К, который через усилители-передатчики 60 блока 2 поступает на шины 1. ПУ на прием кода операции отвечает байтом сосг тояния, сопровождаемым сигналом УПР-А. Байт состояния поступает с входов усилителей-приемников 62 на входы буферного регистра 4, узла 64 и дешифратора 67 блока 2. Результаты дешифрации (сигналы нулевого байта состояния БС-О, конечного байта ТК, байта состояния с указателем Внимание-ВН) и контроля.по четности поступают в блок 3, который по сигналу УПР-А переходит в состояние 11, снимая сигнал выдачи кода операции и сигнал УПР-К. Из состояния 11 через состояние 12 блок 3 переходит в состояние 13, в котором формируется сигнал ИНФ-К. В зависимости от результата дешифрации байта состояния и кода операции, хранящегося в.регистре 9, выполняется переход в состояние 14 или 16 а затем в состояние 15. Из состояния 15 после снятия ПУ сигнала УПР-А блок 3 переходит в состояние 17, снимая сигнал ИНФ-К, в состоянии 17 анализируется ответ ПУ. При передаче ПУ очередного байта состояния блок 3 переходит в состояние 12, при вьщаче ПУ сигнала ИНФ-А - в состояние 21 а при отключении ПУ (снятие сигйала РАБ-А) в состояние 18.

В состояние 21 блок 3 формирует сигнал счета байтов +1С4, поступающий на счетньй вход счетчика 75 блок 7, сигнал вьщачи информации в ПУ Вьщ..ИНФ при вьтолнении операции Запись (наличие кода операции Запись на выходе регистра 9), поступающий на вход коммутатора 68 блока 2, и сигнал ИНФ-К. При выполнении операции Чтение информация от ПУ с шин 1 через усилители-приемники 62 блока 2 поступает на входы узла 64 буферного регистра. 2. После снятия ПУ сигнала ИНФ-А блок 3 переходит в состояние 2, где снимаются сигналы ИНФ-К и Выд. ИНФ. В состоянии 22 проверяется наличие сигналов ИНФ-А, УПР-А и РАБ-А от ПУ. При наличии сигнала ИНФ-А блок 3 переходит в состояние 23, где

0

5

0

5

0

5

0

5

производится анализ сигнала с выхода схемы 76 сравнения блока 7 (сигнал совпадения количества переданных байтов с количеством байтов, заданных в регистре 9, КЧ СОВП). Если сигнал КЧ СОВП отсутствует, то из состояния 23 производится переход в состояние 21, имитатор принимает от ПУ (или передает в ПУ) следующий байт информации. Если есть сигнал КЧ СОВП, то блок 3 переходит в состояние ,- передавая через усилители-передатчики 61 в ПУ сигнал окончания обмена.

После того, как ПУ снимает сигнал ИНФ-А, блок 3 переходит в состояние 25 и снимает сигнал УПР-К. Из состояния 25 происходит переход в состояние 17 с ожиданием ответа ПУ.

Если блок 3 находится в состоянии 22, а от ПУ поступают сигналы РАБ-А и УПР-А или снимается сигнал РАБ-А, то блок 3 переходит в состояние 17, а затем - в состояние 12 или 13 соответственно.

В состоянии 18 анализируются сигналы ЦК (указатель Цепочка команд) из регистра 9, ТК и ВН из дешифратора 67. При наличии сигналов ЦК и ТК (что свидетельствует о нормальном завершении операции) блок 3 переходит в состояние 19, где формирует сигнал +1С4, который поступат в блок 6. Из последнего в регистр 9 при этом производится запись очередного управляющего слова из программы проверки. Из состояния 20 блок 3 переходит в состояние 1. При наличии сигнала ВН и при отсутствии сигнала ЦК блок 3 переходит в состояние 20, а затем в состояние 1,приступая к вводу в ПУ той же операции, код которой хранится в регистре 9. При отсутствии сигналов ЦК и ВН блок 3 через состояние 8 дит в исходное состояние мая сигнал РАБ-К.

Если блок 3 находится в HcxoMMbM состоянии О, то от ПУ через шины 1 поступает сигнал ТРБ-А (сигнал РАБ-А отсутствует) он переходит в состояние 28, где формируется сигнал ВБР-К. При поступлении от ПУ сигналов РАБ-А и АДР-А блок 3 переходит в состояние 27, где снимается сигнал и формиперехо-0, онируется сигнал . В состоянии 27 анализируется сигнал .АДР-А, после снятия сигнала АДР-А блок 3 переходит в состояние 17, снимая сигнал УПР-К, и ожидает ответа от ПУ.

Формула изобретения

Имитатор канала по авт. св. № 1174927, отличающийся тем, что, с целью повышения производительности имитатора, в него введен блок буферной памяти, причем первый выход блока стандартного сопряжения и второй вход-выход условий блока управления соединены соответственно с первыми информационным и командным входами блока буферной памяти, ад- ресньй, пусковой входы и вход начальных условий которого подключены соответственно к первому, третьему и шестому выходам пульта оператора, пятый индикаторный вход которого соединен с выходом блока буферной памяти, синхронизирующий вход которого соединен с третьим выходом блока перезапусков, а вторые инфррмационньй и командный входы блока буферной па- :мяти являются соответственно информационным и командным входами загрузки имитатора, причем блок буферной памяти содержит коммутатор информации и коммутатор управляющих сигнало .первые и вторые информационные входы которых являются соответственно первыми и вторыми информационными и командными входами блока буферной памяти, а управляющие входы - пусковым

0

5

0

5

0

5

входом блока буферной памяти, счетчик адреса, соединенный выходом с первым информационным входом коммутатора адреса, второй вход которого является адресным входом блока буферной памяти, а выход соединен с адресным входом памяти, информационный вход и выход которой соединены соответственно с выходом и первым информационным входом выходного регистра, памяти, вторым информационным входом и управляюпщм входом соединенного соответственно с выходом коммутатора информации и первым выходом узла мик- пропрограммного управления памятью, второй и третий выходы которого соединены соответственно с управляющим входом памяти и счетным входом счетчика адреса, узел приоритета и регистр индикации, причем входы режима и маски узла приоритета являются соответственно входами синхронизации и начальных условий блока буферной памяти, а информационный и синхронизирующий входы соединены соответственно с выходом коммутатора управляющих сигналов и четвертым выходом узла микропрограммного управления памятью, вход условий и пятый выход которого соединены соответственно с первым командным входом блока буферной памяти и синхровходом регистра индикации, информационный вход и выход которого подключены соответственно к выходу памяти и индикаторному выходу блока буферной памяти, выход узла приоритета соединен с адресными входами коммутатора адреса и коммутатора информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1987 |

|

SU1467555A1 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1984 |

|

SU1310823A2 |

| Имитатор канала | 1985 |

|

SU1280633A2 |

| Имитатор канала | 1985 |

|

SU1429115A2 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

Изобретение относится к области вычислительной техники, может быть использовано для контроля и наладки периферийных устройств и является усовершенствованием известного имитатора по а.с. N 1174927. Целью изобретения является повышение производительности имитатора. Для достижения цели в имитатор канала по а.с. N 1174927 введен блок буферной памяти, содержащий память, выходной регистр памяти, регистр индикации, счетчик адреса, коммутаторы информации, адреса и управляющих сигналов, узел приоритета и узел микропрограммного управления памятью. 11 ил.

«

If

e.ffOMf ymofrroflbi 31,32 ж узел 30

/в |33

75

1рие.З

т

Г9 21

8S/t3

I «51

sJ

из

50

.Г,5/ I

:гб

Л К5/

РигЛ

УЧУ//

1т6пл2

Т

HSfif

I 1 i I I s I

I

нбп.Ъ

t

/ГЛ7«

фиг. 5

i i

I

НбпЗ .З V3 5n.8 Из бп 7 фиг.7

фиг 9

Шины сигналов

Коли естдо байт

80 ИЗ блока И

Om6fl. f ОтЬл.20т5л.От6л.9 Кдл.Ю

W

К9Л.11

В 5лок1(

Байт данныхЛ

faum состоя- мия 83

Разрешение 8if

Из блока 3 Фиь.Ю

Кбл.Ь,3

ПтП Пд I

кбя.з

KSfl.s,6

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1988-04-04—Подача