Изобретение относится к вычислительной технике и омжет быть использовано для контроля и наладки периферийных устройств (ПУ).

Известен имитатор канала ЕС ЭВМ (ЭП3.031.324ТО), содержащий узел установки режимов, узел формирования сигналов идентификации и управления канала, узел фиксирования сбоев информации, фотосчитывающее устройство, узел управления фотосчитывающим устройством, ОЗУ, узел управления ОЗУ, узел управления выдачи адреса ОЗУ и информации ОЗУ, узел приемопередатчиков I интерфейса, имитатор УВУ, блок питания и индикации.

Недостатком данного устройства является большой объем используемого оборудования.

Наиболее близким к предлагаемому техническому решению по достигаемому положительному эффекту и технической сущности является имитатор канала, содержащий блок сопряжения, подключенный соответственно первым и вторым входами-выходами соответственно к информационному входу-выходу имитатора и первому входу-выходу блока управления, первым, вторым и третьим информационными входами соответственно к выходам блока формирования данных, регистра данных и регистра управляющего слова, а первым и вторым выходами - соответственно к информационному входу буферного регистра и первому входу индикации блока задания режима и индикации, первый выход которого соединен с адресными входами блока

памяти данных и блока памяти управляющих слов, выход блока памяти данных подключен к первому информационному входу регистра данных, второй выход блока задания режимов и индикации соединен с вторым информационным входом регистра данных и первым информационным входом регистра управляющих слов, выходы которых соединены соответственно с информ.ационными входами блока памяти данных и блока памяти управляющих слов, выход-регистра управляющего слова подключен «управляющему входу блока формирования данных и к первому входу условия блока управления, вторым входом условия соединенного с третьим выходом блока задания режима и индикации, а выходом подключен ного к первому синхровходу буферного регистра и управляющим входам и входам записи регистра данных и регистра управляющего слова, выходы которых соединены соответственно с вторым, третьим-и четвертым входами индикации блока задания режима и индикации, второй вход-выход блока управления соединен с управляющими входами-выходами блока памяти данных, блока памяти управляющих слов и информационным входом-выходом блока формирования данных, коммутатор, блок перезапусков и блок селективной индикации, причем вход режима блока перезапусков подключен к четвертому выходу блока задания режимов и индикации, первый выход блока перезапусков подключен к входу синхронизации блока управления, вход сброса и второй выход блока перезапусков подключены соответственно к выходу и входу сброса имитатора, информационный и синхронизирующий входы у,бло«а селективной индикации соединены соответственно с пятым выходом блока задания режима и индикации и выходом блока управления, а выход - с вторым управляющим входом буферного регистра, управляющий вход блока памяти данных подключен к выходу регистра управляющего слова, выход блока памяти данных и второй информационный вход регистра управляющего слова соединены соответственное первым информационным входом и выходом коммутатора, второй информационный вход и управляющий вход коммутатора подключены соответственно к выходам регистра управляющего слова и выходу блока управления.

Недостатком известного имитатора является большой объем оборудования, так как для обеспечения функционирования в этом имитаторе используется большое количество запоминающих устройств, включенных в блок постоянной памяти, блок

микропрограммного управления и блок памяти управляющих слов, а также оборудования по управлению этими блоками. Недостатком известного имитатора явпяется также использование ручной проверки правильности данных, считанных из ПУ.

Цель изобретения - сокращение аппаратурных затрат имитатора.

Поставленная цель достигается тем, что

в имитатор канала, содержащий блок сопряжения, блок микропрограммного управления, регистр приема информации, блок оперативной памяти, регистр данных, регистр управляющих слов и первый селектор,

причем первые группы выходов и входов идентификации и управления, группа информационных входов и первая группа информационных выходов блока сопряжения являются группами выходов и входов идентификации и управления, первой группой информационных входов и группой информационных выходов имитатора соответственно, первый, второй и третий информационные входы и вторая группа информационных выходов блока сопряжения соединены с выходом регистра приема информации, регистра данных, с разрядами с нулевого по двадцать третий выхода регистра управляющих слов и группой информационных входов регистра приема информации соответственно, вторые группы входов и выходов идентификации и управления блока сопряжения соединены соответственно с группами выходов и вхоДов блока микропрограммного управления., первый управляющий выход, первый и второй информационные входы которого соединены с управляющим входом, первым и вторым выходами ошибок блока сопряжения

соответственно, второй управляющий выход блока микропрограммного управления соединен с первыми управляющими входами регистра управляющих слов, блока оперативной памяти, регистра дагнных и

управляющим входом регистра приема информации, группа информационных входов блока микропрограммного управления соединена с второй группой информационных входов имитатора, группа управляющих

входов блока микропрограммного управления соединена с вторыми управляющими входами регистра управляющих слов, блока оперативной памяти, регистра данных и подключена к группе управляющих входов

имитатора, входы синхронизации блока микропрограммного управления, регистра приема информации, регистра данных и регистра управляющих слов соединены с группой синхронизирующих входов имитатора, выходы регистра приема информации, региС7ра данных, блока оперативной памяти, регистра управляющих слов и группа информационных выходов блока микропрограммного управления соединены с группой выходов индикации имитатора, введены счетчик адреса, регистр переполнения, счетчик байтов, элемент И и шесть селекторов, причем группы информационных входов первого, второго, третьего, четвертого селекторов и первая группа информационных входов пятого селектора соединены с второй группой информационных входов имитатора, управляющие входы первого, второго, третьего, четвертого, пятого и шестого селекторов, первые управляющие входы счетчика адресов и счетчика байтов подключены к группе управляющих входов имитатора, информационные входы первого и третьего селекторов соединены с разрядами с шестнадцатого по тридцать первый информационного выхода микропрограммного управления, разряды с две-, надцатого по девятнадцатый, с четырнадцатого по двадцать третий, с двадцать четвертого по тридцать первый информационного выхода которого соединены с информационными входами регистра приема информации, второго селектора и с первым информационным входом седьмого селектора соответственно, вторая группа информационных входов и выход пятого селектора соединены с второй группой информационных выходов блока сопряжения и информационным входом блока оперативной памяти соответственно, выход блока оперативной памяти соединен с информационным входом четвертого селектора, выход которого соединен с вторым информационным входом седьмого селектора, выход седьмого селектора соединен с информационным входом регистра данных, адресный вход блока микропрограммного управления и первый информационный вход шестого селектора соединены с адресным входом имитатора, второй информационный вход и выход шестого селектора соединены с информационным входом счетчика адрес и адресным входом блока оперативной памяти соответственно, управляющий вход регистра переполнения соединен с вторыми управляющими входами счетчика адресов и счетчика байтов и подключен к второму управляющему выходу блока микропрограммного управления, первый и второй информационные входы регистра переполнения соединены с выходом переполнения счетчика адреса и выходом переполнения счетчика байтов, информационный вход и третий управляющий вход счетчика адреса соединены с выходом второго селектора и

выходом элемента И соответственно, выход регистра переполнения соединен с входом Окончание обмена блока микропрограммного управления, информационный вход 5 счетчика байтов соединен с выходом третьего селектора, а выход переполнения подключен к первому входу элемента И, разряды с двадцать четвертого по тридцать первый и тридцать второй разряд выхода 10 регистра управляющих слов соединены с входом сигнала Признаки управляющих слов блока микропрограммного управления и вторым входом элемента ИЛИ соответственно, входы синхронизации счетчика 15 адресов, регистра переполнения и счетчика байтов соединены с группой синхронизирующих входов имитатора, информационные выходы счетчика адреса, счетчика байтов, выход регистра переполнения подключены 0 к группе выходов индикации имитатора.

Кроме того, блок микропрограммного управления содержит блок оперативной памяти, регистр микрокоманд, счетчик микрокоманд, счетчик хранения адреса 5 микрокоманд, группу из пяти дешифраторов, регистр уравления ШИН-К, группу из трех триггеров ошибок, регистр управляющих сигналов, два мультиплексора, шесть селекторов, группу элементов ИЛИ, два эле0 мента ИЛИ и элемент И, причем труппа информационных входов первого, второго, третьего и четвертого селекторов соединены с группой информационных входов блока, информационный вход, адресный вход и 5 выход блока оперативной памяти соедине. ны с выходом первого селектора, выходом пятого селектора и информационным входом регистра микрокоманд соответственно, разряды с нулевого по третий и с четвертого 0 по шестой выхода регистра микрокоманд соединены с управляющими и информационными входами дешифраторов группы дешифраторов соответственно, разряды с двадцать восьмого по тридцать первый, с 5 двенадцатого по девятнадцатый, с двадцатого по тридцать первый выхода регистра микрокоманд соединены с информационными входами второго и третьего селекторов и с пер&ым информационным входом 0 шестого селектора соответственно, разряды с девятого по одиннадцатый, и с семнадцатого по девятнадцатый соединены с первыми управляющими входами первого и второго мультиплексоров соответственно, 5 разряды с двенадцатого по тридцать первый выхода регистра микрокоманд соединены с информационным выходом блока, информационный вход и выход четвертого селектора соединены с выходом шестого селектора и информационным входом счетчика микрокоманд соответственно, выход счетчика микрокоманд соединен с информационным входом счетчика хранения адреса микрокоманд и первым информационным входом пятого селектора, второй информационный вход которого подключен к адресному входу блока, выход счетчика хранения адреса микрокоманд соединен с вторым информационным входом шестого селектора, выход второго селектора соединен с информационным входом регистра управления ШИН-К, выход которого соединен с первым управляющим выходом блока, выход третьего селектора соединен с информационным входом редгистра управляющих сигналов, группа выходов которого соединена с первым и вторым информационными входами первого мультиплексора и подключена к группе выходов идентификации и управления блока, третий информационный вход первого мультиплексора соединен с группой информационных входов второго мультиплексора и по ключен к группе входов индентификации и управления блока, четвертый и пятый информационные входы первого мультиплексора соединены с входами сигналов Признаки управляющих слов и Окончание обмена блока соответственно, шестойинформационный вход первого мультиплексора является входом сигнала Цикл и подключен к группе управляющих входов блока, первые управляющие входы первого и второго мультиплексоров соединены с разрядами с девятого по одиннадцатый и с семнадцатого по девятнадцатый выхода регистра микрокоманд соответственно, вторые управляющие входы первого и второ го мультиплексоров соединены с первыми управляющими входами регистра управляющих сигналов, регистра управления ШИН-К, счетчика микрокоманд и триггеров группы триггеров ошибок, с управляющими входами счетчика хранения адресов микрокоманд и шестого селектора, с первым входом элемента ИЛИ и выходами элементов ИЛИ группы элементов ИЛИ, первые входы которых соединены с выходами дешифраторов группы дешифраторов, а вторые входы являются входами сигнала Сброс и подключены к группе управляющих входов блока, управляющие входы пёрвого-пятого селекторов блока оперативной памяти, вторые управляющие входы счетчика микрокоманд, регистра управления ШИН-К, регистра управляющих сигналов vi триггеров группы триггеров ошибок соединены с группой управляющих входов блока, первые и вторые информационные входы триггеров, группы триггеров ошибок подключены к первому и второму информационным входам блока соответственно, а третьи информационные входы триггеров соединены с первым входом второго элемента ИЛИ, вторым входом первого элемента ИЛИ и выходом второго мультиплексора, выход первого мультиплексора соединен с третьим входом первого элемента,ИЛИ и вторым входом второго элемента ИЛИ, выходы триггеров группы триггеров ошибок

0 соединены с четвертым входом первого элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с третьим и четвертым управляющими входами счетчика микрокоманд соответственно, управляющий вход регистра микрокоманд соединен с выходом элемента И, первый вход которого является входом сигнала Внутренний тест и подключен к группе управляющих входов блока, второй вход элемента И соединен с

0 входами синхронизации регистра управления ШИН-К, пегистра управляющих сигналов, счетчика микрокоманд, счетчика хранения адреса микрокоманд, триггеров группы триггеров ошибок и подключен к

5 группе синхронизирующих входов блока, выходы счетчика микрокоманд, счетчика хранения адреса микрокоманд, блока оперативной памяти регистра микрокоманд, триггеров группы триггеров ошибок и регистра управления ШИН-К соединены с группой информационных выходов блока.

Сокращение аппаратурных затрат в предлагаемом устройстве по сравнению с известным достигается введением в него

5 счетчика байтов, счетчика адреса, регистра переполнения, элемента И и шести селекторов, а также, за счет изменения структуры блока микропрограммного управления (введения загружаемой памяти микропрограмм

0 и элементов, обеспечивающих возможность организации диагностических микропрограмм) и оригинальных связей между блоками.. В результате обеспечивается сокращение обьема оборудования блоков.

Кроме этого, техническое решение позволяет также расширить функциональные возможности устройства, обеспечивая как ручную, так и автоматическую проверку пра0 вильности данных, считанных из ПУ.

В результате патентных исследований установлено, что предлагаемый имитатор канала обладает существенными отличиями, так как по сравнению с известными техническими решениями, 6н характеризуется новой совокупностью существенных признаков, позволяющей получить достижение поставленной цели.

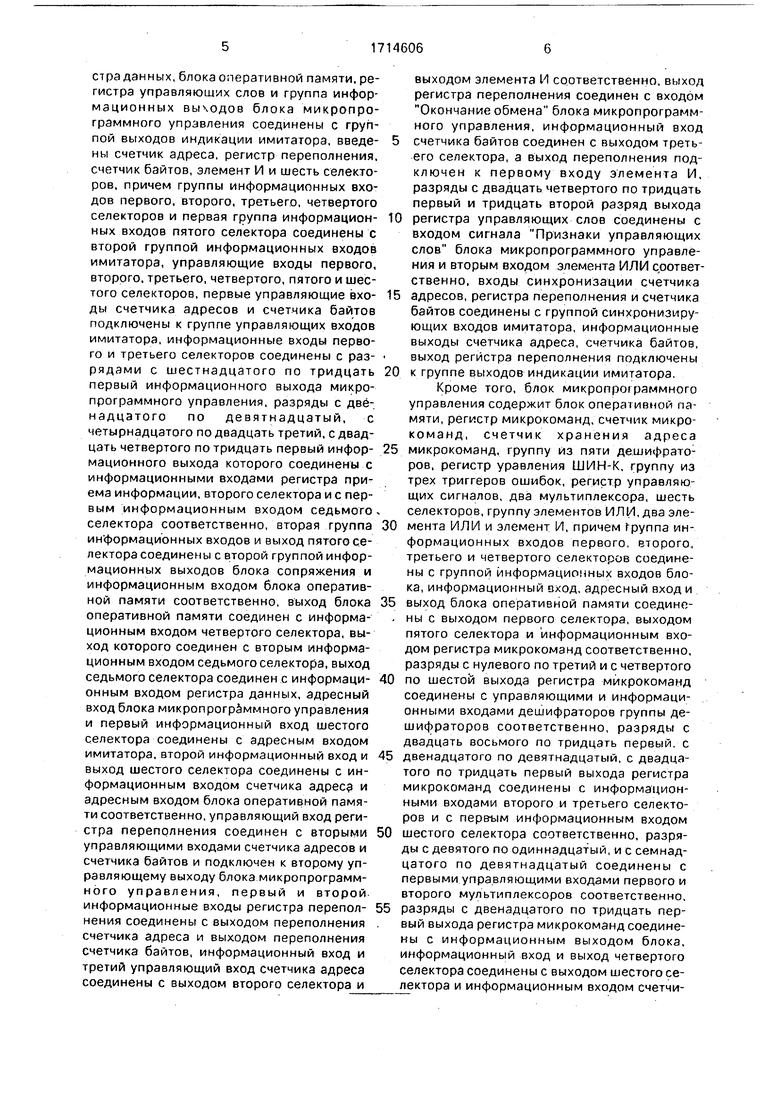

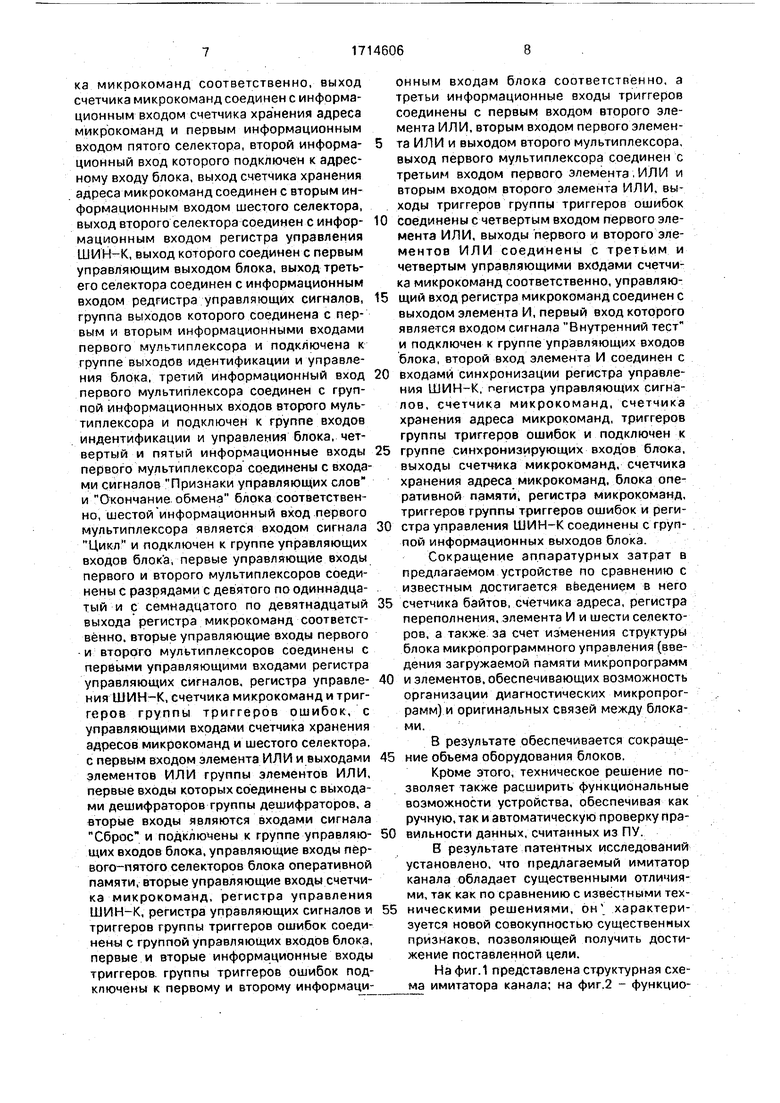

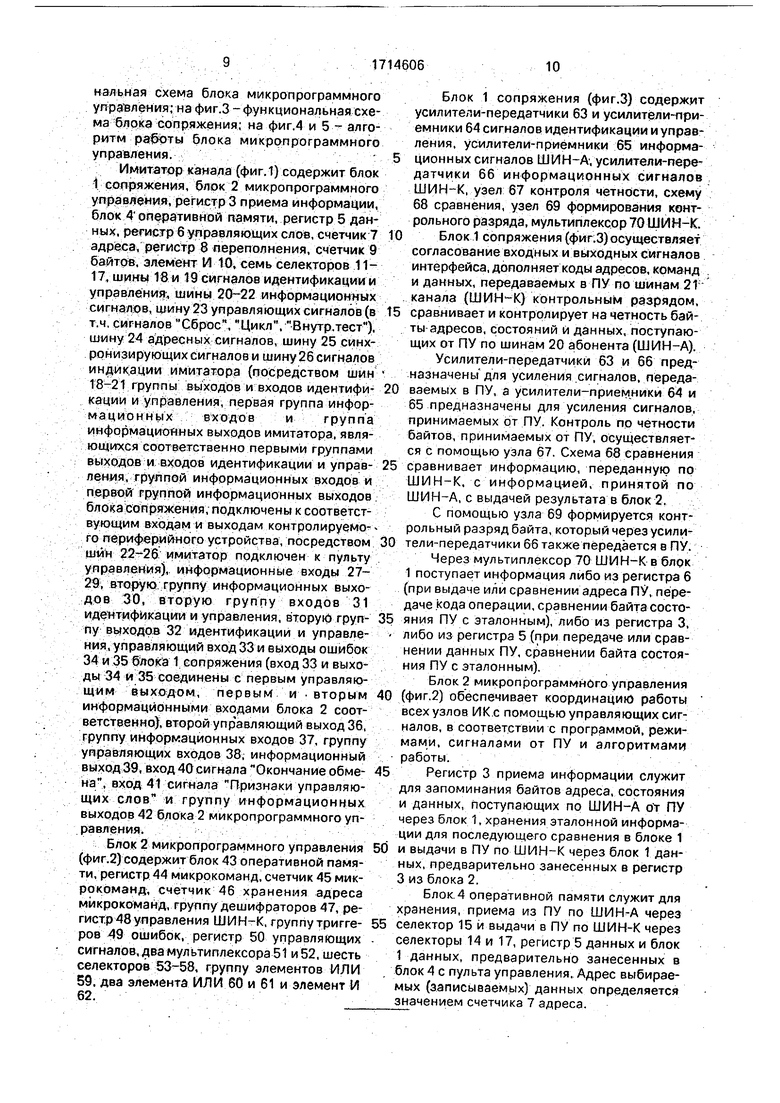

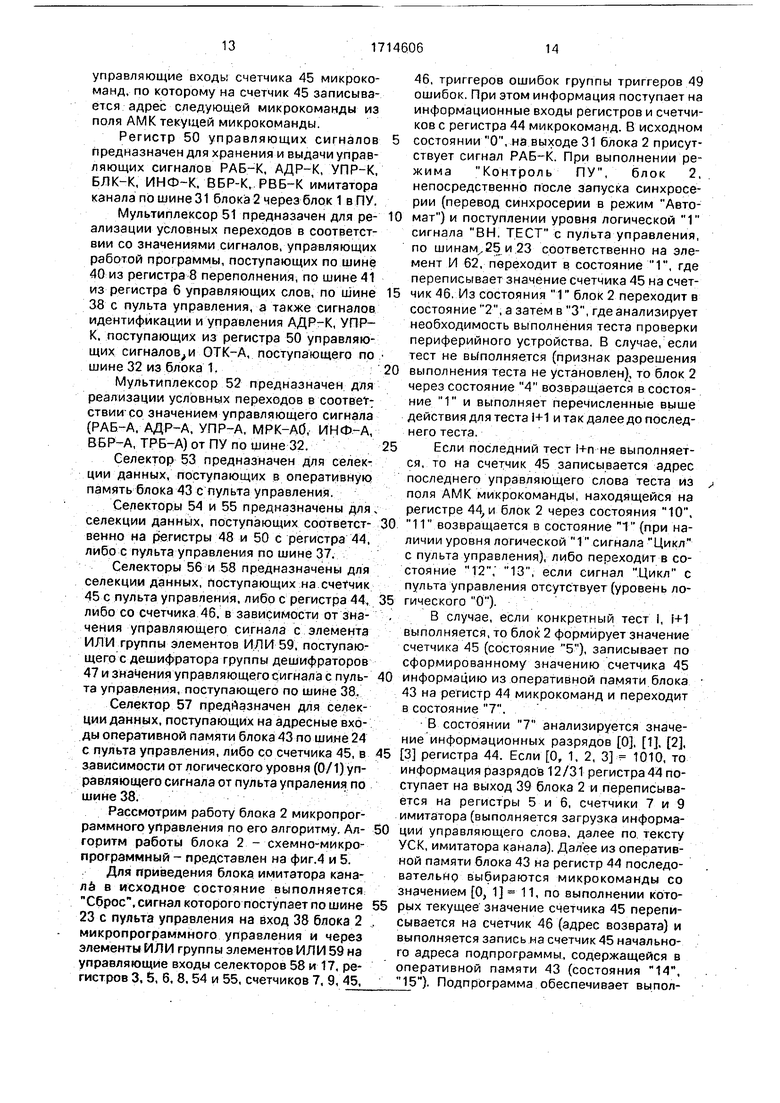

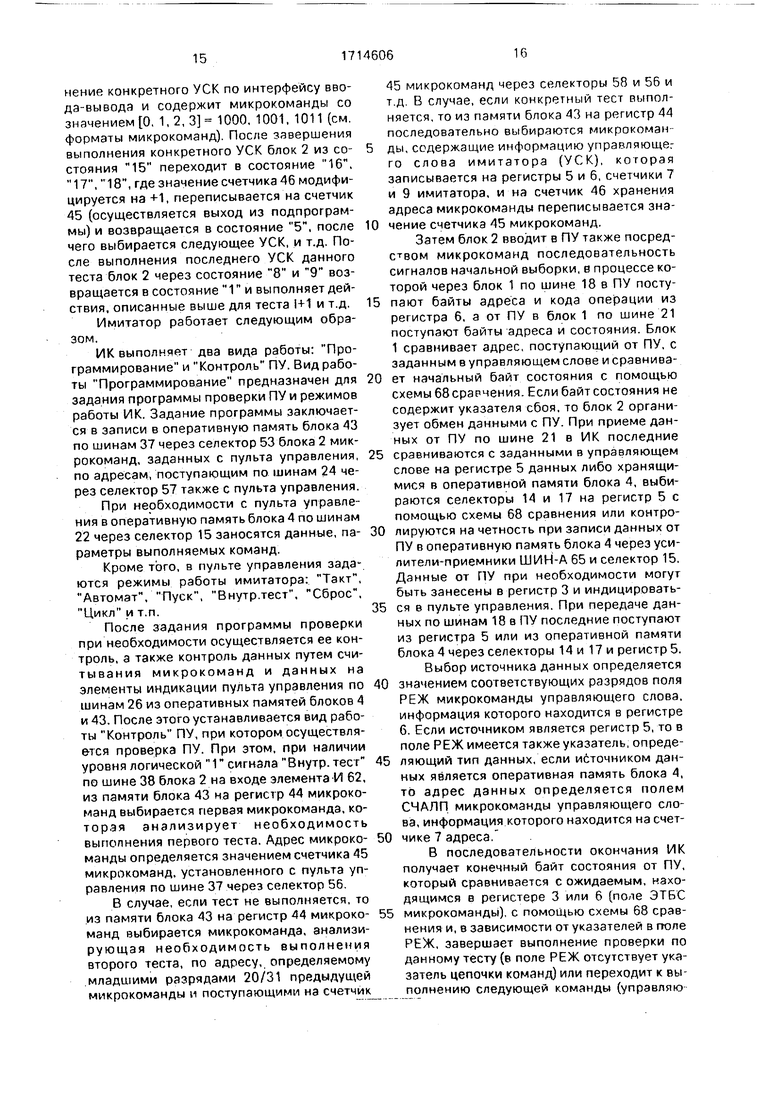

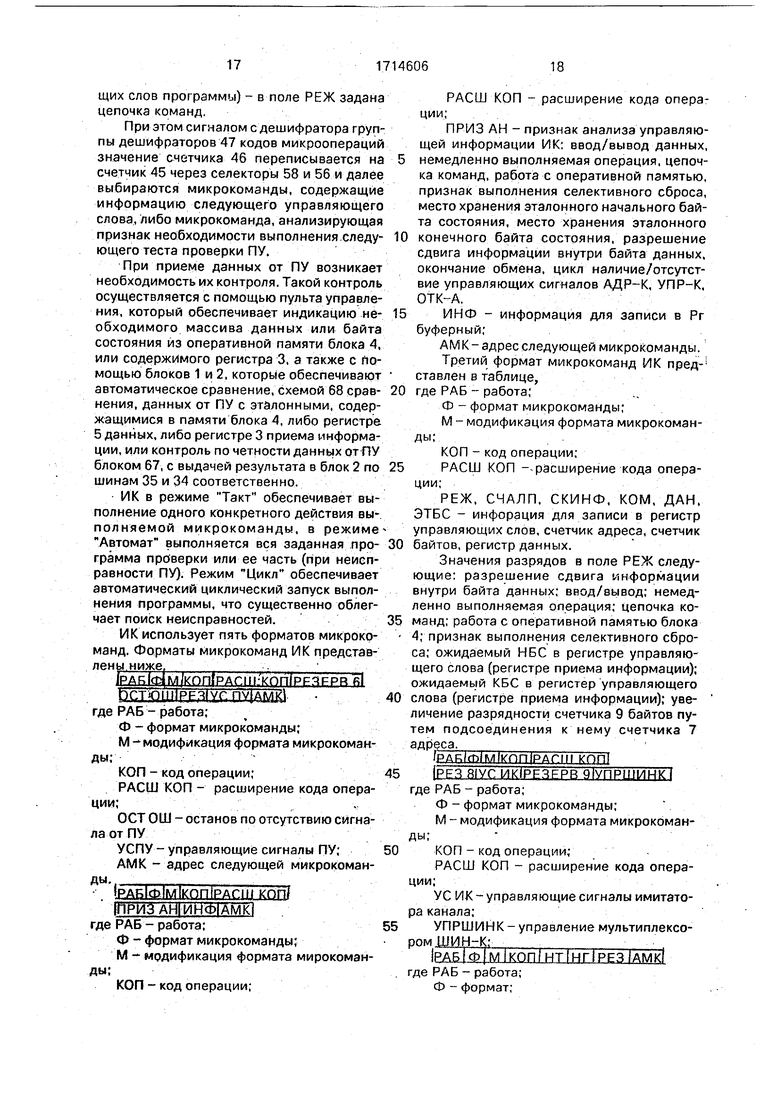

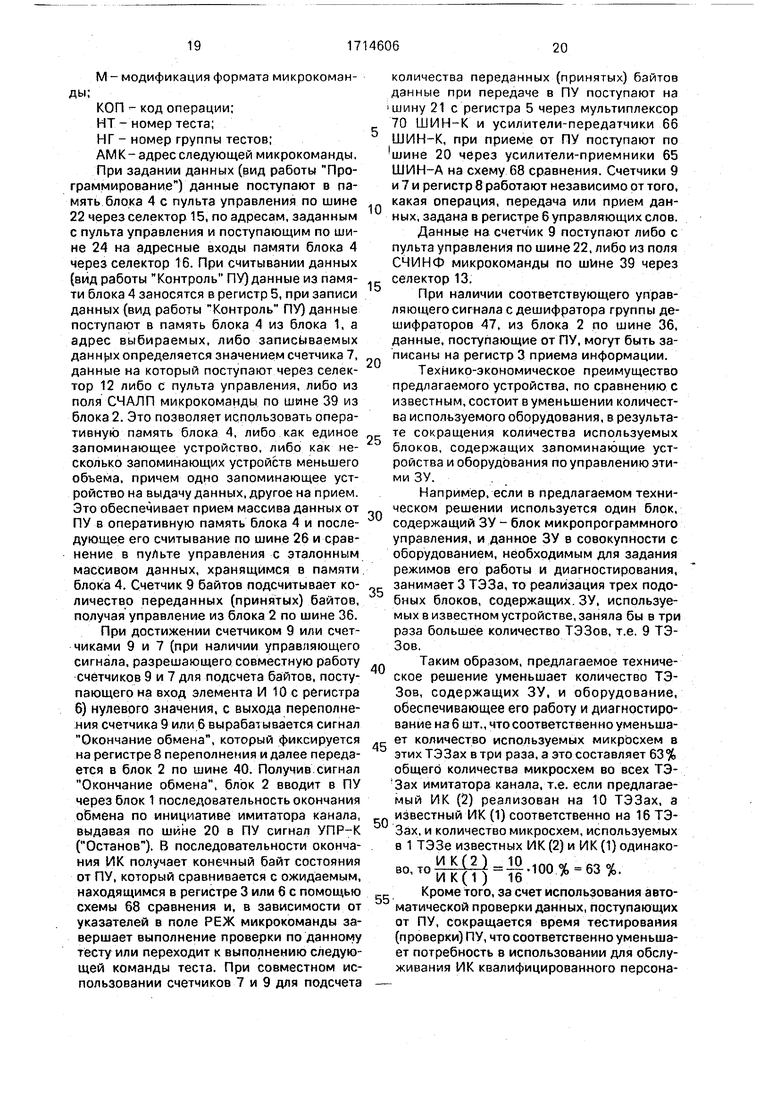

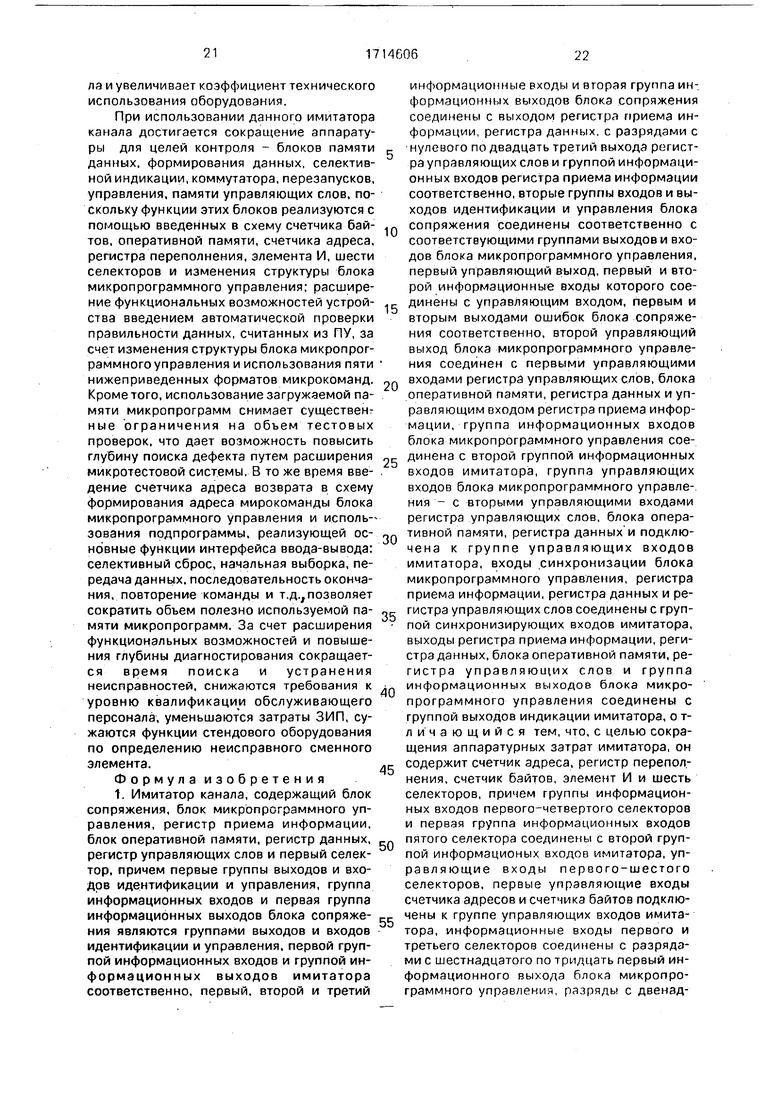

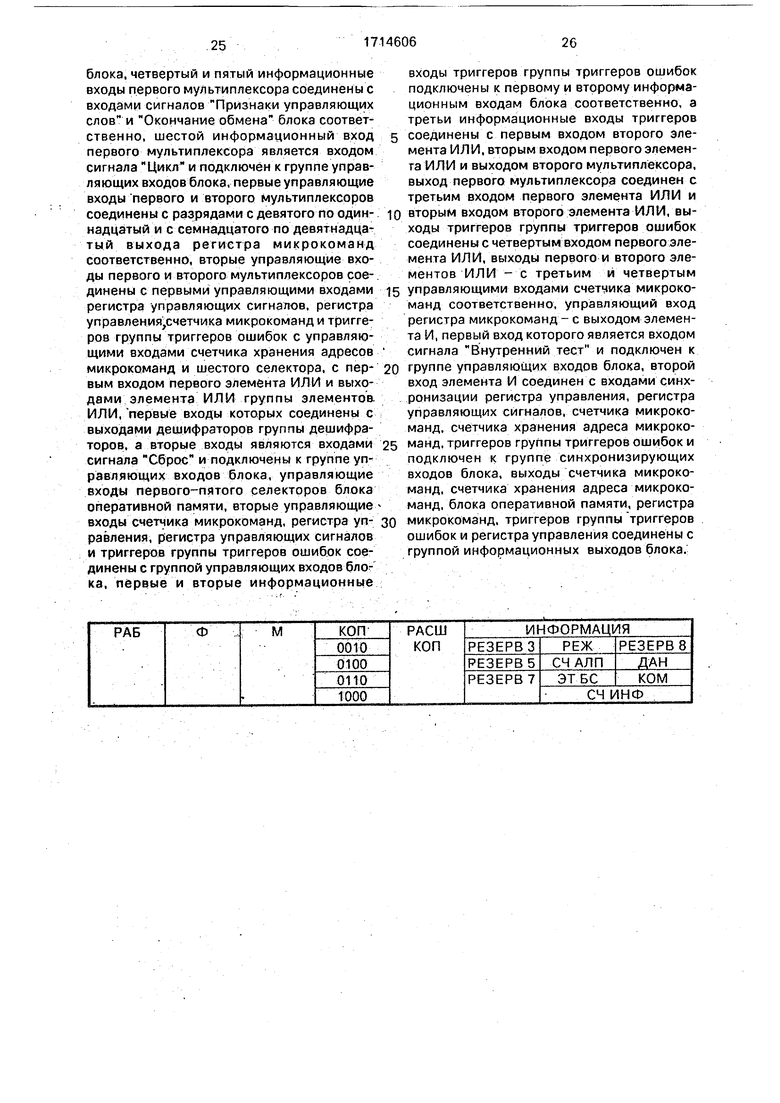

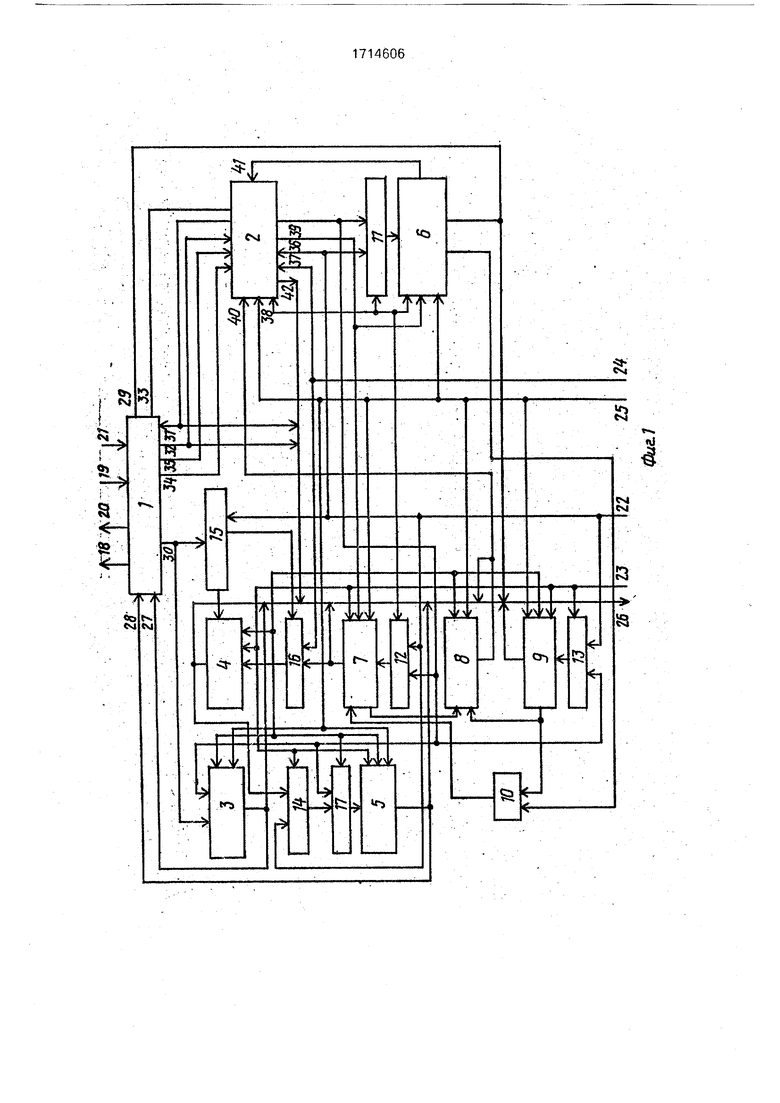

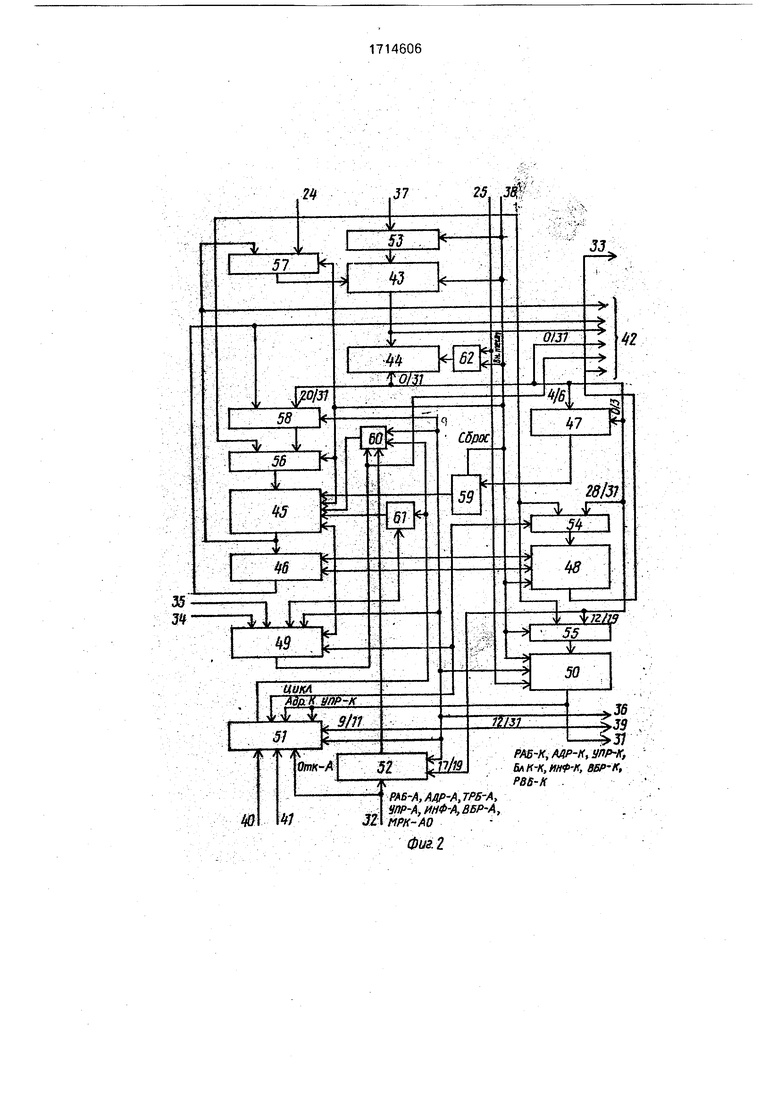

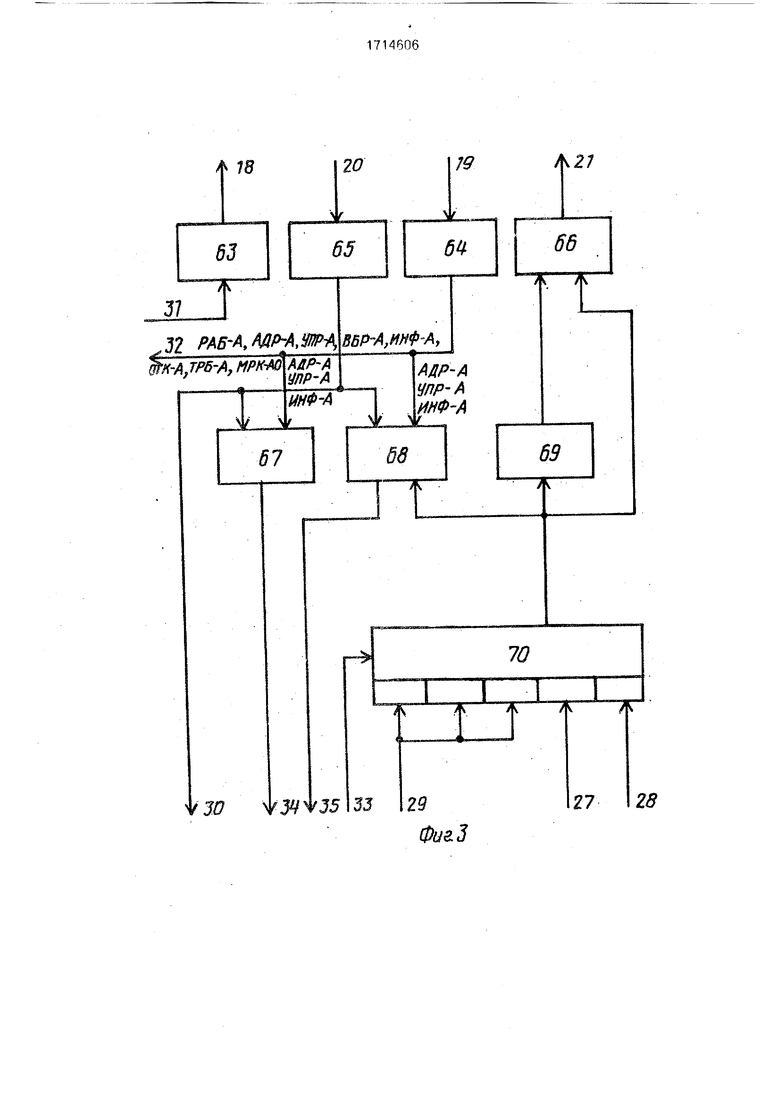

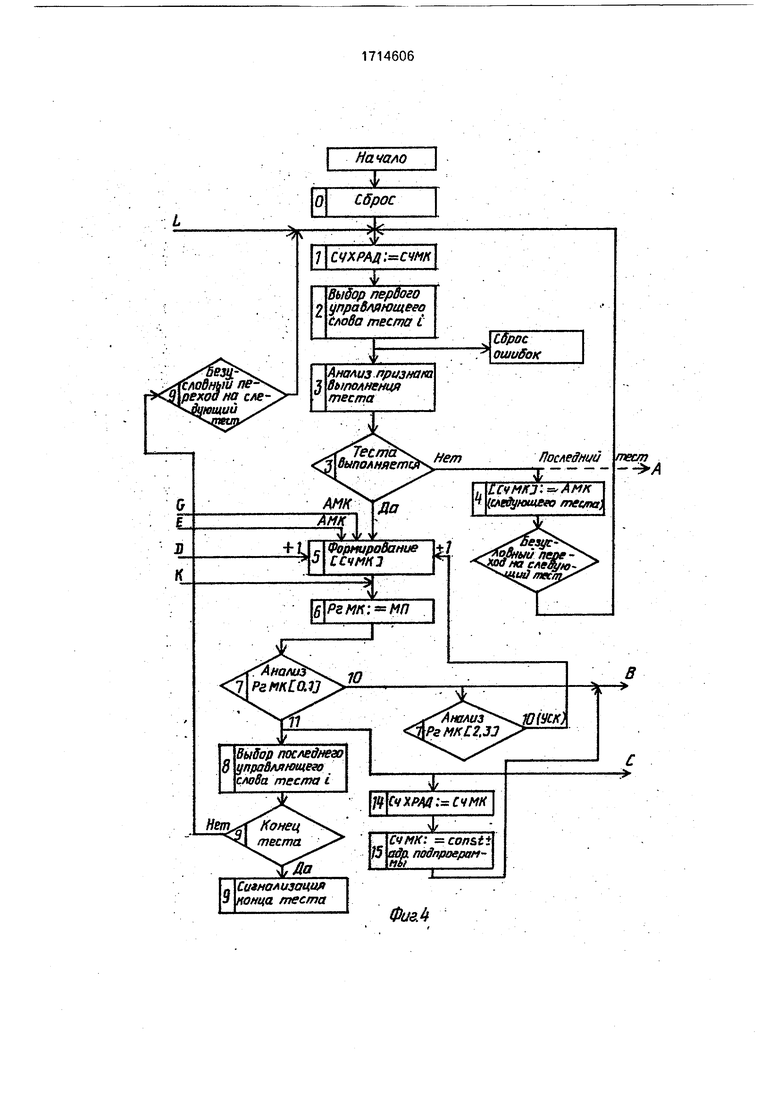

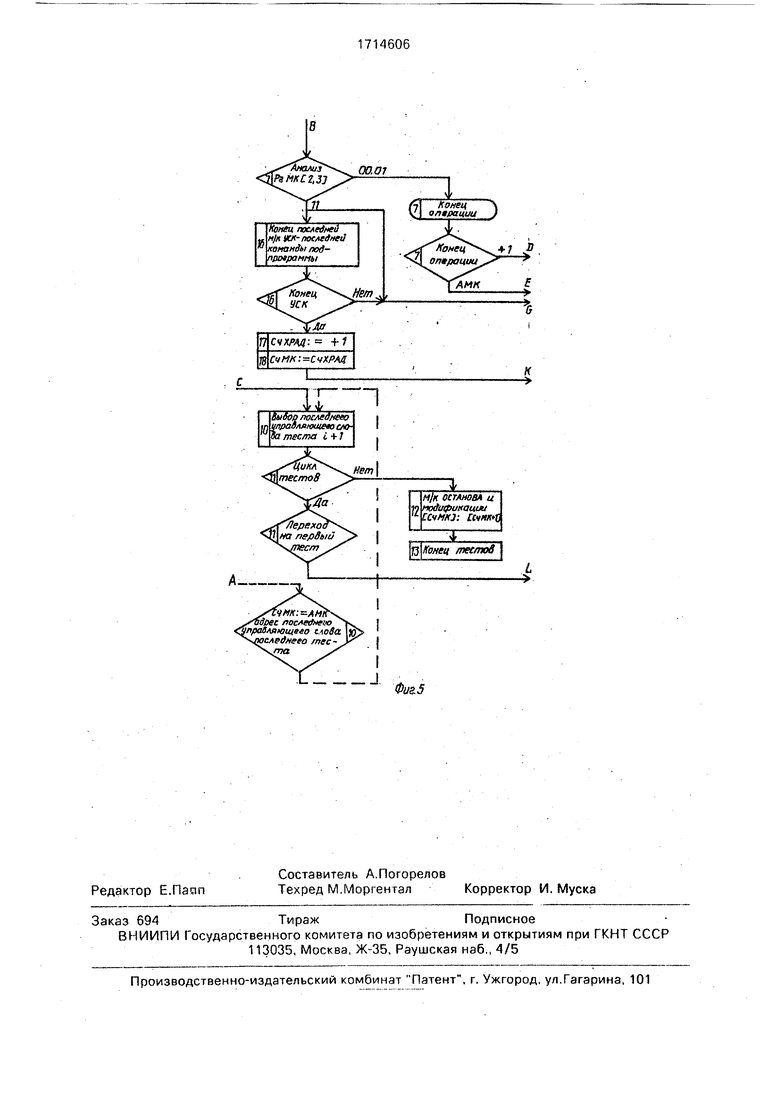

На фиг.1 представлена структурная схема имитатора канала; на фиг.2 - функционаяьная схема блока микропрограммного упрэвлёния; на фиг.З -функциональная схема блока сопряжения; на фиг.4 и 5--алгоритм блока микрр программного упрайления.: Имитатор канала (фиг. 1) содержит блок 1 сопряжения, блок 2 микропрограммного управления, регистр 3 приема информации, блок 4 оперативной памяти, регистр 5 данных, регистр 6 управляющих ел 08, счетчик 7 , регистр 8 переполнения, счетчик 9 байтов, зяемент И 10, семь селекторов 1117, шины 18 и 19 СИГН9ЛО8 идентификации и управления:, шины информационных сигналов, щину 23 управляющих сигналов (в т.ч. сигналов Сброс, Цикл, Внутр.тест), шину 24 адресных сигналов, шину 25 синхронизирующих сигналов и шику 26 сигналов индикации имитатора (посредством шин 18-21 группы выходов и входов идентифи кации и управления, первая группа информационных входов и группа информационных выходов имитатора, являющихся соответственно первыми группами выходов и входов идентификации и управления, группой информационных входов и группой информационных выходов бдОка;сопряжения, подключены к соответствующим входам и выходам контролируемого периферийного устройства, посредством шмн имитатор подключен к пульту управления), информационные входы 2729, вторую группу информационных выходов 30, вторую группу входов 31 идентификации и управления, вторук группу выходов 32 идентификации и управления, управляющий вход 33 и выходы ошибок 34 и 35 блока 1, сопряжения (вход 33 и выходы 34 и 35 соединены с первым управляющим выходом, первым и вторым информационными входами блока 2 соответственно), второй управляющий выход 36, группу информационных входов 37, группу управляющих входов 38. информационный выход 39, вход 40 сигнала Окончание обмена, вход 41 сигнала Признаки управляющих слов и группу информационных выходов 42 блока 2 микропрограммного управления. Блок 2 микропрограммного управления (фиг.2) содержит блок 43 оперативной памяти, регистр 44 микрокоманд, счетчик 45 микрокоманд, счетчик 46 хранения адреса микрокоманд, группу дешифраторов 47, регистр 48управления ШИН-К. группу триггеров 49 ошибок, регистр 50 управляющих сигналов, два мультиплексора 51 и 52, шесть селекторов 53-58, группу элементов ИЛИ В9, два элемента ИЛИ 60 и 61 и элемент И 62. Блок 1 сопряжения (фиг.З) содержит усилители-передатчики 63 и усилители-приемники 64 сигналов идентификации и управления, усилители-приёмники 65 информационных сигналов ШИН-А, усилители-передатчики 66 информационных сигналов ШИН-К, узел 67 контроля чётности, схему 68 сравнения, узел 69 формирования контрольного разряда, мультиплексор 70 ШИМ-К. Блок 1 сопряжения (фиг.З) осуществляет согласование входных и выходных сигналов интерфейса, дополняет коды адресов, команд и данных, передаваемых в ПУ по шинам 21канала (ШИН-К) контрольным разрядом, сравнивает и контролирует на четность байты адресов, состояний И данных, поступающих от ПУ по шинам 20 абонента (ШИН-А). Усилители-передатчики 63 и 66 предназначены для усиления сигналов, передаваемых в ПУ, а усияители-прием.ники 64 и 65 предназначены для усиления сигналов, принимаемых от ПУ. Контроль по четности байтов, принимаемых от ПУ, осуществляется с помощью узла 67. Схема 68 сравнения сравнивает информацию, переданную по ШИН-К, с информацией, принятой по ШИН-А, с выдачей результата в блок 2. С помощью узла 69 формируется контрольный разряд байта, который через усилители-передатчики 66 также передается в ПУ. Через мультиплексор 70 ШИН-К в блок 1 поступает информация либо из регистра 6 (при выдаче или сравнении адреса ПУ, передаче кода операции, сравнении байта состояния ПУ с эталонным), либо из регистра 3, либо из регистра 5 (при передаче или сравнении данных ПУ, сравнении байта состояния ПУ с эталонным). Блок 2 микропрограммного управления (фиг.2) обеспечивает координацию работы всех узлов ИК.с помощью управляющих сигналов, в соответствии с программой, режимами, сигналами от ПУ и алгоритмами работы. Регистр 3 приема информации служит для запоминания байтов адреса, состояния и данных, поступающих по ШИН-А ot ПУ через блок Охранения эталонной информации для последующего сравнения в блоке 1 и выдачи в ПУ по ШИН-К через блок 1 данных, предварительно занесенных в регистр 3 из блока 2. Блок, 4 оперативной памяти служит для хранения, приема из ПУ по через селектор 15 и выдачи в ПУ по ШИН-К через селекторы 14 и 17, регистр 5 данных и блок 1 данных, предварительно занесенных в лок 4 с пульта управления. Адрес выбираеых (записываемых) данных определяется начением счетчика 7 адреса.

Регистр 5 данных служит для хранения текущего значения и формирования переменного кода байта данных для передачи в ПУ,

Регистр 6 управляющих слов служит для хранения текущих значений управляющего слова (кода выполняемой команды, управляющей информации, адреса проверяемого периферийного устройства, эталонного байта состояния, признака необходимости выполнения для каждого теста проверки ПУ).

Счетчик 7 адреса определяет значение адреса оперативной памяти 4.

Регистр 8 переполнения служит для фиксации сигнала окончания счета байтов данных, передаваемых (принимаемых) в (от) ПУ, с выхода переполнения счетчика 9 байтов, либо счетчика 7 адреса (если таковой используется для подсчета количества байтов данных).

Элемент И 10 служит для увеличения разрядности счетчика 9 байтов, посредством подключения счетчика 7 адреса к счетчику 9 байтов в качестве старших разрядов.

Селекторы 11-17 предназначены для селекции данных, постпающих в блок 4, регистры 5 и 6, счетчики 7 и 9 в зависимости от управляющих сигналов, поступающих .по шине 23 от Культа управления.

Посредством шин 18-21 интерфейса имитатор подключается к проверяемому периферийному устройству (ПУ), посредством шин 22-26 - к пульту управления.

Содержимое блоков 1, 2, 4, регистров 3, 5, 6, 8 , счетчиков 7 и 9 по шинам 26 поступает в пульт управления для индикации.

Для пояснения сущности работы имитатора канала приняты следующие обозначения сигналов управления и идентификации: УПР-К- управление от имитатора; АДР-К адрес от имитатора; ИНФ-К - информация от имитатора; РАБ-К - работа имитатора; Б/Ж-К - блокировка; ВВР-К - выборка; РВБ-К - разрешение выборки; УПР-А - управление от ПУ; АД Р-А - адрес от ПУ; ИНФА - информация от ПУ j ВБР-А - обратная выборка; ТРБ-А - требование ПУ; ОТК-А отключение от ПУ; МРК-АО- маркер ГТУ; РАБ-А - работа ПУ; ИНФ - информация (управляющая, адресная, собственно информация).

Блок 2 (фиг.2) реализован в виде ми к ропрограммного автомата, алгоритм которого представлен на фиг.4 и 5. Блок 43 оперативной памяти предназначен для хранения диагностических микропрограмм проверки ПУ. Память программно-адресуемая. Регистр 44 микрокоманд предназначен для приема из блока 43 и хранения до конца

выполнения соответствующей микрокоманды.

Блок 43 предусматривает следующие режимы работы: запись памяти с пульта управления; чтение памяти с пульта управления; чтение регистра 44 микрокоманд с пульта управления; чтение памяти в рабочем режиме.

При загрузке и чтении памяти блока 43

0 с пульта управления адрес поступаете пульта управления по шине 24. Чтение памяти блока 43 в рабочем режиме, при проверке ПУ, выполняется словами (0/31 бит). Адрес памяти (блок 43) в этом случае поступает со

5 счетчика 45 микрокоманд, предназначенного для формирования продвинутого адреса микрокоманды. После выполнения каждой текущей микрокоманды значение счетчика 45 увеличивается на плюс единицу, или на

0 счетчик; 45 записывается значение поля адреса (AMК) из микрокоманды.

С приходом сигналов Прибавление единицы к СЧМК с элементов ИЛИ 59 и 61, Присвоение СЧМК значения адреса микрокоманды из поля АМК микрокоманды с элемента ИЛИ 60, поступающих на управляющие входы счетчика 45 микрокоманд, производится запись выбранной из памяти блока 43 микрокоманды на регистр

0 44 микрокоманд.

Адрес, сформированный на счетчике 45, через селектор 57 адреса поступает на адресный вход памяти блока 43.

Счетчик 46 хранения адреса микрокоманд предназначен для хранения адреса микрокоманд и является счетчиком текущего а,ареса управляющего слова имитатора канала. Данные на счетчик 46 поступают посредством перезаписи адреса со счетчика 45

0 микрокоманд, под управлением микрокоманды. С выхода счетчика хранения адреса адрес поступает на селектор 58 данных.

Группа дешифраторов 47 кодов микроопераций служит для выработки управляющих работой имитатора сигналов в режиме проверки ПУ в зависимости от кода операций в поле КОП микрокоманды. Количество дешифраторов в группе определяется количеством используемых имитатором форма0 тое микрокоманд и равно пяти.

Регистр 48 управления ШИН-К предназначен для управления мультиплексором 70 ШИН-К блока 1.

Группа 49 из трех триггеров ошибок

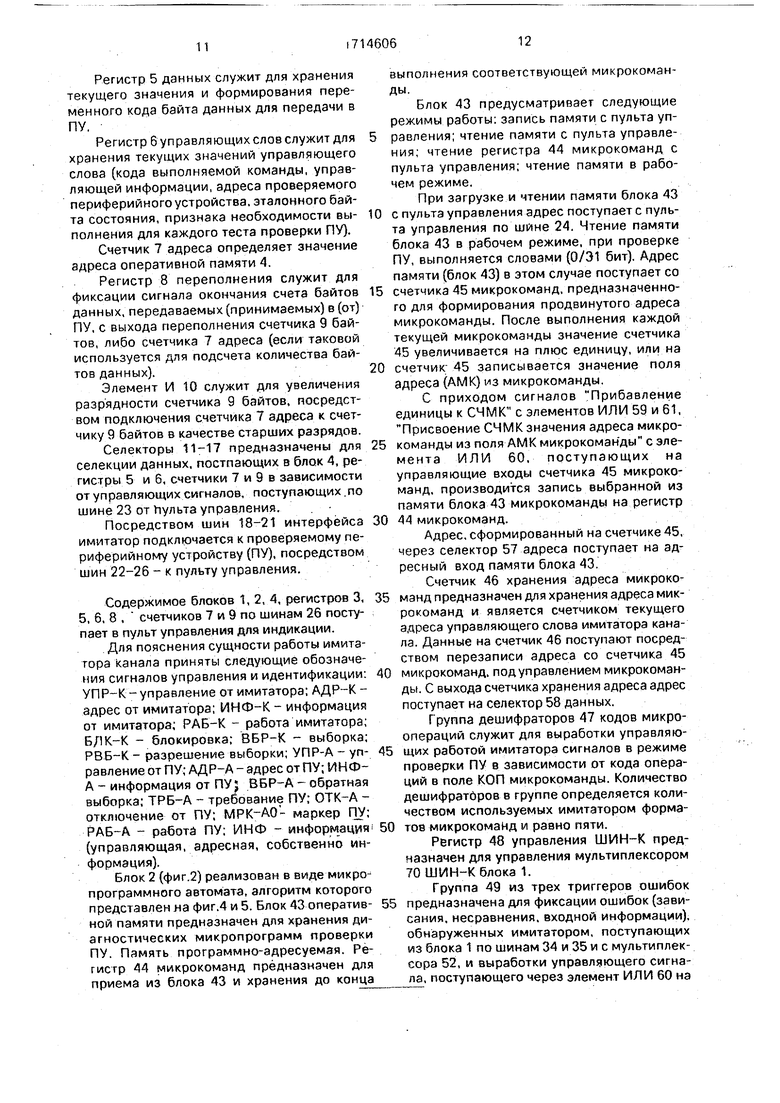

5 предназначена для фиксации ошибок (зависания, несравнения, входной информации), обнаруженных имитатором, поступающих из блока 1 по шинам 34 и 35 и с мультиплексора 52, и выработки управляющего сигнала, поступающего через элемент ИЛИ 60 на управляющие входы счетчика 45 микрокоманд, по которому на счетчик 45 записывается адрес следующей микрокоманды из поля AM К текущей микрокоманды. Регистр 50 управляющих сигналов предназначен для хранения и выдачи управляющих сигналов РАБ-К, АДР-К, УПР-К, БЛК-К, ИНФ-К. ВБР-К, РВБ-К имитатора канала по шине 31 блока 2 через блок 1 вПУ. Мультиплексор 51 предназачен для реализации условных переходов в соответствии со значениями сигналов, управляющих работой программы, поступающих по шине 40 из регистра 8 переполнения, по шине 41 из регистра 6 управляющих слов, по шине 38 с пульта управления, а также сигналов идентификации и управления АДР-К, УПРК, поступающих из регистра 50 управляющих сигнэлов и ОТК-А, поступающего по шине 32 из блока 1. Мультиплексор 52 предназначен для реализации условных переходов в соотвеТ: ствиисо значением управляющего сигиала (РАБ-А. АДР-А, УПР-А. МРК-АО, ИНФ-А, ВБР-А, ТРБ-А) от ПУ по шине 32. Селектор 53 предназначен для селекции данных, поступающих в оперативную память блока 43 с пульта управления. Селекторы 54 и 55 предназначены для, селекции данных, поступающих соответственно на {Регистры 48 и 50 с регистра 44, либо с пульта управления по шине 37. Селекторы 56 и 58 предназначены для селекции данных, поступающих на счетчик 45 с пульта управления, либо с регистра 44, либо со счетчика 46, в зависимости от значения управляющего сигнала с элемента ИЛИ группы элементов ИЛИ 59, поступающего с дешифратора группы дешифраторов 47 и значения управляющего сигнала с пульта управления, поступающего по шине 38, Селектор 57 предназначен для селекции данных, поступающих на адресные входы оперативной памяти блока 43 по шине 24 с пульта управления, либо со счетчика 45, в зависимости от логического уровня (0/1) управляющего сигнала от пульта упраления по шине 38. Рассмотрим работу блока 2 микропрограммного управления по его алгоритму. Алгоритм работы блока 2 - схемно-микропрограммный - представлен на фиг.4 и 5. Для приведения блока имитатора канале в исходное состояние выполняется Сброс, сигнал которого поступает по шине 23 с пульта управления на вход 38 блока 2 микропрограммного управления и через элементы ИЛИ группы элементов ИЛИ 59 на управляющие входы селекторов 58 и 17, регистров 3. 5, 6, 8, 54 и 55, счетчиков 7, 9, 45, 46, триггеров ошибок группы триггеров 49 ошибок. При этом информация поступает на информационные входы регистров и счетчиков с регистра 44 микрокоманд. В исходном состоянии О, на выходе 31 блока 2 присутствует сигнал РАБ-К. При выполнении режима Контроль ПУ, блок 2, . непосредственно после запуска синхросерии (перевод синхросерии в режим Автомат) и поступлении уровня логической 1 сигнала ОН. ТЕСТ с пульта управления, по шинам 25 И.23 соответственно на элемент И 62, переходит в состояние 1, где переписывает значение счетчика 45 на счетчик 46. Из состояния 1 блок 2 переходит в состояние 2, а затем в 3, где анализирует необходимость выполнения теста проверки периферийного устройства. В случае, если тест не вь(полняется (признак разрешения выполнения теста не установлен), то блок 2 через состояние 4 возвращается в состояние 1 и выполняет перечисленные выше действия для теста i+1 и так далее до последнего теста. Если последний тест i+n не выполняется, то на счетчик 45 записывается адрес последнего управляющего слова теста из поля АМК микрокоманды, находящейся на регистре 44 и блок 2 через состояния 10, 11 возвращается в состояние 1(при наличии уровня логической 1 сигнала Цикл с пульта управления), либо переходит в состояние 12, 13, если сигнал .Цикл с пульта управления отсутствует (уровень логического О). В случае, если конкретный тест I, i+1 выполняется, то блок 2 формирует значение счетчика 45 (состояние 5), записывает по сформированному значению счетчика 45 информацию из оперативной памяти блока 43 на регистр 44 микрокоманд и переходит в состояние 7. В состоянии 7 анализируется значение информационных разрядов 0, 1, 2, 3 регистра 44. Если О, 1, 2, 3 - 1010, то информация разрядов 12/31 регистра 44 поступает на выход 39 блока 2 и переписывается на регистры 5 и 6, счетчики 7 и 9 имитатора (выполняется загрузка информации управляющего слова, далее по. тексту УСК, имитатора канала). Далее из оперативной памяти блока 43 на регистр 44 последовательно выбираются микрокоманды со значением О, 1 11, по выполнении которых текущее значение счетчика 45 переписывается на счетчик 46 (адрес возврата) и выполняется запись на счетчик 45 начального адреса подпрограммы, содержащейся в перативной памяти 43 (состояния 14, 15). Подпрограмма обеспечивает выполпение конкретного УСК по интерфейсу ввода-вывода и содержит микрокоманды со значением 0. 1,2,3 1000, 1001, 1011 (см. форматы микрокоманд). После завершения выполнения конкретного УСК блок 2 из состояния 15 переходит в состояние 16, 17, 18, где значение счетчика 46 модифицируется на +1, переписывается на счетчик 45 (осуществляется выход из подпрограммы) и возвращается в состояние 5, после чего выбирается следующее УСК, и т.д. После выполнения последнего УСК данного теста блок 2 через состояние 8 и 9 возвращается в состояние 1 и выполняет действия, описанные выше для теста 1+1 и т.д. Имитатор работает следующим образом.

ИК выполняет два вида работы: Программирование и Контроль ПУ. Вид работы Программирование предназначен для задания программы проверки ПУ и режимов работы ИК. Задание программы заключается в записи в оперативную память блока 43 по шинам 37 через селектор 53 блока 2 микрокоманд, заданных с пульта управления, по адресам, поступающим по шинам 24 через селектор 57 также с пульта управления. При необходимости с пульта управления в оперативную память блока 4 по шинам 22 через селектор 15 заносятся данные, параметры выполняемых команд.

Кроме того, в пульте управления задаются режимы работы имитатора: Такт. Автомат, Пуск, Внутр.тест, Сброс, Цикл и т.п.

После задания программы проверки при необходимости осуществляется ее контроль, а также контроль данных путем считывания микрокоманд и данных на элементы индикации пульта управления по шинам 26 из оперативных памятей блоков 4 и 43. После этого устанавливается вид работы Контроль ПУ, при котором осуществляется проверка ПУ. При этом, при наличии уровня логической 1 сигнала Внутр. тест по шине 38 блока 2 на входе элемента И 62, из памяти блока 43 на регистр 44 микрокоманд выбирается первая микрокоманда, которая анализирует необходимость выполнения первого теста. Адрес микрокоманды определяется значением счетчика 45 микрокоманд, установленного с пульта управления по шине 37 через селектор 56.

В случае, если тест не выполняется, то из памяти блока 43 на регистр 44 микрокоманд выбирается микрокоманда, анализирующая необходимость выполнения второго теста, по адресу,, определяемому .младшими разрядами 20/31 предыдущей микрокоманды и поступающими на счетчик

45 микрокоманд через селекторы 58 и 56 и т.д. В случае, если конкретный тест выполняется, то из памяти блока 43 на регистр 44 последовательно выбираются микрокоманды, содержащие информацию управляющвг го слова имитатора (УСК), которая записывается на регистры 5 и 6, счетчики 7 и 9 имитатора, и на счетчик 46 хранения адреса микрокоманды переписывается зна0 чение счетчика 45 микрокоманд.

Затем блок 2 вводит в ПУ также посредс вом микрокоманд последовательность сигналов начальной выборки, в процессе которой через блок 1 по шине 18 в ПУ поступают байты адреса и кода операции из регистра 6, а от ПУ в блок 1 по шине 21 поступают байты адреса и состояния. Блок 1 сравнивает адрес, поступающий от ПУ, с заданным в управляющем слове и сравнивает начальный байт состояния с помощью схемы 68 срзрчения. Если байт состояния не содержит указателя сбоя, то блок 2 организует обмен данными с ПУ. При приеме данных от ПУ по шине 21 в ИК последние

5 сравниваются с заданными в управляющем слове на регистре 5 данных либо хранящимися в оперативной памяти блока 4, выбираются селекторы 14 и 17 на регистр 5 с помощью схемы 68 сравнения или контролируются на четность при записи данных от ПУ в оперативную память блока 4 через усилители-приемники ШИН-А 65 и селектор 15. Данные от ПУ при необходимости могут быть занесены в регистр 3 и индицировать5 ся в пульте управления. При передаче данных по шинам 18 в ПУ последние поступают из регистра 5 или из оперативной памяти блока 4 через селекторы 14 и 17 и регистр 5. Выбор источника данных определяется

0 значением соответствующих разрядов поля РЕЖ микрокоманды управляющего слова, информация которого находится в регистре 6. Если источником является регистр 5, то в поле РЕЖ имеется также указатель, определяющий тип данных, если источником данных является оперативная память блока 4, то адрес данных определяется полем СЧАЛП микрокоманды управляющего слова, информация которого находится на счетчике 7 адреса.

В последовательности окончания ИК получает конечный байт состояния от ПУ. который сравнивается с ожидаемым, находящимся в регистере 3 или 6 (поле ЭТБС

5 микрокоманды), с помощью схемы 68 сравнения и, в зависимости от указателей в поле РЕЖ, завершает выполнение проверки по данному тесту (в поле РЕЖ отсутствует указатель цепочки команд) или переходит к выполнению следующей команды (управляю щих слов программы) - в поле РЕЖ задана цепочка команд. При этом сигналом с дешифратора группы дешифраторов 47 кодов микроопераций значение счетчика 46 переписывается на счетчик 45 через селекторы 58 и 56 и далее выбираются микрокоманды, содержащие информацию следующего управляющего слова, либо микрокоманда, анализирующая признак необходимости выпол нения .следующего теста проверки ПУ. При приеме данных от ПУ возникает необходимость их контроля. Такой контроль осуществляется с помощью пульта управ тения, который обеспечивает индикацию необходимого массива данных или байта состояния из оперативной памяти блока 4, или содержимого регистра 3. а также с помощью блоков 1 и 2, которые обеспечивают автоматическое сравнение, схемой 68 сравнения, данных от ПУ с эталонными, содержащимися в памяти блока 4, либо регистре 5 данных, либо регистре 3 приема информации, или контроль по четности данных от ПУ блоком 67, с выдачей результата в блок 2 по шинам 35 и 34 соответственно. ИК в режиме Такт обеспечивает выполнение одного конкретного действия выполняемой микрокоманды, в режиме Автомат выполняется вся заданная программа проверки или ее часть (Ири неисправности ПУ). Режим Цикл обеспечивает автоматический циклический запуск выполнения программы, что существенно облегчает поиск неисправностей. ИК использует пять форматов микрокоманд. Форматы микрокоманд И К представлены.ниже, IpA R (d М /КОП|РАС11{:КрП Р Я F РВ ncTJQiJJlpf я|у(: pv| где РАБ - работа: Ф - формат микрокоманды; М- модификация формата микрокомаиды;КОП - код операции, РАСШ КОП - расширение кода операции;ОСТ ОШ - останов по отсутствию сигнала от ПУ УСПУ-управляющие сигналы ПУ; АМК - адрес следующей микрокоман . {ЕАБ1ф м1кпп1РАС1и1оШ {ПРИЗ АН1ИНФ1АШ1 где РАБ - работа; Ф - формат микрокоманды; М - модификация формата мирокоманды;КОП - код операции; РАСШ КОП - расширение кода операции;ПРИЗ АН - признак анализа управляющей информации ИК; ввод/вывод данных, немедленно выполняемая операция, цепочка команд, работа с оперативной памятью, признак выполнения селективного сброса, место хранения эталонного начального байта состояния, место хранения эталонного конечного байта состояния, разрешение сдвига информации внутри байта данных, окончание обмена, цикл наличие/отсутствие управляющих сигналов АДР-К, УПР-К, ОТК-А. ИНФ - информация для записи в Рг буферный; АМК-адрес следующей микрокоманды. Третий формат микрокоманд ИК представлен в таблице, где РАБ - работа; Ф - формат микрокоманды; М - модификация формата микрокоманды;КОП - код операции; РАСШ КОП - расширение кода операции;РЕЖ, СЧАЛП, СКИНФ, КОМ, ДАН, ЭТБС - инфорация для записи в регистр управляющих слов, счетчик адреса, счетчик байтов, регистр данных. Значения разрядов в поле РЕЖ следующие: разрешение сдвига информации внутри байта данных; ввод/вывод; немедленно выполняемая операция; цепочка команд; работа с оперативной памятью блока 4; признак выполнения селективного сброса; ожидаемый НБС в регистре управляющего слова (регистре приема информации); ожидаемый КБС в регистер управляющего слова (регистре приема информации); увеличение разрядности счетчика 9 байтов путем подсоединения к нему счетчика 7 адЬеса. IPABlOlMllCnnlPAr. КПП| {РЕЯ Я1УС ИК1РЕЗЕРВ 91УПРШИЬПП где РАБ - работа; Ф - формат микрокоманды; М - модификация формата микрокоманКОП - код операции;РАСШ КОП - расширение кода операции;УС ИК-управляющие сигналы имитатоа канала; УПРШИНК - управление мультиплексором ДЩНгК. |РАБТФ|М|КОП|НТ НГ|РЕЗ де РАБ - работа; Ф - формат;

М - модификация формата микрокоманды;

КОП - код операции; НТ - номер теста; НГ - номер группы тестов; AM К - адрес следующей микрокоманды, При задании данных (вид работы Программирование) данные поступают в память блока 4 с пульта управления по шине 22 через селектор 15, по адресам, заданным с пульта управления и поступающим по шине 24 на адресные входы памяти блока 4 через селектор 16. При считывании данных (вид работы Контроль ПУ) данные из памяти блока 4 заносятся в регистр 5, при записи данных (вид работы Контроль ПУ) данные поступают в память блока 4 из блока 1, а адрес выбираемых, либо записываемых данных определяется значением счетчика 7, данные на который поступают через селектор 12 либо с пульта управления, либо из поля СЧАЛП микрокоманды по шине 39 из блока 2. Это позволяет использовать оперативнунэ память блока 4, либо как единое запоминающее устройство, либо как несколько запоминающих устройств меньшего объема, причем одно запоминающее устройство на выдачу данных, другое на прием. Это обеспечивает прием массива данных от ПУ в оперативную память блока 4 и последующее его считывание по шине 26 и сравнение в пуЛьте управления с эталонным массивом данных, хранящимся в памяти блока 4. Счетчик 9 байтов подсчитывает количество переданных (принятых) байтов, получая управление из блока 2 по шине 36. При достижении счетчиком 9 или счетчиками 9 и 7 (при наличии управляющего сигнала, разрешающего совместную работу счётчиков 9 и 7 для подсчета байтов, поступающего на вход элемента И 10 с регистра 6) нулевого значения, с выхода переполнения счетчика 9 или 6 вырабатывается сигнал Окончание обмена, который фиксируется на регистре 8 переполнения и далее передается в блок 2 по шине 40. Получив.сигнал Окончание обмена, блок 2 вводит в ПУ через блок 1 последовательность окончания обмена по инициативе имитатора канала, выдавая по шине 20 в ПУ сигнал УПР-К (Останов). В последовательности окончания ИК получает конечный байт состояния от ПУ, который сравнивается с ожидаемым, находящимся в регистре 3 или 6 с помощью схемы 68 сравнения и, в зависимости от указателей в поле РЕЖ микрокоманды завершает выполнение проверки по данному тесту или переходит к выполнению следующей команды теста. При совместном использовании счетчиков 7 и 9 для подсчета

количества переданных (принятых) байтов данные при передаче в ПУ поступают на шину 21 с регистра 5 через мультиплексор 70 ШИН-К и усилители-передатчики 66 ШИН-К, при приеме от ПУ поступают по шине 20 через усилители-приемники 65 ШИН-А на схему 68 сравнения. Счетчики 9 и 7 и регистр 8 работают независимо от того, какая операция, передача или прием данных, задана в регистре 6 управляющих слов.

Данные на счетчик 9 поступают либо с пульта управления по шине 22, либо из поля СЧИНФ микрокоманды по шИне 39 через селектор 13.

При наличии соответствующего управляющего сигнала с дешифратора группы дешифраторов 47, из блока 2 по шине 36, данные, поступающие от ПУ, могут быть записаны на регистр 3 приема информации.

Технико-экономическое преимущество предлагаемого устройства, по сравнению с известным, состоит в уменьшении количества используемого оборудования, в результате сокращения количества используемых блоков, содержащих запоминающие устройства и оборудования по управлению этими ЗУ..

Например, если в предлагаемом техническом решении используется один блок, содержащий ЗУ - блок микропрограммного управления, и данное ЗУ в совокупности с оборудованием, необходимым для задания режимов его работы и диагностирования, занимает 3 ТЭЗа, то реализация трех подобных блоков, содержащих. ЗУ, используемых в известном устройстве, заняла бы в три рэза большее количество ТЭЗов, т.е. 9 ТЭЗов.

Таким образом, предлагаемое техническое решение уменьшает количество ТЭЗов, содержащих ЗУ, и оборудование, обеспечивающее его работу и диагностирование на 6 шт., что соответственно уменьшает количество используемых микросхем в этихТЭЗах в три раза, а это составляет 63% общего количества микросхем во всех ТЭЗах имитатора канала, т.е. если предлагаемый ИК (2) реализован на 10 ТЭЗах, а известный ИК (1) соответственно на 16 ТЭЗах, и количество микросхем, используемых в 1 ТЭЗе известных ИК (2) и ИК (1) одинакоИК(2)10

(Т)

63 %.

Кроме toro, за счет использования автоматической проверки данных. Поступающих от ПУ, сокращается время тестирования (проверки)ПУ, что соответственно уменьшает потребность в использовании для обслуживания ИК квалифицированного персонала и увеличивает коэффициент технического использования оборудования.

При использовании данного имитатора канала достигается сокращение аппаратуры для целей контроля - блоков памяти данных, формирования данных, селективной индикации, коммутатора, перезапусков, управления, памяти управляющих слов, поскольку функции этих блоков реализуются с помощью введенных в схему счетчика байтов, оперативной памяти, счетчика адреса, регистра переполнения, элемента И, шести селекторов и изменения структуры блока микропрограммного управления: расширение функциональных возможностей устройства введением автоматической проверки правильности данных, считанных из ПУ, за счет изменения структуры блока микропрограммного управления и использования пяти нижеприведенных форматов микрокоманд. Кроме того, использование загружаемой памяти микропрограмм снимает существен ные ограничения на объем тестовых проверок, что дает возможность повысить глубину поиска дефекта путем расширения микротестовой системы. В то же время введение счетчика адреса возврата в схему формирования адреса мирокоманды блока микропрограммного управления и исполь-зования подпрограммы, реализующей основные функции интерфейса ввода-вывода: селективный сброс, начальная выборка, передача данных, последовательность окончания, повторение команды и т.д., позволяет сократить объем полезно используемой памяти микропрограмм. За счет расширения функциональных возможностей и повышения глубины диагностирования сокращается время поиска и устранения неисправностей, снижаются требования к уровню квалификации обслуживающего персонала, уменьшаются затраты ЗИП. сужаются функции стендового оборудования по определению неисправного сменного элемента.

Формула изобретения 1. Имитатор канала, содержащий блок сопряжения, блок микропрограммного управления, регистр приема информации, блок оперативной памяти, регистр данных, регистр управляющих слов и первый селектор, причем первые группы выходов и входов идентификации и управления, группа информационных входов и первая группа информационных выходов блока сопряжения являются группами выходов и входов идентификации и управления, первой группой информационных входов и группой информационных выходов имитатора соответственно, первый, второй и третий

информационные входы и вторая группа информационных выходов блока сопряжения соединены с выходом регистра приема информации, регистра данных, с разрядами с нулевого по двадцать третий выхода регистра управляющих слов и группой информационных входов регистра приема информации соответственно, вторые группы входов и выходов идентификации и управления блока сопряжения соединены соответственно с соответствующими группами выходов и входов блока микропрограммного управления, первый управляющий выход, первый и второй информационные входы которого соединены с управляющим входом, первым и вторым выходами ошибок блока сопряжения соответственно, второй управляющий выход блока микропрограммного управления соединен с первыми управляющими входами регистра управляющих слов, блока оперативной памяти, регистра данных и управляющим входом регистра приема информации, группа информационных входов блока микропрограммного управления соединена с второй группой информационных входов имитатора, группа управляющих входов блока микропрограммного управле-. ния - с вторыми управляющими входами регистра управляющих слов, блока оперативной памяти, регистра данных и подключена к группе управляющих входов имитатора, входы синхронизации блока микропрограммного управления, регистра приема информации, регистра данных и регистра управляющих слов соединены с группой синхронизирующих входов имитатора, выходы регистра приема информации, регистра данных, блока оперативной памяти, регистра управляюи их слов и группа информационных выходов блока микропрограммного управления соединены с группой выходов индикации имитатора, о тличающийся тем, что. с целью сокращения аппаратурных затрат имитатора, он содержит счетчик адреса, регистр переполнения, счетчик байтов, элемент И и шесть селекторов, причем группы информационных входов первого-четвертого селекторов и первая группа информационных входов пятого селектора соединены с второй группой информационых входов имитатора, управляющие входы первого-шестого селекторов, первые управляющие входы счетчика адресов и счетчика байтов подключены к группе управляющих входов имитатора, информационные входы первого и третьего селекторов соединены с разрядами с шестнадцатого по тридцать первый информационного выхода блока микропрограммного управления, разряды с двеиадцатого по девятнадцатый, с четырнадцатого по двадцать третий, с двадцать четвертого по тридцать первый информационного выхода которого соединены с информационными входами регистра приема информации, второго селектора и с первым информационным входом седьмого селектора соответственно, вторая группа информационных входов и выход пятого селектора соединены с второй группой информационых выходов блока сопряжения и информационным входом блока оперативной памяти соответственно, выход блока оперативной памяти соединен с информационным входом четвертого селектора, выход которого соединен с вторым информационным входом седьмого селектора, выход седьмого селектора - с информационным входом регистра данных, адресный вход блока микропрограммного управления и первый информационный вход шестого селектора соединены с адресным входом имитатора, второй информационный вход и выход шестого селектора - с информационным входом счетчика адреса и адресным входом блока оперативной памяти соответственно, управляющий вход регистра переполнения - с вторы.ми управляющими входами счетчика адресов и счетчика байтов и подключен к второму управляющему выходу блока микропрограммного управления, первый и второй информационные входы регистра переполнения соединены с выходами переполнения счетчика адреса и счетчика байтов, информационный вход и третий управляющий вход счетчика адреса соединены с выходами второго селектора и элемента И соответственно, выход регистра переполнения соединен с входом Окончание обмена блока микропрограммного управления, информационный вход счетчика байтов соединен с выходом третьего селектора, а выход перегиэлнения подключен к первому входу элемента И. разряды с двадцать четвертого по тридцать первый и тридцать второй разряд выхода регистра управляющих слов соединены с входом сигнала Признаки управляющх слов блока микропрограммного управления и вторым входом элемента ИЛИ соответственно, входы синхронизации счетчика адресов, регистра переполнения и счетчика байтов соединены с группой синхронизирующих входов имитатора, информационные выходы счетчика адреса, счетчика байтов, выход регистра переполнения подключены к группе выходов индикации имитатора,

2. Имитатор по п. 1, о т л и ч а ю щи и с я тем, что блок микропрограммного управления содержит блок оперативной памяти, регистр микрокоманд, счетчик микрокоманд, счетчик хранения адреса микрокоманд, группу из пяти дешифраторов, регистр управления, группу из трех триггеров ошибок, регистр управляющих сигналов, два мультиплексора, шесть селекторов, группу элементов ИЛИ, два элемента ИЛИ и элемент И, причем группа информационных входов первого-четвертого селекторов соединены с группой информационных входов блока, информационный вход, адресный вход и выход блока оперативной памяти соединены с выходами первого и пятого селекторов и информационным входом регистра микрокоманд соответственно, разряды с нулевого по третий и с четвертого по шестой выхода регистра микрокоманд соединены с управляющими и информационными входами дешифраторов группы дешифраторов соответственно, разряды с двадать восьмого по тридцать первый, с двенадцатого по девятнадцатый, с двадцатого по тридцать первый выхода регистра микрокоманд соединены с информационными входами второго и третьего селекторов и с первым информационным входом шестого селектора соответственно, разряды с девятого по одиннадцатый и с семнадцатого по девятнадцатый соединены с первыми управляющими входами первого и второго мультиплексоров соответственно, разряды с двенадцатого по тридцать первый выхода регистра микрокоманд - с информационным выходом блока, информационный вход и выход четвертого селектора - с выходом шестого селектора и информационным входом счетчика микрокоманд соответственно, выход счетчика микрокоманд - с информационным входом счетчика хранения адреса микрокоманд и первым информационным входом пятого селектора, второй информационный вход которого подключен к адресному входу блока, выход счетчика хранения адреса микрокоманд соединен с вторым информационным входом шестого селектора, выход второго селектора - с информационным входом регистра управления, выход которого соединен с первым управляющим выходом блока, выход третьего селектора с информационным входом регистра управляющих сигналов, группа выходов которого соединена с первым и вторым информационными входами первого мультиплексора и подключена к группе выходов идентификации и управления блока, третий информационный вход первого мультиплексора соединен с группой информационных входов второго мультиплексора и подключен к . группе входов идентификации и управления

блока, четвертый и пятый информационные входы первого мультиплексора соединены с входами сигналов Признаки управляющих слов и Окончание обмена блока соответственно, шестой информационный вход первого мультиплексора является входом сигнала Цикл и подключён к группе управляющих входов блока, первые управляющие входыпервого и второго мультиплексоров соединены с разрядами с девятого по одиннадцатый и с семнадцатого по девятнадцатый выхода регистра микрокоманд соответственно, вторые управляющие входы первого и второго мультиплексоров соединены с первыми управляющими входами регистра управляющих сигналов, регистра управления счетчика микрокоманд и триггеров группы триггеров ошибок с управляющими входами счетчика хранения адресов микрокоманд и шестого селектора, с первым входом первого элемента ИЛИ и выходами элемента ИЛИ группы элементоа ИЛИ, первые входы которых соединены с выходами дешифраторов группы дешифраторов, а вторые входы являются входами сигнала Сброс и подключены к группе управляющих входов блока, управляющие входы первого-пятого селекторов блока оперативной памяти, вторые управляющие входы счетчика микрокоманд, регистра управления, регистра управляющих сигналов и триггеров группы триггеров ошибок соединены с группой управляющих входов блог ка, первые и вторые информационные

входы триггеров группы триггеров ошибок подключены к первому и второму информационным входам блока соответственно, а третьи информационные входы триггеров 5 соединены с первым входом второго элемента ИЛИ, вторым входом первого элемента ИЛИ и выходом второго мультиплексора, выход первого мультиплексора соединен с третьим входом первого элемента ИЛИ и 10 вторым входом второго элемента ИЛИ, выходы триггеров группы триггеров ошибок соединены с четвертым входом первого элемента ИЛИ, выходы первого и второго элементов ИЛИ -с третьим и четвертым

5 управляющими входами счетчика микрокоманд соответственно, управляю щий вход регистра микрокоманд - с выходом элемента И, первый вход которого является входом

сигнала Внутренний тест и подключен к

0 группе управляющих входов блока, второй вход элемента И соединен с входами синхронизации регистра управления, регистра

управляющих сигналов, счетчика микрокоманд, счетчика хранения адреса микрокоманд, триггеров группы триггеров ошибок и подключен к группе синхронизирующих входов блока, выходы счетчика микрокоманд, счетчика хранения адреса микрокоманд, блока оперативной памяти, регистра

0 микрокоманд, триггеров группы триггеров ошибок и регистра управления соединены с группой информационных выходов блока.;

35 J

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Имитатор канала | 1984 |

|

SU1239719A2 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Имитатор канала | 1987 |

|

SU1467555A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и наладки периферийных устройств (ПУ). Цель изобретения - сокращение аппаратурных затрат имитатора.Поставленная цель достигается тем, что в имитаторе канала, содержащем блок сопряжения, блок микропрограммного управления, регистр приема информации, блок оперативной памяти, регистр данных, регистр управляющих слов и первый селектор, введены счетчик адреса, регистр переполнения, счетчик байтов, элемент И, шесть селекторов, а также изменена структура блока микропрограммного управления (вве- даны загружаемая память микропрограмм и элементы, обеспечивающие возможность организации диагностических микропрограмм). Кроме этого, техническое решение позволяет также обеспечивать как ручную, так и автоматическую проверку правильности данных, считанных из ПУ. 1 з.п. ф-лы, 5 ид, 1 табл.(Л

Фиг. 2

IB

65

63

7

J2 PABA.,m

MP-A

K-A,TP6-/ j MPK-AO УПРА

ИНФ-А

67

5J

A2;

J9

66

6Ц/ 1

,И}1ФА,

АЛР-А

УЛР-А ИНФ-А

V L

69

68

70

I 1

r

1 v

27 28

29 ФигЗ

Начало

Сброс J Сорос ошибок Последний Фиг. тест

Рзмксг.зз

Конец послед/ли ф ЖК-поемЛне 1 команды по пртрамны

Выбоо последцеео цправлаюаквосмда /песта i + 7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Техническое описание | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-02-23—Публикация

1990-05-14—Подача