Изобретение относится к электроизмерительной технике и может быть использовано при разработке осцил- лографической аппаратуры.

Целью изобретения является улучшение метрологических характеристик осциллографа и повьппение оперативности измерений.

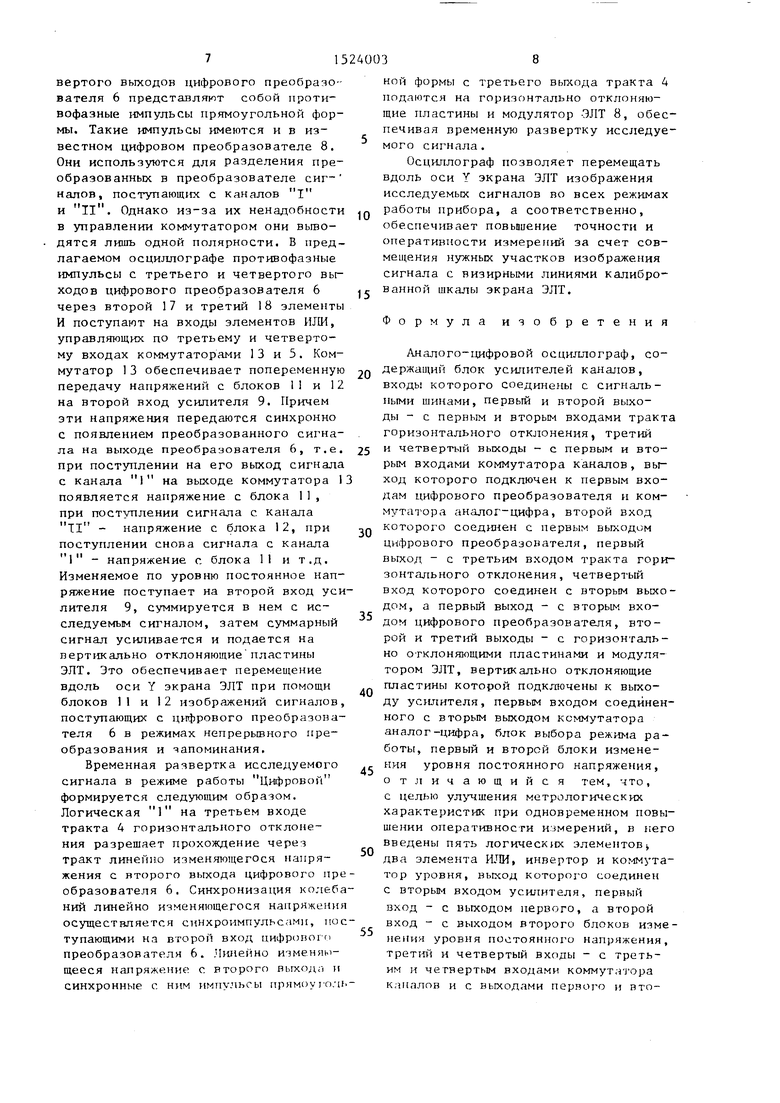

На чертеже изображена структурная схема аналого-цифрового осциллографа

Осциплограф содержит блок 1 усилителей-каналов I и II, сигнальные шины 2 и 3, тракт 4 горизонтального отклонения, коммутатор 5 каналов, цифровой преобразователь 6, коммутатор 7 аналог-цифра, электронно-лучевую трубку 8 (ЭЛТ), усилитель 9, блок 10 выбора режима работы, первый 11 и второй 12 блоки изменения уровн постоянного напряжения, коммутатор 13 уровня, первый 14 и второй 15 логические элементы ИЛИ, первый - пяты логические элементы И 16 - 20 и инвертор 21 ,

Входы блока 1 усилителей каналов I и II соединены с сигнальными шинами 2 и 3, первый и второй выхо- ды - с первым и вторым входами тракта 4 горизонтального отклонения, третий и четвертый выходы - с первым и вторым входами коммутатора 5 каналов, выход которого подключен к первым входам цифрового преобразователя 6 и коммутатора 7 аналог-цифра, второй вход которого соединен с первым выходом 1У1ФРОВОГО преобразователя 6, первый выход - с третьим входо тракта 4 горизонтального отклонения, четвертый вход которого соединен с вторым выходом, а первый выход - с вторым входом цифрового преобразователя 6, второй и третий вькоды - с горизонтально отклоняющими пластинами и модулятором ЭЛТ 8, вертикально отклоняющие пластины которой подключены к выходу усилителя 9, первым входом соединенного с вторым выходом коммутатора 7 аналог-цифра, блок 10 выбора режима работы, первый 11, второй 12 блоки изменения уровня постоя ного напряжения, коммутатор 13 уровн выход которого соединен с вторым входом усилителя 9, первый вход - с выходом первого 11, второй вход - с выходом второго 12 блоков изменения уровня постоянного напряжения, трети и четверты входы - с третьим и четвертым входами KONfMyTaTopa 5 каналон

5

0

5

0

5

и с выходами первого 14 и второго 15 элементов ИЛИ, первые входы которых подключены к выходам первого 16 и второго 17 элементов И, вторые входы - к выходам третьего 18 и четвертого 19 элементов И, первые входы второго 17 и третьего 18 элементов И соединены соответственно с третьим и четвертым выходами цифрового преобразователя 6, вторые входы этих элементов - между собой и с выходом пятого элемента И 20 и входом инвертора 21, выход которого подключен к первым входам первого 16 и четвертого 19 элементов И, второй вход первого элемента И 16 соединен с первым выходом, а второй вход четвертого элемента И 19 - с вторым выходом блока 10 выбора режима работы, третий выход которого подключен к первому входу пятого элемента И 20, вторым входом соединенного с первым выходом коммутатора 7 аналог-цифра.

Осциллограф работает следующим образом,

Исследуемые сигналы, поступая на входы блока 1 усилителей каналов т и II, усиливаются или ослабляются в них и передаются на первый и второй входы коммутатора 5 каналов. Последний работает в одном из режимов: I, II, I+II и Прерьшис- то. Режим работы коммутатора 5 каналов устанавливается при помощи блока 10 выбора режима работы, переключатель которого выведен на лицевую панель осциллографа, В режимах и II на вьЕходе коммутатора 5

0

5

0

5

II J П

каналов имеется один исследуемый сигнал, соответствующий каналу I или 11, а в режиме алгебраического сложения I tIT - сумма или разность сигналов с обоих каналов. Б режиме Прерьшисто имеются сигналы с обоих каналов. Каналы переключаются импульсами в течение прямого хода развертки. С выхода коммутатора 5 каналов сигнал поступает на первые входы цифрового преобразователя 6 и коммутатора 7 аналог-цифра. Коммутатор 7 обеспечивает режимы работы осциллографа: Аналоговый и Цифровой.

В режиме работы Аналоговый на второй выход коммутатора 7 аналог-цифра и первый вход усилителя 9 поступает исследуемый сигнал с коммутатора 5 каналов. Коммутатор 7 устанавливает низкт уровень напряжения (логический О) на втором входе элемента И 20, который поддерживает О на вторьк входах второго 17 и третьего 1 8 элементов И, и через инвертор 21 - 1 на первых входах первого 16 и четвертого 19 элементов И, последние разрешают прохождение команд управления с блока 10 выбора режима работы, а второй 17 и третий 18 элементы И запрещают прохождение команд управления с цифрового преобразователя 6 через первый 14 и второй 15 элементы ИЛИ на входы коммутаторов 13

10

пакхдими на первый и второй входы та 4 горизонтального отклонения.

В режиме работы Цифровой на рой выход коммутатора 7 аналог-ци и первый вход усилителя 9 поступа сигнал с цифрового преобразовател 6. Последний предназначен для пре зования аналогового сигнала в код его запоминания и обратного преоб разования кода в аналоговый сигна Преобразователь 6 выполняет непре ное преобразование исследуемого сигнала в код и непрерьшное обрат

5. Коммутатор 13 работает синхрон-15 преобразование кода в аналоговый

и

но с коммутатором 5 каналов, т.е. в одном из режимов I, II, I±II и Прерьшисто. Синхронность работы коммутаторов состоит в том, что при включении блоком 10 режима I или 11 или коммутатор 13 уровня подает на второй вход усилителя изменяемое по уровню постоянное напряжение с первого 11 или второго 12 иди обоих блоков. В режиме Прерывисто в такт с включением каналов I и II на второй вход усилителя 9 попеременно поступают напряжения с блоков 11 и I2.

Изменяемое по уровню постоянное напряжение, поступающее на второй вход усилителя 9, суммируется в нем с исследуемым сигналом и подается на вертикально отклоняющие пластины ЭЛТ В. Синхронность работы коммутаторов каналов 5 и уровня 13 обеспечивает в режимах I и II и Прерьшисто перемещение при помощи блока 1 1 изображения сигнала с канала I, а при помощи блока 12 - с канала II. В режиме It II на перемещение изображения суммарного сигнала воздействуют оба блока 11 и 12.

Временная развертка сигналов в режиме работы Аналоговый формируется трактом 4 горизонтального отклонения, Линейно изменяющееся напряжение с второго выхода тракта 4 подается на горизонтально отклоняющие пластины ЭЛТ 8 и обеспечивает временную развертку сигнала. Синхронные с этим напряжением прямоугольные импульсы с третьего выхода тракта 4 . поступают на модулятор ЭЛТ 8 и отпирают ее на время прямого входа развертки. Синхронизация колебаний развертывающего напряжения осуществляется исследуемыми сигналами, посту20

25

30

35

40

45

50

55

сигнал с последующим выводом прео разованного сигнала на первый вых преобразователя при наличии на ег ром входе сигнала синхронизации, прерьшное преобразование исследуе сигнала в код, фиксирование (запо нание) кода при отсутствии сигнал синхронизации на втором входе пре образователя, обратное преобразов ние запомненного кода в аналоговы сигнал и вывод его на первый выход. В режимах работы коммутатора каналов I, II и lill блок 10 выбора режима работы устанавли ет на первом входе элемента И 20 гический О, который через инвер 21 обеспечивает 1 на первых вх дах первого 1б и четвертого 19 эл ментов И, разрешая прохождение си налов управления с выходов блока на коммутаторы 3 и 5, которые ра тают синхронно как в режиме Анал вый. Синхронность работы коммута торов позволяет перемещать вдоль оси Y экрана ЭЛТ 8 изображение си ла непрерьшного преобразования ил запомненного, поступающего с цифр го преобразователя 6 через коммут 7 и усилитель 9.

В режиме Прерьшисто на перво входе элемента И 20 устанавливает 1 (на втором входе элемента подд живается 1), которая обеспечива О на первых входах первого 16 и четвертого 19 элементов И и 1 на вторых входах второго 17 и третьег 18 элементов И. Первый 16 и четвер тьй 19 элементы И запрещают прохож дение сигналов управления с блока 10 выбора режима, а второй 17 и тр тий 18 элементы И запрещают прохож ние сигналов управления с цифровог преобразователя 6. Сигналы управле ния, поступающие с третьего и чет

пакхдими на первый и второй входы тракта 4 горизонтального отклонения.

В режиме работы Цифровой на второй выход коммутатора 7 аналог-цифра и первый вход усилителя 9 поступает сигнал с цифрового преобразователя 6. Последний предназначен для преобразования аналогового сигнала в код, его запоминания и обратного преобразования кода в аналоговый сигнал. Преобразователь 6 выполняет непрерьш- ное преобразование исследуемого сигнала в код и непрерьшное обратное

5 преобразование кода в аналоговый

0

5

0

5

0

5

0

5

сигнал с последующим выводом преобразованного сигнала на первый выход преобразователя при наличии на его втором входе сигнала синхронизации, непрерьшное преобразование исследуемого сигнала в код, фиксирование (запоминание) кода при отсутствии сигнала синхронизации на втором входе преобразователя, обратное преобразовя ние запомненного кода в аналоговый сигнал и вывод его на первый выход. В режимах работы коммутатора 5 каналов I, II и lill блок 10 выбора режима работы устанавливает на первом входе элемента И 20 ло гический О, который через инвертор 21 обеспечивает 1 на первых входах первого 1б и четвертого 19 элементов И, разрешая прохождение сигналов управления с выходов блока 10 на коммутаторы 3 и 5, которые работают синхронно как в режиме Аналоговый. Синхронность работы коммутаторов позволяет перемещать вдоль оси Y экрана ЭЛТ 8 изображение сигнала непрерьшного преобразования или запомненного, поступающего с цифрового преобразователя 6 через коммутатор 7 и усилитель 9.

В режиме Прерьшисто на первом входе элемента И 20 устанавливается 1 (на втором входе элемента поддерживается 1), которая обеспечивает О на первых входах первого 16 и четвертого 19 элементов И и 1 на вторых входах второго 17 и третьего 18 элементов И. Первый 16 и четверг тьй 19 элементы И запрещают прохождение сигналов управления с блока 10 выбора режима, а второй 17 и третий 18 элементы И запрещают прохождение сигналов управления с цифрового преобразователя 6. Сигналы управления, поступающие с третьего и четвертого выходов цифрового преобразователя 6 представляют собой противофазные импульсы прямоугольной формы. Такие импульсы имеются и в известном цифровом преобразователе 8. Они используются для разделения преобразованных в преобразователе сиг- налов, поступающих с каналов I и II. Однако из-за их ненадобности в управлении коммутатором они вьшо- дятся лишь одной полярности, в предлагаемом осциллографе противофазные импульсы с третьего и четвертого выходов цифрового преобразователя 6 через второй 17 и третий 18 элементы И поступают на входы элементов ИЛИ, управляющих по третьему и четвертому входах коммутаторами 13 и 5. Коммутатор 13 обеспечивает попеременную передачу напряжений с блоков 1 и 12 на второй вход усилителя 9. Причем эти напряжения передаются синхронно с появлением преобразованного сигнала на выходе преобразователя 6, т.е. при поступлении на его выход сигнала с канала 1 на выходе коммутатора 1 появляется напряжение с блока 11 , при поступлении сигнала с канала Т1 - напряжение с блока 12, при поступлении снова сигнала с канала 1 - напряжение с блока 11 и т.д. Изменяемое по уровню постоянное напряжение поступает на второй вход усилителя 9, суммируется в нем с исследуемым сигналом, затем суммарный сигнал усиливается и подается на вертикально отклоняющие пластины ЭЛТ. Это обеспечивает перемещение вдоль оси Y экрана ЭЛТ при помощи блоков 11 и 12 изображений сигналов, поступающих с цифрового преобразователя 6 в режимах непрерьтного преобразования и запоминания.

Временная развертка исследуемого сигнала в режиме работы Цифровой формируется следующим образом. Логическая 1 на третьем входе тракта 4 горизонтального отклонения разрешает прохождение через тракт линейно изменяющегося напряжения с второго выхода цифрового преобразователя 6. Синхронизация колебаний линейно изменяющегося напряжения осуществляется ст1нхроимпульсамп, поступающими на второй вход пифровогч преобразователя 6. Линейно итменяы- щееся напряжение с второго выхода и синхронные с ним импульсы прямоу го.чь

5

0

5

0

5

0

5

0

5

ной формы с третьего тракта 4 подаются на горизонтально отклоняющие пластины и модулятор -ЭЛТ 8, обеспечивая временную развертку исследуемого сигнала.

Осциллограф позволяет перемещать вдоль оси Y экрана ЭЛТ изображения исследуемых сигналов во всех режимах работы прибора, а соответственно, обеспечивает повьпиение точности и оперативности измерений за счет совмещения нужных участков изображения сигнала с визирными линиями калиброванной шкалы экрана ЭЛТ.

Формула изобретения

Аналого-цифровой осциллограф, содержащий блок усилителей каналов, входы которого соединены с сигнальными шинами, первый и второй выходы - с первым и вторым входами тракта горизонтального отклонения, третий и четвертый выходы - с первым и вторым входами коммутатора каналов, выход которого подключен к первым входам цифрового преобразователя и ком- мутап ора аналог-цифра, второй вход которого соединен с первым выходом цифрового преобразователя, первый выход - с третьим входом тракта горизонтального отклонения, четвертый вход которого соединен с вторым Bbtxo- дом, а первый выход - с вторым входом цифрового преобразователя, второй и третий выходы - с горизонтально отклоняющими пластинами и модулятором ЭЛТ, вертикально отклоняющие пластины которой подключены к выходу усилителя, первым входом соединенного с вторым вькодом коммутатора аналог-цифра, блок выбора режима работы, первый и второй блоки изменения уровня постоянного напряжения, отличающийся тем, что, с целью ул чшения метрологических характеристик при одновременном повышении оперативности измерений, в него введены пять логических элементовv два элемента ИЛИ, инвертор и коммутатор уровня, выход которого соединен с вторым входом усилителя, первый вход - с вьгходом первого, а второй вход - с выходом второго блоков изменения уровня постоянного напряжения, трет1-п 1 и четвертый входы - с третьим и четвертым входами коммута Ора капалов и с выходами первого и вто9 1524003

рого элементов ИЛИ, первые входы ко-подключен к первым входам первого и

торых подключены к выходам первогочетвертого элементов И, второй вход

и второго элементов И, вторые входыпервого элемента И соединен с первым

к выходам третьего и четвертого эле-выходом, а второй вход четвертого

ментов И, первые входы второго иэлемента И - с вторым выходом блока

третьего элементов И соединены соот-выбора режима работы, третий выход

ветственно с третьим и четвертым вы-которого подключен к первому входу

ходами цифрового преобразователя,пятого элемента И, вторым входом соевторые входы этих элементов - ме) диненного с первым выходом коммутатособой и с выходом пятого элемента Ира аналог-цифра. и входом инвертора, выход которого

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой осциллограф | 1987 |

|

SU1525589A1 |

| Измеритель фазовых сдвигов четырехполюсников | 1979 |

|

SU890264A1 |

| Электронно-лучевой осциллограф | 1987 |

|

SU1442922A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Осциллографический регистратор одиночных электрических импульсов | 1982 |

|

SU1108880A1 |

| Измеритель временных интервалов | 1987 |

|

SU1442923A1 |

| Устройство для измерения мгновенных значений периодических сигналов | 1987 |

|

SU1430899A1 |

| Устройство для оценки функционального состояния головного мозга | 1989 |

|

SU1814871A1 |

| Осциллографический измеритель амплитудных параметров электрических сигналов | 1985 |

|

SU1285380A1 |

| Цифровое измерительное осциллографическое устройство | 1980 |

|

SU951147A1 |

Изобретение относится к электроизмерительной технике и может быть использовано при разработке осциллографической аппаратуры. Цель изобретения - улучшение метрологических характеристик осциллографа при одновременном повышении оперативности измерений. Исследуемые сигналы, поступая на входы блока 1 усилителей каналов, усиливаются или ослабляются в них и передаются на входы коммутатора 5 каналов (КК). КК 5 работает в режимах "I", "II", "I±II", "Прерывисто. В режимах "I или "II" наблюдается сигнал с одного из каналов, в режиме "I±II" - сумма или разность сигналов, в режиме "Прерывисто" - оба сигнала одновременно. С выхода КК 5 сигнал поступает на входы цифрового преобразователя 6 и коммутатора 7 аналог-цифра. Коммутатор 7 аналог-цифра обеспечивает аналоговый и цифровой режимы. Благодаря введению в устройство элементов И 16 - 20, элементов ИЛИ 14 и 15, инвертора 21 и коммутатора 13 уровня появилась возможность перемещать осциллограмму вдоль оси Y в режиме воспроизведения запомненного сигнала, что повышает точность и оперативность измерений. 1 ил.

| АВТОМАТИЧЕСКИЕ ВЕСЫ ДЛЯ ЗЕРНОВЫХ ПРОДУКТОВ | 1925 |

|

SU4000A1 |

Авторы

Даты

1989-11-23—Публикация

1987-05-04—Подача