Изобретение относится к измерительной технике и может быть использовано для записи, хранения и отображения информации о формах сигналов в многофазной электрической сети при наличии переходного процесса и его времени, а также может найти широкое применения в других областях науки и техники.

Известен электронно-лучевой осциллограф с цифровым запоминанием формы исследуемого сигнала, содержащий усилитель вертикального отклонения, вход которого подключен к исследуемому сигналу, а выход через последовательно соединенные аналого-цифровой преобразователь (АЦП), быстродействующее оперативное запоми- нающее устройство (ОЗУ) и цифроаналоговый преобразователь (ЦАП) связан с вертикально отклоняющими пластинами электронно-лучевой трубки (ЭЛТ), причем горизонтально отклоняющие пластины ЭЛТ через блок горизонтальной развертки подсоединены к входу синхронизации.

Известно многоканальное устройство для регистрации и индикации мгновенных сигналов, имеющее почти аналогичное назначение.

Известен также электронно-лучевой осциллограф с цифровым запоминанием формы исследуемого сигнала, содержащий последовательно соединенные усилитель вертикального отклонения, АЦП, быстродействующее ОЗУ, блок управления, второе ОЗУ, арифметическое логическое устройство (АЛУ), блок совпадения кодов и электронный коммутатор, выход которого подключен к катоду ЭЛТ, генератор тактовых импульсов, связанный через счетчик точек в строке, счетчик строк и блок формирования строчной и кадровой разверток с отклоняющими электродами ЭЛТ, при этом выходы блока управления связаны с соответствующими входами счетчика строк, второго ОЗУ, счетчика точек в строке, электронного коммутатора и АЛУ, выходы блока формирования строчной и кадровой разверток подключены к входам счетчика точек в строке, а второй вход электронного коммутатора связан с ОЗУ. По совокупности существенных признаков этот осциллограф принят за прототип.

Из функциональной схемы и описания работы прототипа вытекает, что в блок формирования строчной и кадровой разверток входят усилители вертикального и горизонтального отклонения, выходы которых подключены к вертикальным и горизонтальным отклоняющим пластинам ЭЛТ, и высоковольтный источник питания.

Принцип действия прототипа заключается в следующем. За сравнительно малый временной интервал τ мгновенные значения напряжения входного аналогового сигнала преобразуются в их цифровые эквиваленты Nк (коды) и записываются в ячейки памяти ОЗУ, а затем с помощью блока управления и ЦАП вновь преобразуются в аналоговый сигнал, который периодически отображается на экране ЭЛТ.

Очень часто при проведении исследовательских и эксплуатационных работ требуется специальный необслуживаемый электронный осциллограф, который бы автоматически переходил в режим записи информации о времени переходного процесса t, значениях пиковых напряжений обоих полярностей ±Ui всех контролируемых каналов n и, самое главное, формы этих сигналов.

Переходные процессы в энергосетях могут быть обусловлены грозовыми разрядами, разрядами между проводами линий электропередачи, резкими изменениями нагрузки и прочими дестабилизирующими факторами. Эти процессы характеризуются тем, что на сигнал основной частоты (например, 50 Гц) накладываются высокочастотные составляющие сигнала, которые постепенно затухают (примерно через 0,1 с) скорее всего по экспоненциальному закону, причем более высокочастотные составляющие сигнала затухают быстрее. Чтобы более рационально использовать память ОЗУ, необходимо по мере затухания переходного процесса снижать частоту опроса fт сигнала Uс, что влечет изменение функциональной схемы устройства управления. Переходным или аварийным процессом в энергосетях может быть принят сигнал, мгновенное значение которого превышает амплитудное напряжение, например, на 10%.

Используя различные преобразователи неэлектрических величин в электрические с помощью заявляемого регистратора можно автоматически регистрировать форму и значение вибрации, землетрясения, давления и т.д., значения которых превышают выбранный порог, с возможностью записи их формы колебаний и времени этого события. Целью изобретения является расширение функциональных возможностей регистратора за счет автоматической регистрации формы переходных или аварийных процессов, значений пиковых напряжений обоих полярностей всех каналов и времени этого процесса с отображением информации на экране ЭЛТ, цифровом индикаторе и цифропечатающем устройстве (ЦПУ).

Цель достигается тем, что в цифровой регистратор переходных процессов, содержащий три идентичных канала, в каждом из которых последовательно включены согласующий усилитель, АЦП, ОЗУ, блок D-триггеров и ЦАП, усилитель вертикального отклонения и блок развертки, связанные с соответствующими пластинами ЭЛТ, введены блок операционных детекторов, входы которого подсоединены к входам схемы автоматического запуска и к выходам согласующих усилителей, а выходы через первый кодоуправляемый аналоговый коммутатор, четвертый АЦП и второе ОЗУ подключены к входам блока индикации и регистрации данных, электронные часы, кодовые выходы которых подсоединены к информационным входам второго кодоуправляемого аналогового коммутатора, биполярный источник образцового напряжения, связанный с входами третьего кодоуправляемого аналогового коммутатора, блок управления записи и считывания информации, стробирующие выходы которого подключены к стробирующим входам блока вывода данных, причем выходы ЦАП соединены с информационными входами третьего кодоуправляемого аналогового коммутатора, а выход последнего связан с входом усилителя вертикального отклонения, биполярный источник образцового напряжения подсоединен к четвертому входу, а выход блока индикации и регистрации данных к пятому входу схемы автоматического запуска, выход "Запуск" которой подключен к входу блока управления записи и считывания информации, а выходы +Uпор и -Uпор подсоединены к соответствующим входам первого кодового управляемого аналогового коммутатора, выходы кода адреса блока управления записи и считывания информации связаны с адресными входами ОЗУ, с блоком вывода данных, блоком развертки и блоком индикации и регистрации данных, выходы младших разрядов кода адреса подключены к адресным входам всех кодоуправляемых аналоговых коммутаторов, выходы WR-1 и CS-1 заведены на входы первого ОЗУ, а выходы WR-2 и CS-2 - на входы второго ОЗУ, выходы RD-1 и RD-2 подключены соответственно к блоку D-триггеров и к блоку индикации и регистрации данных, выходы Г3-1 - к входам запуска первых трех АЦП, выход Г3-2 - к входу запуск четвертого АЦП, выход С4 - к стробирующему входу первого кодоуправляемого аналогового коммутатора, выходы второго кодоуправляемого аналогового коммутатора подключены к информационным входам второго ОЗУ, входы согласующих усилителей связаны с источниками сигнала.

Анализ технической и патентной литературы показал, что не существует технических решений, которые по функциональным признакам были бы близки к заявляемому устройству. Поэтому данное устройство обладает существенными отличиями и новизной.

Работа заявляемого устройства поясняется чертежами, временными диаграммами и осциллограммами, изображенными на фиг.1-фиг.10.

На фиг.1 изображена функциональная схема цифрового регистратора переходных процессов, который содержит согласующие усилители 1, 2 и 3, схему 4 автоматического запуска, электронные часы и таймер 5, АЦП 6, 7, 8 и 11; блок 9 операционных детекторов, кодоуправляемые аналоговые коммутаторы 10, 12 и 23, ОЗУ 13 и 15, блок 14 управления записью и считыванием информации, блок 16 D-триггеров, блок 17 вывода данных, блок 18 индикации и регистрации данных, ЦАП 19, 20 и 21, блок 22 развертки, биполярный источник 24 образцовых напряжений, усилитель 25 вертикального отклонения, ЭЛТ 26.

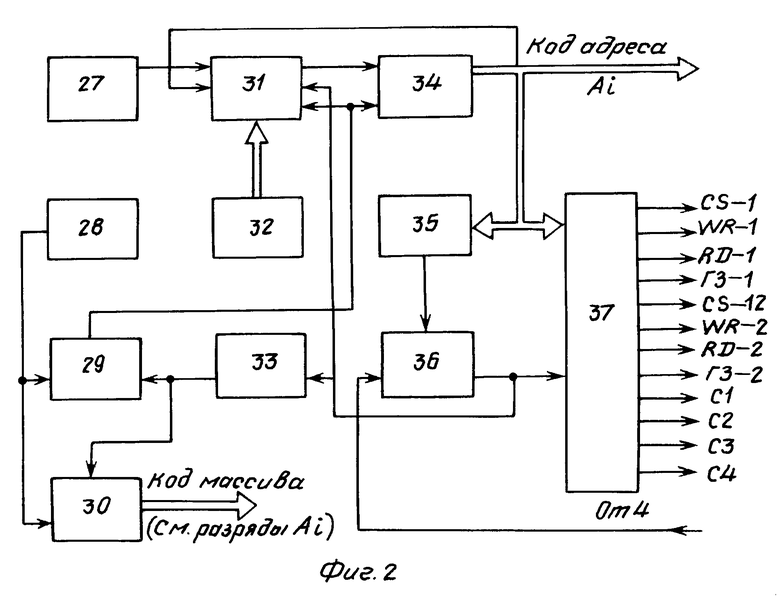

На фиг. 2 представлена функциональная схема одной из возможных реализаций блока 14 управления записью и считыванием информации, который содержит генератор 27 тактовых импульсов, схему 28 общего сброса, логический элемент ИЛИ 29, счетчик 30 команд, кодоуправляемый делитель 31 частоты, схему 32 формирования кодов режима работы, формирователь 33 коротких импульсов, счетчик-формирователь 34 кода адреса, логический элемент И-НЕ 35, RS-триггер 36 и формирователь 37 импульсов, необходимый для функционирования регистратора.

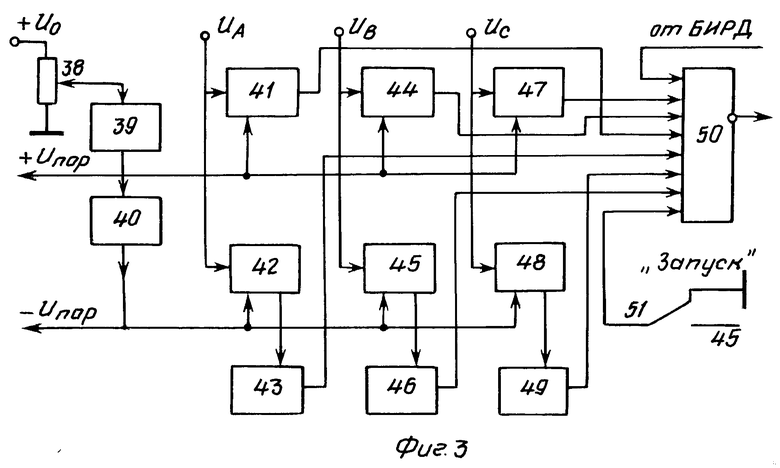

На фиг. 3 изображена одна из возможных реализаций схемы 4 автоматического запуска, которая содержит потенциометр 38, согласующий усилитель 39, аналоговый инвертор 40, аналоговые компараторы 41, 42, 44, 45, 47 и 48, логические инверторы 43, 46 и 49, логическую схему 8 ИЛИ-НЕ 50, кнопка 51 "Запуск".

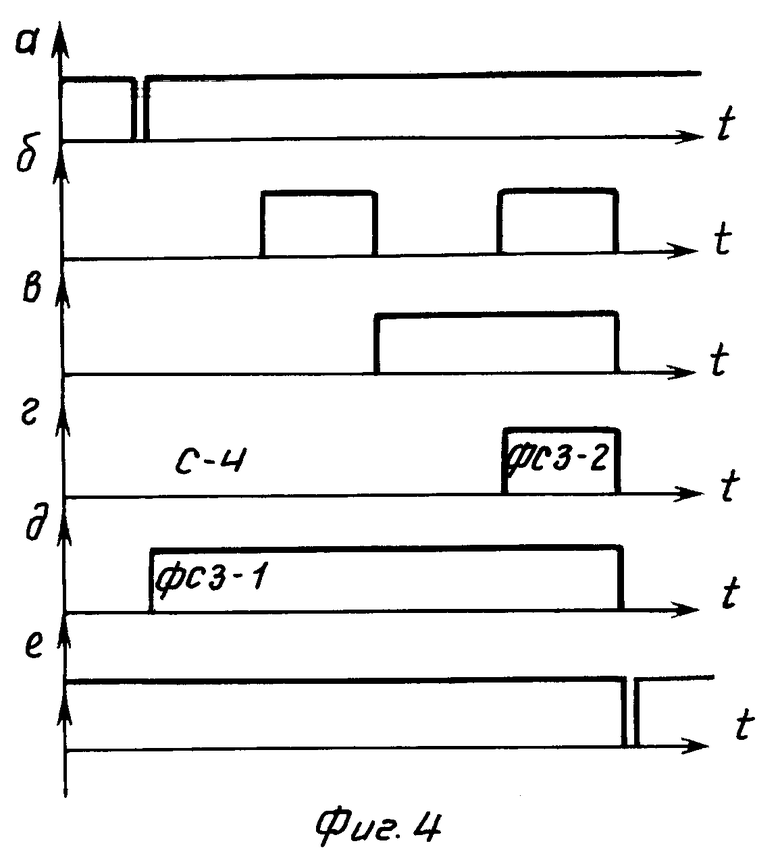

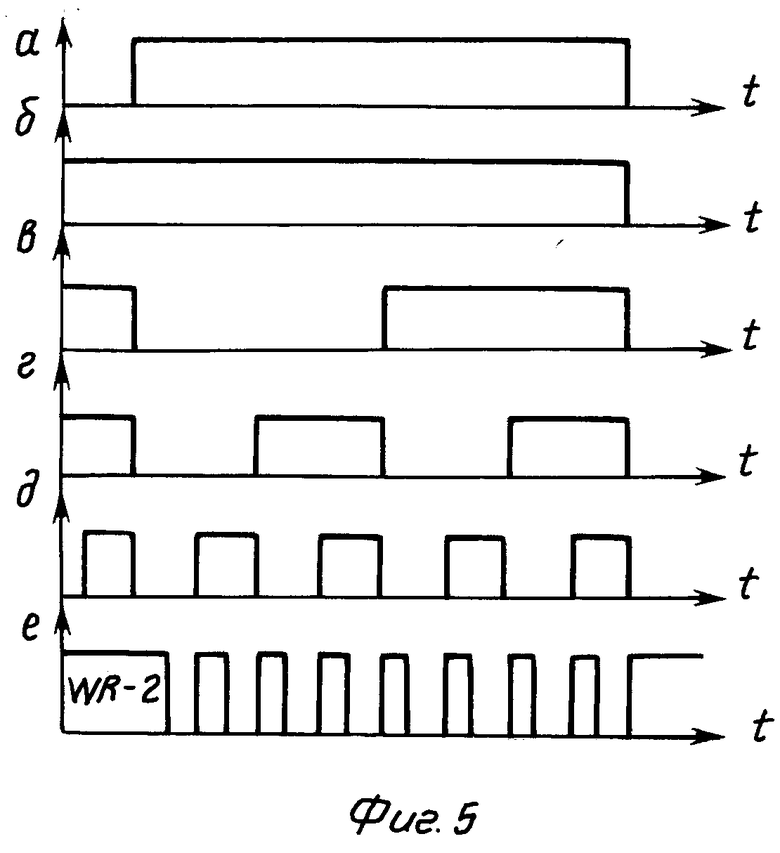

На фиг.4 представлены временные диаграммы, поясняющие формирование импульсов "Запись" и "Строб записи 2"; на фиг.5 - временные диаграммы, поясняющие формирование пачки импульсов WR-2; на фиг.6 - ориентировочные временные положения импульсов Г3-2, WR-2, CS-2 и RD-2. Следует отметить, что одновременное наличие импульсов WR-2 и RD-2 невозможно. В режиме записи формируются импульсы WR-2, а в режиме считывания информации непрерывно вырабатываются импульсы RD-2.

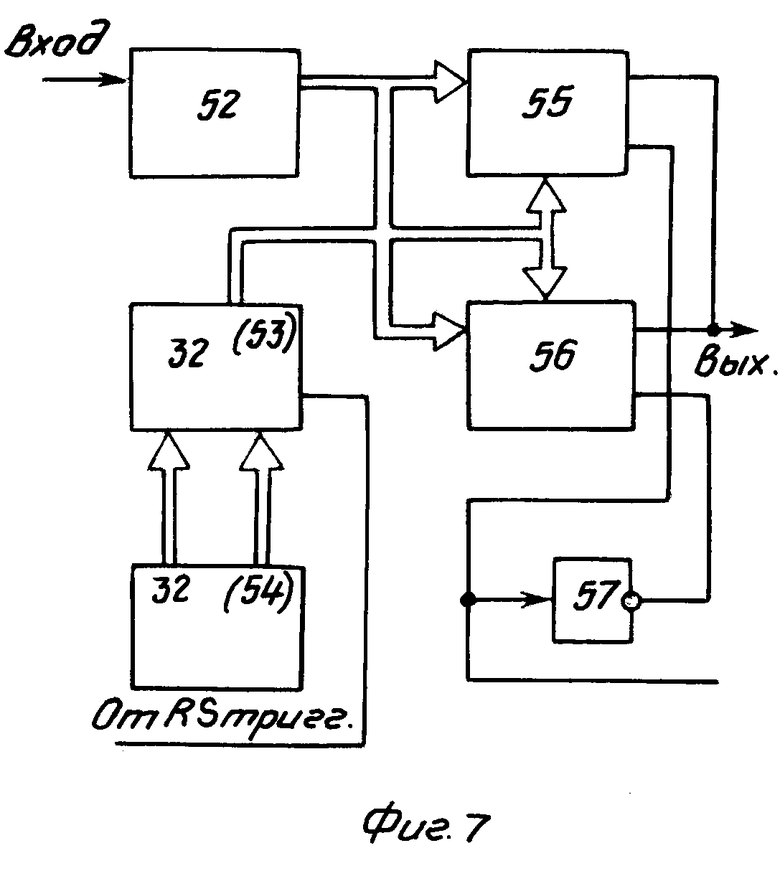

На фиг. 7 представлена одна из возможных реализаций кодоуправляемого делителя 31 частоты, который содержит двоичный делитель 52 частоты, коммутатор 53 кодов, схему 54 (32) формирования кодов режима работы, кодоуправляемые коммутаторы 55 и 56, логический инвертор 57.

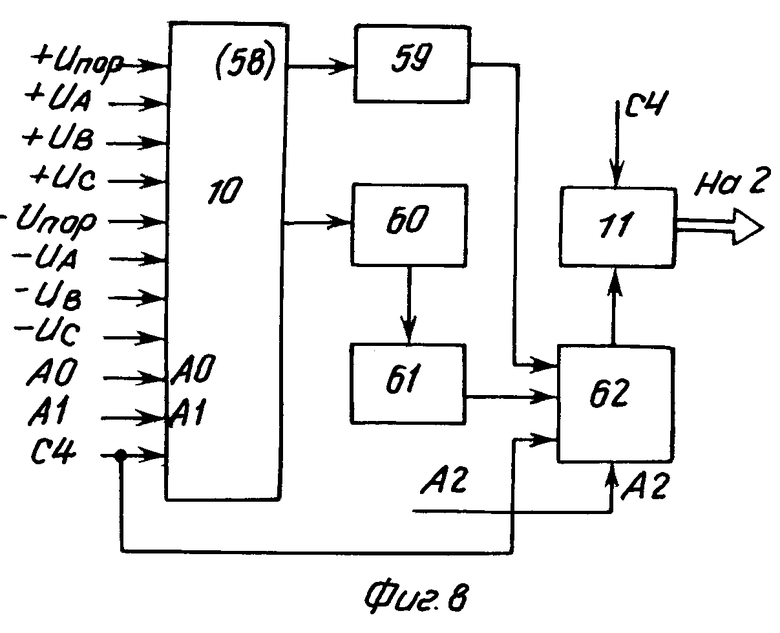

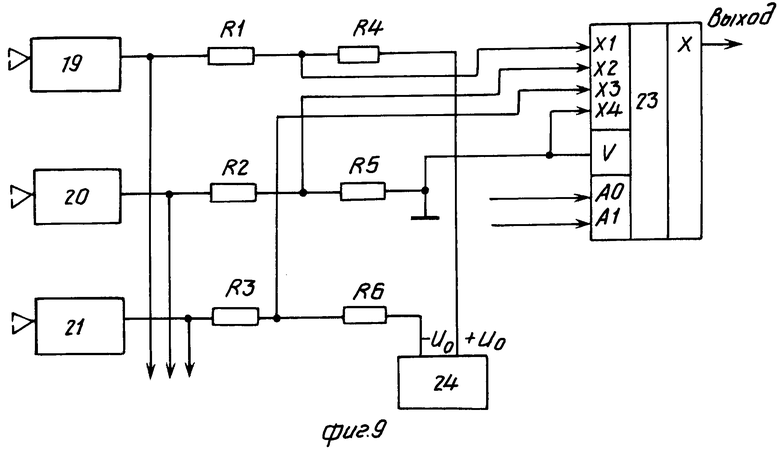

На фиг. 8 показан кодоуправляемый аналоговый коммутатор 58 (10) и приняты следующие обозначения: 59 и 60 - согласующие усилители, 61 - аналоговый инвертор, 62 - кодоуправляемый аналоговый коммутатор. На фиг.9 показано формирование сигнала вертикального отклонения с помощью кодоуправляемого аналогового коммутатора 23.

Цифровой регистратор переходных процессов работает следующим образом.

Входные сигналы, пропорциональные напряжениям в фазах А, В и С (UA', UB' и UC'), через согласующие усилители 1, 2 и 3 поступают на входы АЦП 6, 7 и 8, а также на входы схемы 4 автоматического запуска и блока 9 операционных детекторов. Кодовые выходы АЦП подсоединены к информационным входам ОЗУ 13. При нормальном напряжении в трехфазной сети переменного тока никакой информации в память ОЗУ 13 с АЦП не записывается и регистратор работает в режиме воспроизведения информации. Схема 4 автоматического запуска вырабатывает два пороговых напряжения +Uпор и -Uпор, абсолютные значения которых приблизительно равны и превышают амплитуду выходных сигналов Uс согласующих усилителей 1-3, например, на 10%.

Если мгновенное значение напряжения сигнала Uc на выходе хотя бы одного из согласующих усилителей 1-3 превысит |Uпор|, то на выходе схемы 4 автоматического запуска вырабатывается импульс, который поступает на вход блока 14, взводит RS-триггер 36 и переводит регистратор в режим записи информации. Передний фронт RS-триггера с помощью формирователя 33 коротких импульсов вырабатывает импульс, который через элемент ИЛИ 29 поступает на шины сброса кодоуправляемого делителя 31 частоты и счетчика-формирователя 34 кода адреса и устанавливает их триггеры в нулевое состояние. С этого момента регистратор автоматически переходит в режим параллельной записи информации в память ОЗУ 13 по всем трем каналам. Каждый импульс, поступающий на вход счетчика-формирователя 34, увеличивает его код на единицу.

Кодовые выходы счетчика-формирователя 34 подключены к соответствующим адресным входам ОЗУ 13, 15 и блоков 17, 18 и 22, причем к адресным входам ОЗУ 15 подсоединены только старшие разряды счетчика-формирователя 34. Это приводит к тому, что каждый вновь поступивший импульс на вход счетчика-формирователя записывает в очередную строку ОЗУ 13 новую информацию, вырабатываемую АЦП 6, 7 и 8. В действующем макете регистратора ОЗУ 13 реализовано на 24 интегральных микросхемах типа КР537РУ10, т.е. каждый канал рассчитан на хранение 16384 восьмиразрядных слов. Формирователь 37 импульсов вырабатывает три последовательности импульсов: Г3-1, с помощью которых осуществляются сброс предыдущих значений АЦП 6, 7 и 8 и их запуск, WR-1, с помощью которых ОЗУ 13 переходит в режим записи информации, и CS-1 - стробирующие импульсы.

Временная диаграмма последовательности импульсов Г3-1, WR-1 и CS-1 аналогична временной диаграмме, изображенной на фиг.6 и поясняющей работу ОЗУ 15.

Когда на всех триггерах счетчика-формирователя 34 будут высокие логические потенциалы, на выходе элемента И-НЕ 35 вырабатывается импульс, поступающий на S-вход RS-триггера 36 и возвращающий его в исходное состояние. С этого момента регистратор вновь автоматически переходит в режим воспроизведения информации. В режиме воспроизведения информации тактовые импульсы, имеющие, как правило, более низкую частоту fт, поступают на вход счетчика-формирователя 34 и последовательно изменяют его код Nк.

На каждый тактовый импульс блока 14 вырабатывает импульсы RD-1 и CS-1, с помощью которых информация, хранящаяся в памяти ОЗУ 13 последовательно импульсам RD-1 перезаписывается в память блока 16 D-триггеров. Кодовые выходы блока 16 подключены к соответствующим входам блока 17 вывода данных и к информационным входам 19, 20 и 21, на выходах которых вырабатываются периодически повторяющиеся последовательности мгновенных значений аналоговых сигналов, соответствующих последнему переходному процессу.

Эти сигналы (UA, UB и UC) могут поступать на входы графопостроителя, с помощью которого записывается форма сигналов переходного или аварийного процесса, и на аналоговые входы третьего кодоуправляемого аналогового коммутатора 23, на адресные входы которого подаются логические потенциалы, вырабатываемые блоком 14.

При коде адреса строки КСО = 0 и КС1 = 0 на выходе коммутатора 23 выделяется сигнал UA. При коде адреса строки КСО = 1 и КС1 = 0 на выходе коммутатора 23 выделяется сигнал UB, а при коде КСО = 0 и КС1 = =1 - сигнал UC. Для одновременного отображения формы осциллограмм переходного процесса по трем каналам на экране однолучевой ЭЛТ коммутатор 23 от биполярного источника 24 образцовых напряжений заводятся напряжения +Uo и -Uo. Одна из возможных схемных реализаций коммутатора 23 представлена на фиг.9.

Логические сигналы кода адреса, вырабатываемые блоком 14, поступают на адресные входы ОЗУ 13 и на блок 22. При коде N = 0 или N = Nмакc осуществляется запуск блока 22, вырабатывающего линейно изменяющееся напряжение горизонтальной развертки Uг. Это напряжение прикладывается к горизонтально отклоняющим пластинам ЭЛТ (26), а вертикально отклоняющие пластины ЭЛТ через усилитель 25 вертикального отклонения подключены к выходу коммутатора 23.

Кодовые выходы электронных часов 5 через второй кодоуправляемый коммутатор 12 подсоединены к информационным входам второго ОЗУ 15. Кроме того, информационные входы ОЗУ 15 через четвертый АЦП 11 и первый кодоуправляемый аналоговый коммутатор 10 подключены к выходам блока 9 операционных детекторов, который вырабатывает напряжения, равные пиковым значениям сигналов положительной и отрицательной полярности всех трех каналов.

Передний фронт импульса запуска, изображенного на фиг.4а, взводит RS-триггер 36, формируя строб записи ФСЗ-1, и с помощью формирователя 33 коротких импульсов через элемент ИЛИ 29 сбрасывает в нулевое состояние триггеры кодоуправляемого делителя 31 частоты и счетчика-формирователя 34 кода адреса, кодовые выходы которого подключены к элементу И-НЕ 35 и к формирователю 37 ОЗУ, 13, 15, блокам 17, 18 и 22. Каждый тактовый импульс, поступивший на вход счетчика-формирователя 34, увеличивает его код на единицу. Когда этот код N достигнет максимального значения Nмакс, на выходе элемента И-НЕ 35 вырабатывается низкий логический потенциал (фиг.4е), который возвращает формирователь 37 импульсов в исходное состояние и переводит регистратор в режим воспроизведения информации. Таким образом, ФСЗ-1 вырабатывает импульс, изображенный на фиг.4д. Старшие разряды кода адреса (фиг.4б, в) подключены к входам ФСЗ-2, входящего в формирователь 37, на выходе которого вырабатывается импульс строба С4 (фиг.4г).

За время действия импульса С4 (фиг.5а) на выходе формирователя 37 вырабатывается пачка из восьми импульсов WR-2 низкого логического потенциала (фиг.5е), которые поступают на вход WR ОЗУ 15, т.е. запись пиковых значений напряжений осуществляется в конце регистрируемого переходного процесса.

Одновременно на адресные входы АО, А1 и А2 кодоуправляемых аналоговых коммутаторов 10 и 12 поступают логические потенциалы, представленные соответственно на фиг.5в, 5г и 5д. В зависимости от кода адреса А0-А2 на вход АЦП 11 через коммутатор 10 поступает тот или иной аналоговый сигнал, который преобразуется АЦП 11 в цифровой эквивалент (код) и записывается в соответствующую строку ОЗУ 15. Реализация АЦП 11 представлена на фиг.8.

Согласующие усилители 59 и 60 предназначены для обеспечения большого входного сопротивления, предотвращающего разряд накопительных конденсаторов Сн блока 9 операционных детекторов. Аналоговый инвертор 61 имеет коэффициент усиления -1 и преобразует коммутируемые отри- цательные сигналы -Uпор, -UАмакс, -UBмакс и -UСмакс в положительные сигналы той же величины, т.е. на вход АЦП 11 поступают сигналы только положительной полярности. Старший разряд кода адреса А2 осуществляет подключение на вход АЦП 11 сигналов, снимаемых с выходов усилителя 59 или инвертора 61.

На фиг. 6 представлены временные диаграммы, поясняющие работу АЦП 11 и ОЗУ 15. После смены кода адреса АО вырабатывается импульс Г3-2, с помощью которого осуществляется сброс (гашение) предыдущей выходной информации АЦП 11, а задний фронт этого импульса осуществляет запуск АЦП 11, т.е. дает команду на очередное измерение сигнала.

Импульс опроса CS-2 располагается примерно в средней части импульса WR-2. Время tп отводится АЦП 11 для получения эквивалентного кода Nк. В режиме записи информации блок 14 вырабатывает импульсы WR-2, а в режиме воспроизведения информации - импульсы RD-2 (импульсы считывания), которые поступают на входы D-триггеров блока 16.

Блок 18 индикации и регистрации данных включает в свой состав схему цифрового воспроизведения данных с цифровым индикатором и ЦПУ. Для перевода каретки ЦПУ в блоке 18 формируются коды перевода строки и возврата каретки, после которого блок 18 вырабатывает импульс запуска, поступающий на вход схемы 4 и увеличивает код адреса массива счетчика 30 команд на единицу, т. е. подготавливает для регистрации на ЦПУ информации о следующем переходном процессе. В блоке 18 имеется тумблер "Запрет записи", который позволяет считывать информацию без ее стирания в ОЗУ. ЦПУ работает в обычном режиме запрос - ответ. Для индикации данных на цифровом индикаторе в блоке 18 имеются дешифратор двоично-десятичного кода в позиционный семисегментный код, а также регистр сдвига для динамической индикации данных, входы которого подключены к выходам блока 14.

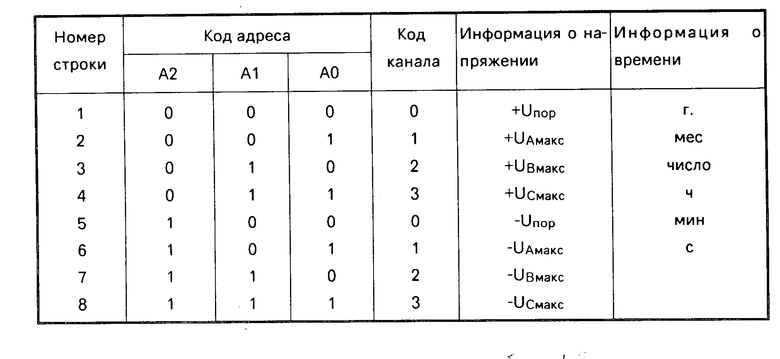

Код адреса А0-А2 определяет, какая информация записывается в память ОЗУ 15, и в реализованном макете регистратора она может быть представлена в виде таблицы.

Рассмотрим работу блока 14 управления записью и считыванием информации.

На вход кодоуправляемого делителя 31 частоты поступают тактовые импульсы генератора 27. Установочные входы делителя 31 связаны со схемой 32 формирования кода режима работы. Одна из возможных схемных реализаций делителя 31 представлена на фиг. 7. Выходы двоичного делителя 52 частоты подключены к информационным входам кодоуправляемых коммутаторов 55 и 56 таким образом, чтобы на одноименные входы коммутатора 56 поступали импульсы, период следования которых был бы в 4 или в 8 раз больше, чем у коммутатора 55. Адресные входы коммутаторов 55 и 56 одинаковые, а код, подаваемый на них, определяется коммутатором 53 и схемой 32, которая задает код записи и код считывания информации.

Предположим, что коммутатор работает только при низком логическом потенциале на входе "Разрешение". Соединив выход старшего разряда, например А10, счетчика-формирователя 34 непосредственно с входом "Разрешение" коммутатора 55 и через инвертор 57 с входом "Разрешение" коммутатора 56, запрещают их одновременную работу.

Пока выходной код Nк счетчика-формирователя 34 меньше 0,5˙Nмакс, выход старшего разряда имеет низкий логический уровень и на вход счетчика-формирователя 34 поступают тактовые импульсы с выхода коммутатора 55. Когда выходной код N ≥0,5 Nмакс, выход старшего разряда приобретает высокий логический потенциал, под действием которого закрывается коммутатор 55 и открывается коммутатор 56. С этого момента период следования тактовых импульсов возрастает, например, в 4 или 8 раз. Эта реализация необходима для того, чтобы начальный участок переходного процесса, характеризующийся наличием высоко- частотных составляющих сигнала, опpашивать с более высокой тактовой частотой fт.

Скорость считывания информации может быть выбрана ниже и выше скорости записи информации, и их значения зависят от положения переключателей схемы 32. Управляющий вход коммутатора 53 кодов подключен к RS-триггеру 36. При отсутствии переходного процесса на адресные входы коммутаторов 55 и 56 через коммутатор 53 кодов поступает код считывания информации, а при переходном процессе - код записи.

Так как в режимах "запись" и "считывание" управления разрешением старшим разрядом счетчика-формирователя 34 аналогичны, то при воспроизведении информации на ЭЛТ наблюдают целостную картину.

Счетчик-формирователь 34 представляет собой обычный двоичный счетчик, реализованный на ИМС типа КР1561ИЕ20.

Временные диаграммы, поясняющие взаимное смещение импульсов Г3-2, WR-2, CS-2 и RD-2, представлены на фиг.6. Аналогичное расположение имеют импульсы Г3-1, WR-1, CS-1 и RD-1. Эти импульсы легко могут быть получены при использовании интегральных микросхем КМОП или ТТЛ или с помощью микропроцессорных схем и не требуют пояснений. В режиме записи информации отсутствуют импульсы RD-1 и RD-2, а в режиме считывания информации отсутствуют импульсы Г3-1, Г3-2, WR-1 и WR-2. Режим работы регистратора определяет логический потенциал на выходе RS-триггера. Импульсы Г3-1 осуществляют сброс-запуск быстродействующих АЦП 6, 7 и 8. В начале каждого переходного процесса формирователя 33 коротких импульсов вырабатывает импульс, который обнуляет триггеры делителя 31 частоты и счетчика-формирователя 34, а также увеличивает на единицу выходной код Nск счетчика 30 команд.

Кодовые выходы этого счетчика подсоединены к старшим разрядам ОЗУ 13 и 15, которые реализованы на ИМС типа КР537РУ10, причем ОЗУ 13 содержит 24, а ОЗУ 15 - две ИМС, имеющих организацию 2048х8.

Как видно из вышеприведенной таблицы, на каждый цикл записи информации о переходном процессе в ОЗУ 15 отводятся восемь строк. Для выбранных ИМС типа КР537РУ10 ОЗУ 15 способно хранить до 256 циклов измерения переходных процессов. Чтобы обеспечить полную загрузку памяти ОЗУ 15, счетчик 30 команд должен иметь максимальный выходной код массива Nск.макс = 256 и может быть реализован на одной ИМС типа КР561ИЕ20, К561ИЕ10 и пр.

Для выбранной организации памяти ОЗУ 13 оно способно хранить коды осциллограмм восьми переходных процессов. В зависимости от длительности записываемого процесса t и спектрального состава сигнала fмакс количество строк, отводимых на один цикл измерения, и количество циклов измерения n могут изменяться в широких пределах.

В состав формирователя 37 импульсов входит счетчик строк, кодовые выходы КСО и КС1 которого подключены к соответствующим адресным входам А0 и А1 коммутатора 23, одна из возможных схемных реализаций которого представлена на фиг.9. На выходе коммутатора 23 поочередно выделяются сигналы переходных процессов, соответствующие фазам А, В и С. Частота циклического обновления информации отображаемого переходного процесса должна быть не ниже 20 Гц. Выходы счетчика строк подсоединены также к дешифратору, на выходе которого вырабатываются стробирующие импульсы С1, С2 и С3, поступающие на соответствующие входы блока 17, а на информационные входы блока 17 подается цифровая информация с выхода блока 16 D-триггеров.

Таким образом, на шину данных ЭВМ последовательно передаются коды мгновенных значений напряжений Ui вначале канала А, затем каналов В и С. При необходимости на ЭВМ могут быть переданы данные кода адреса Аi и кода массива Вi. ЭВМ определяет уровни спектральных составляющих сигнала для данного переходного процесса. Если есть необходимость сохранения информации, хранящейся в памяти ОЗУ 13 и 15, то необходимо в формирователе 37 установить переключатель в положение "запрет записи", а затем с помощью кнопки 51 "Запуск" можно шаг за шагом производить считывание информации, которая хранится в памяти ОЗУ. В схеме 8 ИЛИ-НЕ 50 предусмотрен вход для изменения кода массива с помощью импульсов запроса, вырабатываемого ЦПУ блока 18.

Делитель 31 частоты совместно со счетчиком-формирователем 34 могут примерно в 1000 раз изменять скорость записи и воспроизведения информации. При визуальном отображении информации с цифрового индикатора блока 18 период обновления информации обычно выбирают 2-4 с.

Информация, соответствующая последнему циклу измерения или циклу, выбранному оператором, циклически обновляется в порядке, который указан в таблице, до тех пор, пока не наступит новый переходный процесс или не будет нажата кнопка "Запуск".

Вместо ЭЛТ в заявляемом регистраторе может быть применена светодиодная матрица, например, с организацией 1024х1024. При этом три сектора 1024х256 следует отвести на отображение переходного процесса, а один сектор матрицы 1024х256 использовать на отображение информации ОЗУ 15. Это ведет к тому, что отпадет необходимость в использовании ЦАП, усилителей горизонтального и вертикального отклонения и высоковольтного источника напряжения, но в блок 18 потребуется ввести знаковый генератор, например, выполненный на интегральной микросхеме ИМС типа К555РЕЧ и способный отображать 256 разновидностей знаков (цифры, буквы русского, латинского и греческого алфавитов, алгебраические, тригонометрические и прочие знаки). Для этого необходимо выходы блока 16 D-триггеров и выходы кода адреса блока 14 соединить соответственно с вертикальными и горизонтальными входами матрицы.

Схема 4 автоматического запуска автоматически переводит многоканальный осциллограф в режим записи очередного переходного процесса и включает в свой состав шесть аналоговых компараторов, на первые входы которых подаются выходные напряжения согласующих усилителей 1, 2 и 3, а на вторые - пороговые напряжения +Uпор и -Uпор, которые снимаются с выходов четвертого согласующего усилителя 39 и аналогового инвертора 40 (фиг.3). Эти же пороговые напряжения поступают соответственно на первый и пятый информационные входы первого кодоуправляемого аналогового коммутатора 10.

Аналогично выход согласующего усилителя 39 подсоединен к вторым входам первого, третьего и пятого аналоговых компараторов 41, 44 и 47 и к первому аналоговому входу коммутатора 10. Первые входы первого и второго аналоговых компараторов 41 и 42 связаны с выходом первого согласующего усилителя 1. Аналогично первые входы компараторов 43 и 44 подсоединены к выходу согласующего усилителя 2, а первые входы компараторов 47 и 48 - к выходу согласующего усилителя 3.

При отсутствии переходного процесса на выходах компараторов 41, 44, 47 имеется низкий логический уровень (уровень логического "0"), а на выходах аналоговых компараторов 42, 45, 48 - высокий логический уровень, который через цифровые инверторы 43, 46 и 49 подключены к соответствующим входам схемы 8ИЛИ-НЕ 50. Bыходы аналоговых компараторов 41, 44, 47 и контакт кнопки 51 "Запуск" также подсоединены к соответствующим входам схемы 8ИЛИ-НЕ 50.

Таким образом, при отсутствии переходного процесса на выходе схемы 8ИЛИ-НЕ 50 существует высокий логический потенциал. Если мгновенное значение напряжения UA, UB и (или) UC превысит выбранный уровень пороговых напряжений +Uпор и -Uпор, то на соответствующем (соответствующих) входе схемы 8ИЛИ-НЕ 50 появляется импульс положительной полярности, который изменяет выходной уровень схемы 8ИЛИ-НЕ 50 и тем самым запускает RS-триггер 36.

Уровень порогового напряжения оператор может устанавливать вручную по своему усмотрению. Последующие импульсы, вырабатываемые схемой 4, не могут изменить состояние уже взведенного RS-триггера.

После поступления импульса элемента И-НЕ 35 на другой вход RS-триггера 36 процесс записи завершается и регистратор автоматически переходит в режим воспроизведения последней информации. Процесс записи может возобновиться лишь с началом нового переходного процесса.

Уровни пороговых напряжений +Uпор ≈|-Uпор| обычно выбираются на 10-15% больше амплитуды сигналов, снимаемых с выходов согласующих усилителей 1, 2 и 3, и соответствуют нормальным условиям эксплуатации энергосети.

ОЗУ 13 и 15 реализуются на КМОП ИМС, т.е. имеют очень малое потребление тока в режиме хранения информации и питаются от маломощного буферного источника питания, работающего в режиме подзаряда. Это дает возможность сохранить информацию о переходных процессах в обесточенном регистраторе в течение ≈ 2000 ч, т.е. при транспортировании регистратора из одного пункта в другой информация сохраняется.

Предлагаемый регистратор может эксплуатироваться на не обслуживаемом человеком (оператором) объекте и автоматически записывать в память ОЗУ форму переходного процесса в каждом канале, его экстремальные значения напряжений и время, соответствующее этому переходному процессу, хранить в памяти ОЗУ несколько переходных процессов и последовательно воспроизводить их на экране ЭЛТ или светосигнальной матрице, иметь более высокие эксплуатационные характеристики.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА | 1991 |

|

RU2011966C1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2008 |

|

RU2377721C1 |

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1480127A1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

| Автоматическое устройство для поверки стрелочных электроизмерительных приборов | 1985 |

|

SU1320783A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

Изобретение относится к электроизмерительной технике и может быть использовано для записи, хранения и воспроизведения формы сигналов в сети трехфазного переменного тока при наличии переходного непериодического процесса. Целью изобретения является расширение функциональных возможностей регистратора за счет автоматической регистрации переходных процессов, пиковых значений напряжений обоих полярностей и времени переходного процесса с отображением этой информации на экране ЭЛТ, цифровом индикаторе и цифропечатающем устройстве. Сущность изобретения: регистратор содержит схему 4 автоматического запуска, выход которой подключен к блоку 14 управления записью и считыванием информации, а входы - к выходам согласующих усилителей 1, 2 и 3 и входам блока 9 операционных детекторов, четвертый аналого-цифровой преобразователь 11, вход которого через кодоуправляемый аналоговый преобразователь 10 связан с выходами блока 9 операционных детекторов и схемой 4 блока D = триггеров, кодоуправляемый коммутатор 12, выходы которого подсоединены к информационным входам второго оперативного запоминающего устройства 15, информационные входы - к выходам электронных часов 5, а адресные входы - к блоку 14, третий кодоуправляемый аналоговый коммутатор 23, аналоговые входы которого подключены к выходам цифроаналоговых преобразователей 19, 20 и 21 и к выходам биполярного источника 24 образцового напряжения, а адресные входы - к выходам делителя частоты блока 14. 1 з.п. ф-лы, 1 табл., 9 ил.

| Данилов Р.В | |||

| и др | |||

| Справочник | |||

| Применение интегральных микросхем в вычислительной технике | |||

| М.: Радио и связь, 1987. |

Авторы

Даты

1995-02-20—Публикация

1990-05-03—Подача