СЭуе. /

тения - повышение помехоустойчивости Работа анализатора основана на анализе прошедшего через объект 2 контро- ля специального сигнала, которьм Содержит в себе попарную последователь- JHocTb импулв сов тональной частоты |для контроля амплитудно-частотной характеристики и один равномерно-стру- |пенчатый импульс для контроля ампли- тудной характеристики. Каждая пара содержит один, первьш импульс постоянной опорной частоты и один импульс переменной контрольной частоты. Сигнал на входе анализатора фильтруется и детектируется. Напряжение сигнала опорной частоты запоминается в первом элементе 16 памяти и поступает одновременно в первый делитель 18 напряжения, в котором вырабатывается нор- мированное напряжение. С этим напряжением в элементе 11 сравнения сравнивается напряжение контрольной частоты, пришедшее непосредственно с объекта 1 контроля. Результат срав-

нения через ключ 8 поступает в регистратор 46. Для контроля амплитудной характеристики первая максимальная посьшка запоминается во втором элементе 16 памяти и делится равномерно в количество раз, равное количеству ступенек, образуя квазизталонное ступенчатое напряжение Затем поступен- чато сравниваются посылки, пришедшие с объекта с квазиэталонными. Процесс контроля реализуется только в том случае, если открыты ключи 34-36 для прохождения опорного сигнала на формирование когерентных управляющих напряжений работой анализатора. Ключи управляются от схемы повышения помехоустойчивости. В этой схеме компараторы 39 и 40 в сочетании с аналоговым интеграторами 42 и 43 и одно- вибpaтopa ш 30-32 осуществляют селекцию по уровню напряжения и длительности посыпок, а в сочетании с сумматором 45 обеспечивают достижение цели изобретения 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля амплитудных характеристик | 1985 |

|

SU1308943A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| Устройство для контроля изделий и материалов | 1982 |

|

SU1078319A2 |

| Устройство для контроля состояния информационно-измерительной системы | 1986 |

|

SU1314342A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство для считывания графической информации | 1981 |

|

SU987646A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Устройство для контроля неравномерности амплитудно-частотной характеристики | 1985 |

|

SU1298931A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для автоматического контроля параметров объектов с переменными параметрами. Цель изобретения - повышение помехоустойчивости. Работа анализатора основана на анализе прошедшего через объект 2 контроля специального сигнала, который содержит в себе попарную последовательность импульсов тональной частоты для контроля амплитудно-частотной характеристики и один равномерно-ступенчатый импульс для контроля амплитудной характеристики. Каждая пара содержит один, первый импульс постоянной опорной частоты и один импульс переменной контрольной частоты. Сигнал на входе анализатора фильтруется и детектируется. Напряжение сигнала опорной частоты запоминается в первом элементе 16 памяти и поступает одновременно в первый делитель 18 напряжения, в котором вырабатывается нормированное напряжение. С этим напряжением в элементе 11 сравнения сравнивается напряжение контрольной частоты, пришедшее непосредственно с объекта 1 контроля. Результат сравнения через ключ 8 поступает в регистратор 46. Для контроля амплитудной характеристики первая максимальная посылка запоминается во втором элементе 16 памяти и делится равномерно в количество раз, равное количеству ступенек, образуя квазиэталонное ступенчатое напряжение. Затем поступенчато сравниваются посылки, пришедшие с объекта с квазиэталонными. Процесс контроля реализуется только в том случае, если открыты ключи 34 - 36 для прохождения опорного сигнала на формирование когерентных управляющих напряжений работой анализатора. Ключи управляются от схемы повышения помехоустойчивости. В этой схеме компараторы 39 и 40 в сочетании с аналоговыми интеграторами 42 и 43 и одновибраторами 30 - 32 осуществляют селекцию по уровню напряжения и длительности посылок, а в сочетании с сумматором 45 обеспечивают достижение цели изобретения. 3 ил.

Изобретение относится к контроль- но-изм,ерительной технике и может быть использовано для автоматического кон троля параметров объектов с переменными параметрами.

. Цель изобретения - повьш1ение помехоустойчивости.

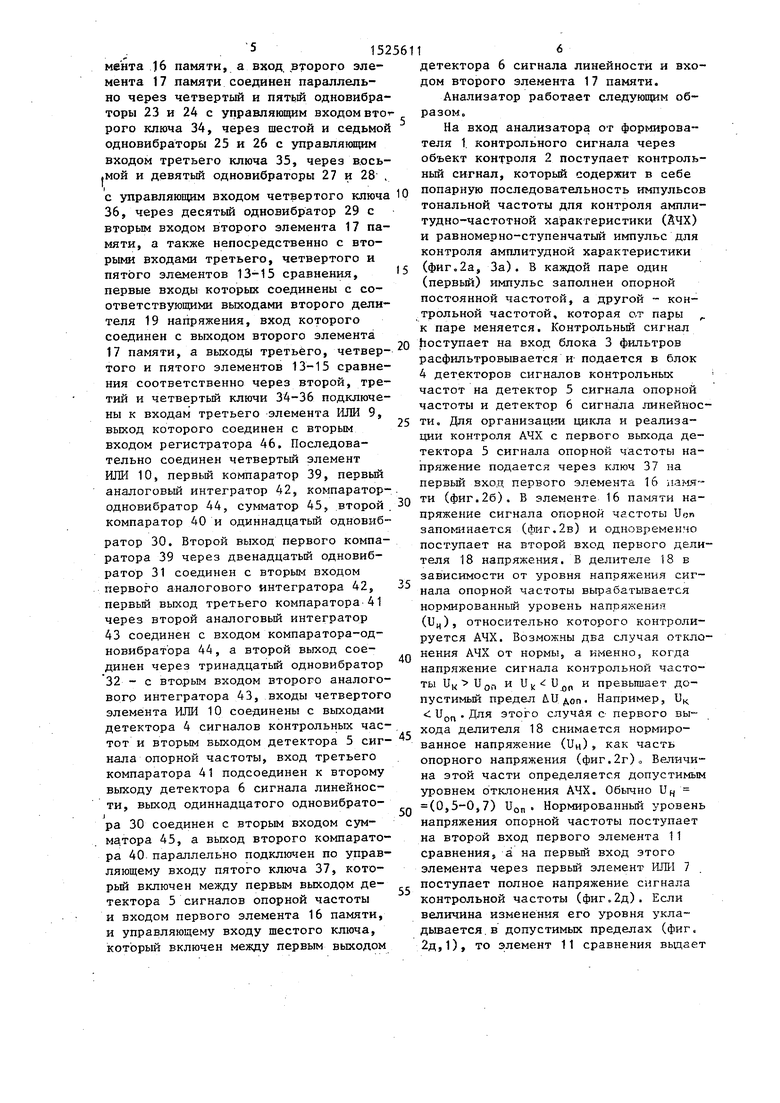

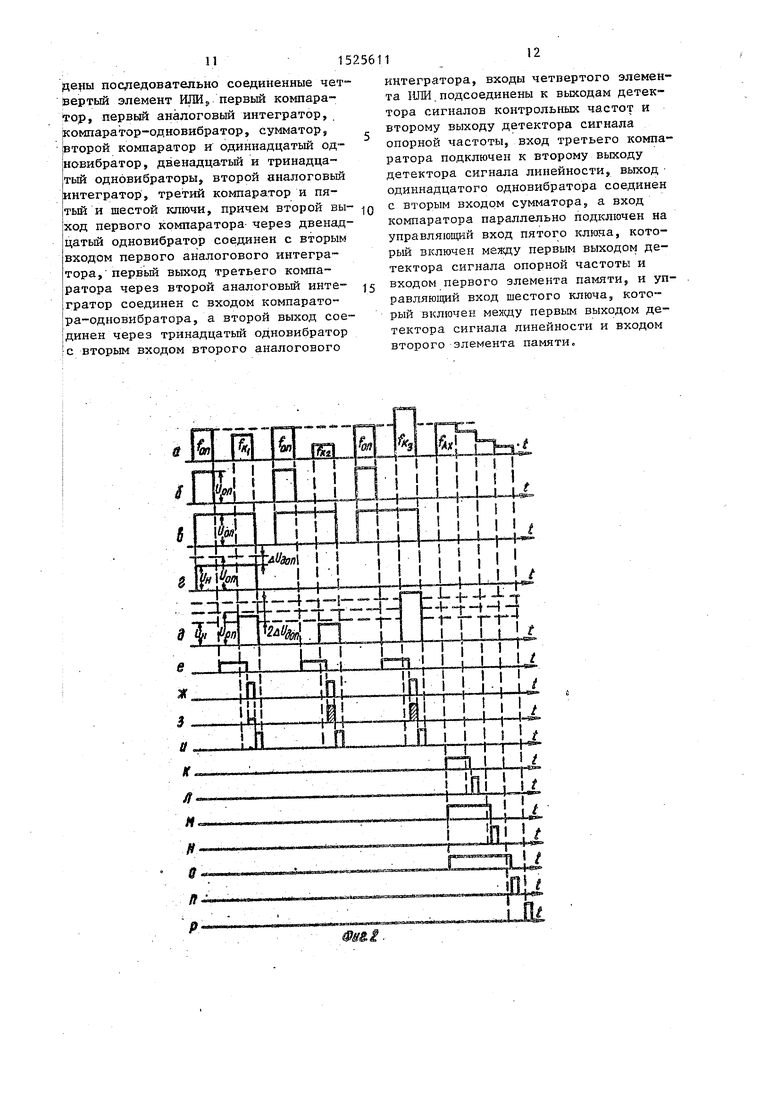

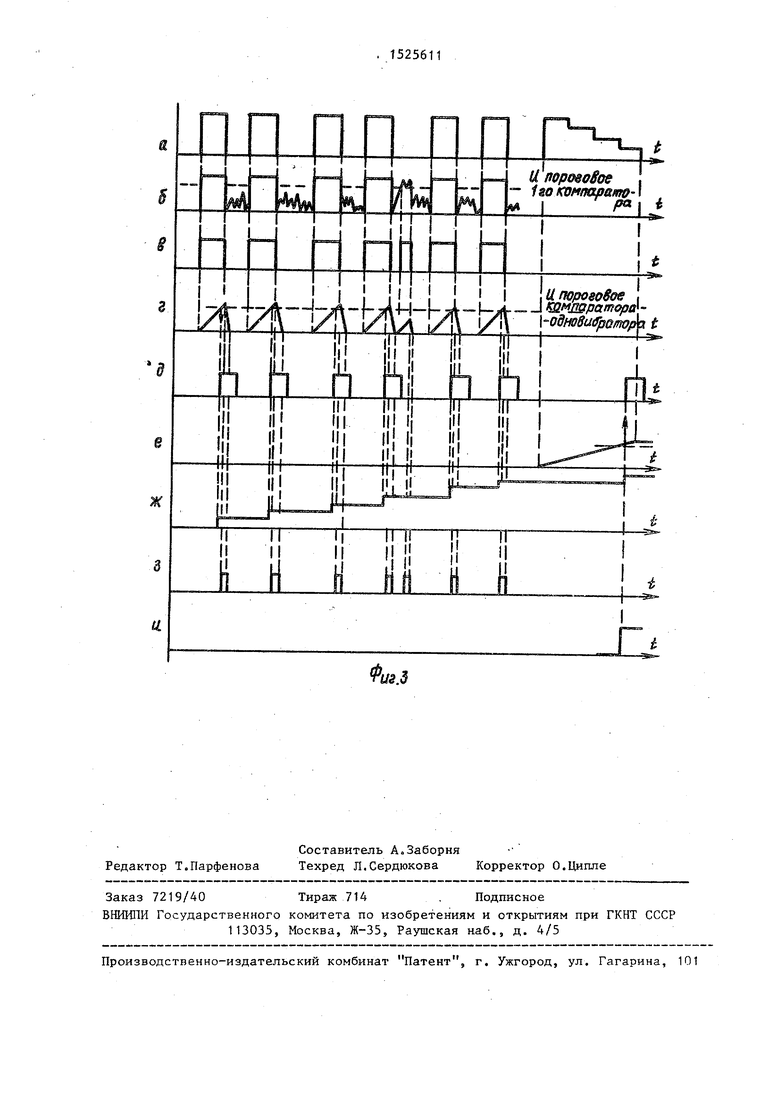

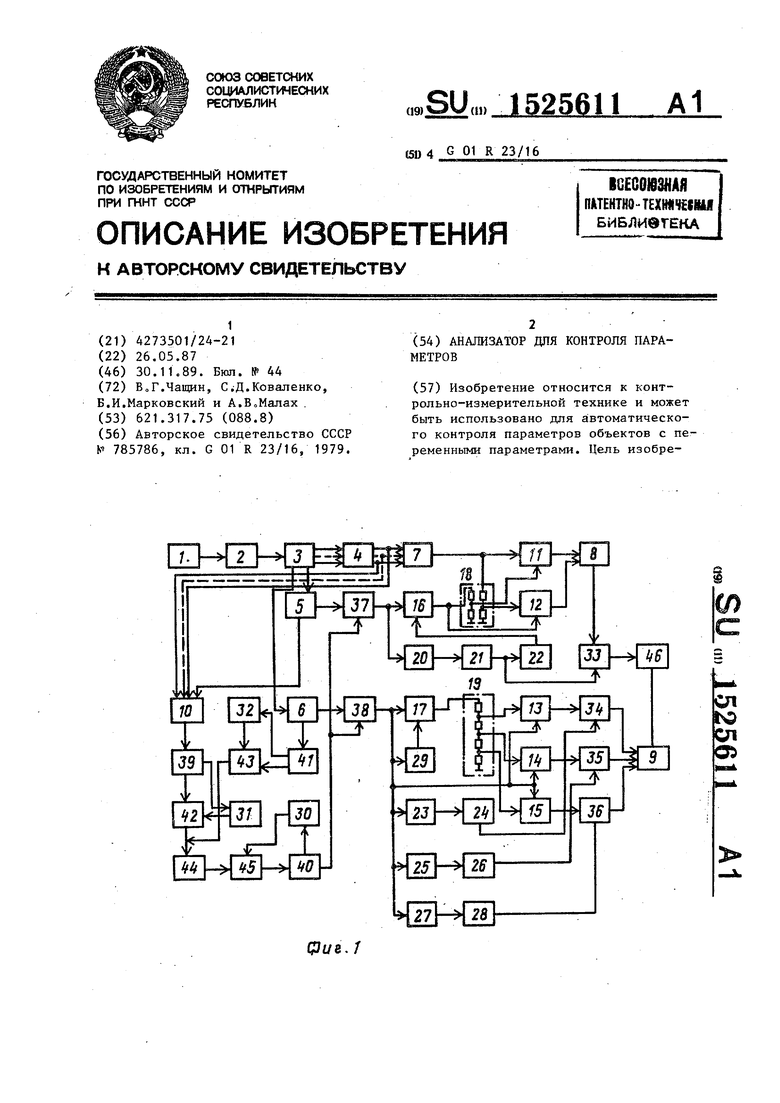

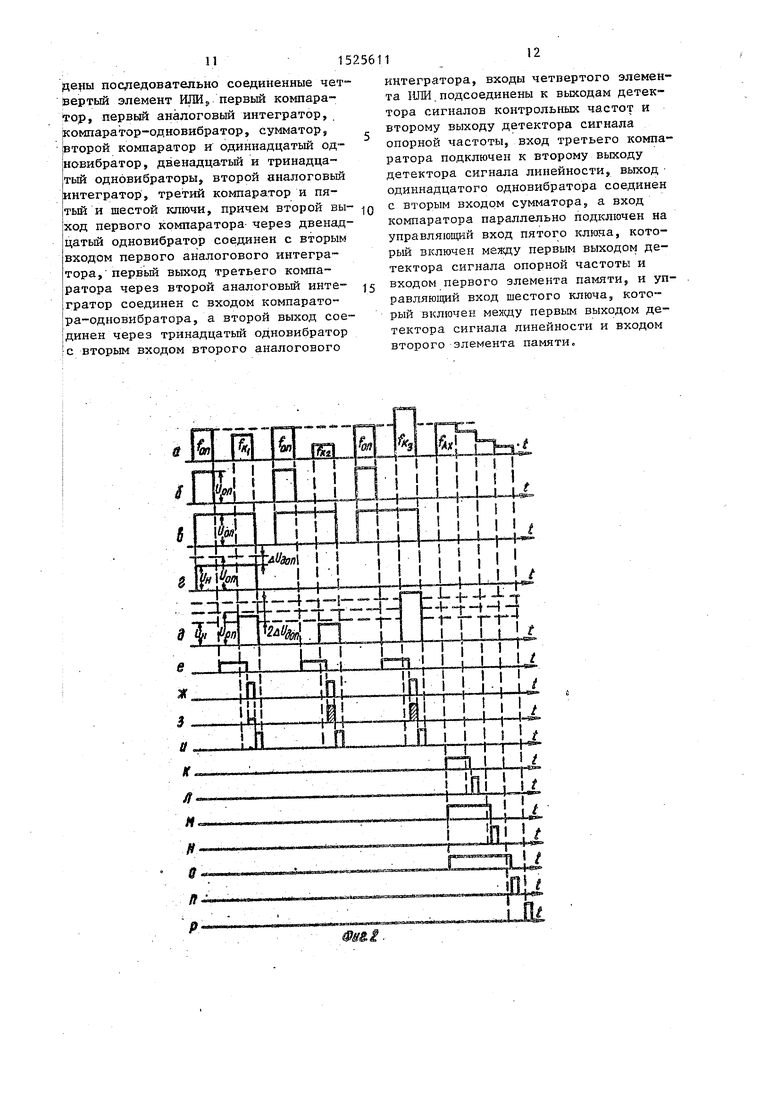

На фиг.1. приведена структурная схема предлагаемого устройства; на фиг.2 и 3 - диаграммы работы устрой- ства.

Анализатор для контроля параметров содержит формирователь 1 контрольного сигнала, объект 2 контроля, блок 3 фильтров, детектор 4 сигналов кон- трольньк частот, детектор 5 сигнала опорной частоты, детектор 6 сигнала линейности, элементы ИЛИ 7-10, элементы 11-15 сравнения, элементы 16 и 17 памяти, делители 18 и 19 напряжения, одновибраторы 20-32, ключи 33-38 компараторы 39-41, аналоговые интеграторы 42 и 43, компаратор-одновиб- ратор 44, сумматор 45, регистратор 46

Формирователь 1 контрольногб СИГ-N нала подключен к входу объекта 2 кон- троля, вход блока 3 фильтров подключен к выходу объекта 2 контроля, а первьм выход соединен с входом детек5

„

г

тора 6 сигнала линейности, второй выход соединен с входом детектора 5 сигнала опорной частоты, а выходы кон трольных частот - с последовательно соединенными детектором 4 сигналов контрольных частот и первым элементом ИЛИ 7, выход которого соединен

.параллельно через последовательно соединенные первый элемент 11 сравнения, второй элемент ИЛИ 8 и .первьй ключ 33 с первым входом регистратора 46 и с первым входом первого делителя 18 напряжения, на второй вход которого подключены параллельно вьпсод первого, элемента 16 памяти и первьй вход второго элемента. 12 сравнения, а первый и второй выходы первого делителя 18 напряжения подключены соответственно на вторые входы первого и второго элементов 11 и 12 сравнения, выход которого подключен на второй вход второго элемента Ш(Е 8, вход первого элемента 16 памяти соединен через первый одновибратор 20 с входом второго одновибратора 21, выход которого соединен параллельно с управляющим входом первого ключа 33 и с входом третьего одновибратора 22, выход которого подключен на второй вход эле

. 515

мента 16 памяти, а вход второго элемента 17 памяти соединен параллельно через четвертый и одновибра- торы 23 и 24 с управляющим входом вто рого ключа 34, через шестой и седьмой одновибраторы 25 и 26 с управлякнцим входом третьего ключа 35, через в.ось- .мой и девятый одновибраторы 27 и 28 ,

с управляющим входом четвертого ключа 36, через десятый одновибратор 29 с вторым входом второго элемента 17 памяти, а также непосредственно с вторыми входами третьего, четвертого к пятого элементов 13-15 сравнения, первые входы которых соединены с соответствующими выходами второго делителя 19 напряжения, вход которого соединен с выходом второго элемента 17 памяти, а выходы третьего, четвер- того и пятого элементов 13-15 сравнения соответственно через второй, третий и четвертый ключи 34-36 подключены к входам третьего элемента ИЛИ 9, выход которого соединен с вторым входом регистратора 46, Последовательно соединен четвертый элемент ИЛИ 10, первый компаратор 39, первый аналоговый интегратор 42, компаратородновибратор 44, сумматор 45,, второй компаратор 40 и одиннадцатьш одновибратор 30. Второй выход первого компаратора 39 через двенадцатый одновибратор 31 соединен с вторым входом первого аналогового интегратора 42, первый выход третьего компаратора 41 через второй аналоговый интегратор 43 соединен с входом компаратора-од- новибратора 44, а второй выход соединен через тринадцатьй одновибратор 32 - с вторым входом второго аналогового интегратора 43, входы четвертого элемента ИЛИ 10 соединены с вьпх.одами детектора 4 сигналов контрольных частот и вторым выходом детектора 5 сиг- нала опорной частоты, вход третьего компаратора 41 подсоединен к второму выходу детектора 6 сигнала линейности, выход одиннадцатого одновибратора 30 соединен с вторым входом сум- ма.тора 45, а выход второго компаратора 40 параллельно подключен по управляющему входу пятого ключа 37, который включен между первым выходом де- тектора 5 сигналов опорной частоты и входом первого элемента 16 памяти, и управляющему входу шестого ключа, который включен между первым выходом

5

61

5 0 5

0

16

детектора 6 сигнала линейности и входом второго элемента 17 памяти.

Анализатор работает следующим образом.

На вход анализатора от формирователя 1. контрольного сигнала через объект контроля 2 поступает контроль- ньй сигнал, который содержит в себе попарную последовательность импульсов тональной частоты для контроля амплитудно-частотной характеристики (ЙЧХ) и равномерно-ступенчатый импульс для контроля амплитудной характеристики (фиг.2а. За). В каждой паре один (первый) импульс заполнен опорной постоянной частотой, а другой контрольной частотой, которая о,т пары к паре меняется. Контрольный сигнал Поступает на вход блока 3 фильтров расфильтровывается и подается в блок 4 детекторов сигналов контрольных частот на детектор 5 сигнала опорной частоты и детектор 6 сигнала линейности. Для организации цикла и реализации контроля АЧХ с первого выхода детектора 5 сигнала опорной частоты напряжение подается через ключ 37 на первый вход первого элемента 16 ти (фиг.2б). В элементе 16 памяти напряжение сигнала опорной частоты Поп запоминается (фиг.2в) и одновременчо поступает на второй вход первого делителя 18 напряжения. В делителе 18 в зависимости от уровня напряжения сигнала опорной частоты вырабатывается нормированный уровень напряжения (и,), относительно которого контролируется АЧХ. Возможны два случая отклонения АЧХ от нормы, а именно, когда напряжение сигнала контрольной частоты UK UQ,-, и U, i и превьпиает допустимый предел Д.идоп. Например, U Up . Для этого случая с первого выхода делителя 18 снимается нормированное напряжение (UH), как часть опорного напряжения (фиг.2г)о Величина этой части определяется допустимым уровнем отклонения АЧХ. Обычно V (0,5-0,7) UQ, Нормированньш уровень напряжения опорной частоты поступает на второй вход первого элемента 11 сравнения, а на первьй вход этого элемента через первьй элемент ИЛИ 7 поступает полное напряжение сигнала контрольной частоты (фиг.2д). Если величина изменения его уровня укладывается, в допустимых пределах (фиг. 2д,1), то элемент 11 сравнения вьщает

715

сигнал Норма. Если напряжение сигнала контрольной частоты меньше нормированного уровня (фиг.2д,2), т.е. изменилось на величину больше, чем допустимо, то на выходе блока сравнения сигнал Не норма Для случая, когда и (J V Ujjj, , работает второй эле- ме;нт 12. сравнения. На один его вход . в качестве нормированного уровня по- дается полное напряжение опорной частоты, а на другой вход - часть напряжения контрольной частоты. Если часть напряжения контрольной частоты превы - сит полное напряжение опорной часто- ты (фиг.2д,3), на вЬгходе элемента 12 сравнения возникает сигнал Не годен . Сигналы с выходов элементов 11 и 12 сравнения через второй элемент ИЛИ 8 подаются на вход первого ключа 33. В определенный момент времени ключ по управляющему входу открывается, и результат сравнения напряжений поступает в регистратор 46. Управление работой тракта контроля АЧХ (ключом 33) осуществляется когерент- ными сигналами от схемы управления,- в которую входят первый 20, второй 21 н третий 22 одновибраторы. Первый одновибратор 20 запускается от задне го фронта импульса напряжения сигнала опорной частоты и определяет мо мент начала сравнения напряжений опорной и контрольной частот (фиг.2е) Второй.одновибратор 21 запускается задним фронтом импульса одновибратора 20 и вьфабатывает импульс, которьш определяет .длительность процесса сравнения, открывая на это время по управляющему входу ключ 33 (фиг„2ж)о Третий одновибратор 22 запускается задним фронтом импульса одновибратора 21 и вырабатьшает импульс (фиг. 2и) который освобождает элемент 16 памяти от напряжения.сигнала опорной час- тоты, подготавливая его к контролю уровня следующей пары частот контрольного сигнала.

Для организации цикла и реализации контроля амплитудной характерис- тики с выхода детектора 6 сигнала линейности огибающая контрольного сигнала через шестой ключ 38 поступает на первьш вход второго элемента

17 памяти и на входы элементов 13-15 сравнения. В. элементе 17 памяти определяется величина первой максималь.. ной ступеньки контрольного напряжения и сохраняется на весь цикл контроля. Это напряжение делится равномерно на долевые части в линейном делителе 19 напряжения, вырабатьшая как бы зталонньш сигнал по равномерности характеристики. Количество частей определяется количеством ступенек контрольного сигнала. С выходов делителя 19 напряжение поступает на другие входы элементов 13-15 сравнения. Таким образом, на одних входах элементов сравнения постоянно присутствуют напряжения ступенек квазиэталонного напряжения, а на других входах - напряжения ступенек непосредственно с выхода детектора с -Результат сравнения через ключи 34-36 и третий элемент ИЛИ 9 поступает на регистратор 46 (фиг.2з). Когерентность работы элементов устройства обеспечивается определенной последовательностью синхронных импульсов, поступающих из схемы управления. С этрй целью напряжение с первого выхода детектора 6 поступает параллельно как на элемент 17 памяти, так и на вход одновибратора 23, 25 и 27, кото рые запускаются и вырабатывают напряжение (фиг.2 к,м,о), определяющее последовательность и момент пробы результатов срав.нения каждой ступеньки напряжения. Задним фронтом эти одновибраторы запускают одновибраторы 24, 26 и 28, которые управляют ключами 34-36 и т.д. и определяют временную продолжительность пробы ,(фиГо2 л,н,п).. По окончании контрольного напряжения запускается одновибратор 29 и вырабатывает ш«1Пульс (фиг,2 р), который, освобождает элемент от контрольного напряжения и подготавливает его к слудующему циклу.

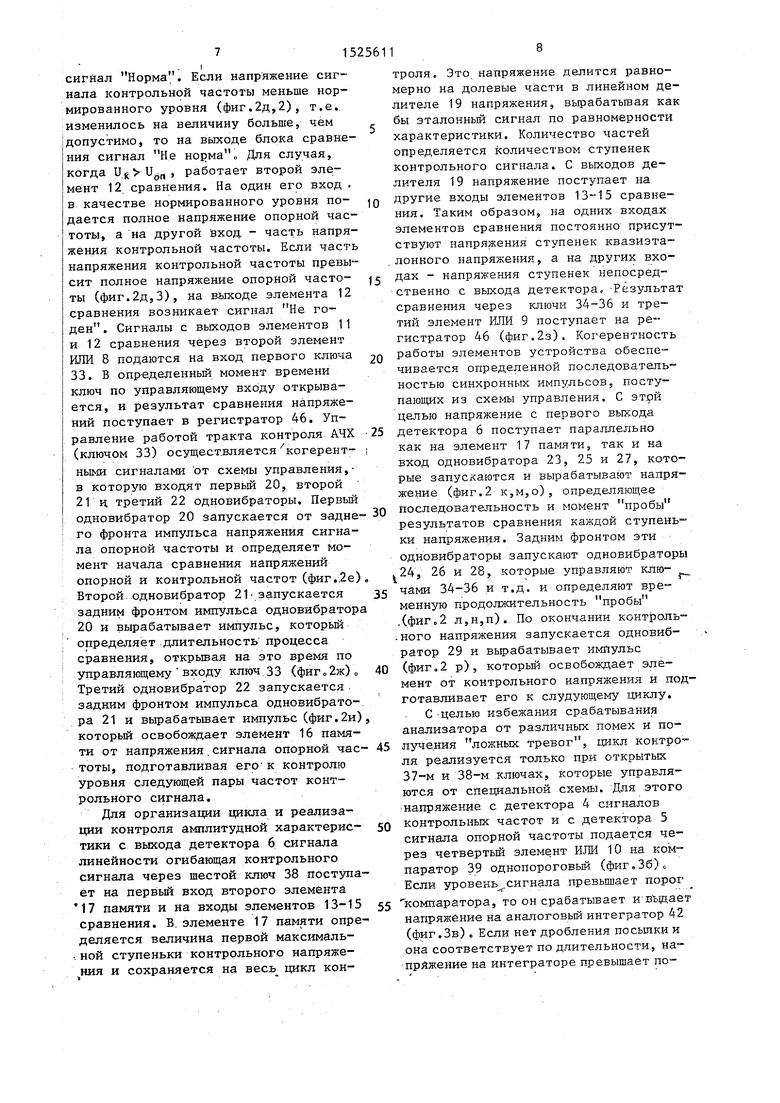

С Целью избежания срабатывания анализатора от различных помех и получения ложных тревог, цикл контро ля реализуется только при открытых 37-м и 38-м .ключах, которые управляются от специальной схемы. Для этого напряжение с детектора 4 сигналов контрольных: частот и с детектора 5 сигнала опорной частоты подает.ся через четвертьш элемент ИЖ 10 на компаратор 39 однопороговьй (фиг.36)о Если уровень сигнала превьЕпает порог компаратора, то он срабатывает И выдает напряжение на аналоговьй интегратор 42 (фиг.Зв). Если нет дробления посылки и она соответствует по длительности, на- прйжение на интеграторе превышает порог срабатывания (фиг.Зг) компаратора- одновибратора 44, который выдает импульс определенной длительности (фиг.Зд) в сумматор 45 (фиг.Зж). По окончании контрольной посьшки компаратор 39 возвращается в исходное состояние и задним фронтом запускает одновиб- ратор 31 (фиг.Зз), который выдает импульс, освобождающий аналоговьй ин- тегратор 42 от напряжения и- подготавливающий его к анализу следующей посьшки. Таким образом обрабатывается каждая посылка опорной и контрольных частот. Многоступенчатая посьтка сиг- нала линейности обрабатывается аналогичным образом с использованием компаратора 41 одновибратора 32 и аналогового интегратора 43 (фиг.Зе). При положительном решении по резуль- татам всех посьшок напряжение на сумматоре возрастает до определенного уровня, при котором срабатывает компаратор 40 однопороговый (фиг.Зи) и открывает ключи 37 и 38. Начинается процесс контроля. Если на входе анализатора имеются какие-то кратковременные выбросы помех либо контрольные посьшки искажены (дробление, преобла- дание), то интеграторы закорачиваются (фиг.3,1)5 не оказывая воздействия в конечном итоге на сумматор, а анализатор для контроля остается закрытым. Постоянная времени сумматора выбирается из расчета, что если на входе анализатора отсутствует конт- рольньш сигнал больше, чем полпериода, то срабатывает компаратор 40, закрывает анализатор и возвращает сумматор в исходное состояние, освобож- пая от напряжения через одновибра- тор 30.

Использование предлагаемого анализатора при эксплуатации автоматизированных радиолиний, трактов и тех- нических средств с переменными параметрами позволяет повысить помехоустойчивость, практически исключить сигналы ложных тревог, следовательно повысить достоверность контроля и надежность связи либо эффективность профилактических и экспериментальных работ.,

Формула изобретения

Анализатор для контроля параметров-, содержащий формирователь контрольного сигнала, выход которого соединен с клеммой для подключения входа объекта контроля, блок фильтров, вход которого соединен клеммой для подключения выхода объекта контроля, а первый выход соединен с входом детектора сигнала линейности, второй выход соединен с входом детектора сигнала опорной частоты, а выходы контрольных частот с последовательно соединенными детектором сигналов контрольных частот и первым элементом ИЛИ, выход которого подключен к первому входу первого делителя напряжения и через последовательно соединенные первый элемент сравнения, второй элемент ИЛИ и первый ключ - с первым входом регистратора, на второй вход первого делителя напряжения подключены вьЬсод первого элемента памяти и первый вход второго элемента сравнения, а первый и вто рой выходы первого делителя напряжения подключены соответственно на вторые входы первого и второго элементов сравнения, выход которого подключен на второй вход второго элемента ИЖ, причем вход первого элемента памяти соединен через первьй одновибратор с входом второго одновибратора, выход которого соединен с управляющим входом первого ключа и с входом третьего одновибратора, выход которого подключен на второй вход первого элемента памяти, а вход второго элемента паг Юти соединен параллельно через четвертый и пятый одновибраторы с управляющим входом второго ключа, чере шестой и седьмой одновибраторы с управляющим входом третьего ключа, через восьмой и девятый одновибраторы с управляющим входом четвертого ключа, через десятый одновибратор с вторым входом второго элемента памяти, а также непосредственно с вторыми входами третьего, четвертого и пятого элементов сравнения, первые входы которых соединены с соответствующими выходами второго делителя напряжения вход которого соединен с выходом второго элемента памяти, а выход третьего, четвертото и пятого элементов сравнения соответственно через второй, третий и четвертый ключи подключены к входам третьего элемента ИЛИ, выход которого соединен с вторым входом регистратора, отличающ и и с я тем, что, с целью повьппе- ния помехоустойчивости, в него ввбдеры посутедовательно соединенные чет- йертьш элемент ШШ первый компара- Фор, первый аналоговый интегратор, |компаратор-одновибратор, сумматор, второй компаратор и одиннадцатый од- новибратор, двенадцатьй и тринадцатый одновибраторыу второй аналоговый интегратор, третий компаратор и пятый и шестой ключи, причем второй выход первого компаратора через двенадцатый одновибратор соединен с вторым входом первого аналогового интегратора, первьш выход третьего компаратора через второй аналоговый интегратор соединен с входом компарато- ра-одновибратора, а второй выход соединен через тринадцатый одновибратор с вторым входом второго аналогового

интегратора, входы четвертого элемента ШШ, подсоединены к выходам детектора сигналов контрольных частот и второму выходу детектора сигнала опорной частоты, вход третьего компаратора подключен к второму выходу детектора сигнала линейности, выход одиннадцатого одновибратора соединен

с вторым входом сумматора, а вход компаратора параллельно подключен на управляющий вход пятого клюна, кото- рьш включен меязду первым выходом детектора сигнала опорной частоты и

входом первого элемента памяти, и управляющий вход шестого ключа, который включен меясду первым выходом детектора сигнала линейности и входом второго элемента памяти.

| Анализатор для контроля параметров радиоэлектронной аппаратуры | 1979 |

|

SU785786A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-11-30—Публикация

1987-05-26—Подача