Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматической настройки режимов питания оптически управляемых транспорантов.

Цель изобретения - повышение быстродействия и точности путем реализации практически мгновенного возвращения в точку глобального экстремума с учетом инерционности измерительно-преобразовательного канала как в режиме поиска, так и в режиме подстройки на глобальный экстремум.

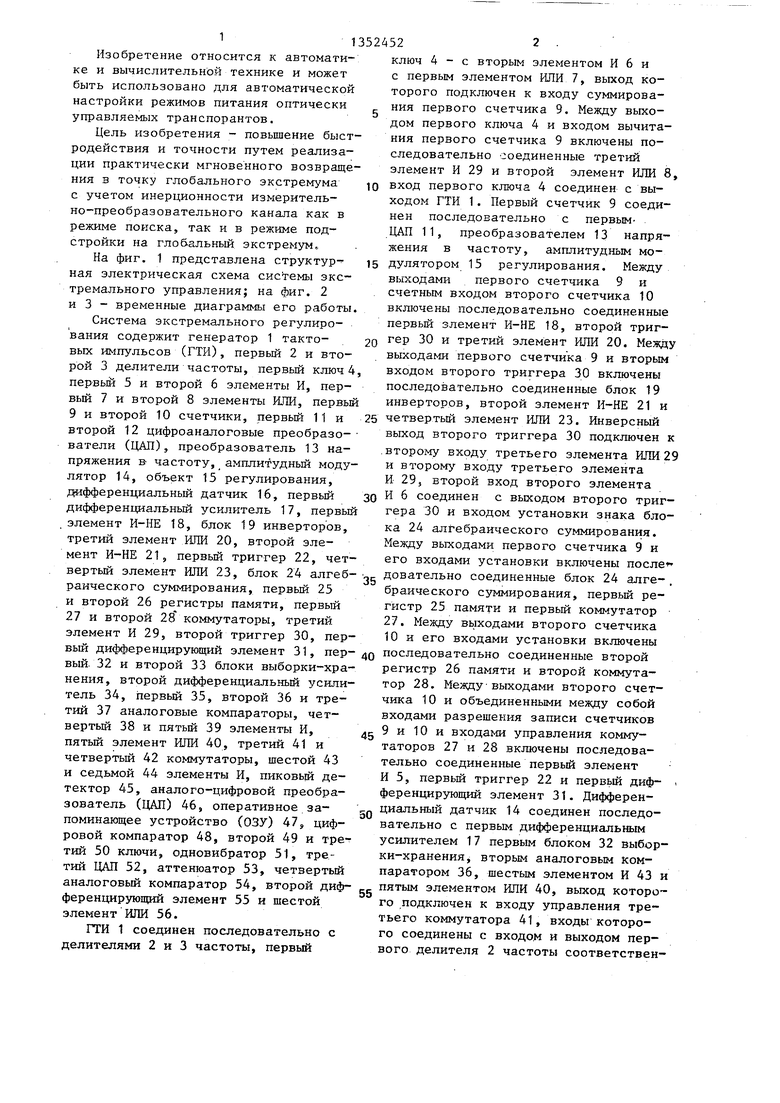

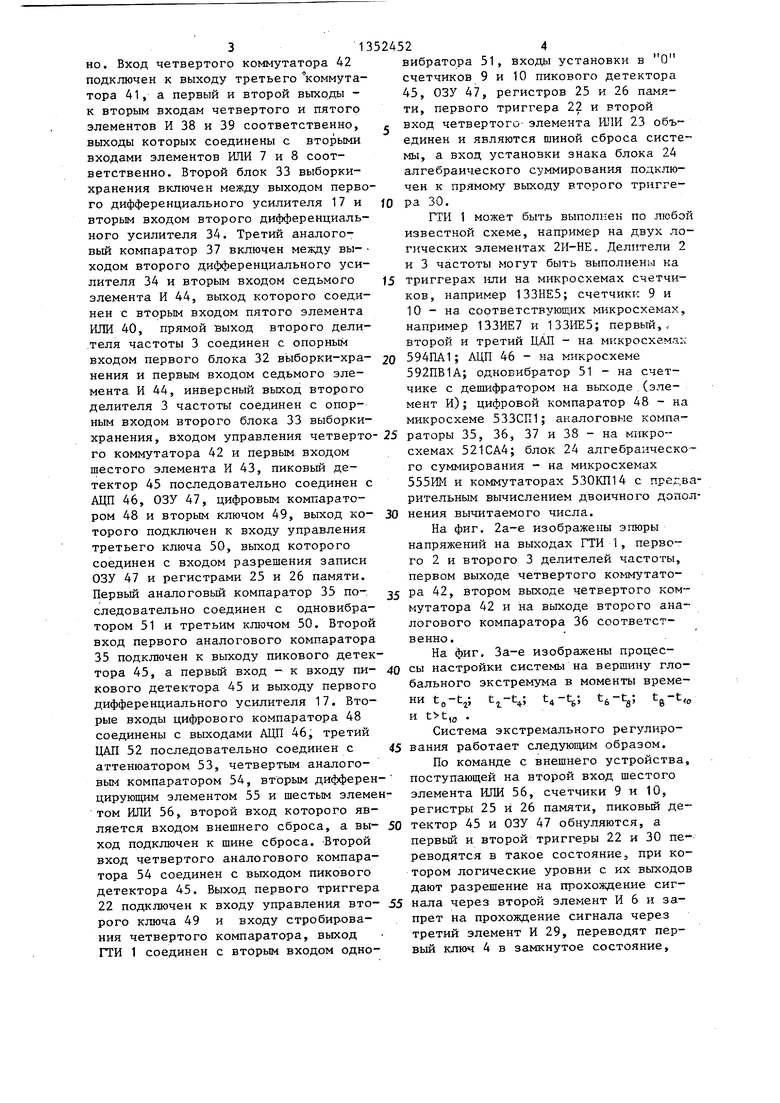

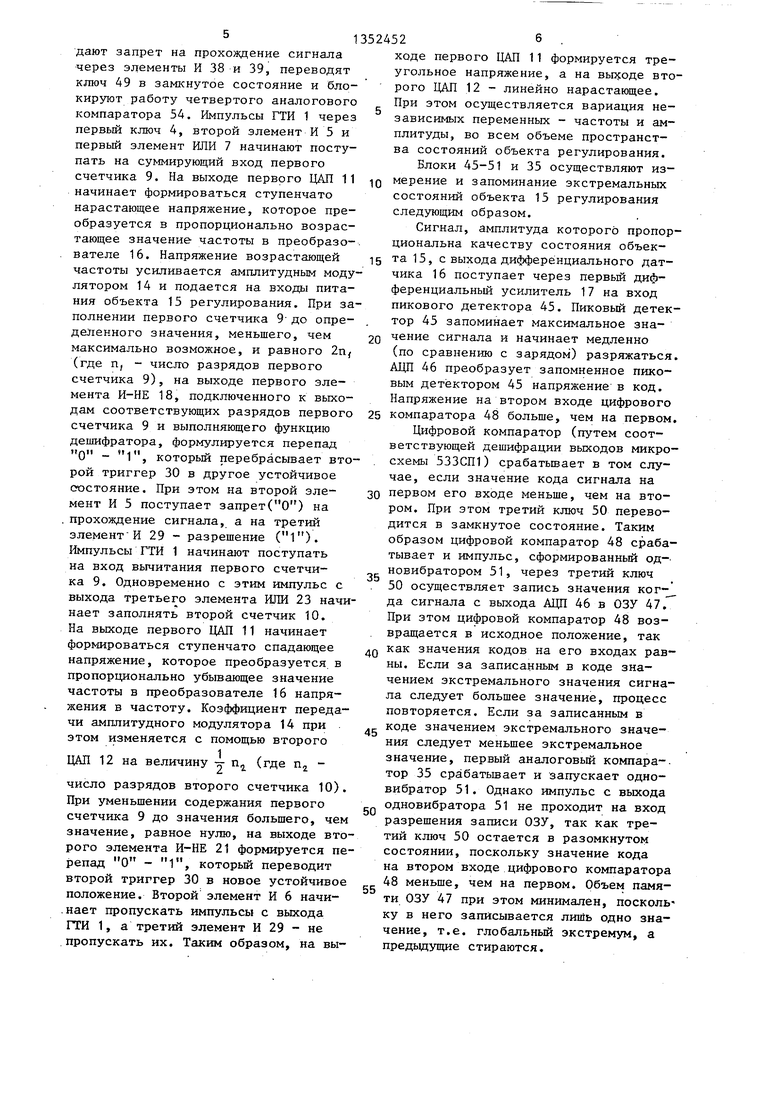

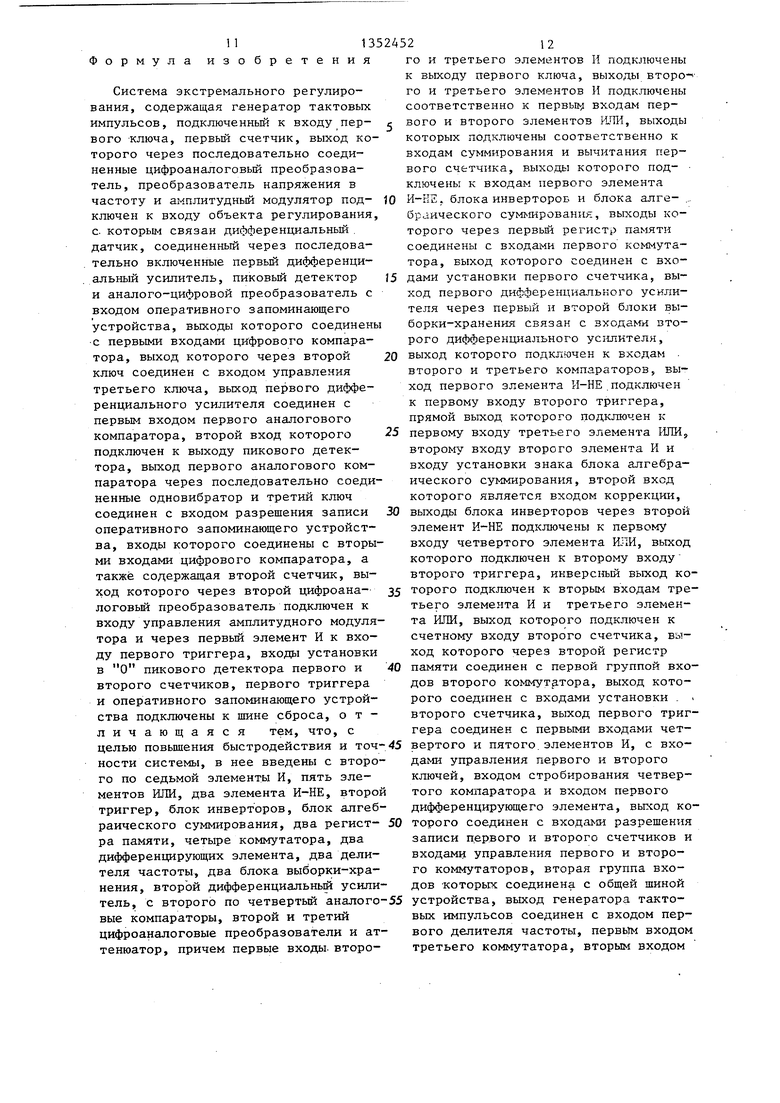

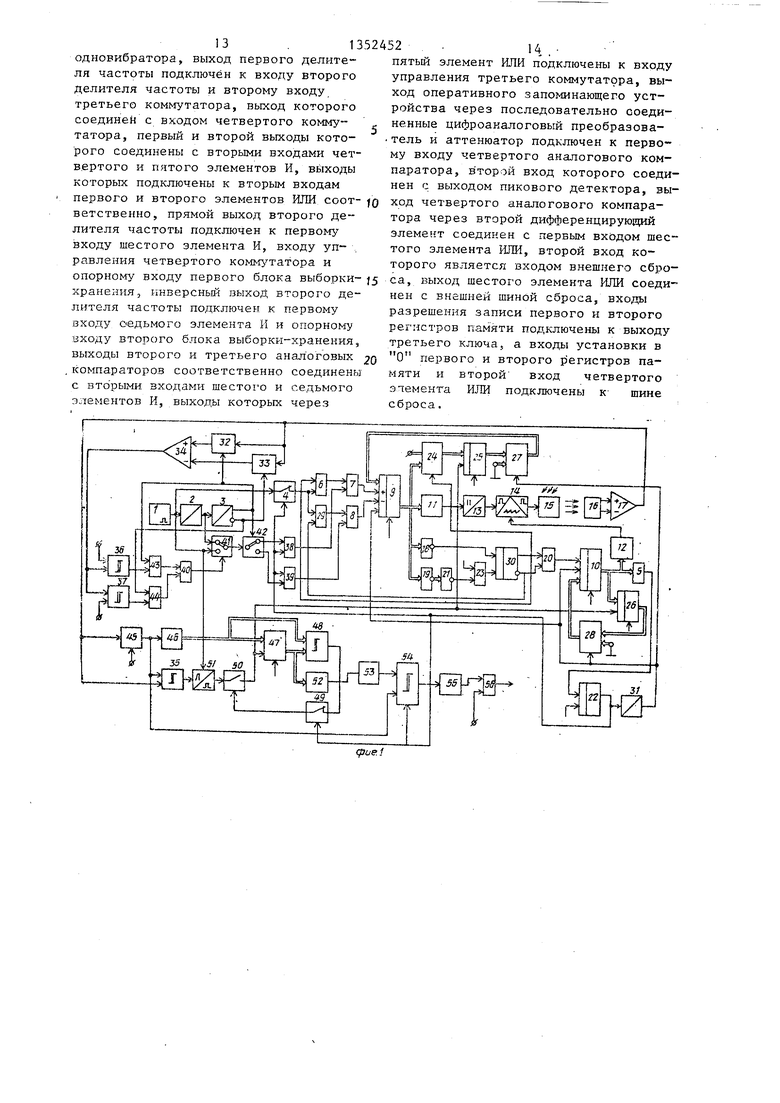

На фиг. 1 представлена структурная электрическая схема системы экстремального управления; на фиг. 2 и 3 - временные диаграммы его работы.

Система экстремального регулирования содержит генератор 1 тактовых импульсов (ГТИ), первый 2 и второй 3 делители частоты, первьй ключ 4 первьш 5 и второй 6 элементы И, первый 7 и второй 8 элементы ИЛИ, первьй 9 и второй 10 счетчики, первый 11 и второй 12 цифроаналоговые преобразо- ватели (ЦАП), преобразователь 13 напряжения в- частоту, амплитудный модулятор 14, объект 15 регулирования, да1фференциальньш датчик 16, первый дифференциальный усилитель 17, первый .элемент И-НЕ 18, блок 19 инверторов, третий элемент ИЛИ 20, второй элемент И-НЕ 21, первый триггер 22, четвертый элемент ИЛИ 23, блок 24 алгеб- -ц довательно соединенные блок 24 алге-. раического суммирования, первьй 25 браического суг мирования, первьй ре- и второй 26 регистры памяти, первый гистр 25 памяти и первьй коммутатор 27 и второй 28 коммутаторы, третий 27. Между выходами второго счетчика элемент И 29, второй триггер 30, пер- 10 и его входами установки включены вый дифференцирующий элемент 31, пер- 40 последовательно соединенные второй вый 32 и второй 33 блоки выборки-хра- регистр 26 памяти и второй коммута-

нения, второй дифференциальный усилитель 34, первый 35, второй 36 и третий 37 аналоговые компараторы, четвертьй 38 и пятьй 39 элементы И, пятьй элемент ИЛИ 40, третий 41 и четвертый 42 коммутаторы, шестой 43 и седьмой 44 элементы И, пиковьй детектор 45, аналого-цифровой преобразователь (ЦАП) 46, оперативное запоминающее устройство (ОЗУ) 47, цифровой компаратор 48, второй 49 и третий 50 ключи, одновибратор 51, третий ЦАП 52, аттенюатор 53, четвертьй аналоговый компаратор 54, второй дифференцирующий элемент 55 и шестой элемент ИЛИ 56.

ГТИ 1 соединен последовательно с делителями 2 и 3 частоты, первый

ключ 4 - с вторым элементом И 6 и с первым элементом ИЛИ 7, выход которого подключен к входу суммирования первого счетчика 9. Между выходом первого ключа 4 и входом вычитания первого счетчика 9 включены последовательно соединенные третий элемент И 29 и второй элемент ИЛИ 8,

вход первого ключа 4 соединен с выходом ГТИ 1. Первый счетчик 9 соединен последовательно с первым . ЦАП 11, преобразователем 13 напряжения в частоту, амплитудным модулятором 15 регулирования. Между выходами первого счетчика 9 и счетным входом второго счетчика 10 включены последовательно соединенные первьй элемент И-НЕ 18, второй триггер 30 и третий элемент ИЛИ 20. Между выходами первого счетчика 9 и вторым входом второго триггера 30 включены последовательно соединенные блок 19 инверторов, второй элемент И-НЕ 21 и

четвертьй элемент ИЛИ 23. Инверсный выход второго триггера 30 подключен к

.второму входу третьего элемента ИЛИ 29 и второму входу третьего элемента И 29, второй вход второго элемента И 6 соединен с выходом второго триггера 30 и входом установки знака блока 24 алгебраического суммирования. Между выходами первого счетчика 9 и его входами установки включены после тор 28. Междувыходами второго счетчика 10 и объединенными между собой входами разрешения записи счетчиков g 9 и 10 и входами управления коммутаторов 27 и 28 включены последовательно соединенные первьй элемент И 5, первьй триггер 22 и первьй дифференцирующий элемент 31. Дифференциальный датчик 14 соединен последовательно с первым дифференциальным усилителем 17 первым блоком 32 выборки-хранения, вторым аналоговьм Компаратором 36, шестым элементом И 43 и пятым элементом ИЛИ 40, выход которого подключен к входу управления третьего коммутатора 41, входы которого соединены с входом и выходом первого делителя 2 частоты соответствен0

но. Вход четвертого коммутатора 42 подключен к выходу третьего коммутатора 41, а первый и второй выходы - к вторым входам четвертого и пятого элементов И 38 и 39 соответственно, выходы которых соединены с вторыми входами элементов ИЛИ 7 и 8 соответственно. Второй блок 33 выборки- хранения включен между выходом первого дифференциального усилителя 17 и вторым входом второго дифференциального усилителя 34. Третий аналоговый компаратор 37 включен между вы- ходом второго дифференциального усилителя 34 и вторым входом седьмого элемента И 44, выход которого соединен с вторым входом пятого элемента ИЛИ 40, прямой выход второго дели- .теля частоты 3 соединен с опорным входом первого блока 32 выборки-хра- нения и первым входом седьмого элемента И 44, инверсный выход второго делителя 3 частоты соединен с опорным входом второго блока 33 выборки- хранения, входом управления четверто го коммутатора 42 и первым входом шестого элемента И 43, пиковый детектор 45 последовательно соединен с АЦП 46, ОЗУ 47, цифровым компаратором 48 и вторым ключом 49, выход ко- торого подключен к входу управления третьего ключа 50, выход которого соединен с входом разрешения записи ОЗУ 47 и регистрами 25 и 26 памяти. Первый аналоговый компаратор 35 по- следовательно соединен с одновибра- тором 51 и третьим ключом 50. Второй вход первого аналогового компаратора 35 подключен к выходу пикового детектора 45, а первый вход - к входу пи- кового детектора 45 и выходу первого дифференциального усилителя 17. Вторые входы цифрового компаратора 48 соединены с выходами АЦП 46, третий ЦАЦ 52 последовательно соединен с аттенюатором 53, четвертым аналоговым компаратором 54, вторым дифферен цирующим элементом 55 и шестым элеметом ИЛИ 56, второй вход которого является входом внешнего сброса, а вы- ход подключен к шине сброса. Второй вход четвертого аналогового компаратора 54 соединен с выходом пикового детектора 45. Выход первого триггера 22 подключен к входу управления вто- рого ключа 49 и входу стробирова- ния четвертого компаратора, выход ГТИ 1 соединен с вторым входом одновибратора 51, входы установки в О счетчиков 9 и 10 пикового детектора 45, ОЗУ 47, регистров 25 и 26 памяти, первого триггера 22 и второй вход четвертого- элемента ИЛИ 23 объединен и являются шиной сброса системы, а вход установки знака блока 24 алгебраического суммирования подключен к прямому выходу второго триггера 30.

ГТИ 1 может быть выполнен по любо известной схеме, например на двух логических элементах 2И-НЕ, Делители 2 и 3 частоты могут быть выполнены на триггерах Iiли на микросхемах счетчиков, например 133НЕ5; счетчики 9 и 10 - на, соответствующих микросхемах, например 133ИЕ7 и 133ИЕ5; первый,.- второй и третий ЦАП - на микросхемах 594ПА1; АЦП 46 - на микросхеме 592ПВ1А; одновибратор 51 - на счетчике с дешифратором на выходе (элемент И); цифровой компаратор 48 - на микросхеме 533СП1; аналоговые компараторы 35, 36, 37 и 38 - на микро-схемах 521СА4; блок 24 алгебраического суммирования - на микросхемах 555ИМ и коммутаторах 530КП14 с предврительным вычислением двоичного допонения вычитаемого числа.

На фиг. 2а-е изображены эпюры напряжений на выходах ГТИ 1, первого 2 и второго 3 делителей частоты, первом выходе четвертого коммутатора 42, втором выходе четвертого коммутатора 42 и на выходе второго аналогового компаратора 36 соответственно.

На фиг, За-е изображены процессы настройки системы на вершину глобального экстремума в моменты времени to-ц; tg-t, и ,o .

Система экстремального регулирования работает следующим образом.

По команде с внешнего устройства, поступающей на второй вход шестого элемента ИЛИ 56, счетчики 9 и 10, регистры 25 и 26 памяти, пиковый детектор 45 и ОЗУ 47 обнуляются, а первый и второй триггеры 22 и 30 пе- реводятся в такое состояние, при котором логические уровни с их выходов дают разрешение на прохождение сигнала через второй элемент И 6 и запрет на прохождение сигнала через третий элемент И 29, переводят первый ключ 4 в замкнутое состояние.

дают запрет на прохождение сигнала через элементы И 38 и 39, переводят ключ 49 в замкнутое состояние и блокируют работу четвертого аналогового компаратора 54. Импульсы ГТИ 1 через первый ключ 4, второй элемент И 5 и первый элемент ИЛИ 7 начинают поступать на суммирующий вход первого счетчика 9. На выходе первого ЦАП 11 начинает формироваться ступенчато нарастающее напряжение, которое преобразуется в пропорционально возрастающее значение частоты в преобразователе 16. Напряжение возрастающей частоты усиливается амплитудным модулятором 14 и подается на входы питания объекта 15 регулирования. При заполнении первого счетчика 9 до определенного значения, меньшего, чем максимально возможное, и равного 2п, (где п, - число разрядов первого счетчика 9), на выходе первого элемента И-НЕ 18, подключенного к выходам соответствующих разрядов первого счетчика 9 и выполняющего функцию дешифратора, формулируется перепад О - 1, которьй перебрасывает второй триггер 30 в другое устойчивое состояние. При этом на второй элемент И 5 поступает запрет(0) на прохождение сигнала, а на третий элемент И 29 - разрешение (1). Импульсы ГТИ 1 начинают поступать на вход вычитания первого счетчика 9. Одновременно с этим импульс с выхода третьего элемента ИЛИ 23 начинает заполнять второй счетчик 10, На выходе первого ЦАП 11 начинает формироваться ступенчато спадающее напряжение, которое преобразуется, в пропорционально убывающее значение частоты в преобразователе 16 напряжения в частоту. Коэффициент передачи амплитудного модулятора 14 при этом изменяется с помощью второго

ЦАП 12 на величину у п, (где п число разрядов второго счетчика 10). При уменьшении содержания первого счетчика 9 до значения большего, чем значение, равное нулю, на выходе второго элемента И-НЕ 21 формируется пе- 15епад О - 1, который переводит второй триггер 30 в новое устойчивое положение. Второй элемент И 6 начи- нает пропускать импульсы с выхода ГТИ 1, а третий элемент И 29 - не пропускать их. Таким образом, на вы-

10

20

25

3524526 .

ходе первого ЦАП 11 формируется треугольное напряжение, а на выводе второго ДАЛ 12 - линейно нарастающее. При этом осуществляется вариация независимых переменных - частоты и амплитуды, во всем объеме пространства состояний объекта регулирования.

Блоки 45-51 и 35 осуществляют измерение и запоминание экстремальных состояний объекта 15 регулирования следующим образом.

Сигнал, амплитуда которого пропорциональна качеству состояния объек- 15 та 15, с выхода дифференциального датчика 16 поступает через первьш дифференциальный усилитель 17 на вход пикового детектора 45. Пиковый детектор 45 запоминает максимальное значение сигнала и начинает медленно (по сравнению с зарядом) разряжаться. АЦП 46 преобразует запомненное пиковым детектором 45 напряжение в код. Напряжение на втором входе цифрового компаратора 48 больше, чем на первом.

Цифровой компаратор (путем соответствующей дешифрации выходов микросхемы 533СП1) срабатывает в том случае, если значение кода сигнала на первом его входе меньше, чем на втором. При этом третий ключ 50 переводится в замкнутое состояние. Таким образом цифровой компаратор 48 срабатывает и импульс, сформированньй од- новибратором 51, через третий ключ 50 осуществляет запись значения ког- да сигнала с выхода АЦП 46 в ОЗУ 47. При этом цифровой компаратор 48 возвращается в исходное положение, так как значения кодов на его входах равны. Если за записанным в коде значением экстремального значения сигнала следует большее значение, процесс повторяется. Если за записанным в коде значением экстремального значения следует меньшее экстремальное значение, первый аналоговый компара-. тор 35 срабатьшает и запускает одно- вибратор 51. Однако импульс с выхода одновибратора 51 не проходит на вход разрешения записи ОЗУ, так как третий ключ 50 остается в разомкнутом состоянии, поскольку значение кода на втором входе цифрового компаратора 48 меньше, чем на первом. Объем памяти ОЗУ 47 при этом минимален, посколь ку в него записывается лийь одно значение, т.е. глобальный экстремум, а предьщущие стираются.

30

35

40

45

50

55

Пиковый детектор 45 как бы растягивает во времени экстремальное значение сигнала, в результате чего требования к быстродействию АЦП 46 многократно снижаются, что позволяет использовать АЦП, постронные по методу приближения, т.е. с числом разрядов, большим или равным 12, и, следовательно, получить высокую точность.

При прохождении экстремальнь1х, возрастающих по величине значений, импульс записи, поступающий с выход одновибратора 51 на вход разрешения

записи ОЗУ 47, поступает одновремен- J5 вом скате экстремальной характеристино и на входы разрешения записи регистров 25 и 26 памяти. При этом в эти регистры записывается код час- тоты ,и амплитуды, соответствукщий экстремальному значению сигнала. По- сколько импульс на выходе одновибратора 51 формируется через заданное время путем подсчета определенного количества импульсов с выхода ГТИ 1,

поступающих на его второй вход. Это 25 ля 34. Поскольку перед этим был вклюколичество импульсов, переведенное в код, вычитается из кода на выходе первого счетчика 9 с учетом знака, который определяется состоянием на выходе второго триггера 30 с той целью, чтобы при возвращении в заданную точку пространства состояний объекта 15 регулирования попасть на вершину глобального экстремума с учетом инерционности АЦП 46 и одновибратора 51 (фиг. 3).

Возвращение происходит практически мгновенно следующим образом.

При перебрасывании первого триггера 22 на выходе первой дифференцирую-40 щей цепи 31 формируется импульс, который переводит коммутаторы 27 и 28 в такое положение, при котором на их выходы проходят коды сигналов с вычен второй блок 33 выборки-хранения, то в первьш момент времени tg (импульс на фиг. 2г и точка а на фиг. За) напряжения на входах второго дифЛе30 ренциального усилителя 34 равны между собой. При этом коммутаторы 41 и 42 находятся в исходном состоянии (фиг. 1), импульсы с выхода второго делителя 3 частоты (фиг. 2в) удержи35 вают четвертый коммутатор 42 в каж дом состоянии в течение времени

Т

(где Т - период сигнала с выходов

второго делителя 3 частоты).

Таким образом, первый импульс а проходит с выхода второго делителя частоты 2 через коммутаторы 41 и 42 на вход суммирования первого счетчика 9 и увеличивает частоту сигнала ходов первого и второго регистров 25 45 с выхода преобразователя 13. При этом и 26 памяти. Одновременно этот же им- увеличивается напряжение на выходах пульс поступает на входы установки дифференциальных усилителей 17 и 34 счетчиков 9 и 10. При этом в счетчи- (фиг. За, точка в). Второй импульс b ки 9 и 10 производится запись кодов (фиг. 2г), пройдя ту же цепь, еще сигнала с выходов регистров 25 и 26, 50 .больше увеличивает напряжение на выходах дифференциальных усилителей 17 и 34 (фиг. За, точка с). Происходит превьшгение порога срабатывания второго аналогового компаратора 36 (tj ,

а на выходах ДАЛ 11 и 12 формируются значения напряжений сигналов, соответствующих глобальному экстремуму. Если возвращение в точку пространства состояний произошло неточно или 55 фиг. 2е), у которого порог положитель- за время изучения и измерения пара- ный (у третьего аналогового компара- метры объекта 15 регулирования из- тора 37 порог отрицательный (фиг.За), менились, или одна из внешних не- При этом компаратор 36 через шестой

зависимых переменных (например, освещенность) стала изменяться, происходит автоматическая подстройка системы на вершину глобального экстремума следующим образом.

При указанном вьше переключении первого триггера 22 сигнал с его выхода выключает первый ключ 4 и дает разрешение на прохождение сигналов с выходов четвертого коммутатора на входы суммирования и вычитания первого счетчика 9 (фиг. 2),

Предположим, что в исходном поло- женки рабочая точка оказалась на леки (фиг. За, точка i), а напряжение на прямом выходе делителя 3 частоты в ЭТОТ момент времени равно 1 (фиг. 2в). Это приводит к тому, что первый блок 32 выборки-хранения открывается и напряжение с выхода первого дифференциального усилителя 17 поступает на неинвертирующий вход второго дифференциального усилитечен второй блок 33 выборки-хранения, то в первьш момент времени tg (импульс на фиг. 2г и точка а на фиг. За) напряжения на входах второго дифЛеренциального усилителя 34 равны между собой. При этом коммутаторы 41 и 42 находятся в исходном состоянии (фиг. 1), импульсы с выхода второго делителя 3 частоты (фиг. 2в) удерживают четвертый коммутатор 42 в каж дом состоянии в течение времени

Т

(где Т - период сигнала с выходов

элемент И 43 и пятый элемент ИЛИ 40 переводит третий коммутатор 41 в полжение, при котором через него проходят импульсы повышенной частоты непосредственно с выхода ГТИ на вход суммирования первого счетчика 9 (фиг. 2г - импульсы а, Ь, с, d, е, f,, g, h, i). После поступления девятого импульса i состояние выходов второго делителя 3 частоты меняется (фиг. 2в, t, , фиг. 2е). Четвертый коммутатор 42 переходит в состояние, когда его выход подключается к вхо- ду вычитания первого счетчика 9. Включается второй блок 33 выборки- хранения. Поскольку при этом напряже ния на входах дифференциального усилителя 34 равны, компаратор 36 отпускает и третий коммутатор 41 возвращается в исходное состояние. Им- пульсы а,Ь,с (фиг. 2д) увеличивают напряжение на инвертирующем входе второго дифференциального усилителя 34 относительно неинвертирующего входа; опять срабатывает компаратор 36 (t, фиг. 2е), однако напряжение 1 с его выхода не проходит на вход управления третьего коммутатора 41 j так как в это время напряжение на втором входе шестого эле- мента И 43 равно О (фиг. 2в). Таким образом, частота преобразователя 13 уменьшается только на три ступеньки а,Ь,с (фиг. 36). Затем вновь включается первый блок 32 выборки- хранения (t, фиг. 2е) и вновь происходит движение к вершине экстремальной характеристики (фиг. 3с). Однако количество ступеней движения меньше, так как при приближении к. вершине градиент изменения функции уменьшается, а следовательно, большее количество движений необходимо для превьш1ения порога д. срабатьшани компаратора (фиг. 2г,е, фиг. Зв). Затем процесс повторяется до тех пор, пока не будет достигнута верши на экстремальной характеристики (фиг. Зг,д).

Если бы рабочая точка оказалась на правой стороне ската экстремальной характеристики, процесс происходил бы аналогичным образом, с той лишь разницей, что работал бы третий аналоговый компаратор 37, а не второй. Аналогично этому происходит процесс подстройки, если в момент подстройки первый счетчик 9 оказал

ся на отрицательном склоне формируемого треугольного напряжения.

Применение автоматической подстроки режимов питания объекта регулирования в сочетании с использованием блоков выборки-хранения повьшгает быстродействие подстройки при абсолютной устойчивости, так как обратная связь во время подстройки в контуре регулирования разорвана и, как следствие, обеспечивает возможность функционирования системы оптической обработки информации при быстром изменении освещенности, В этом режиме система настройки может функционировать длительное время. Если по ка- ким-либо причинам величина глобального экстремума уменьшилась на величину, большую порога срабатьюания чевертого аналогового ком паратора 54, задаваемую аттенюатором 53, т.е. напряжение на выходе пикового детектора 45 уменьшилось до заданного значения, срабатывает компаратор 54, импульс с выхода второй дифференцирующей цепи 55 переводит систему в исходное состояние и процесс повторяется.

При формировании треугольного напряжения с выхода первого ЦАП 11 используются не все разряды с выходов первого счетчика 9 с той целью, чтобы обеспечить запасы подстройки в том случае, если точка глобального экстремума выходной функции объекта 15 регулирования оказалась в области близкой к вершинам треугольного колебания. Б этом случае при подстройке обеспечивается запас варьирования частоты.

Техническое преимзтдество изобретения заключается в реализации практически мгновенного возвращения в ку пространства состояний объекта регулирования после изучения всех возожных его состояний путем вариации независимых переменных, в увеличении

точности настройки в результате учета инерционности системы измерения точки, соответствующей глобальному экстремуму при возвращении системы в эту точку после изучения пространства состояний объекта регулирования, а также в обеспечении возможности подстройки системы после настройки на глобальный экстремум.

Формула изобретения

Система экстремального регулирования, содержащая генератор тактовых импульсов, подключенный к входу пер- вого ключа, первый счетчик, выход которого через последовательно соединенные цифроаналоговый преобразователь, преобразователь напряжения в частоту и амплитудный модулятор под- ключен к входу объекта регулирования с. которым связан дифференциальный , датчик, соединенньЕй через последовательно включенные первый дифференциальный усилитель, пиковьй детектор и аналого-цифровой преобразователь с входом оперативного запоминающего устройства, выходы которого соединены с первыми входами цифрового компаратора, выход которого через второй ключ соединен с входом управления третьего ключа, выход первого дифференциального усилителя соединен с первым входом первого аналогового компаратора, второй вход которого подключен к выходу пикового детектора, выход первого аналогового компаратора через последовательно соединенные одновибратор и третий ключ соединен с входом разрешения записи оперативного запоминающего устройства, входы которого соединены с вторыми входами цифрового компаратора, а также содержащая второй счетчик, выход которого через второй дифроана- логовьй преобразователь подключен к входу управления амплитудного модулятора и через первый элемент И к входу первого триггера, входы установки в О пикового детектора первого и второго счетчиков, первого триггера и оперативного запоминающего устройства подключены к шине сброса, отличающаяся тем, что, с целью повьшения быстродействия и точ ности системы, в нее введены с второго по седьмой элементы И, пять элементов ИЛИ, два элемента И-НЕ, второ триггер, блок инверторов, блок алгебраического суммирования, два регист- ра памяти, четыре коммутатора, два дифференцирующих элемента, два делителя частоты, два блока выборки-хранения, второй дифференциальньш усилитель, с второго по четвертый аналого вые компараторы, второй и третий цифроаналоговые преобразователи и аттенюатор, причем первые входы, второго и третьего элементов И подключены к выходу первого ключа, выходы второго и третьего элементов И подключены соответственно к первь - входам первого и второго элементов РШИ, выходы которых подключены соответственно к входам суммирования и вычитания первого счетчика, выходы которого под- ключены к входам первого элемента И-НЕ. блока инверторов и блока алге- . браического суммирования, выходы которого через первьй регистр памяти соединены с входами первого коммутатора, выход которого соединен с входами установки первого счетчика, выход первого дифференциального усилителя через первый н второй блоки выборки-хранения связан с входами второго дифференциального усилителя, выход которого подключен к входам . второго и третьего компараторов, выход первого элемента И-НЕ подключен к первому входу второго триггера, прямой выход которого подключен к первому входу третьего элемента ИЛИ,, второму входу второго элемента И и входу установки знака блока алгебраического суммирования, второй вход которого является входом коррекции, выходы блока инверторов через второй элемент И-НЕ подключены к первому входу четвертого элемента ИЛИ, выход которого подключен к второму входу второго триггера, инверсный выход которого подключен к вторым входам третьего элемента И и третьего элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, выход которого через второй регистр памяти соединен с первой группой входов второго коммутр.тора, выход которого соединен с входами установки , второго счетчика, выход первого триггера соединен с первыми входами четвертого и пятого.элементов И, с входами управления первого и второго ключей, входом стробирования четвертого компаратора и входом первого дифференцирующего элемента, выход которого соединен с входа ш разрешения записи первого и второго счетчиков и входами управления первого и второго коммутаторов, вторая группа входов -которых соединена с общей шиной устройства, выход генератора тактовых импульсов соединен с входом первого делителя частоты, первь м входом третьего коммутатора, вторым входом

одновибратора, выход первого делителя частоты подключён к входу второго делителя частоты и второму входу третьего коммутатора, выход которого соединен с входом четвертого комму- татора, первый и второй выходы которого соединены с вторыми входами четвертого и пятого элементов И, выходы которых подключены к вторым входам первого и второго элементов ИЛИ соот- ветственно, прямой выход второго делителя частоты подключен к первому входу шестого элемента И, входу уп , равления четвертого комментатора и опорному входу первого блока выборкихранения, инверсный выход второго делителя частоты подключен к первому входу седьмого элемента И и опорном-у входу второго блока выборки-хранения выходы второго и третьего анал оговых ,компараторов соответственно соединены с вто рыми входами шестого и седьмого элементов И, выходы которых через

пятый элемент ИЛИ подключены к входу управления третьего коммутатора, выход оперативного запоминающего устройства через последовательно соединенные цифроаналоговый преобразователь и аттенюатор подключен к первому входу четвертого аналогового компаратора, в торой вход которого соединен с выходом пикового детектора, выход четвертого аналогового компаратора через второй дифференцирующий элемент соединен с первым входом шестого элемента ИЖ, второй вход которого является входом внешнего сброса, выход шестого элемента ИЛИ соединен с внешней шиной сброса, входы разрешения записи первого и второго регистров памяти подключены к выходу третьего ключа, а входы установки в О первого и второго регистров памяти и второй вход четвертого этемента ИЛИ подключены к- шине сброса.

tv)

« « 0)

и

О)

0}

фие.д

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания магнитных меток | 1986 |

|

SU1469491A1 |

| Многоканальное измерительное электролокационное устройство | 1988 |

|

SU1571528A1 |

| Устройство для выделения и анализа R-зубцов электрокардиосигнала | 1986 |

|

SU1364298A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| Устройство контроля энергии удара | 1985 |

|

SU1343435A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2007 |

|

RU2354985C2 |

| Устройство для программного управления процессом обработки изделий микроэлектроники | 1986 |

|

SU1386962A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство контроля электромагнитных параметров гибкого магнитного диска | 1988 |

|

SU1578627A1 |

| Устройство для измерения времени переключения радиостанций | 1982 |

|

SU1029420A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для -автоматической настройки режимов питания оптически управляемых транспорантов в системах оптической и оптоэлектрон- ной обработки информации. Цель изобретения - повышение быстродействия, точности, что достигается реализацией практически мгновенного возвращения в точку глобального экстремума и последующей подстройкой с заданной точностью на глобальньй экстремум. Система экстремального регулирования содержит генератор тактовых импульт сов, два делителя частоты, три ключа, семь элементов И, пять элемен- тов ИЖ, два счетчика, три цифроана- логовых преобразователя, преобразователь напряжения в частоту, амплитудный модулятор, объект управления, дифференциальный датчик, два дифференциальных усилителя, два элемента И-НЕ, блок инверторов, два триггера, блок алгебраического суммирования,, два регистра памяти, четьфе аналоговых компаратора, пиковый детектор, аналого-цифровой преобразователь, оперативное запоминающее устройство, цифровой компаратор-, одновибратор, два дифференцирую Дих элемента и аттенюатор. 3 ил. с s

| Устройство для определения глобального экстремума функции многих переменных | 1974 |

|

SU667954A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1232042, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-11-15—Публикация

1985-07-16—Подача