1

(21)4433J62/24-2J

(22)30.05.88

(46) 30.01 .90. Бкт. N 4

(71)Харьковский авиационный институт им. Н.Е.Жуковского

(72)К.В.Соболевский, Г.А.Черепа- щук, A.M. Науменко и И.М.Кушнир (53) 621.317.32(088.8)

(56) Авторское свидетельство СССР № 1265631, кл. G 01 R 19/04, 19S5.

Авторское свидетельство СССР № 1228026, кл. G 01 R 19/04, 19.11.84.

(54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ЭКСТРЕ- МУМОВ

(57) Изобретение относится к измерительной технике и может использоваться для анализа параметров случай- ных электрических сигналов, содержащих помехи. Цель изобретения - повышение помехоустойчивости и расширение функциональных возможностей. Устройство содержит аналого-цифровой преобразователь 1, элементы 13, 14, 24 задержки, элементы И 6, 7-10, 22, 23, элементы ИЛИ 11, 12, запоминаю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремумов | 1984 |

|

SU1228026A1 |

| Устройство для определения экстремумов | 1987 |

|

SU1538139A1 |

| Устройство для определения экстремумов | 1981 |

|

SU985749A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для определения экстремумов электрического сигнала | 1984 |

|

SU1273816A1 |

| Устройство для выделения экстремумов | 1983 |

|

SU1111174A1 |

| Цифровой указатель экстремумов сигнала | 1975 |

|

SU557718A1 |

| Устройство для определения экстремумов электрического сигнала | 1988 |

|

SU1645940A1 |

| Устройство для определения экстре-МАльНыХ зНАчЕНий СлучАйНыХпРОцЕССОВ | 1978 |

|

SU805358A1 |

Изобретение относится к измерительной технике и может использоваться для анализа параметров случайных электрических сигналов, содержащих помехи. Цель изобретения - повышение помехоустойчивости и расширение функциональных возможностей. Устройство содержит аналого-цифровой преобразователь 1, элементы 13,14,24 задержки, элементы И6,7-10,22,23, элементы ИЛИ 11,12, запоминающие регистры 2,17,25, регистр 4 экстремальных значений, аналоговый вход 27, цифровой вход 28, выход 29 кода экстремизма, выходы 30,31 вида экстремума, выход 32 индикации момента времени измерения экстремума, синхронизирующие выходы 33,34. Арифметико-логический блок 3, блок 15 сравнения и регистр 16 уставки обеспечивает фильтрацию медленно изменяющейся помехи, введение арифметико-логического блока 18, блока 19 сравнения регистра 21 уставки, триггера 20 позволило исключить влияние импульсной помехи. Введение запоминающего регистра 25 и регистра 26 времени позволило обеспечить фиксацию моментов времени наступления экстремумов сигнала. За счет этого удалось повысить помехоустойчивость устройства и расширить его функциональные возможности. 1 з.п.ф-лы, 1 ил.

5У

«г

|о1Ё

(Л

ел

bo со

CD

1

00

Ночальная установка

Фиг,.

щие регистры 2, 17, 25, регистр 4 экстремальных значений, аналоговый вход 27, цифровой вход 28, выход 29 кода экстремума, выходы 30, 31 вида экстремума, выход 32 индикации момента времени измерения экстремума,синхронизирующие выходы 33, 34. Арифметико- логический блок 3, блок 15 сравнения и регистр 16 уставки обеспечивают фильтрацию медленно изменяющейся помехи, введение арифметикоИзобретение относится к измерительной технике и может быть использовано для анализа параметров случайных электрических сигналов, в частности выделения экстремумов сигнала, содержащего импульсные помехи.

Целью изобретения является повышение помехоустойчивости и расширение функциональных возможностей путем обеспечения датирования каждого экстремума.

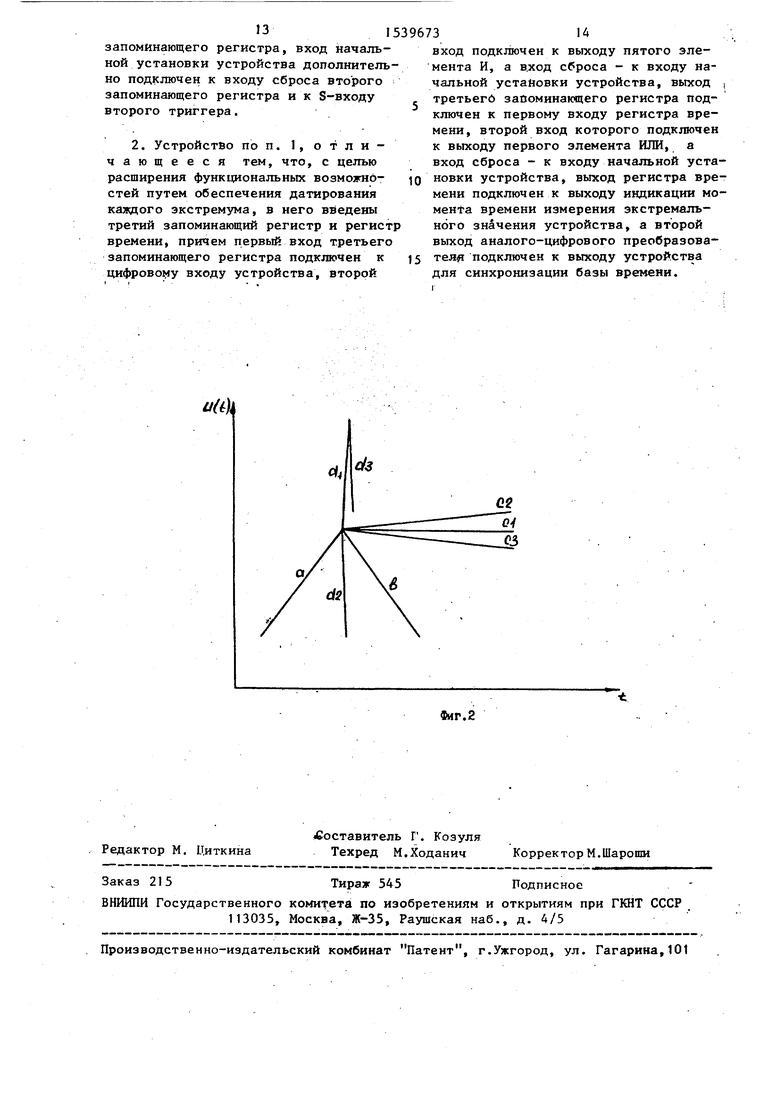

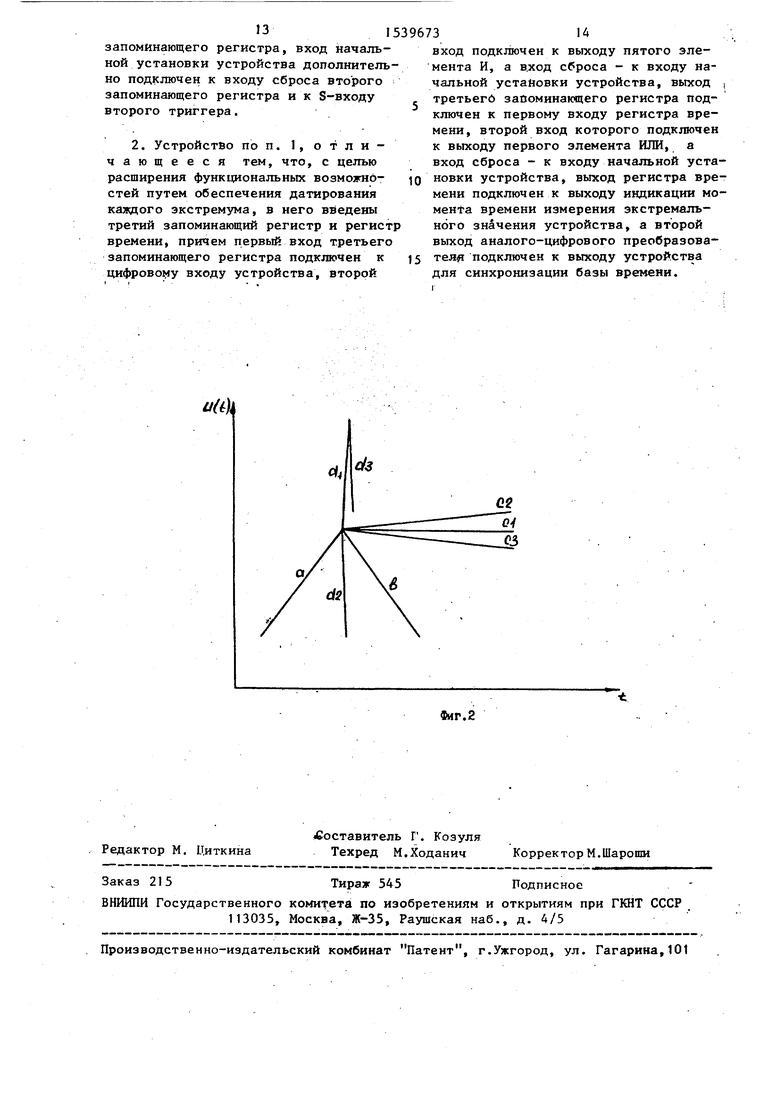

На фиг. 1 представлена функцио- нальная схема устройства; на фиг.2 - временная диаграмма :вх9дного сигнала.

Устройство для выделения экстремумов (фиг.J) содержит аналого-цифровой преобразователь 1 (АЦП), запоминающий регистр 2, арифметико- логический блок 3, регистр 4 экстремальных значений, RS-триггер 5, элементы И 6-10, элементы 11, 12, элементы 13, 14 задержки, блок 15 сравнения, регистр 16 уставки, запоминающий регистр 17, арифметико-логический блок 18, блок 1,9 сравнения, JK-триггер 20, регистр 21 уставки, элементы И 22, 23, элемент 24 задержки, запоминающий регистр 25 и регистр 26 времени.

Аналоговый вход 27 устройства подключен к входу аналого-цифрового преобразователя 1, информационный выход которого подключен к информационным входам запоминающих регистров 2 и 17 и к первым входам арифметико-логических блоков 3 и 18, выход запоминающего регистра 2 подключен к второму входу арифметико-логического блока 3 и к первому информационному входу регистра 4, выход запоминающего регистра 17 подключен к второму входу ариф

логического блока 18, блока 19 сравнения, регистра 21 уставки, триггера 20 позволило исключить влияние импульсной помехи. Введение запоминающего регистра 25 и регистра 26 времени позволило обеспечить фиксацию моментов времени наступления экстремумов сигнала. За счет этого удалось повысить помехоустойчивость устройства и расширить его функциональные возможности. 1 з.п.ф-лы, 2 ил.

0

0

5

метико-логического блока 18. Цифровой вход 28 устройства подключен к информационному входу запоминающего регистра 25, выход которого подключен к информационному входу регистра 26 времени. Первый выход арифметико- логического блока 3 подключен к пер- 5 вому входу элемента И 6, а второй

выход - к первому входу элемента И 7. Выход регистра 16 уставки подключен к первому входу блока 15 сравнения, к второму входу которого подключен информационный выход арифметико-логического блока 3. Выход блока 15 сравнения подключен к третьим входам элементов И 6 и 7 и к первому входу элемента И 10. Выходы элементов И 6 и 7 подключены к второму и третьему информационным входам регистра 4 экстремальных значений соответственно и к первым входам элементов И .8 и 9 соответственно. Выход элемента И 8 подключен к первому входу элемента ИЛИ Пик S-входу RS-триггера 5, выход элемента И 9 соединен с вторым входом элемента ИЛИ 11 и с первым входом элемента ИЛИ 12 соответственно . Выход элемента ИЛИ 12 подключен к R-входу RS-триггера 5, а выход элемента ИЛИ 1 подключен к синхронизирующим входам регистра 4 экстре- i мальных значений и регистра 26 времени, а также к входу элемента 14 задержки. Прямой и инверсный выходы RS-триггера 5 подключены к вторым входам элементов И 7 и 6 соответственно. Первый выход регистра 4 экстремальных значейий является выходом 29 кода экстремума устройства, а второй и третий выходы этого регистра являются выходами 30, 31 вида экстремума устройства. Выход регистра 26f

0

5

0

5

времени является выходом 32 индика- ции момента времени измерения экстремального значения устройства. Выход элемента 14 задержки подключен к синхронизирующему выходу 33 устройства.

Выход арифметико-логического блока 18 подключен к первому входу блока

19 сравнения, к второму входу которо- 10 чения сигнала U- . го подключен выход регистра 21 устав- Арифметико-логический блок 3 по- ки. Первый выход блока 19 сравнения подключен к первому входу элемента И 23 и J-входу триггера 20, второй выход блока 19 сравнения подключен к первому входу элемента И 22, выход которого подключен к R-входу триггера 20. Выход триггера 20 подключен к второму входу элемента И 23, выход которого подключен к четвертым входам элементов -И 6 и 7 и к второму входу элемента И 10.

Синхронизирующий выход АЦП 1 подключен к входу элемента 13 задержки

и синхронизирующему выходу 34 устрой- 25 сутСтБУет уровень логической ства. Выход элемента 13 задержки подключен к входу элемента 24 задержки и к второму входу элемента И 22. Выход элемента 24 задержки подключен к синхронизирующим входам запоминающего регистра 17 и триггера 20, третьему

нала, проверяемого на экстремальность, - Ue .

Запоминающий регистр 25 предназна чен для хранения кода момента времени измерений сигнала, проверяемого на экстремальность.

Запоминающий регистр 17 предназна чен для хранения кода предыдущего зн

средством вычитания производит сравнение значения сигнала Ue, проверяемого на экстремальность, и вновь по- 15 ступающего U(.

С информационного выхода арифмети ко-логического блока 3 снимается код модуля разности |Uj - Ue|, а с перво и второго логических выходов - знак разности. Если U, UB, то на первом логическом выходе присутствует уро- 0, а на втором 20

вень логического уровень логической Г

то на первом логическом выходе приit 1

если U; t Ue, i

. на втором - уровень логического

если же Ut- Up, то на первом и вто ром логических выходах присутствует уровень логического О. 30 Арифметико-логический блок 18 посредством вычитания производит сравнение предыдущего значения сигнала U. и вновь поступившего U(. С его выхода снимается код модуля разности IU р U , |,

входу элемента И 10 и к вторым входам элементов И 8 и 9. Вход элемента И 10 подключен к синхронизирующим входам запоминающих регистров 2 и 25, К-вход триггера 20 подключен к шине логического 0 устройства.

Вход начальной установки устройства подключен к второму входу эле-.

нящимся в регистре 16 уставки, и ес. мента ИЛИ 12, входам сброса запоминай- 40 ли (и. , -, диммн) то На его выщих регистров 2, 17, 25, регистра 4 экстремальных значений, регистра 26 времени и к S-входу триггера 20.

Работа устройства заключается в следующем.

АЦП 1 работает в режиме циклического непрерывного преобразования входного сигнала U в цифровой параллельный код Uj. После каждого цикла преобразования на информационном выходе аналого-цифрового преобразователя 1 появляется код текущего зна- €ения сигнала U;, а на синхронизирующем выходе - импульс конца измерения, который осуществляет временную, привязку работы устройства.

Запоминающий регистр, 2 предназначен для хранения кода значения сигходе присутствует уровень логической I, и наоборот.

Блок 19 сравнения сранивает модуль разности |U - U,.t | с макси45 малъно допустимым за один цикл преоб разования приращением и UMQKC хранящимся в регистре 21 уставки, и если |Uj - U-, г 3UwaRCS то на его первом выходе присутствует уровень ло50 гической 1, а на втором выходе - - уровень логического О, и наоборот.

Регистр 4 экстремальных значений предназначен для хранения кода вы- сс деленного экстремума Ue,ги его вида MAX,- MIN.

Регистр 26 времени предназначен для хранения кода момента времени измерения экстремума Тех.г.

чения сигнала U- . Арифметико-логический блок 3 по-

нала, проверяемого на экстремальность, - Ue .

Запоминающий регистр 25 предназначен для хранения кода момента времени измерений сигнала, проверяемого на экстремальность.

Запоминающий регистр 17 предназна- чен для хранения кода предыдущего значения сигнала U- . Арифметико-логический блок 3 по-

сутСтБУет уровень логической

средством вычитания производит сравнение значения сигнала Ue, проверяемого на экстремальность, и вновь по- ступающего U(.

С информационного выхода арифметико-логического блока 3 снимается код модуля разности |Uj - Ue|, а с первого и второго логических выходов - знак разности. Если U, UB, то на первом логическом выходе присутствует уро- 0, а на втором

вень логического уровень логической Г

то на первом логическом выходе приit 1

если U; t Ue, i

. на втором - уровень логического

сутСтБУет уровень логической

если же Ut- Up, то на первом и втором логических выходах присутствует уровень логического О. Арифметико-логический блок 18 посредством вычитания производит сравнение предыдущего значения сигнала U. и вновь поступившего U(. С его выхода снимается код модуля разности IU р U , |,

Блок 15 сравнения сравнивает модуль разности I Uj - Ue(с минимально

ми и t

храдопустимым приращением dU,

нящимся в регистре 16 уставки, и если (и. , -, диммн) то На его выходе присутствует уровень логической I, и наоборот.

Блок 19 сравнения сранивает модуль разности |U - U,.t | с максималъно допустимым за один цикл преобразования приращением и UMQKC хранящимся в регистре 21 уставки, и если |Uj - U-, г 3UwaRCS то на его первом выходе присутствует уровень логической 1, а на втором выходе - - уровень логического О, и наоборот.:

Регистр 4 экстремальных значений предназначен для хранения кода вы- деленного экстремума Ue,ги его вида MAX,- MIN.

Регистр 26 времени предназначен для хранения кода момента времени измерения экстремума Тех.г.

Устройство имеет два вида работы: выделение максимума и выделеие минимума. Вид работы определяется состоянием триггера 5. Если триггер 5 находится в единичном состоянии, то происходит выделение минимума, а если он в нулевом состоянии, то происходит выделение максимума.

Синхронизация работы устройства осуществляется элементами 13, J4, 24 задержки.

Элемент 13 задержки задерживает импульс конца измерения аналого-цифрового преобразователя 1 на время, достаточное для установления стабильных уровней на выходе арифметико- логического блока 18 и блока 19 сравнения .

Элемент 24 задержки задерживает выходной импульс элемента 13 задержки на время, достаточное для установления стабильных уровней на выходе арифметико-логического блока 3 и блока 15 сравнения, а также для сброса триггера 20, срабатывания элементов И 23, 6 и 7.

Блок 14 задержки задерживает импульс, прошедший через элементы И 8, 9 и элемент ИЛИ 1J на время, доста- точное для записи информации в регистр 4 экстремальных значении и регистр 26.

В исходное состояние устройство приводится сигналом с входа началь- ной установки. При этом ячейки запом нающих регистров 2, 17 и 25 регистра 4 экстремальных значений, регистра 2 Времени и триггер 5 устанавливаются в нулевое состояние, а триггер 20 - в единичное. Так как триггер 5 установлен в нулевое состояние, то происходит выделение максимума.

Между кодами значений сигналов U Ug.Uj.,, dUmHH, Лижвкс возможны следующие соотношения:

(О

(2) (3) (4) 55

При выделении максимума и выполнении условия (1) на участке нормальио- го возрастания сигнала (фиг.2,учас10

15 5396738

ток а) комбинация сигналов на входах элементов И 6 и 7 следующая: логический О с первого логического выхода арифметико-логического блока 3 на первом входе элемента И 6 и логический О с неинвертирующего выхода сброшенного триггера 5 на втором входе элемента И 7 закрывает их. Поэтому импульс не поступает на входы триггера 5, регистра 4 экстремальных значений, регистра 26 времени и их состояние не изменяется.

Сигнал с второго выхода блока 19 сравнения закрывает элемент И 22, и сброс триггера 20 не происходит. Комбинация сигналов на входе элемента И 10 разрешает прохождение импульса на синхронизирующий вход за- поминающего регистра 2. Задний фронт этого импульса производит запись кода текущего сигнала U; в запоминающие регистры 2 и 17 и подтверждает состояние триггера 20. Пронормалъ-значение, записанное в запоминающем регистре 2, изменяется в соответствии с входным сигналом.

После окончания участка с нормальным возрастанием сигнала будет выполнено условие (2), (3) и (4) (фиг.2, участки Ъ,с или d соответственно) .

При выполнении условия (2)(сигнал начал нормально убывать,фиг.2,

цесс повторяется на участке ного возрастания сигнала, а

5 0

5

0

5

комбинация сигналов на элемента И 6 открывает его.

участок Ь), входе

Сигнал с его выхода поступает на второй информационный вход регистра 4 экстремальных значений и на первый вход элемента И 8. Импульс с выхода элемента 24 задержки проходит через открытый элемент И 8 на S-вход триггера 5 и переключает его в единичное состояние, переключая устройство на выделение минимума. Кроме того,этот импульс, пройдя через элемент ИЛИ 11 на синхронизирующий вход регистра 4 экстремальных значений, передним фронтом производит перезапись кода экстремума Ug из регистра 2, а также вида экстремума (максимум или минимум) с выходов элементов И 6 и 7 в регистр 4 экстремальных значений . Сигнал с второго выхода блока сравнения закрывает элемент И 22, и сброс триггера 20 не происходит. Комбинация сигналов на входе элемента И 10 разрешает прохождение импульса на синхронизирующий вход запоминающего регистра 2, и по заднему фронту этого импульса производится запись ко-

дов текущего значения сигнала U в запоминающие регистры 2 и 17.

При выполнении условия (3) (сигнал начал медленно изменяться, фиг.2, участки с, с2 или сЗ) выход- ной сигнал блока 15 сравнения закрывает элементы И 6, 7, 10, поэтому изменение состояния запоминающего регистра 2, регистра 4 экстремальных значений и триггера 5 не происходит, устройство находится в режиме ожидания превышения минимально допустимого приращения. При этом запоминающий регистр 17 записывает код текущего значения сигнала, а состояние триггера 20 не изменяется.

При выполнении условия (J) после выполнения условия (3) в заломи- v нающий регистр 2 будет записан код текущего значения сигнала U. и устройство начнет следить за изменениями сигнала. Если же после выполнения условия (3) выполнится условие (2), то будет произведена перезапись выделенного максимума Ue из запоминающего регистра 2 и вида экстремума с выходов элементов И 6 и 7 в регистр 4 экстремальных значений, и

10

20

мя спада помехи условие (4) не нару шается и устройство находится в реж ме ожидания окончания помехи.

После окончания воздействия поме хи выполняется условие (1), (2) или (3), При этом задним фронтом первого импульса с выхода элемента 24 задержки устанавливается триггер 20 15 При выполнении условия (1) устройство переходит в режим отслеживания изменения входного сигнала. При выполнении условия (2) после окончани следующего цикла преобразования про изводится перезапись кода выделенно го экстремума из запоминающего регистра 2 в регистр 4 экстремальных значений и устройство переходит к в делению минимума. При выполнении

условия (3) устройство переключает ся из режима ожидания окончания помехи в режим ожидания превышения минимально допустимого приращения. При выделении минимума устройство работает по аналогичному алгоритму. Так, при выполнении условия (2) элемент И 10 открывается и разрешает запись кода текущего зна чения сигнала U- в запоминающий р

25

30

устройство перейдет к выделению мини- эс гистр 2, т.е. устройство находится

в режиме слежения. При выполнении условия (4) элементы И 6,7 и 10 закрыты выходным сигналом элемента И 23 и устройство находится в режиме ожидания окончания помехи. При выполнении условия (1) открывается элемент И 7, производится перезапись кода минимума из регистра 2 в регистр 4 и устройство переходит к выделению максимума.

мума.

При выполнении условия (4)(сигнал начал быстро изменяться - фиг,2. участки dl или d2, что характерно при воздействии импульсной помехи) сигнал с первого выхода блока 19 сравнения закрывает элемент И 23, выходной сигнал которого закрывает элементы И 6, 7 и 10, поэтому изменение состояния запоминающего регистра 2, регистра 4 экстремальных значений и триггера 5 не происходит. Устройство находится в режиме ожидания окончания помехи. При этом импульс с выхода элемента 13 задержки, пройдя через открытый элемент И 22, сбрасывает триггер 20 в нулевое состояние.

Процесс повторяется на участке быстрого изменения сигнала, т.е. на участке фронта импульсной помехи.

Вблизи экстремума помехи (фиг.2, участки dl, d3), возможен случай однократного нарушения неравенства

IU; - и,--,

ной сигнал состояние мент И 23 и триггер

10 I и 11 . При этом выходЯЧС|К --

установленного в нулевое триггера 20 закрывает эле- и запись в регистры 2, 4 5 не производится. Во вре

0

мя спада помехи условие (4) не нарушается и устройство находится в режиме ожидания окончания помехи.

После окончания воздействия помехи выполняется условие (1), (2) или (3), При этом задним фронтом первого импульса с выхода элемента 24 задержки устанавливается триггер 20. 5 При выполнении условия (1) устройство переходит в режим отслеживания изменения входного сигнала. При выполнении условия (2) после окончания следующего цикла преобразования производится перезапись кода выделенного экстремума из запоминающего регистра 2 в регистр 4 экстремальных ч значений и устройство переходит к выделению минимума. При выполнении

условия (3) устройство переключается из режима ожидания окончания помехи в режим ожидания превышения минимально допустимого приращения. При выделении минимума устройство работает по аналогичному алгоритму. Так, при выполнении условия (2) элемент И 10 открывается и разрешает запись кода текущего значения сигнала U- в запоминающий ре5

0

0

5

0

5

в режиме слежения. При выполнении условия (4) элементы И 6,7 и 10 закрыты выходным сигналом элемента И 23 и устройство находится в режиме ожидания окончания помехи. При выполнении условия (1) открывается элемент И 7, производится перезапись кода минимума из регистра 2 в регистр 4 и устройство переходит к выделению максимума.

В процессе работы устройства осуществляется датирование каждого экстремума. Для этого в момент времени, когда в запоминающий регистр 2 производится запись кода значения сигнала, проверяемого на экстремальность,в запоминающий регистр 25 производится запись кода момента времени измерения этого значения.

Если значение сигнала, проверяемого на экстремальность, оказалось действительным экстремумом, то оно переписывается в регистр 4 экстремальных значений и выводится как экс1

тремум. При этом код момента времени измерения этого значения переписывается из запоминающего регистра 25 в регистр 26 времени и выводится как момент времени измерения экстремума .

Формула изобретения

12

выход регистра экстремальных значений является выходом кода экстремума устройства, а второй и третий - выходами вида экстремума, второй вход второго элемента ИЛИ, входы сброса запоминающего регистра и регистра экстремальных значений соединены с входом начальной установки устройства,

выход регистра уставки подключен к первому входу блока сравнения, второй вход которого подключен к информационному выходу арифметико-логического блока, выход блока сравне5 ния подключен к третьим входам первого и второго элементов И и к первому входу пятого элемента И, отличающееся тем, что, с целью повышения помехоустойчивости, в него

0 введены второй запоминающий регистр, второй арифметико-логический блок, второй блок сравнения, второй триггер, второй регистр уставки, шестой и седьмой элементы И и третий эле5 мент задержки, причем первый выход аналого-цифрового преобразователя дополнительно подключен к первым входам второго запоминающего регистра и второго арифметико-логического

0 блока, выход второго запоминающего регистра подключен к второму входу второго арифметико-логического блока, выход которого подключен к первому входу второго блока сравнения, выход второго регистра уставки подключен

5

к второму входу второго блока сравнения., первый выход второго блока

5

сравнения подключен к лерво.му JBXO- ду шестого элемента И и J-входу второго триггера, второй выход второго блока сравнения подключен к первому входу седьмого элемента И, .выход ко- торого подключен к R-входу второго триггера, К-вход которого подключен к шине логического нуля устройства, выход второго триггера подключен к второму входу шестого элемента И, выход которого подключен к четвертым входам первого и второго элементов И и к второму входу пятого элемента И, выход первого элемента задержки подключен к второму входу седьмого элемента И и к входу третьего элемента задержки, выход третьего элемента задержки подключен к вторым входам третьего и четвертого элементов И и тактовому входу второго триггера, к третьему входу пятого элемента И и к второму входу второго

0

5

запоминающего регистра, вход начальной установки устройства дополнительно подключен к входу сброса второго запоминающего регистра и к S-входу второго триггера.

вход подключен к выходу пятого элемента И, а вход сброса - к входу начальной установки устройства, выход третьего запоминающего регистра подключен к первому входу регистра времени, второй вход которого подключен к выходу первого элемента ИЛИ, а вход сброса - к входу начальной установки устройства, выход регистра времени подключен к выходу индикации момента времени измерения экстремального значения устройства, а второй выход аналого-цифрового преобразователя подключен к выходу устройства для синхронизации базы времени.

Авторы

Даты

1990-01-30—Публикация

1988-05-30—Подача