1228026 гой

Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах для анализа параметров случайных электрических сигналов. 5

Цель изобретения - повьшение быстродействия устройства.

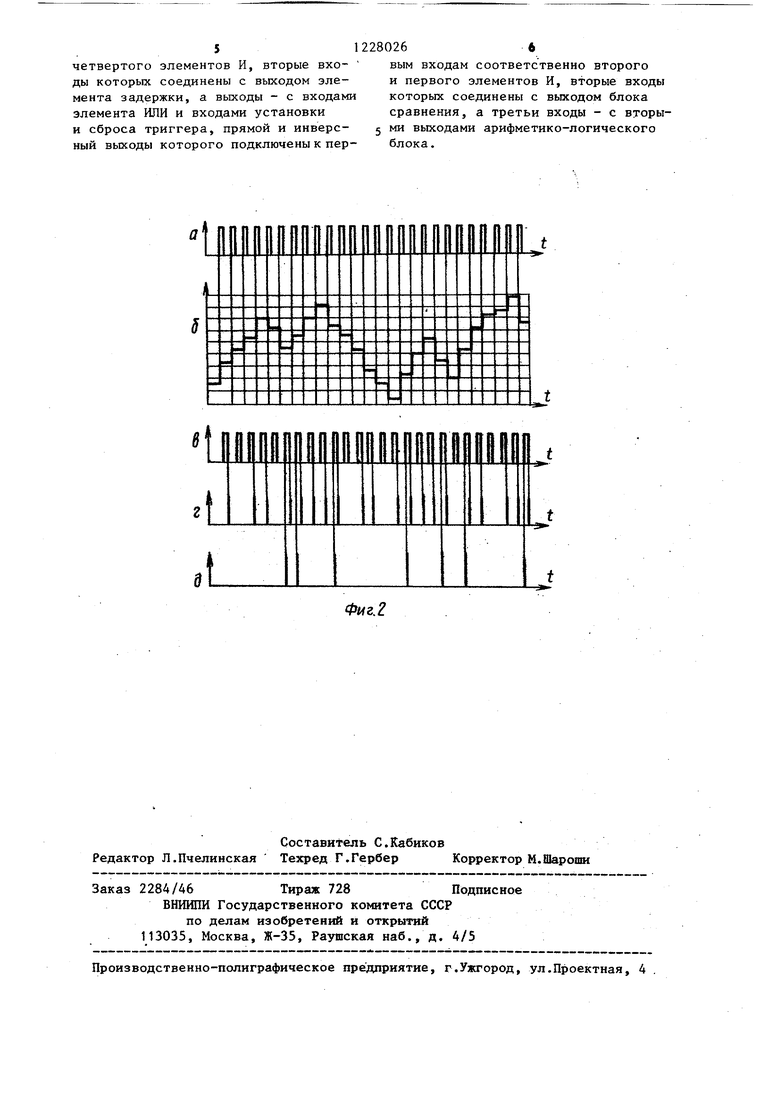

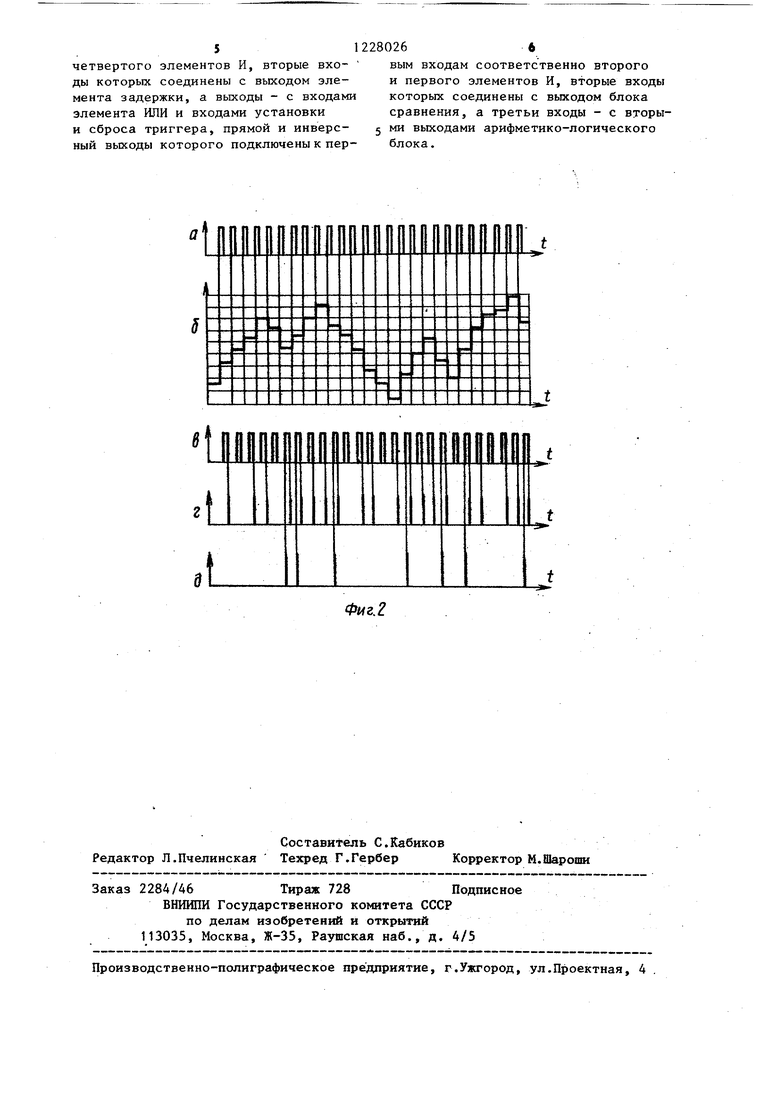

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - временные диаграммы его работы. Ю

Устройство для определения экстремумов содержит аналого-цифровой преобразователь 1, элемент задержки 2, элемент И 3, запоминающий регистр 4, арифметико-логический блок 5, задат- чик 6 добавочного кода, блок 7 сравнения , элементы И 8 - 11, элемент ИЛИ 12, триггер 13, регистр 14 экстремальных значений. Элементы И В - 11 и триггер 13 образуют селектор. Первый вход арифметико-логического блока i 5 подключен к выходу регистра 4 и информационному входу регистра 14, а второй вход - к информационному входу регистра 4 и информационному выходу аналого-цифрового преобразователя 1, вход которого является входом устройства, а синхронизирую- пщй выход, через элемент 2 задержки, подключен к первому входу элёмен- 30 та И 3, выход которого соединен с синхронизирующим входом регистра 4, а второй вход - с выходом блока 7 сравнения, входы которого подключены

вход которого соединен с входно шиной начальной установки.

Устройство работает следующим об разом.

Сигнал начальной установки через элемент ИЛИ 15 устанавливает триггер 13 в состояние О. Исследуемый сигнал U(t) поступает на вход анало го-цифрового преобразователя 1. Каж дое новое кодированное значение N; входного сигнала устанавливается на информационном выходе преобразовате ля 1 в момент появления импульса К нец измерения (КИ) на его синхрони

5 зирующем выходе (фиг. 2а). Этот импульс задерживается элементом 2 задержки и по спаду задержанного импу са через элемент И 3 производится з пись настоящего кодированного значе

ния N;(t) выходного сигнала в запом нающий регистр 4 (фиг. 2д). Арифмет ко-логический блок 5 производит выч тание двух п-раз рядных чисел, одно из которых N(t) поступает с выхода

запоминающего регистра 4, а второе N,(t) с информационного выхода пре образователя 1.

При N, +,(t)N;(t) информационные выходы и блока 5 переключаю

4 11

(t)N;(t) эти

ся соответственно в состояние и О. При сигнале N,-, выходы меняют свое состояние на про тивоположное. Блок 7 сравнения прои водит сравнение двух п-разрядных чи

соответственно к первому выходу ариф- 35 сел, одно из которых /N-(t)-N;(t)/

метико-логического блока 5 и задатчи- ка 6 добавочного кода. Первые входы элементов И 10 и 11 Соединены с выходами элементов И 8 и 9, вторые входы - с выходом элемента 2 задержки, а выходы - соответственно с входами установки и сброса триггера 11,- прямой и инверсный выходы которого соединены соответственно с первыми входами элементов И 9 и 8, вторые входы кото- 45 блока 7 сравнения устанавливается

поступает с информационного выхода блока 5, а второе - постоянное (уст новочное) значение кода N - с выхо да задатчика 6. Установка значения 40 добавочного цифрового кода AN произ водится из условия ANMNno , (где N„0 - цифровой код помехи, присут ствующей на выходе преобразователя При условии J N|,(t)-N(t) AN, выхо

рых подключены к выходу блока 7 сравнения, а третьи входы - к вторым выходам ар;и4 1етико-логического. блока 5. Синхронизирующий .вход регистра 14

в состояние 1. При анализе сигналов, поступаяяцик с вькодов блоков 5 и 7, а также триггера 13 на входы элементов И 8 и 9 возможным следуюподключен через элемент ИЛИ 12 к выхо- д дам элементов И 10 и 11,. а управляющие входы - к выходам элементов И 8 и 9 соответственно.

Дополнительно устройство содержит элемент ИЛИ 15, причем вход сброса .триггера 13 соединен с выходом эле- гента И 11 через элемент ИЛИ 15, дру228026гой

5

Ю

30вход которого соединен с входной шиной начальной установки.

Устройство работает следующим образом.

Сигнал начальной установки через элемент ИЛИ 15 устанавливает триггер 13 в состояние О. Исследуемый сигнал U(t) поступает на вход аналого-цифрового преобразователя 1. Каждое новое кодированное значение N; (t) входного сигнала устанавливается на информационном выходе преобразователя 1 в момент появления импульса Конец измерения (КИ) на его синхрони 5 зирующем выходе (фиг. 2а). Этот импульс задерживается элементом 2 задержки и по спаду задержанного импульса через элемент И 3 производится запись настоящего кодированного значе ния N;(t) выходного сигнала в запоминающий регистр 4 (фиг. 2д). Арифметико-логический блок 5 производит вычитание двух п-раз рядных чисел, одно из которых N(t) поступает с выхода

запоминающего регистра 4, а второе N,(t) с информационного выхода преобразователя 1.

При N, +,(t)N;(t) информационные выходы и блока 5 переключают- 4 11

(t)N;(t) эти

ся соответственно в состояние и О. При сигнале N,-, выходы меняют свое состояние на противоположное. Блок 7 сравнения производит сравнение двух п-разрядных чи35 сел, одно из которых /N-(t)-N;(t)/

блока 7 сравнения устанавливается

поступает с информационного выхода блока 5, а второе - постоянное (установочное) значение кода N - с выхода задатчика 6. Установка значения добавочного цифрового кода AN производится из условия ANMNno , (где N„0 - цифровой код помехи, присутствующей на выходе преобразователя). При условии J N|,(t)-N(t) AN, выход

в состояние 1. При анализе сигналов, поступаяяцик с вькодов блоков 5 и 7, а также триггера 13 на входы элементов И 8 и 9 возможным следую д либ случаи:

55

|N,-,(t)N;(t) при |N;,,(t)N;(t)l ДЫ при |Nu.(t)N;(t) при при

В первом случае на входы элементов И 8 и 9 с выхода блока 7 сравнения поступает 1, разрешающая анаЛИЗ информации с выходов арифметико- логического блока 5 и состояния триггера 13. При 3TOMj если триггер 13 установлен в О, сигнал 1, с выхода блока 5 не поступает на первьш вход элемента И 11. Сигналы установки макс и мин с выходов элементов И 8 и 9 отсутствуют, в результате чего отсутствует запись в регистр 14 экстремальных значений, но 1, присутствующая на втором входе элемента ИЗ, дает разрешение на прохождение задержанного импульса с выхода элемента 2 задержки на синхронизирующий вход запоминающего регистра 4, по спаду которого производится з апись настоящего кодированного значения Nj(t) в запоминающий регистр 4 (-фиг. 2д) .

Во втором случае с выхода блока 5 на вход элемента И 8 поступает 1, триггер t3 установлен 1 с выхода элемента И-8 поступает на вход V,(макс) регистра 14 экстремальных значений и через элемент И 10 разр ешается прохождение импульса с выхода элемента 2 задержки на син- хройизирующий вход регистра 14 экстремальных значений через элемент

ИЛИ 12, производя запись по его фрон-зо з )зыход элемента ИЛИ соединен с син- ту значения содержимого запоминающего регистра 4, являющегося экстремальным (4иг. 2Ь), а также происходит изменение состояния триггера 13 на противоположное. Б запоминающий регистр 4 производится запись нового настоящего кодированного значения аналогично первому случаю.

35

40

Nj,,(t)

При переходе от второго случая к первому при установленном триггере t3 с выхода блока 5 на вход элемента И 9 поступает 1. С выхода элемента И 9 она поступает на вход Vj (мин) регистра 14 экс- ремальных значений и разрешает прохождение син-45 хроимпульса на синхронизирующий вход регистра 14 экстремальных значений через элемент И 11 и элемент ИЛИ 12, производя запись значения содержимого запоминающего регистра 4, являющего- 50 ся экстремальным (фиг. 2В). Происходит изменение состояния триггера 13 на противоположное. В запоминающий регистр 4 производится запись нового кодированного значения входного сигна-55 ла. В третьем случае на выходе блока 7 устанавливается О

сравнения

котохронизируклцим входом регистра экстремальных значений, выход которого является выходом устройства, о т л и - чающееся тем, что, с целью повышения быстродействия, второй вход арифметико-логического блока подключен к информационному выходу аналого- цифрового преобразователя, а -второй выход - к третьему входу селектора, первый и второй выходы которого соеди нены с соответствующими входами элемента ИЛИ, а третий и четвертый выходы соответственно, с первым и вторым управляющими входами регистра экстремальных значенийJ информацнон- ньй вход которого подключен к выходу запоминающего регистра, причем второй вход блока сравнения соединен с выходом задатчика добавочного кода, а выход - с вторым входом элемента И.

2. Устройство по п. 1, о т л и - чающееся, тем, что селектор содержит четыре элемента И и триггер, причем выходы первого и второго элементов И подключены к соответствующим управляюпщм входам регистра экстремальных значений и соответственно - к первым входам третьего и

рый блокирует работу элементов И 3,8

и 9, в результате чего изменения состояния триггера 13 и перезаписи, в регистре 14 не происходит.

Таким образом, быстродействие уст- ройства зависит только от быстродействия преобразователя 1.

Формула изобретения

1. Устройство для определения экстремумов, содержащее элемент 1, элемент ИЛИ, регистр экстремальных значений и запоминающий регистр, селектор, задатчик добавочного кода, блок сравнения, арифметико-логический блок,

элемент задержки и аналого-цифровой преобразователь, вход которого является входом уст|ройства, информационный выход подключен к информационному входу запоминающего регистра, а

синхронизирующий выход через элемент задержки - к первому входу селектора и первому входу элемента И, выход которого соединен с синхронизирующим входом запоминающего регистра, выход

которого подключен к первому входу арифметико-логического блока, первый выход которого соединен с первым входом блока сравнения, выход которого подключен к второму входу селектора.

зо з )зыход элемента ИЛИ соединен с син-

35

40

45 50 55

хронизируклцим входом регистра экстремальных значений, выход которого является выходом устройства, о т л и - чающееся тем, что, с целью повышения быстродействия, второй вход арифметико-логического блока подключен к информационному выходу аналого- цифрового преобразователя, а -второй выход - к третьему входу селектора, первый и второй выходы которого соединены с соответствующими входами элемента ИЛИ, а третий и четвертый выходы соответственно, с первым и вторым управляющими входами регистра экстремальных значенийJ информацнон- ньй вход которого подключен к выходу запоминающего регистра, причем второй вход блока сравнения соединен с выходом задатчика добавочного кода, а выход - с вторым входом элемента И.;

2. Устройство по п. 1, о т л и - чающееся, тем, что селектор содержит четыре элемента И и триггер, причем выходы первого и второго элементов И подключены к соответствующим управляюпщм входам регистра экстремальных значений и соответственно - к первым входам третьего и

5

четвертого элементов И, вторые входы которых соединены с выходом элемента задержки, а выходы - с входами элемента ИЛИ и входами установки и сброса триггера, прямой и инверсный выходы которого подключены к пер

1

Фиг.2

Составитель С.Кабиков Редактор Л.Пчелинская Техред Г.Гербер Корректор М.В1ароши

Заказ 2284/46 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная, 4

вым входам соответственно второго и первого элементов И, вторые входы которых соединены с выходом блока сравнения, а третьи входы - с вторы- 5 ми выходами арифметико-логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремумов | 1981 |

|

SU985749A1 |

| Устройство для определения экстремумов | 1987 |

|

SU1538139A1 |

| Устройство для выделения экстремумов | 1988 |

|

SU1539673A1 |

| Устройство для определения экстремумов электрического сигнала | 1984 |

|

SU1273816A1 |

| Устройство для определения экстремумов электрического сигнала | 1986 |

|

SU1322161A2 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Система стабилизации задержки | 1981 |

|

SU957422A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАКСИМАЛЬНОГО ЗНАЧЕНИЯ ИМПУЛЬСНОГО АНАЛОГОВОГО СИГНАЛА | 1993 |

|

RU2063048C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Устройство для определения стационарности случайного процесса | 1984 |

|

SU1251120A1 |

Изобретение относится к измерительной технике. Может быть использовано в информационно-измерительных системах для анализа параметров случайных электрических сигналов. Цель изобретения - повьшение быстродействия - достигается введением новых функциональных связей между блоками и схемными элементами устройства, а также схемного выполнения селектора на логических элементах (ЛЭ) и 8- 11 и триггере 13. Устройство содержит также аналого-цифровой преобразователь 1, элемент задержки 2, ЛЭ ИЗ, запоминающий регистр 4, арифметико- логический блок 5, датчик 6 добавочного кода, блок сравнения 7, ЛЭ ИЛИ 12 и 15, регистр 14. Быстродействие данного устройства зависит только от быстродействия анапого-ци Фового преобразователя 1 и может быть повышено по сравнению с известными устройствами того же назначения. 1 з.п. ф-лы, 2 ил.. extr FO X э ND 3d Начальная ycmaftetffa фиг, г

| Цифровой пиковый детектор | 1982 |

|

SU1118926A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения экстремумов | 1981 |

|

SU985749A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-30—Публикация

1984-11-19—Подача