ел

Јъ

сп to

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения фазы сигналов | 1987 |

|

SU1442932A2 |

| Устройство для определения фазы сигналов | 1987 |

|

SU1479887A2 |

| Устройство для определения фазы сигналов | 1988 |

|

SU1580279A1 |

| Устройство для определения фазы сигналов | 1986 |

|

SU1345134A1 |

| Измеритель фазы сигналов | 1986 |

|

SU1368803A1 |

| Устройство для определения квадрата амплитуды сигнала | 1987 |

|

SU1531010A2 |

| Низкочастотный цифровой фазометр | 1990 |

|

SU1784924A1 |

| Устройство контроля комбинационных составляющих сигнала нелинейного четырехполюсника | 1985 |

|

SU1264111A1 |

| Измеритель фазы сигналов | 1987 |

|

SU1506379A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

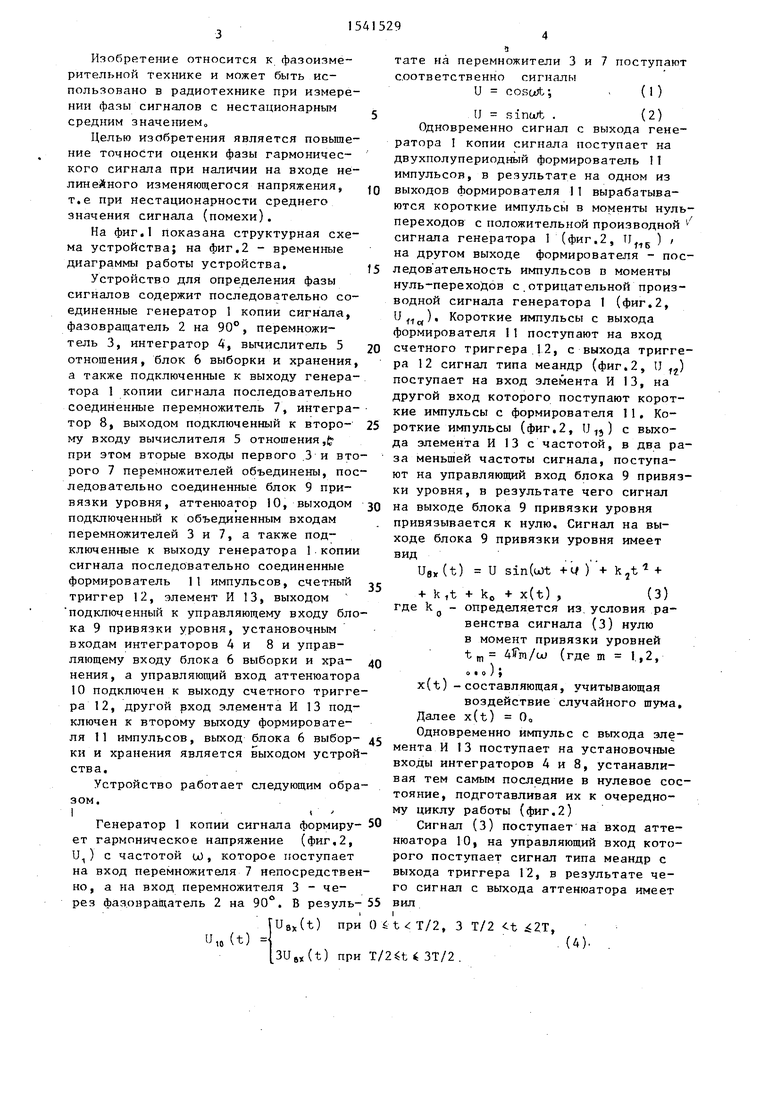

Изобретение относится к электроизмерительной технике и может быть использовано при измерении фазы сигналов с нестационарным средним значением. Целью изобретения является повышение точности определения фазы гармонического сигнала при наличии на входе нелинейно изменяющегося напряжения, т.е. при нестационарности среднего значения сигнала (помехи). Устройство содержит генератор 1 копии сигнала, фазовращатель 2 на 90°, перемножитель 3, интегратор 4, вычислитель 5 отношения, блок 6 выборки-хранения, перемножитель 7, интегратор 8, блок 9 привязки уровня, аттенюатор 10, формирователь 11 импульсов, счетный триггер 12 и элемент И 13. Достижение цели обеспечивается регулированием амплитуды измеряемого сигнала по определенному закону и формированием определенных временных границ регулирования амплитуды и интегрирования перемноженных сигналов, что позволяет свести к нулю в результирующем сигнале составляющие нелинейно изменяющегося напряжения. 2 ил.

9asJ

тате на перемножители 3 и 7 поступают соответственно сигналы

U ooswt; (1)

U sinoA . (2) Одновременно сигнал с выхода генератора 1 копии сигнала поступает на двухполупериодный формирователь 11 импульсов, в результате на одном из выходов формирователя 11 вырабатываются короткие импульсы в моменты нуль- переходов с положительной производной (у сигнала генератора I (фиг.2, Пт ) / на другом выходе формирователя - пос- 15 ледовательность импульсов в моменты нуль-переходов с.отрицательной производной сигнала генератора 1 (фиг.2,

10

U

). Короткие импульсы с выхода формирователя 11 поступают на вход

««

поступает на вход элемента И 13, на другой вход которого поступают короткие импульсы с формирователя 11, КоИзобретение относится к фазоизме- рительной технике и может быть использовано в радиотехнике при измерении фазы сигналов с нестационарным средним значением,,

Целью изобретения является повышение точности оценки фазы гармонического сигнала при наличии на входе нелинейного изменяющегося напряжения, т.е при нестационарности среднего значения сигнала (помехи).

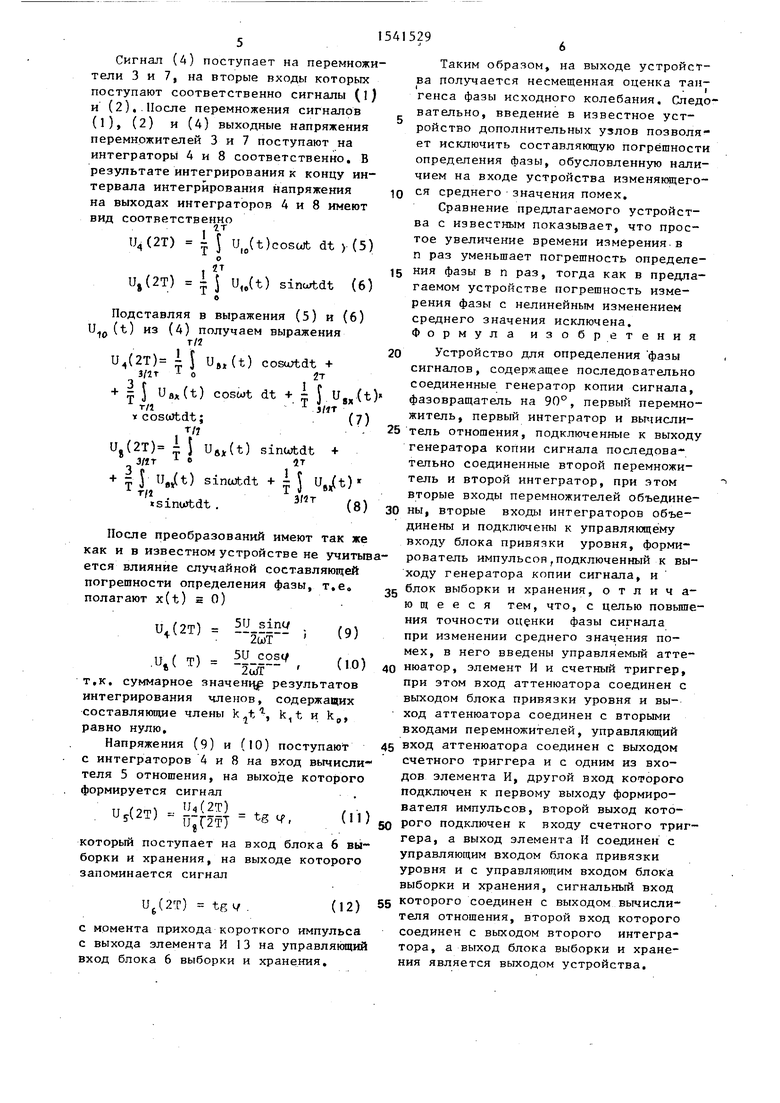

На фиг.1 показана структурная схема устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство для определения фазы сигналов содержит последовательно соединенные генератор 1 копии сигнала, фазовращатель 2 на 90°, перемножитель 3, интегратор 4, вычислитель 5 20 счетного триггера 12, с выхода тригге- отношения, блок 6 выборки и хранения, ра 12 сигнал типа меандр (фиг.2, U tz) а также подключенные к выходу генератора 1 копии сигнала последовательно соединенные перемножитель 7, интегратор 8, выходом подключенный к второ- 25 роткие импульсы (фиг.2, U13) с выхо- му входу вычислителя 5 отношения, да элемента И 13 с частотой, в два ра- при этом вторые входы первого 3 и вто- За меньшей частоты сигнала, поступа- рого 7 перемножителей объединены, пос- Ют на управляющий вход блока 9 привяз- ледовательно соединенные блок 9 при- Ки уровня, в результате чего сигнал вязки уровня, аттенюатор 10, выходом 30 на выходе блока 9 привязки уровня подключенный к объединенным входам привязывается к нулю. Сигнал на вы- перемножителей 3 и 7, а также подключенные к выходу генератора 1 копии сигнала последовательно соединенные формирователь 11 импульсов, счетный 35 триггер 12, элемент И 13, выходом подключенный к управляющему входу блока 9 привязки уровня, установочным входам интеграторов 4 и 8 и управляющему входу блока 6 выборки и хра- 40 нения, а управляющий вход аттенюатора 10 подключен к выходу счетного триггера 12, другой вход элемента И 13 подключен к второму выходу формирователя 11 импульсов, выход блока 6 выбор- Д5 кн и хранения является выходом устройства.

Устройство работает следующим образом.

ходе блока 9 привязки уровня имеет вид. ,.

U8x(t) U sin(urt -Ш ) + k,t +

+ ktt + kc + x(t) , (3) где k - определяется из условия paвенства сигнала (3) нулю в момент привязки уровней t m 41Гт/си (где т 1,2,

о О )

x(t) -составляющая, учитывающая

воздействие случайного шума.

Далее x(t) 0„

Одновременно импульс с выхода элемента И 13 поступает на установочные входы интеграторов 4 и 8, устанавливая тем самым последние в нулевое состояние, подготавливая их к очередному циклу работы (фиг,2)

Генератор 1 копии сигнала формиру- 50 ет гармоническое напряжение (фиг,2, U,) с частотой и), которое поступает на вход перемножителя 7 непосредственно, а на вход перемножителя 3 - через фазовращатель 2 на 90°. В резуль- 55 вил

U8x(t) при О Л Т/2, 3 Т/2 t 2Т, U«(t) (4).

|3UM(t) при Т/241 ЗТ/2.

Сигнал (3) поступает на нюатора 10, на управляющий рого поступает сигнал типа выхода триггера 12, в резу го сигнал с выхода аттенюа

тате на перемножители 3 и 7 поступают соответственно сигналы

U ooswt; (1)

U sinoA . (2) Одновременно сигнал с выхода генератора 1 копии сигнала поступает на двухполупериодный формирователь 11 импульсов, в результате на одном из выходов формирователя 11 вырабатываются короткие импульсы в моменты нуль- переходов с положительной производной (у сигнала генератора I (фиг.2, Пт ) / на другом выходе формирователя - пос- ледовательность импульсов в моменты нуль-переходов с.отрицательной производной сигнала генератора 1 (фиг.2,

U

). Короткие импульсы с выхода формирователя 11 поступают на вход

««

счетного триггера 12, с выхода тригге- ра 12 сигнал типа меандр (фиг.2, U tz) роткие импульсы (фиг.2, U13) с выхо- да элемента И 13 с частотой, в два ра- За меньшей частоты сигнала, поступа- Ют на управляющий вход блока 9 привяз- Ки уровня, в результате чего сигнал на выходе блока 9 привязки уровня привязывается к нулю. Сигнал на вы- поступает на вход элемента И 13, на другой вход которого поступают короткие импульсы с формирователя 11, Косчетного триггера 12, с выхода тригге- ра 12 сигнал типа меандр (фиг.2, U tz) роткие импульсы (фиг.2, U13) с выхо- да элемента И 13 с частотой, в два ра- За меньшей частоты сигнала, поступа- Ют на управляющий вход блока 9 привяз- Ки уровня, в результате чего сигнал на выходе блока 9 привязки уровня привязывается к нулю. Сигнал на вы-

счетного триггера 12, с выхода тригге ра 12 сигнал типа меандр (фиг.2, U tz) роткие импульсы (фиг.2, U13) с выхо- да элемента И 13 с частотой, в два ра За меньшей частоты сигнала, поступа- Ют на управляющий вход блока 9 привяз Ки уровня, в результате чего сигнал на выходе блока 9 привязки уровня привязывается к нулю. Сигнал на вы-

ходе блока 9 привязки уровня имеет вид. ,.

U8x(t) U sin(urt -Ш ) + k,t +

+ ktt + kc + x(t) , (3) где k - определяется из условия paвил

венства сигнала (3) нулю в момент привязки уровней t m 41Гт/си (где т 1,2,

о О )

x(t) -составляющая, учитывающая

воздействие случайного шума.

Далее x(t) 0„

Одновременно импульс с выхода элемента И 13 поступает на установочные входы интеграторов 4 и 8, устанавливая тем самым последние в нулевое состояние, подготавливая их к очередному циклу работы (фиг,2)

Сигнал (3) поступает на вход аттенюатора 10, на управляющий вход которого поступает сигнал типа меандр с выхода триггера 12, в результате чего сигнал с выхода аттенюатора имеет

Сигнал (4) поступает на перемножители 3 и 7, на вторые входы которых поступают соответственно сигналы (l) и (2). После перемножения сигналов (1), (2) и (4) выходные напряжения перемножителей 3 и 7 поступают на интеграторы 4 и 8 соответственно, В результате интегрирования к концу интервала интегрирования напряжения на выходах интеграторов 4 и 8 имеют

вид соответственно гт

и4(2Т) - j Ule(t)costA dt ) (5)

о 2T

U4(2T) i j U,e(t) sinwtdt (6)

О

Подставляя в выражения (5) и (6) U.n (t) из (4) получаем выражения

Т/2

U(2T) j UB, (t) cosurtdt +

з/i т

2т

+ - J Uflx(t) coswt dt + J UgJ((t

r/l

cosuftdt; fit

3I1T

(7)

U,(2T) i J UM(t) sinwtdt + 8 лят L IT

+ f J ) sincotdt + | J Ujt)

T/l

«sinwtdt.

WT

(8)

После преобразований имеют так же как и в известном устройстве не учитывется влияние случайной составляющей погрешности определения фазы, т.е полагают x(t) s О)

U,(2T) Styinc, . (9)

,, I ггЛ 5U COSt/, .

1 2ЙТ (10) т.к. суммарное значение результатов

интегрирования членов, содержащих составляющие члены k.tг, k,t и k0 равно нулю.

Напряжения (9) и (10) поступают с интеграторов 4 и 8 на вход вычислителя 5 отношения, на выходе которого формируется сигнал

U(2T) 0$8 в

который поступает на вход блока 6 выборки и хранения, на выходе которого запоминается сигнал

Ut(2T) tg v

(12) 55

с момента прихода короткого импульса с выхода элемента И I3 на управляющий вход блока 6 выборки и хранения.

д

15

20

)

25

30

а

40

45

50

55

Таким обраэом, на выходе устройства получается несмещенная оценка тангенса фазы исходного колебания. Следовательно, введение в известное устройство дополнительных узлов позволяет исключить составляющую погрешности определения фазы, обусловленную наличием на входе устройства изменяющегося среднего значения помех.

Сравнение предлагаемого устройства с известным показывает, что простое увеличение времени измерения в п раз уменьшает погрешность определения фазы в п раз, тогда как в предлагаемом устройстве погрешность измерения фазы с нелинейным изменением среднего значения исключена. Формула изобретения

Устройство для определения фазы , сигналов, содержащее последовательно соединенные генератор копии сигнала, фазовращатель на 90°, первый перемножитель, первый интегратор и вычислитель отношения, подключенные к выходу генератора копии сигнала последовательно соединенные второй перемножитель и второй интегратор, при этом вторые входы перемножителей объединены, вторые входы интеграторов объединены и подключены к управляющему входу блока привязки уровня, формирователь импульсов,подключенный к выходу генератора копии сигнала, и блок выборки и хранения, о т л и ч а- ю щ е е с я тем, что, с целью повышения точности оценки фазы сигнала при изменении среднего значения помех, в него введены управляемый аттенюатор, элемент И и счетный триггер, при этом вход аттенюатора соединен с выходом блока привязки уровня и выход аттенюатора соединен с вторыми входами перемножителей, управляющий вход аттенюатора соединен с выходом счетного триггера и с одним из входов элемента И, другой вход которого подключен к первому выходу формирователя импульсов, второй выход которого подключен к входу счетного триггера, а выход элемента И соединен с управляющим входом блока привязки уровня и с управляющим входом блока выборки и хранения, сигнальный вход которого соединен с выходом вычислителя отношения, второй вход которого соединен с выходом второго интегратора, а выход блока выборки и хранения является выходом устройства.

1

Ј

,

5г

Составитель М. Катанова

Редактор И. Шулла Техред М.Дидык

Заказ 277Тираж 546Подписное

ВНИИПИ Государствечного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Г

«

Ј

111

Hi

Ь «ч Q

gg

I

«7

A

4J

г,Корректор М, Самборская

| 1972 |

|

SU410331A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения фазы сигналов | 1986 |

|

SU1345134A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-02-07—Публикация

1988-06-23—Подача