подключен ко второму информационному входу блока наделения дискретной информафи.

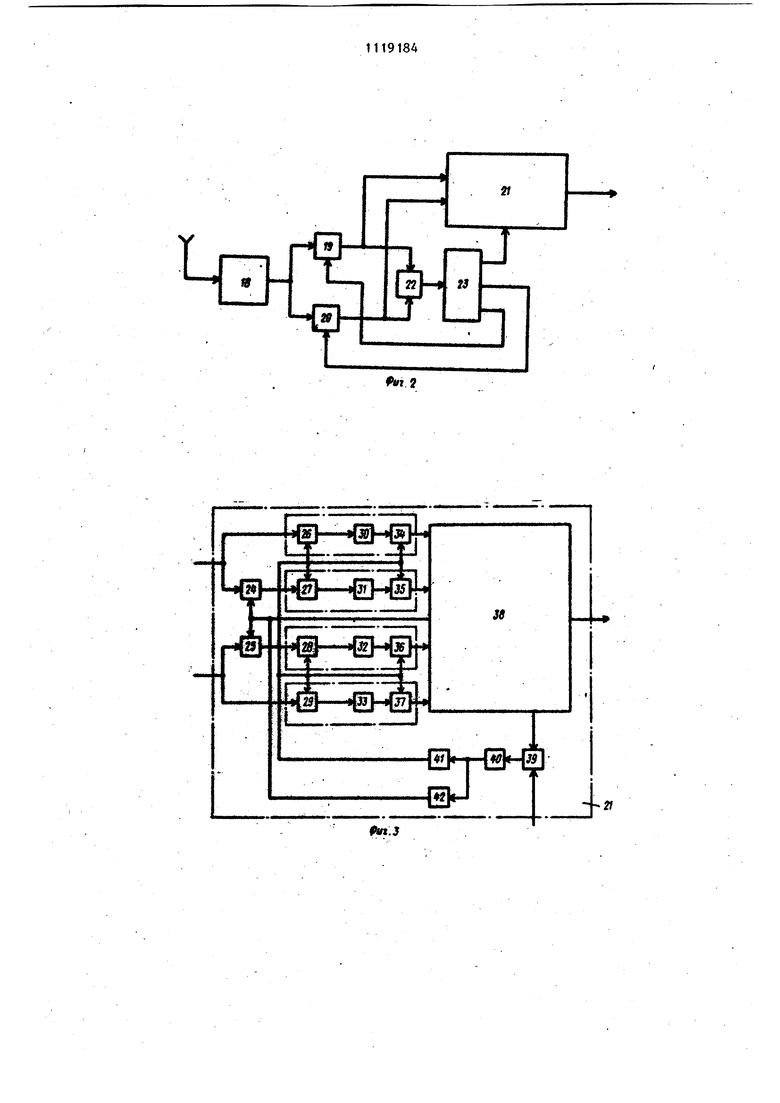

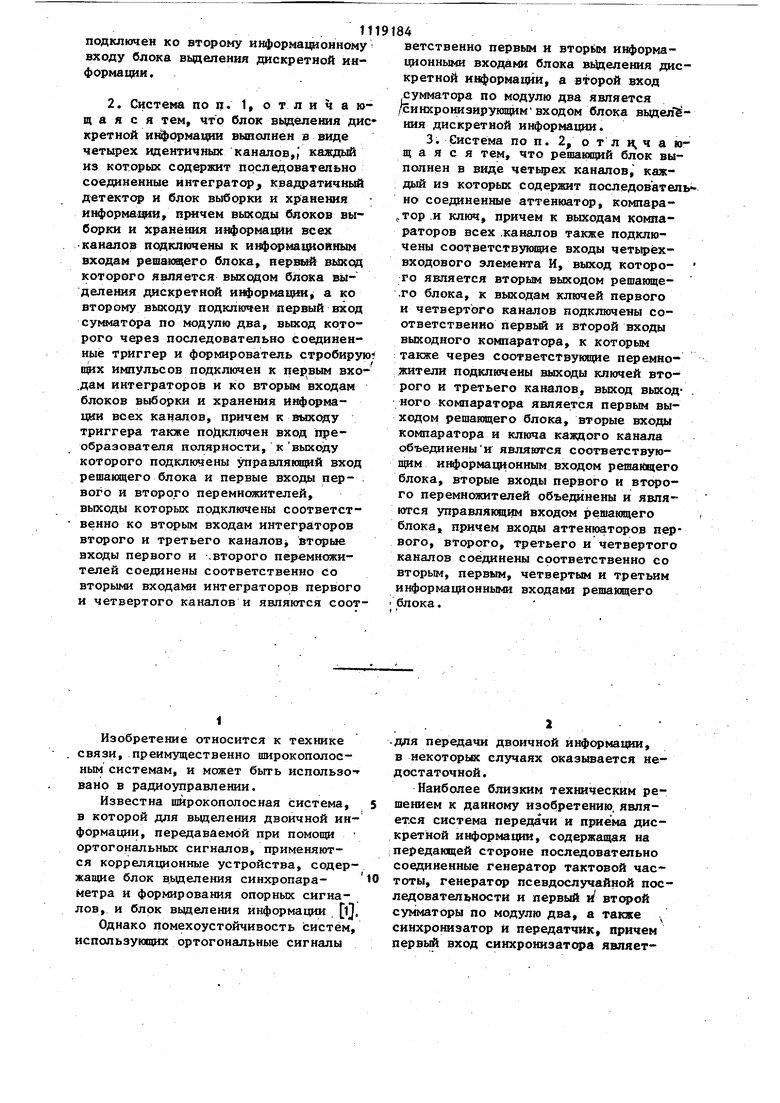

2. Система по п, 1, о т л и ч а ющ а я с я тем, что блок ввделения дискретной информадаи вьшолнен в виде четырех идентичных каналов,, каждьй из которых содержит последовательно соединенные интегратор квадратичный детектор и блок выборки и хранения информаЩШ, П1жчем выходы блоков выборки и хранеш1я информахр и всех каналов подключены к инфсфма19 ойным входам решакщего блока, вервшй выхрд которого является выходом блока выделеьшя дискретной информахщи а ко второму выходу подключен первый вход сумматора по модулю два, выход которого через последовательно соединенные триггер и формирователь стробирую npix импульсов подключен к вхо.дам интеграторов и ко вторым входам блоков выборки и хранения информации всех каналов, причем к выходу триггера также подключен вход преобразователя НОЛЯрНОСТИ, к BbKOJDiy

которого подключены управляюшрий вход решакяцего блока и первые входы первого и второго перемножителей, выходы которых подключены соответственно ко вторым входам интеграторов второго и третьего каналов вторые входы первого и .второго перемножителей соединены соответственно со вторыми входаьм интеграторов первого и четвертого каналов и являются соответственно первым и вторьш информационными входакв блока в|Дцеления дискретной информации, а второй вход сумматора по модулю два является синхронизирующимвходом блока вьздел ния дискретной информации.

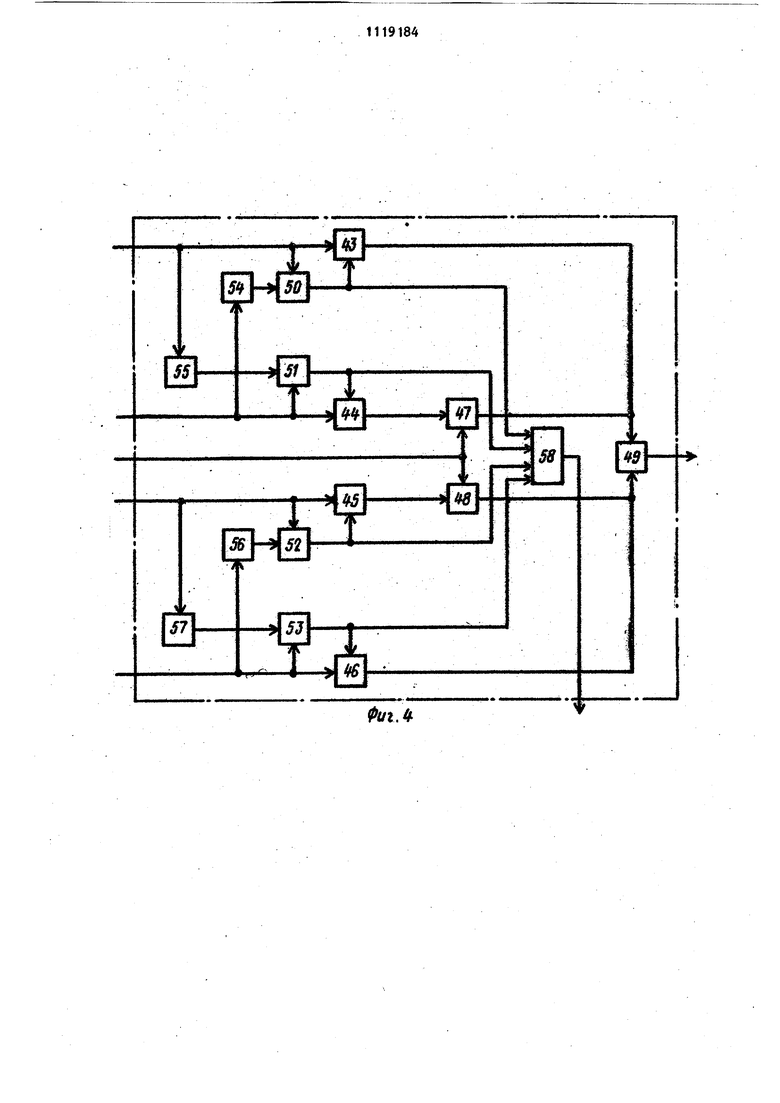

3. Система по п. 2, о т л i ч а ющ а я с я тем, что решакяций блок выполнен в виде четьфех каналов, каждый из которых содержит последователь но соединеншле аттенюатор, компаратор ,и ключ, причем к выходам компараторов всех .каналов также подключены соответствующие входы четь1рёхвходового элемента И, выход которо- го является вторым выходом решакице.го блока, к выходам ключей первого и четвертого каналов подключены соответственно первьй и второй входы выходного компаратора, к которым также через соответствующие перемно.жители подключены выходы ключей второго и третьего каналов, выход выход- . ного компаратора является первым выходом решающего блока, вторые входы компаратора И ключа каждого канала объединеныи являются соответствующим информационным входом решайхцего блока, вторые входы первого и второго перемножителей объединены и являются управлякщим входом решающего блока, причем входы аттенюаторов первого, второго, третьего и четвертого каналов соединены соответственно со вторым, первым, четвертым и третьим информационными входами решаницего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1986 |

|

SU1317683A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПРИ МНОГОЛУЧЕВОМ РАСПРОСТРАНЕНИИ РАДИОВОЛН | 1992 |

|

RU2099891C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1976 |

|

SU1840434A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Адаптивный приемник сигналов минимальной частотной манипуляции | 1989 |

|

SU1835611A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840118A1 |

| Радиолиния с псевдослучайными сигналами | 1981 |

|

SU1054917A1 |

| УСТРОЙСТВО ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1982 |

|

SU1840540A1 |

| Система радиосвязи с псевдослучайными сигналами | 1987 |

|

SU1501293A1 |

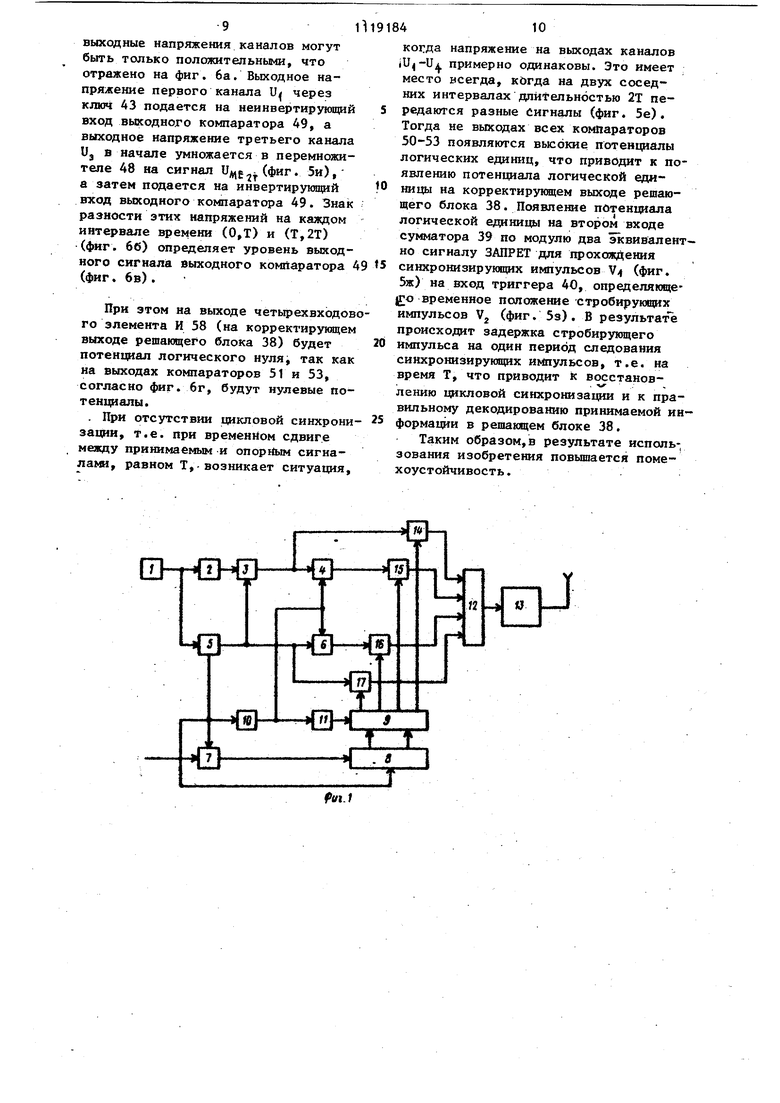

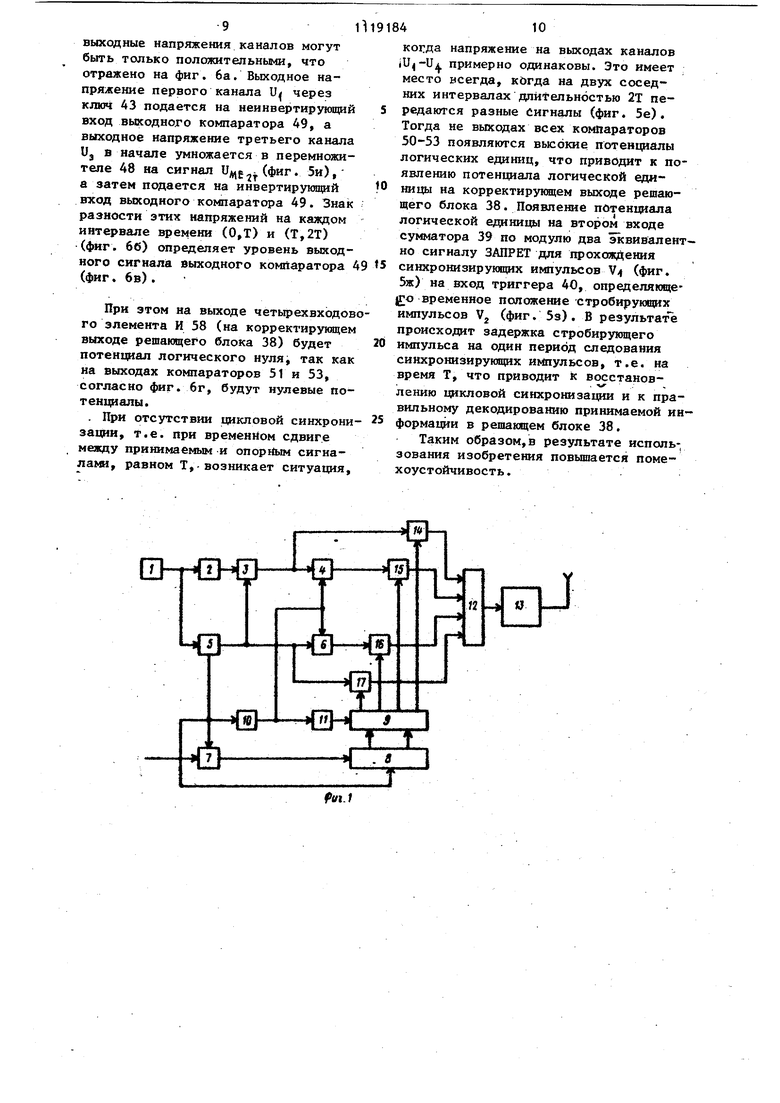

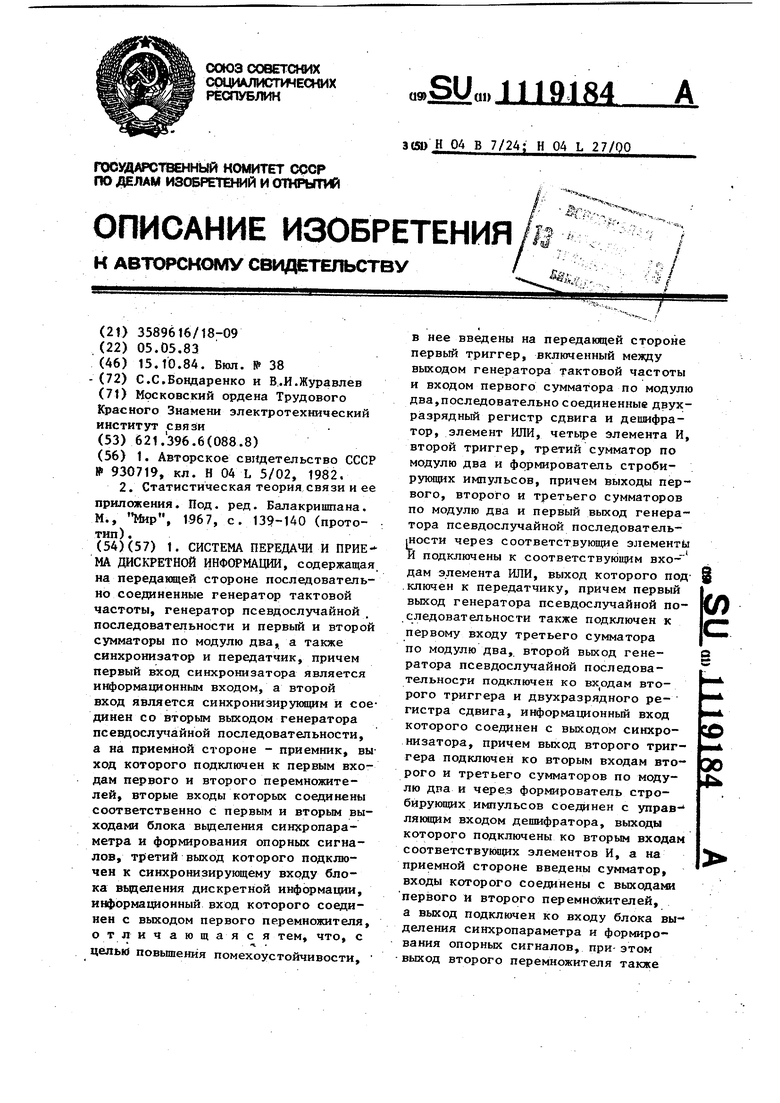

1. СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ, содержащая, иа передающей стороне последовательно соединенные генератор тактовой частоты, генератор псевдослучайной , последовательности и первый и второй сумматоры по модулю два, а также синхронизатор и передатчик, причем первый вход синхронизатора является информационным входом, а второй вход является синхронизирующим и соединен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне - приемник, выход которого подключен к первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с первым и вторым выхода1 01 блока вьзделения синхропараметра и формирования опорных сигналов, третий выход которого подключен к синхронизирующему входу блока вьделения дискретной информации, информационный вход которого соединен с выходом первого перемножителя, отлич ающая с я тем, что, с целью повьппения помехоустойчивости, в нее введены на передающей стороне первый триггер, включенный между выходом генератора тактовой частоты и входом первого сумматора по модулю два,последовательно соединенные двухразрядный регистр сдвига и дешифратор, элемент ИЛИ, четыре элемента И, второй триггер, третий сумматор по модулю два и формирователь стробирующих импульсов, причем выходы первого, второго и третьего сумматоров по модулю два и первый выход генератора псевдослучайной последовательности через соответствующие элементы « подключены к соответствующим входам элемента ИЛИ, выход которого под.ключен к передатчику, причем первый выход генератора псевдослучайной последовательности также подключен к первому входу третьего сумматора по модулю два, второй выход генератора псевдослучайной последовательносуи подключен ко второго триггера и двухразрядного регистра сдвига, информационный вход СО которого соединен с выходом синхронизатора, причем выход второго тригX) гера подключен ко вторым входам второго и третьего сумматоров по моду4 лю дпа и чере.з формирователь стробирующих импульсов соединен с управляющим входом дешифратора, выходы которого подключены ко вторым входам соответствунмцих элементов И, а на приемной стороне введены сумматор, входы которого соединены с выходами первого И второго перемножителей, а выход подключен ко входу блока вы- деления синхропараметра и формирования опорных сигналов, при-этом выход второго перемножителя также

1

Изобретение относится к технике связи, преимущественно широкополосным системам, и может быть использо- вано в радиоуправлении.

Известна широкополосная система, в которой для вьщеления двоичной информации, передаваемой при помощи ортогональных сигналов, применяются корреляционные устройства, содержащие блок вьщеления синхропарайетра и формирования опорных сигналов, и блок вьщеления информац(ш lj.

Однако помехоустойчивость систем, использующих ортогональные сигналы

.дпя передачи двоичной информации, в некоторык случаях оказывается недостаточной .

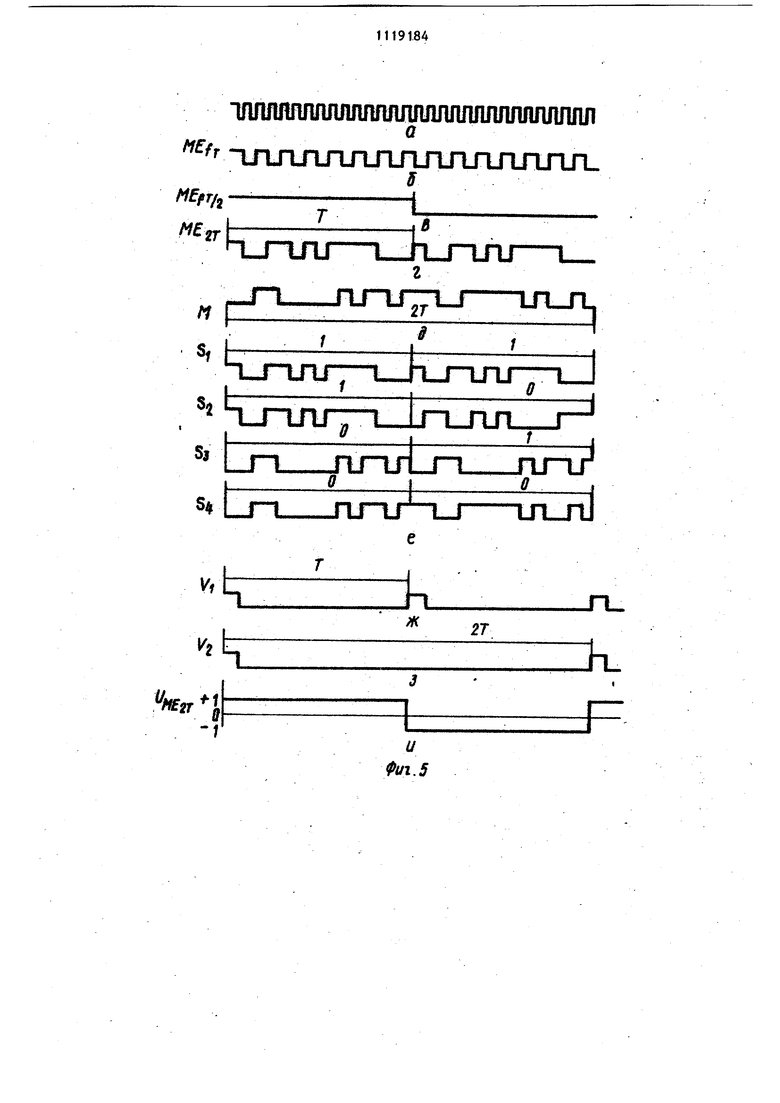

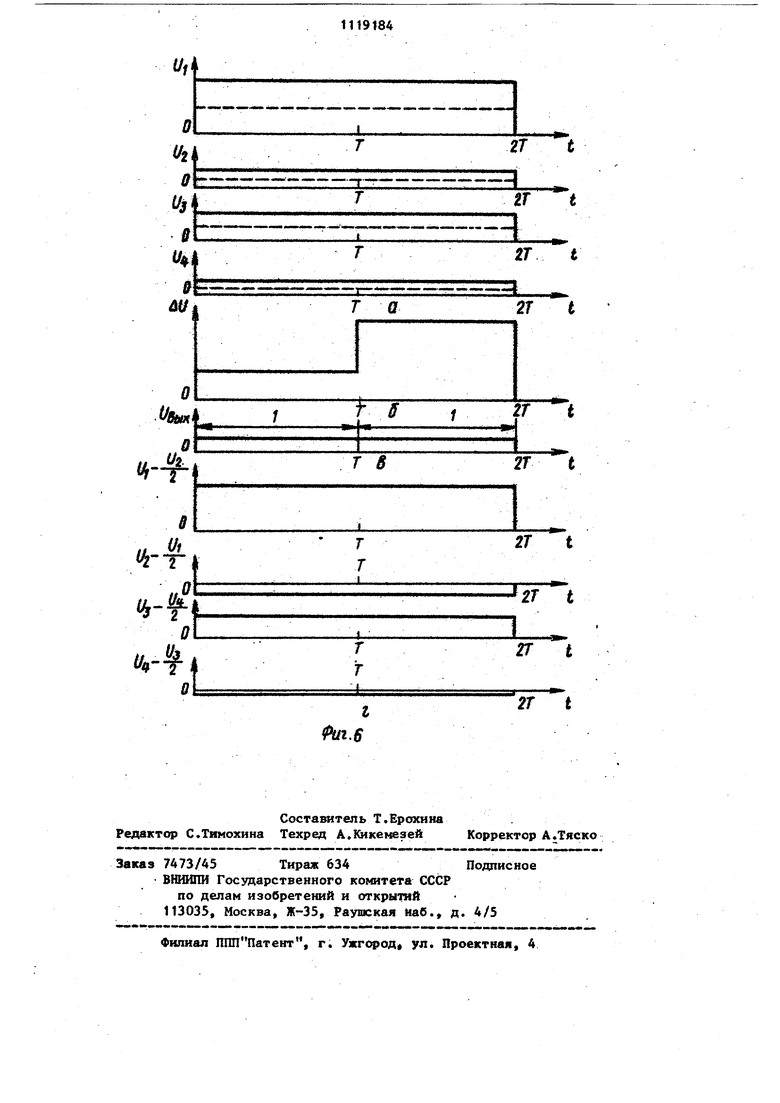

Наиболее близким техническим решением к данному изобретению, является система передачи и приема дискретной информации, содержащая на ;передающей стороне последовательно соединенные генератор тактовой частоты, генератор псевдослучайной последовательности и первый 1 сумматоры по модулю два, а также / синхронизатор и передатчик, причем первый вход синхронизатора являетУ.Я информационным входом, а второй вход является синхронизирующим и coe динен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне - приемник, вы ход которого подключен к первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с первым и вторым выходаьо блока вьщеления синхропараметра и формирования опорных сигна.лов, третий выход которого подключен к синхронизирующему входу блока выде ления дискретной информации, информа ционный вход которого соединен с выходом первого перемножитепя . Однако реальная помехоустойчивост такой системы передачи и приема дискретной информации невысока. Цель изобретения - повышение помехоустойчивости. Для .достижения указанной цели в систему передачи и приема дискретной информации, содержащую на передающей стороне последовательно соединенные генератор тактовой частоты, генерато псевдослучайной последовательности и первый и второй сумматоры по модулю два, а также синхронизатсф и пере датчик причем первый вход синхрониз тора является информационным входом, а второй вход является синхронизируюощм и соединен со вторым выходом генератора псевдослучайной последовательности, а на приемной стороне приемник, выход которого подклкМен . к первым входам первого и второго перемножителей, вторые входы которых соединены соответственно с Первым и вторым выходами блока вьщеления синхропараметра и формирования опсфных сигналов,третий выход которого подключен к синхронизирующему входу бло ка вьщеления дискретной информахцт, информационный вход которого соединен с выходом первого перемножителя, , введены на передакнцей стороне первый триггер, включенный мбжду выходом генератора тактовой частоты и входом первого сумматора по модулю два, последовательно соединенные дву разрядный регистр сдвига и дешифратор, элемент ШШ, четыре элемента И, второй триггер, третий сумматор по модулю два и формирователь стробирующих импульсов, причем выходы первого, второго и третьего сумматоров по модулю два и первый выход генератора псевдослучайной последовательности через соответствующие элементы И подключены к соответствующим входам элемента ИЛИ, выход которого подключен к передатчику, причем первый выход генератора псевдослучайной последовательности также подключен к первому входу третьего сумматора по модулю два, второй выход генератора псевдослучайной последователь йости подключен ко входам второго триггера и двухразрядного регистра сдвига, информационный вход которого соединен с выходом .синхронизатор а, причем выход второго триггера подключен ко вторым входам второго и третьего сумматоров по модулю два и через формирователь стробирукяцих импульсов соединен с управлякицим входом дешифратора, выходы которого подключены ко вторым входам соответствую цих элементов И, а на приемной стороне введен сумматор, входы которого соединены с вьпсодами первого и второго перемножителей,.а выход подключен ко входу блока вьщеления синхропараметра и формирования опорных сигналов, при этом выход второго перемножителя также подключен ко второму информационному входу блока выделения дискретной информации. Блок вьщеления дискретной информа.ции вьнтолнен в виде четьфех идентичных каналов, каждый из которых содержит последовательно соединенные интегратор, квадратичный детектор и блок выборки и хранения информации, причем выходы блоков выборки и хранения информации всех каналов подключены к информационным входам решающего блока, первый выходкоторого является выходом блока вьиеления дискретной информации, а ко второму выходу подключен первый вход сумматора по модулю два, выход которого через последовательно соединенные триггер и формирователь стробирующих импульсов подключен к первым входам интеграторов и ко вторым входам блоков выборки и хранения информации всех каналов, причем к выходу триггера также Подключен вход преобразователя полярности, к выходу которого подключены управляющий вход решающего блока и первые входы первого и второго перемножителей, выходы которых подключены соответственно ко вторым входам интеграторов второго н тре- тьего каналов, вторые входы первого и второго перемножителей сЬединены соответственно со вторыми входами интеграторов первого и четвертого каналов и являются соответственно первым и вторым информационными входами блока ввделения дискретной инфррма1ЦШ, а второй вход сумматора по модулю два является Синхронизирующим входом блока вьщеления дискретной информации. Решаюпщй блок выполнен в виде четырех каналов, каждЕ из которых содержит последовательно соединенные Аттенюатор, компаратор и ключ, при-J чем к выходам компараторов всех каналов также подключены соответствующие входы четырехвходового элемента И, выход которого является вторым выходом решакицего блока, к выходам ключей первого и четвертого каналов подключены соответственно первый и второй входы выходного компаратора к которым также через соответствукнци перемиожители.подключены выходы ключей второго и третьего каналов, выход выходного компаратора является первы выходом решакщего блока, вторые входы компаратора и ключа каждого канала объединены и являются с оответству щим информационным входом решакщего блока, вторые входы первого и второго перемножителей объединены и являются управляющим входом решающего бл ка, причем входы аттенюаторов первого, второго,третьего и четвертого каналов соединены соответственно со вторым, первым, четвертым и третьим информационными входами решаняцего блока. На фиг. 1 представлена структурна электрическая схема передающей части системы передачи и приема дискретной информации /на фиг. 2 -структурная электрическая схема приемной . части системы передачи и приема дие кретной информации} на фиг. 3 - стру турная схема блока ввделения дискрет ной информации; на фиг, 4 - структур ная схема решающего блока на фиг. 5 и 6 - временные диаграммы, поясняющие работу системы. Устройство передачи и приема дискретной информации содержит на пере дающей стороне генератор 1 тактовой частоты, первый триггер 2, первый сумматор 3 по модулю-два,второй сумматор 4 по модулю два, генератор 5 1 4 псевдослучайной последовательности, третий сумматор 6 по модулю два, синхронизатор 7, двухразрядный регистр сдвига 8,дешифратор 9, второй триггер 10, формирователь 11 стробирующих импульсов, элемент ИЛИ 12, передатчик 13, элементы И 14--17, а на приемной стороне - приемник 18, первьш перемножитель 19, второй перемножитепь 20, блок 21 вь(целеиня дискретной информации, сумматор 22, блок 23 выделения синхропараметра и формирования опорных сигналов. Блок 21 вьщеления дискретной информации содержит первый и второй перемножители 24 и 25, интеграторы 26-29, квадратичные, детекторы , блоки 34-37 выборки и хранения информации, решанщий блок 38, сумматор 39 по модулю два, триггер 40, фор- , мирователь 41 стробирующих импульсов, преобразователь 42 полярности. Решающий блок 38 содержит ключи 3-46, перемножители 47-48 выходной компаратор 49, компараторы 50-53, аттенюаторы 54-57, четырехвходовый элемент И 58. Система передачи и приема дискретной информации работает следунлцим образом. Сигнал тактовой частоты МЕ(фиг. 5а-5б) с выхода генератора 1 одновременно постзшает на входы первого триггера 2 и генератора 5 псевдослучайной последовательности, на входах которых формируются сигналы Щ (меандр полутактовой частоты)J М (т последовательность) и Vf (сигнал синхронизации двоичных символов, поступающих на вход синхронизатора 7). Сигнал V;j также поступает на вход второго триггера 10, на выходе которого формируется сигнал Ш (меандр с периодом, радным удвоенному периоду следования двоичных символов). В результате операций суммирования по модулю два сигналов М, и выходах сумматоров 3, 4, о образуются ,три различных сигнала с периодом 2Т. В сочетании с сигналом М они образуют ансамбль из четырех ортого«нальных сигналов с пе1«одом 2Т (фиг. 5е). Дв жчные символы 1 и О, поступакяцие на основной вход синхронизатора 7, записываются я двyxpaзpядньiй регистр сдвига 8 в моменты (времени, кратные периоду следования двоичных символов кТ (к 1,2,3,...). Комбинация двоичных символов, записанная в регистр, в моменты времени, кратные удвоенному периоду еле дова1ШЯ двоичных символов 2кТ (к 1,2,3,...)« поступает в дешифратор 9, который определяет номер полученной комбинации и вьщает сигнал в виде потенциала логической единицы н второй вход соответствующего элемента И в течение всего интервала времени (0,2т). В результате один из сигналов S.-S, соответствующий данной комбинации двоичных символов, проходит на вход радиопередающего устройства, где осуществляется модуляция фазы несущего колебания данным сигналом, перенос спектра полученного фазоманипулированного сигнала в нужный диапазон частот и усиление по мощности. Таким образом, как следует из фиг 5в-5е, выходные сигналы Sj и Sj сумматоров и 6 формируются из сигналов М и М, снимаемых с выходов генератора 5 псевдослучайной последовательности и первого сумматора 3 по модулю два, посредством дополницельной инверсной манипуляции сиг- J налом . Поэтому на приемной стор не (фиг. 2) при форм{{ровага1и опорных сигналов, подаваемых на вторые входы первого 19 и-второго 20 перемножителей, достаточно использовать только эти два сигнала, так как независимо от конкретного варианта сигнала при наличии рассогласования между приним емым и опорным сигналами на выходе сумматора 22 будзгт присутствовать с полутактовой частотой составляюйще -|-или fnyl-fS где tnn - некоторая промежуточная частота, амплитуда и фаза которых определяется степенью рассогласования. В блоке 23 осуществляется фильтрация указанных составляющих и за;Тем в результате леремкожения этих составляющих либо при возведении квадрат любой из них Устраняется инверсная манипуляция и после фильтрацЕ1и вБщеляется сигнал тактовой час трты М, который используется для синхронизации опорных сигналов. Благодаря йеремножителям 24 и 25 в блоке 21 вьщепения даескретной им формации (фиг. 3) осуществляется 1 48 дополнительная инверсная манипуляция выходных сигналов перемножителей 19 , MEjT Ь формии 20 сигналов вькоде преобразователя поруемым на лярности 42 из выходного сигнала Ж ттриггера 40. Предположим, что на интервале (0,2Т) передавался сигнал S|. Тогда при нал1|чии цикловой синхронизации в результате корреляционной обработки, входной смесу, состоящей из полезного сигнала S(t), и шума n(t) y(t) S(t)(t) 0 t$ 2Т на выходах каналов (с учетом запаздывания на 2Т) появляются напряжения /(л., представляющие собой продукты взаимной корреляции между y(t) и соответствующими опорными сигналами (фиг. 6а). Эти напряжения поступают на информационные входы решающего блока 38 (фиг. 4) и далее - на коммути руемые входы ключей 43-46 и на неинвертирующие входы кo шapaтopoв 50-53, На инвертирующие входы компараторов поступают напряжения с выходов соответствующих аттенюаторов 54-57. Знак разности этих напряжений (фиг. 6г) определяет состояние сосответствующих ключей 43-46. При положительном знаке на выходе компаратора появляется потенциал логической единицы, при отрицательном - логического нуля. Следовательно, ключ, на управляющем входе которого появляется потенщал логической единицы, открыт, и j выходное напряжение данного канала поступает на соответствук щий вход выходного компаратора 49 либо непосредственно, либо через соответствуииций перемножитель 47, 48. Последние необходимы для окончательного вынесения решения о принятом сигнале и для декодирования принятой информации, т.е. для восстановления исходной последовательности воичных символов. Следовательно, на выходе выходного к шаратора 49 (выходе радиолинии) ормируется сразу переданная послеовательность двоичных символов в еальнсн4 масштабе времени (фиг. 6в). Это достигается следукнцим образом. Так как в каналах обработки стоят квадратичные детекторы 30-33, то

выходные напряжения каналов могут быть только положительными, что отражено на фиг. 6а. Выходное напряжение первого канала U через ключ 43 подается на неинвертирукшщй вход выходного компаратора 49, а выходное напряжение третьего канала Uj в начале умножается в перемножителе 48 на сигнал (фиг. 5и), а затем подается на инвертирующий вход вьЕходного компаратора 49. Знак разности этих напряжений на каждом интервале времени (О,Т) и (Т,2Т) (фиг. 66) определяет уровень выходного сигнала выходного компаратора (фиг. 6в). .При этом на выходе четырехвходового элемента И 58 (на корректирующем выходе решающего блока 38) будет20 потенциал логического нуля, так как на выходах компараторов 51 и 53, согласно фиг. 6г, будут нулевые потенциалы. . При отсутствии цикловой синхрони-25 зафи, т.е. при временном сдвиге между принимаемым и опорным сигналами, равном Т,-возникает ситуация,

когда напряжение на выходах каналов . примерно одинаковы. Это имеет место всегда, кЬгда на двух соседних интервалах длительностью 2Т передаются разные сигналы (фиг. 5е). Тогда не выходах всех компараторов 50-53 появляются высокие потенциалы логических единиц, что приводит к появлению потенциала логической единицы на корректирунщем выходе решающего блока 38. Появление потенциала логической едини1Д 1 на втором входе сумматора 39 по модулю два эквивалентно сигналу ЗАПРЕТ для прохождения синхронизирующих импульсов У, (фиг. 5ж) на вход триггера 40, определяюще временное положение стробирующих импульсов V (фиг. 5з). В результате происходит задержка стробирующего импульса на один период следования синхронизирующих импульсов, т.е. на время Т, что приводит к восстановлению цикловой синхронизации и к прааильному декодированию принимаемой информац|1и в решающем блоке 38. Таким образом,в результате использования изобретения повышается помехоустойчивость.

тшшппшишшшгаш/шппллгашпшш

JглJ JlJгглJглJгплJlJ

Q

tH

s

JLTU LJ

tr

LTLJll

e

k

ru

ж

2T

k

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для корреляционного приема сложных фазоманипулированных сигналов | 1980 |

|

SU930719A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Статистическая теория связи и ее приложения | |||

| Под | |||

| ред | |||

| Балакришпана | |||

| М., Мир, 1967, с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

Авторы

Даты

1984-10-15—Публикация

1983-05-05—Подача