Изобретение относится к контрольно-измерительной технике и может быт использовано при производстве и контроле твердотельных интегральных микросхем с диодной изоляцией, выполненных на базе биполярных или полевых транзисторов.

Цель изобретения - повышение быстродействия контроля и упрощение его реализации за счет обеспечения возможности одновременного контроля целостности всех выводов твердотельной интегральной микросхемы с диодной изоляцией при одинаковом значении испытательного напряжения.

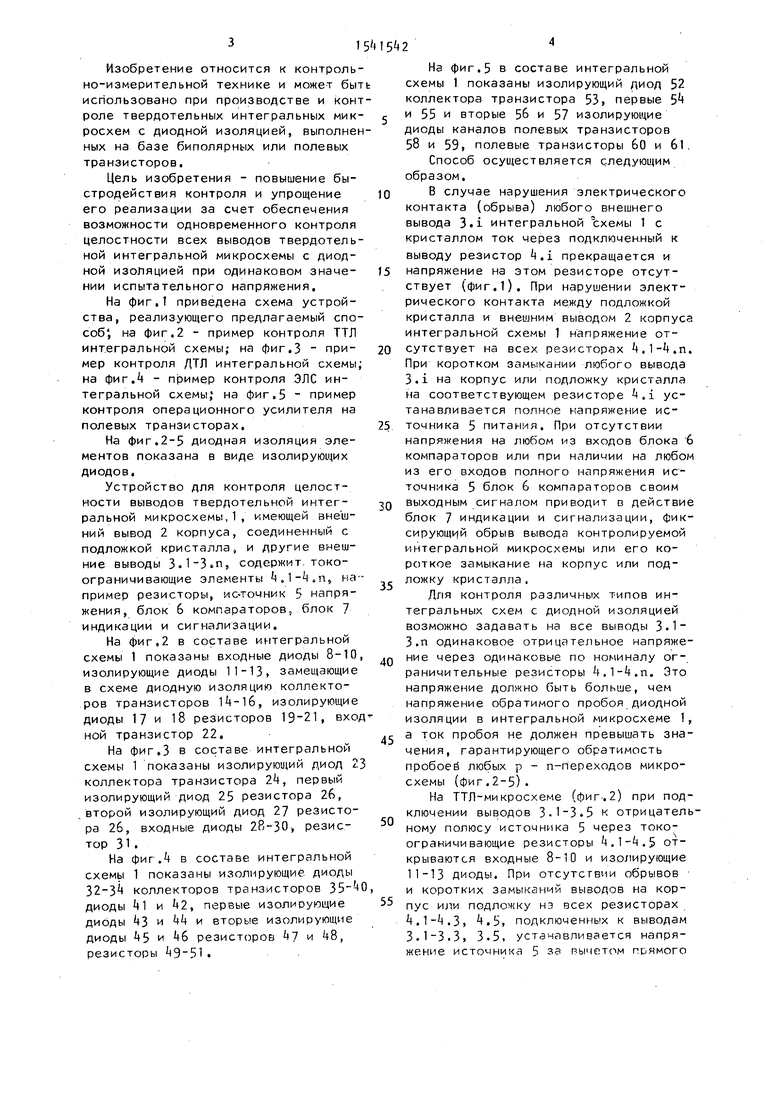

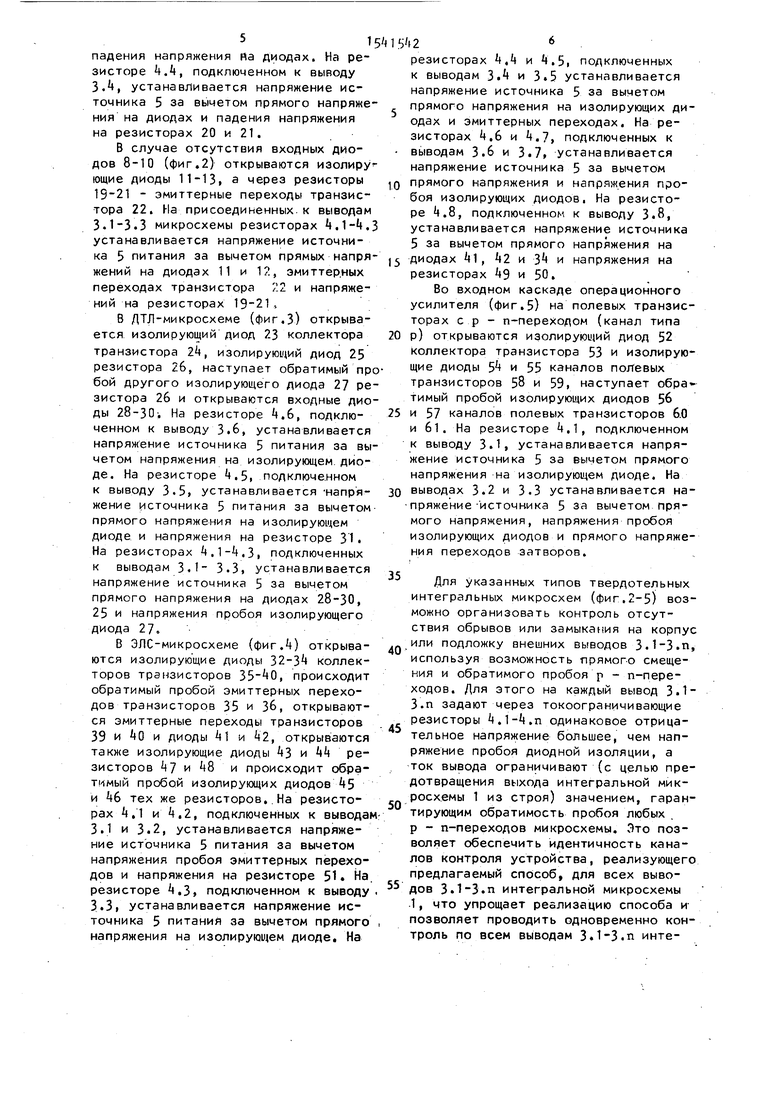

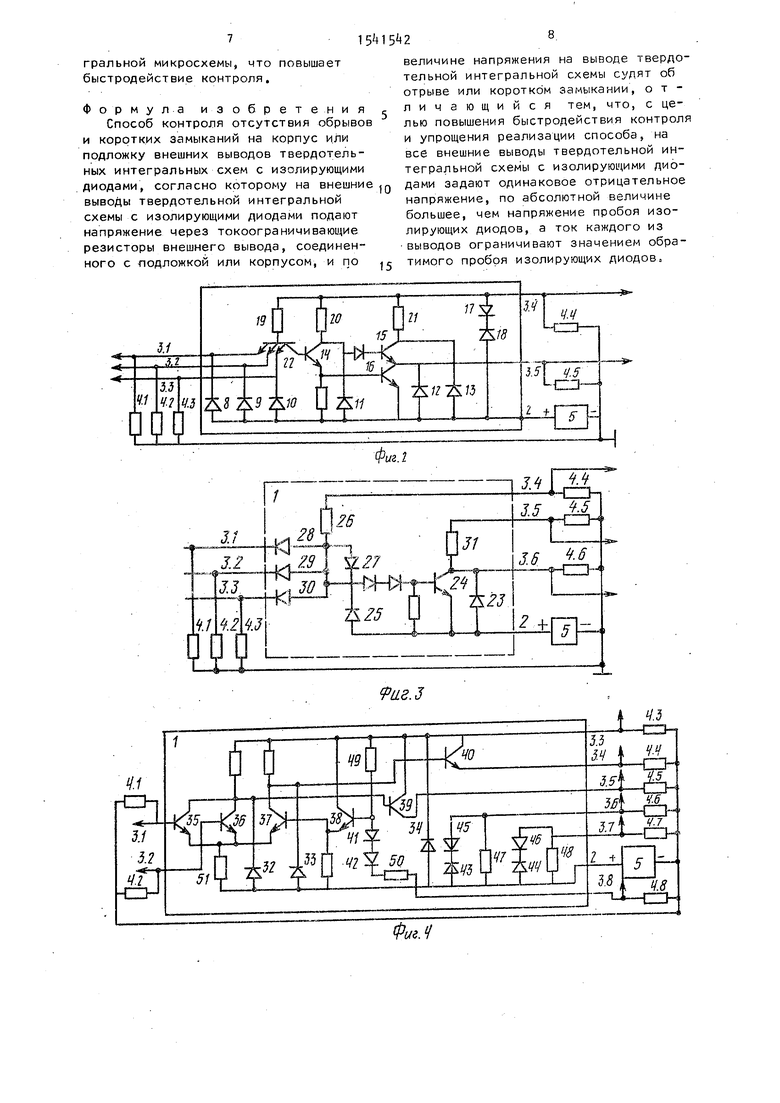

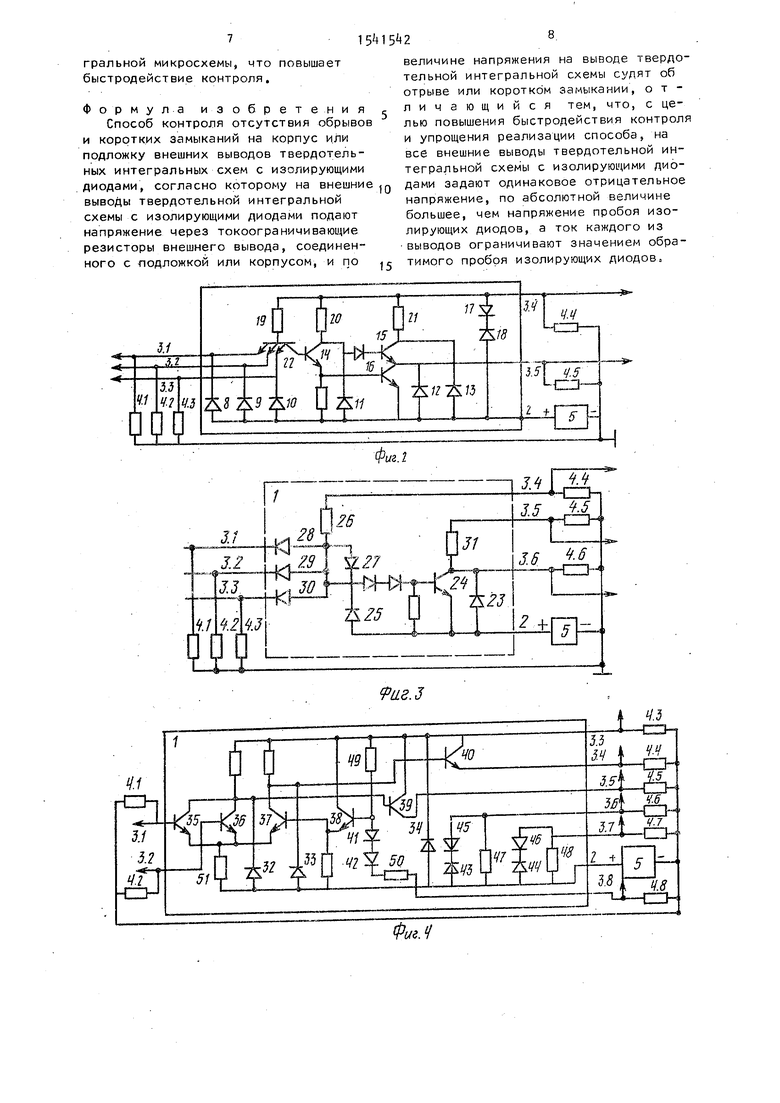

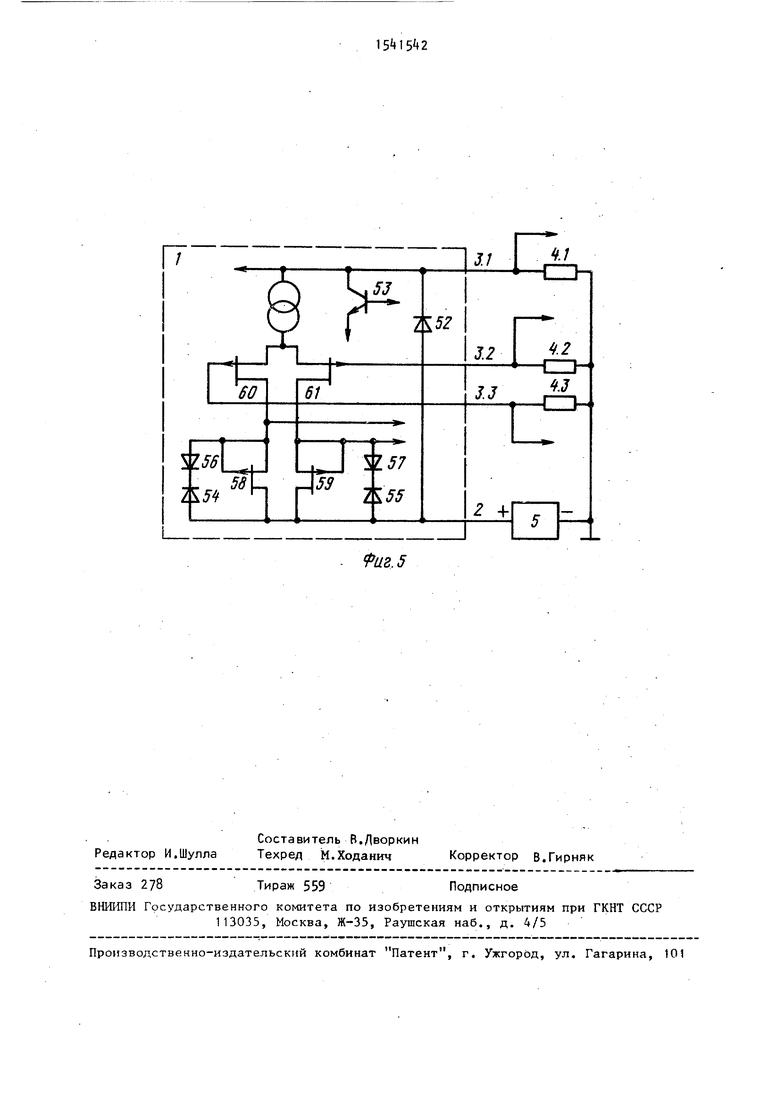

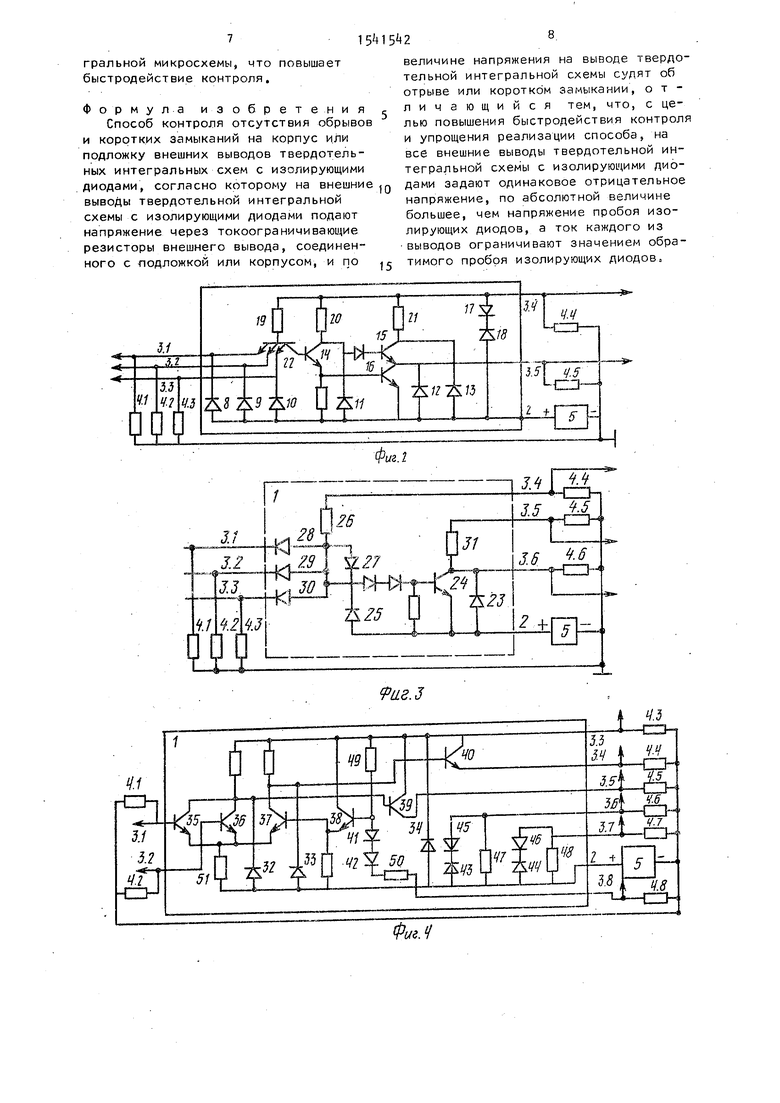

На фиг.1 приведена схема устройства, реализующего предлагаемый способ , на фиг.2 - пример контроля ТТЛ интегральной схемы; на фиг.З - пример контроля ДТЛ интегральной схемы; на фиг.4 - пример контроля ЭЛС интегральной схемы; на фиг.5 - пример контроля операционного усилителя на полевых транзисторах.

На фиг.2-5 диодная изоляция элементов показана в виде изолирующих диодов.

Устройство для контроля целостности выводов твердотельной интегральной микросхемы,, имеющей внешний вывод 2 корпуса, соединенный с подложкой кристалла, и другие внешние выводы 3..п, содержит токо- ограничивающие элементы 4.1-4.п5 например резисторы, источник 5 напряжения, блок 6 компараторов, блок 7 индикации и сигнализации,

На фиг,2 в составе интегральной схемы 1 показаны входные диоды 8-10, изолирующие диоды 11-13, замещающие в схеме диодную изоляцию коллекторов транзисторов 14-16, изолирующие диоды 17 и 18 резисторов , вход ной транзистор 22.

На фиг.З в составе интегральной схемы 1 показаны изолирующий диод 23 коллектора транзистора 24, первый изолирующий диод 25 резистора 26, второй изолирующий диод 27 резистора 26, входные диоды 28-30, резистор 31 .

На фиг .4 в составе интегральной схемы 1 показаны изолирующие диоды 32-34 коллекторов транзисторов диоды 41 и 42, первые изолирующие диоды 43 и 44 и вторые изолирующие диоды 45 и 46 резисторов 47 и 48, резисторы 49-51.

На фиг.5 в составе интегральной схемы 1 показаны изолирующий диод 52 коллектора транзистора 53, первые 54

и 55 и вторые 56 и 57 изолирующие диоды каналов полевых транзисторов 58 и 59i полевые транзисторы 60 и 61,

Способ осуществляется следующим образом.

g В случае нарушения электрического контакта (обрыва) любого внешнего вывода 3«1 интегральной Ъхемы 1 с кристаллом ток через подключенный к выводу резистор 4.1 прекращается и

5 напряжение на этом резисторе отсутствует (фиг.1). При нарушении электрического контакта между подложкой кристалла и внешним выводом 2 корпуса интегральной схемы 1 напряжение от0 сутствует на всех резисторах 4.1-4.п. При коротком замыкании любого вывода 3.1 на корпус или подложку кристалла на соответствующем резисторе 4.1 устанавливается полное напряжение ис5 точника 5 питания. При отсутствии

напряжения на любом из входов блока 6 компараторов или при наличии на любом из его входов полного напряжения источника 5 блок 6 компараторов своим

Q выходным сигналом приводит в действие блок 7 индикации и сигнализации, фик- сирующи,й обрыв вывода контролируемой интегральной микросхемы или его короткое замыкание на корпус или подложку кристалла.

Для контроля различных типов интегральных схем с диодной изоляцией возможно задавать на все выводы 3.1 3.п одинаковое отрицательное напряжеQ ние через одинаковые по номиналу ограничительные резисторы 4.1-4.п. Это напряжение должно быть больше, чем напряжение обратимого пробоя диодной изоляции в интегральной микросхеме 1,

с а ток пробоя не должен превышать значения, гарантирующего обратимость пробоей любых р - n-переходов микросхемы (фиг.2-5).

На ТТЛ-микросхеме (фиг.2) при подключении выводов 3..5 к отрицатель0

ному полюсу источника 5 через токоограничивающие резисторы 4.1-4.5 открываются входные 8-10 и изолирующие 11-13 диоды. При отсутствии обрывов и коротких замыканий выводов на кор- 5 пус или подложку нз всех резисторах 4.1-4.3, 4.5, подключенных к выводам 3.1-3.3, 3.5, устанавливается напряжение источника 5 за Рычетом прямого

51

падения напряжения на диодах. На резисторе 4.4, подключенном к выводу 3.4, устанавливается напряжение источника 5 за вычетом прямого напряжения на диодах и падения напряжения на резисторах 20 и 21.

В случае отсутствия входных диодов 8-10 (фиг.2) открываются изолирующие диоды 11-13, а через резисторы 15-21 - эмиттерные переходы транзистора 22. На присоединенных к выводам 3.1-3.3 микросхемы резисторах 4.1-4.3 устанавливается напряжение источника 5 питания за вычетом прямых напряжений на диодах 11 и 1, эмиттерных переходах транзистора 2 и напряжений на резисторах 19-215

В ДТЛ-микросхеме (фиг.З) открывается изолирующий диод 23 коллектора транзистора 2k, изолирующий диод 25 резистора 26, наступает обратимый прбой другого изолирующего диода 27 резистора 26 и открываются входные диоды 28-30. На резисторе 4.6, подключенном к выводу 3.6, устанавливается напряжение источника 5 питания за вычетом напряжения на изолирующем диоде. На резисторе 4.5, подключенном к выводу 3.5, устанавливается -напряжение источника 5 питания за вычетом прямого напряжения на изолирующем диоде и напряжения на резисторе 31. На резисторах А. 1-4.3, подключенных к выводам 3.1- 3.3, устанавливается напряжение источника 5 за вычетом прямого напряжения на диодах 28-30, 25 и напряжения пробоя изолирующего диода 27.

В ЗЛС-микросхеме (фиг.4) открываются изолирующие диоды 32-34 коллекторов транзисторов , происходит обратимый пробой эмиттерных переходов транзисторов 35 и 36, открываются эмиттерные переходы транзисторов 39 и 40 и диоды 41 и 42, открываются также изолирующие диоды 43 и 44 резисторов 47 и 48 и происходит обратимый пробой изолирующих диодов 45 и 46 тех же резисторов. На резисторах 4.1 и 4.2, подключенных к вывода 3.1 и 3.2, устанавливается напряжение источника 5 питания за вычетом напряжения пробоя эмиттерных переходов и напряжения на резисторе 51 На резисторе 4.3, подключенном к выводу 3.3, устанавливается напряжение источника 5 питания за вычетом прямого напряжения на изолирующем диоде. На

5426

резисторах 4.4 и 4.5, подключенных к выводам 3.4 и 3.5 устанавливается напряжение источника 5 за вычетом прямого напряжения на изолирующих диодах и эмиттерных переходах. На резисторах 4.6 и 4.7, подключенных к выводам 3.6 и 3.7, устанавливается напряжение источника 5 за вычетом

прямого напряжения и напряжения пробоя изолирующих диодов, На резисторе 4.8, подключенное к выводу 3.8, устанавливается напряжение источника 5 за вычетом прямого напряжения на

5 диодах 41, 42 и 34 и напряжения на резисторах 49 и 50.

Во входном каскаде операционного усилителя (фиг.5) на полевых транзисторах с р - n-переходом (канал типа

0 р) открываются изолирующий диод 52 коллектора транзистора 53 и изолирующие диоды 54 и 55 каналов полевых транзисторов 58 и 59, наступает обратимый пробой изолирующих диодов 56

5 и 57 каналов полевых транзисторов 60 и 61. На резисторе 4.1, подключенном к выводу 3.1, устанавливается напряжение источника 5 за вычетом пряного напряжения на изолирующем диоде. На

о выводах 3.2 и 3.3 устанавливается напряжение источника 5 за вычетом прямого напряжения, напряжения пробоя изолирующих диодов и прямого напряжения переходов затворов.

Для указанных типов твердотельных интегральных микросхем (фиг.2-5) возможно организовать контроль отсутствия обрывов или замыкания на корпус или подложку внешних выводов 3..п, используя возможность прямого смещения и обратимого пробоя р - п-пере- ходов. Для этого на каждый вывод 3.1 З.п задают через токоограничивающие резисторы 4.1-4.П одинаковое отрицательное напряжение большее, чем напряжение пробоя диодной изоляции, а ток вывода ограничивают (с целью предотвращения выхода интегральной микросхемы 1 из строя) значением, гарантирующим обратимость пробоя любых р - n-переходов микросхемы. Зто позволяет обеспечить идентичность каналов контроля устройства, реализующего предлагаемый способ, для всех выво5 дов 3..п интегральной микросхемы 1, что упрощает реализацию способа и позволяет проводить одновременно контроль по всем выводам .п инте0

5

0

тральной микросхемы, что повышает быстродействие контроля.

Формула изобретения

Способ контроля отсутствия обрывов и коротких замыканий на корпус или подложку внешних выводов твердотельных интегральных схем с изолирующими диодами, согласно которому на внешние выводы твердотельной интегральной схемы с изолирующими диодами подают напряжение через токоограничивающие резисторы внешнего вывода, соединенного с лодложкой или корпусом, и по

величине напряжения на выводе твердотельной интегральной схемы судят об отрыве или коротком замыкании, отличающийся тем, что, с целью повышения быстродействия контроля и упрощения реализации способа, на все внешние выводы твердотельной интегральной схемы с изолирующими диодами задают одинаковое отрицательное напряжение, по абсолютной величине большее, чем напряжение пробоя изолирующих диодов, а ток каждого из выводов ограничивают значением обратимого пробоя изолирующих диодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации обрывов и коротких замыканий на корпус или подложку внешних выводов твердотельных интегральных схем с диодной изоляцией | 1989 |

|

SU1691790A1 |

| УСТРОЙСТВО ДЛЯ ЗАРЯДА АККУМУЛЯТОРНОЙ БАТАРЕИ АСИММЕТРИЧНЫМ ТОКОМ | 1992 |

|

RU2025022C1 |

| Активный фильтр для сглаживания пульсаций | 1990 |

|

SU1771050A1 |

| УСТРОЙСТВО ДЛЯ НИЗКОЧАСТОТНОЙ ТЕРАПИИ | 1992 |

|

RU2020979C1 |

| Стабилизатор напряжения постоянного тока | 1989 |

|

SU1677703A1 |

| УСТРОЙСТВО ДЛЯ ГАЛЬВАНИЧЕСКОГО РАЗДЕЛЕНИЯ СИГНАЛОВ | 2013 |

|

RU2522913C1 |

| ПОНИЖАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 2011 |

|

RU2470450C1 |

| Высоковольтный транзисторный переключатель | 1990 |

|

SU1734203A1 |

| Устройство для контроля обрывов и замыканий электродов в электровакуумных и ионных приборах | 1984 |

|

SU1226358A1 |

| КОММУТАЦИОННОЕ УСТРОЙСТВО | 1997 |

|

RU2175166C2 |

Изобретение относится к контрольно-измерительной технике и может быть использовано при производстве и контроле твердотельных интегральных схем с изолирующими диодами. Цель изобретения - повышение быстродействия контроля и упрощение его реализации за счет обеспечения возможности одновременного контроля контактирования по всем выводам твердотельной интегральной схемы с изолирующими диодами на одинаковом значении испытательного напряжения. Устройство, реализующее способ контроля контактирования твердотельной интегральной схемы 1, имеющей внешний вывод 2 корпуса, соединенный с подложкой, и другие выводы 3.1-3N корпуса, содержит токоограничивающие элементы 4.1-4N, например резисторы, источник 5 напряжения, блок 6 компараторов, блок 7 индикации и сигнализации. Способ заключается в том, что на все выводы 3.1-3N корпуса контролируемой твердотельной интегральной схемы 1 задают относительно вывода 2 корпуса, соединенного с подложкой, через токоограничивающие резисторы 4.1-4N одинаковое отрицательное напряжение, по абсолютной величине большее, чем напряжение пробоя изолирующих диодов, а ток каждого из выводов ограничивают значением, гарантирующим обратимость пробоя изолирующих диодов. Это возволяет обеспечить идентичность каналов контроля устройства, реализующего способ, и проводить одновременно контр

Р

PttgJ

Фиг Ч

60

Г

61

1156 2SW

i i pT

Редактор И.Шулла

Составитель В.Дворкин

Техред М.Ходанич Корректор В.Гирняк

Заказ 278

Тираж 559

ВНИИПИ Государственного ко итета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

53

4/ db

Ц52

4f

-cm

«.J -ШН

1157 2155

2 +

Риг. 5

Подписное

| Устройство контроля контактирования интегральных схем | 1976 |

|

SU646279A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля контактирования интегральных схем | 1981 |

|

SU978085A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ( СПОСОБ КОНТРОЛЯ ОТСУТСТВИЯ ОБРЫВОВ И КОРОТКИХ ЗАМЫКАНИЙ НА КОРПУС ИЛИ ПОДЛОЖКУ ВНЕШНИХ ВЫВОДОВ ТВЕРДОТЕЛЬНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ИЗОЛИРУЮЩИМИ ДИОДАМИ | |||

Авторы

Даты

1990-02-07—Публикация

1985-10-10—Подача