Os

ю

ю о

Изобретение относится к контрольно- измерительной технике и может быть использовано при производстве и контроле 1|вердотельных интегральных схем с диод- ной изоляцией в процессе испытаний на Е иброустойчивость и воздействие акустиче- с ких шумов.

Цель изобретения - повышение достоверности контроля за счет исключения возможности индикации случайных электрических помех и расширение функциональных возможностей за счет возможности контроля при воздействии механических вибраций и акустических шумов.

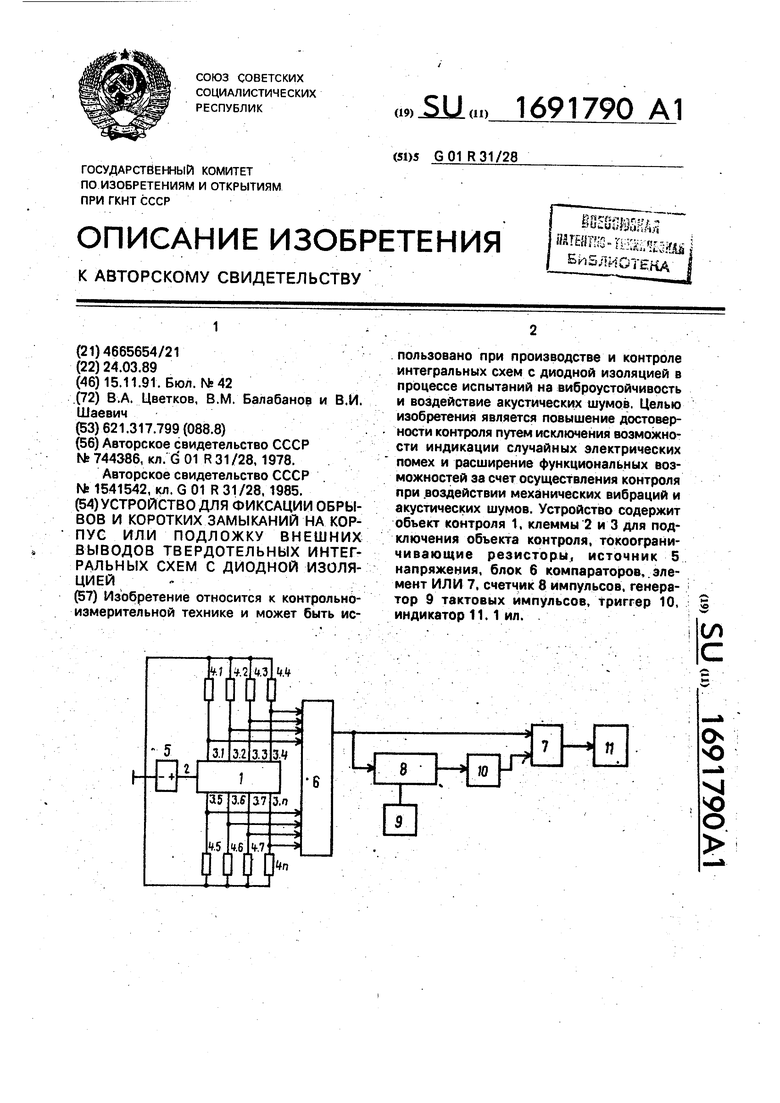

На чертеже изображена схема предло- кенного устройства.

Устройство содержит объект 1 контроля микросхема), клемму 2 для подключения эбъекта контроля (вывод корпуса или под- южки кристалла), клеммы 3.1 - З.п для подключения объекта контроля, токоогра- ичивающие резисторы 4.1 - 4.п, источник 5 напряжения, блок 6 компараторов, элемент ИЛИ 7, счетчик 8 импульсов, генератор 9 тактовых импульсов, триггер 10, индикатор 11с соответствующими связями.

Устройство работает следующим образом.

Напряжение источника 5 превышает напряжение пробоя диодной изоляции микросхемы 1. При этом р-п переходы элементов микросхемы 1 либо смещаются в прямом направлении, либо наступает их обратный пробой. Во внешних клеммах 2, 3.1 - З.п микросхемы 1 появляются токи, значения которых ограничиваются резисторами 4,1 - 4.п до величин, гарантирующих обратимость пробоев р-п переходов. При отсутствии обрывов и коротких замыканий выводов на корпус или подложку кристалла на резисторах 4.1 - 4.п и на входах блока 6 компараторов присутствуют потенциалы. Значения потенциалов отличны от нуля и меньше напряжения источника 5. При наличии на всех входах блока 6 компараторов потенциалов, отличных от нуля и меньших напряжения источника 5, на выходе блока 6 компараторов имеется напряжение, соответствующее уровню О.

В случае обрыва любой из клемм 3.1 - З.п микросхемы 1 на соответствующем входе блока б компараторов устанавливается нулевой потенциал. В случае обрыва клеммы 2, соединенной с подложкой кристалла микросхемы 1, нулевой потенциал устанавливается на всех входах блока 6 компараторов. В случае короткого замыкания любой из клемм 3.1 - З.п микросхемы 1 на корпус или подложку кристалла на соответствующем входе блока 6 компараторов устанавливается полное напряжение источника 5. Появление на любом входе блока б компараторов нулевого потенциала, либо потенциалаг равного полному напряжению источника 5,

вызывает появление на выходе блока 6 компараторов напряжения, соответствующего уровню Т.

Если в процессе испытаний микросхемы 1 произойдет невосстановимое нарушение целостности ее выводов (обрыв вывода или замыкание на корпус или подложку кристалла), то на выходе блока б компараторов установится и будет постоянно держаться уровень 1, который через элемент ИЛИ 7

поступает на вход индикатора 11, фиксирующего неисправность микросхемы.

Счетчик 8 импульсов периодически обнуляется генератором 9 тактовых импульсов

с частотой f об и имеет емкость N импульсов, т. е„ если за период обнуления Тоб 1/fo6 на вход счетчика поступит число импульсов, меньшее или равное N, то на выход счетчика импульсы проходить не будут. Если за

период Тоб на вход счетчика 8 поступит число импульсов, большее N, то все импульсы,- следующие за импульсом с номером N в интервале времени Т0б, пройдут на выход счетчика.

На микросхему 1 воздействуют вибрации или акустические шумы в диапазоне частот от fmin до fmax. Наибольшая вероятность появления невосстановимых и кратковременных, восстановимых нарушений целостности выводов микросхем должна наблюдаться на частотах, совпадающих с частотами механических резонансов выводов, если частоты механических реэонансов лежат в интервале от fmin до fmax. Таким

образом, если в процессе испытаний микросхем появляются кратковременные, восстановимые нарушения целостности выводов, то частота следования нарушений должна совпадать с одной из частот механического

резонанса выводов и находиться в пределах от fmin до fmax. Если на определенном участке этого диапазона в микросхеме 1 возникают кратковременные, восстановимые нарушения целостности выводов, то на выходе блока б компараторов и на входе обнуляемого счетчика 8 импульсов появляются импульсы напряжения с уровнем 1 следующие с частотой воздействия вибрацией или акустических шумов. Частота обнуления

forf и емкость N счетчика 8 выбираются из условия f0e(N+ 1) Ј fmm, при переполнении счетчика 8 импульс с его выхода поступает на вход триггера 10. При этом на выходе триггера установится уровень Г, который через элемент ИЛИ 7 пройдет на вход блока

11 индикации, который зафиксирует неисправность микросхемы.

Вследствие электрических помех, возникающих во входных цепях блока 6 компараторов из-за больших сопротивлений и длин цепей, на выходе блока б компараторов могут появляться случайные импульсы, не связанные с обрывами и замыканиями клемм 2, 3.1 - З.п микросхемы 1. Если за период обнуления ТоЈ счетчика 8 число этих случайных импульсов не будет превышать емкости N счетчика, то импульсы не будут проходить на его выход, а также они не поступают на триггер 10 и не приводят в действие индикатор 11, т. е. исключается возможность индикации случайных электрических (емкостных и электромагнитных) помех.

Формула изобретения Устройство для фиксации обрывов и ко- ротких замыканий на корпус или подложку внешних выводов твердотельных интегральных схем с диодной изоляцией, содержащее п -1 клемм для подключения объекта контроля, п токоограничивающих резисто-

ров, источник напряжения, индикатор, блок компараторов, каждый из п входов которого соединен с первыми выводами каждого из п токоограничивающих резисторов и с каждой из п клемм для подключения объекта контроля соответственно, (п + 1)-я клемма которого соединена с положительным полюсом источника напряжения, отрицательный полюс которого соединен с общей точкой устройства и вторыми выводами каждого из п токоограничивающих резисторов соответственно, отличающееся тем, что, с целью повышения достоверности контроля и расширения функциональных возможностей, в него введены счетчик импульсов, генератор тактовых импульсов, триггер, элемент ИЛИ, первый вход которого соединен с выходом блока компараторов и со счетным входом счетчика импульсов, выход генератора тактовых импульсов соединен с входом начальной установки счетчика импульсов, выход которого соединен с входом триггера, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с входом индикатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля отсутствия обрывов и коротких замыканий на корпус или подложку внешних выводов твердотельных интегральных схем с изолирующими диодами | 1985 |

|

SU1541542A1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| СПОСОБ КОНТРОЛЯ СТЕПЕНИ АКУСТИЧЕСКОГО КОНТАКТА | 1991 |

|

RU2022548C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ | 1992 |

|

RU2027403C1 |

| Устройство для контроля тока | 1985 |

|

SU1290183A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КРИТИЧЕСКОГО УРОВНЯ РАБОЧЕЙ ЖИДКОСТИ | 1996 |

|

RU2112219C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ФИЗИЧЕСКОЙ ВЕЛИЧИНЫ | 1999 |

|

RU2162592C2 |

| ИСТОЧНИК ПИТАНИЯ ДЛЯ ЭЛЕКТРОЛЮМИНЕСЦЕНТНОЙ ПАНЕЛИ | 2001 |

|

RU2210120C1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ АППАРАТОВ ТОКОВОЙ ЗАЩИТЫ | 1990 |

|

RU2024888C1 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ С МОДУЛЯЦИЕЙ ДЛЯ РЕЗОНАНСНОГО КОНТУРА | 2007 |

|

RU2436210C2 |

Изобретение относится к контрольно- измерительной технике и может быть использовано при производстве и контроле интегральных схем с диодной изоляцией в процессе испытаний на виброустойчивость и воздействие акустических шумов. Целью изобретения является повышение достоверности контроля путем исключения возможности индикации случайных электрических помех и расширение функциональных возможностей за счет осуществления контроля при воздействии механических вибраций и акустических шумов. Устройство содержит объект контроля 1, клеммы 2 и 3 для подключения объекта контроля, токоограни- чивающие резисторы, источник 5 напряжения, блок 6 компараторов, элемент ИЛИ 7, счетчик 8 импульсов, генератор 9 тактовых импульсов, триггер 10, индикатор 11.1 ил. сл

| Устройство для фиксации обрывов и коротких замыканий электродов транзисторов | 1978 |

|

SU744386A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ контроля отсутствия обрывов и коротких замыканий на корпус или подложку внешних выводов твердотельных интегральных схем с изолирующими диодами | 1985 |

|

SU1541542A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-11-15—Публикация

1989-03-24—Подача