Фиг.1

Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике.

Целью изобретения является повышение надежности работы устройству за счет введения новых связей, исключающих сбои в работе устройства,

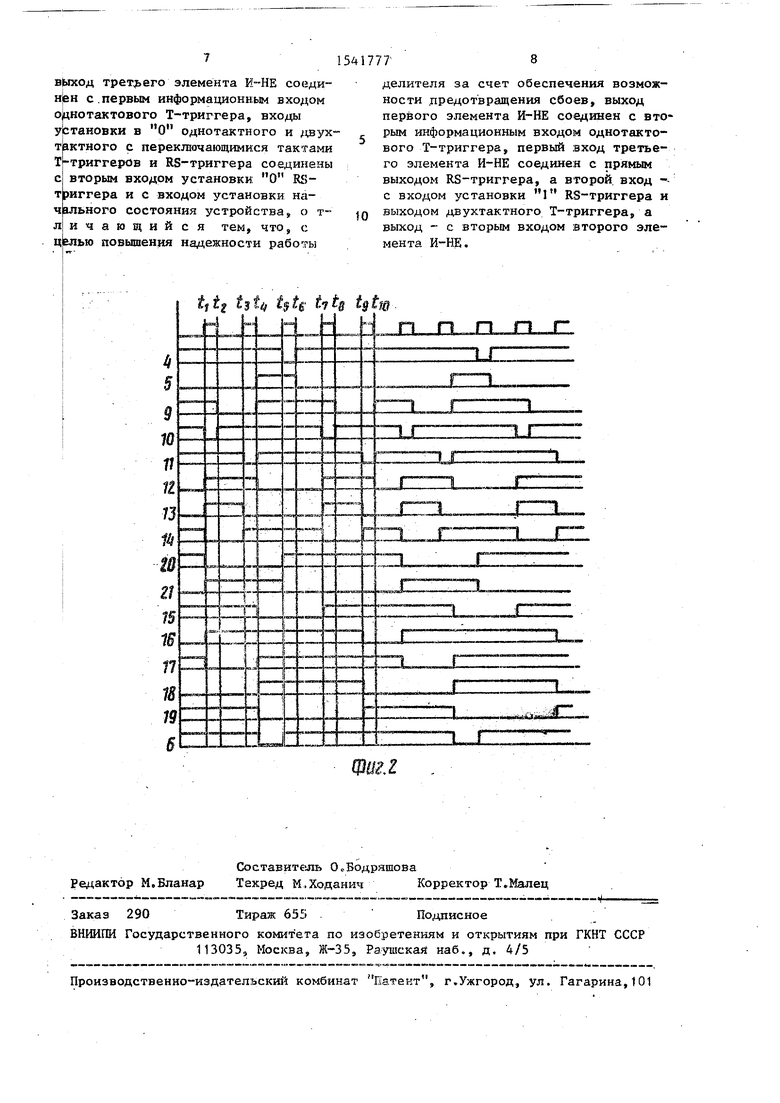

На фиг.1 изображена структурно- электрическая схема делителя; на фиг.2 - временные диаграммы, поясняющие работу делителя.

Делитель частоты со/держит одно- тактный Т-триггер 1s двухтактный Т- триггер 2 с перекрывающимися тактами, асинхронный RS-триггер 3, первый 4, второй 5 я третий 6 элементы И-НЕ0

Вход синхронизации однотактного Т-триггера соединен с входной шиной 7 устройства и первым входом первого элемента И-НЕ 4, а инверсный выход и инверсный выход с задержкой соединены соответственно с первым и вторым входами синхронизации двухтактного Т-триггера„ Второй вход первого элемента И-НЕ 4 соединен с выходом второго элемента И-НЕ 5Э а выход - с первым информационным входом одно- тактного Т-триггер 1s первым входом второго элемента И-НЕ 5 и первым входом установки О RS-триггера 30

Второй вход второго элемента И-НЕ 5 соединен с вторым информационным входом однотак-тного Т-триггера 1 и выходом третьегс элемента И-НЕ 6, первый вход которого „,.,здинен с прямым выходом RS-триггера 3, а второй вход - с входом установки 1 RS-триггера 3 и выходом двухтактного Т-триггера 2,

Вход 8 установки начального состояния устройства соединен с входами утановки

вторым входом установки гера 3, с вторым входом второго элемента И-НЕ 5, первый вход третьего элемента И-НЕ соединен с прямым выходом RS-триггера 35 вход установки в 1 которого соединен с вторым входом третьего элемента И-НЕ 6 и трещим входом второго Т-триггера 2„Первый Т-триггер 1 содержит шесть элементов И-НЕ второй Т-триггер 2 содержит пять элементов И-НЕ 15-19, RS-триггер З содержит два элемента И-НЕ 20 и 21. Вместо элементов И-НЕ можно использовать элементы ИЛИ-НЕ

О Т-триггеров 1 и 2 и с

О RS-триг

5

Делитель работает следующим образ ом „

Перед подачей входных положительных импульсов во всех триггерах делителя установлено состояние О (выходы элементов 13, 18 и 21 - прямые выходы триггеров).

С приходом первого положительного

импульса (момент t,) на вход делителя 7, на выходе элемента 10 формируется нулевой сигнал, который формирует единичные сигналы на выходах элементов 12, 13 и 160 В момент tz сигнал

5 на выходе элемента 10 становится

единичным, что вызывает наличие единичных сигналов на входах элемента 9. Это приводит к появлению нулевого сигнала на выходе элемента 9„ Других

0 изменений выходных сигналов элементов в момент ty не происходит. Таким образом, после первого импульса в делителе оказывается число 101

С приходом второго импульса (момент tj) на всех входах элемента 11 оказываются единичные сигналы, и на его выходе появляется нулевой сигнал, что вызывает появление единичного сигнала на выходе элемента 14„ После этого на всех входах элемента 13 оказываются единичные сигналы, и на его выходе формируется нулевой сигнал. Остальные выходные сигналы логических элементов остаются неизменными до момента t окончания второго импульса, В момент t,). сигнал на выходе элемента 11 становится единичным.Вследствие этого на всех входах элемента 12 оказываются единичные сигналы, и на его выходе формируется нулевой сигнал, в результате чего на выходе элемента 9 формируется единичный сигнал После этого на все входы элемента 15 подают единичные сигналы и на его выходе появляется нулевой сигнал , которьй переводит в состояние 1 элемент 18„ После этого на всех входах элемента 19 - единичные сигналы, вследствие чего на его выходе формируется нулевой сигнал, который переводит элемент 17 в состояние 1 После этого на всех входах элемента 6 оказываются единичные сигналы, и на его выходе формируется сигнал Сигнал О На выходе элемента 6 переводит элемент 5 в состояние 1. Других изменений сигналов на выходах элементов в момент t& не происходит,

0

0

и в делителе частоты оказывается число ПО.

С приходом третьего импульса (момент tj) на всех входах элемента 4 оказываются единичные сигналы, что приводит к появлению нулевого сигнала на его выходе, который устанавливает в состояние 1 элемент 20 Нулевой сигнал на выходе элемента 4 подтверждает единичные сигналы на выходах элементов 5 и 10„ После этого на всех входах элемента 21 оказывается единичный сигналs что вызывает появление на его выходе нулевого сигнала0 Этот сигнал устанавливае в состояние 1 элемент 6„ Далее в течение действия третьего импульса сигналы на выходах элементов делителя частоты импульсов на пять останутся без изменений В момент t окончания третьего импульса на выходе элемента 4 появляется единичный сигнал, и на всех входах элемента 5 оказываются единичные сигналы Таким образом, на выходе элемента 5 формируется нулевой сигнал. Других изменений сигналов на выходах элементов делителя частоты импульсов на пять в момент tg не происходит и в его триггерах по окончании третьего импульса оказывается число 010.

С приходом четвертого импульса (момент tt) на всех входах элемента 10 оказываются единичные сигналы,что приводит к появлению нулевого сигнала на его выходе. Этот сигнал под- тверждает единичные сигналы на выходах элементов 9 и 11 и устанавливает в состояние 1 элемент 13. После этого на всех входах элемента 14 появляются единичные сигналы, на его выходе появляется нулевой сигнал.Он подтверждает единичный сигнал на выходе элемента 1 б и устанавливает в состояние 1 элементы 12 и 15„ Остальные выходные сигналы элементов остаются неизменными до момента te окончания четвертого импульса, В момент t8 на выходе элемента 10 формируется единичный сигнал, на всех входах элемента 9 оказываются единичные сигналы и на его выходе формируется нулевой сигнал. Других изменений сигналов в момент t8 не происходит и в делителе окажется записано число 011,

С приходом пятого положительного импульса (момент t9) на всех входах элемента 11 оказываются единичные

0

5

сигналы, и на его выходе формируется нулевой сигнал. Он подтверждает единичный сигнал на выходе элемента 12 и вызывает появление единичного сигнала на выходе элемента 14. После этого на всех входах элементов 13 и 16 оказываются единичные сигналы, на их выходах формируются нулевые сигналы. Нулевой сигнал на выходе эпемента 16 подтверждает единичный сигнал на выходе элемента 17 и устанавливает в единичное состояние сигнал на выходе элемента 19. Вследствие этого, на всех входах элемента 18 оказываются единичные сигналы, и на его выходе формируется нулевой сигнал Такие сигналы сохраняются до момента t,e окончания пятого импульса. В момент 0 t,0 сигнал на выходе элемента 1 1 делается единичным и на всех входах элемента 12 оказываются единичные сигналы. На выходе элемента 12 появляется нулевой сигнал, который вызывает появление на выходе элемента 9 единичного сигнала. Никаких других изменений сигналов в момент t10 не происходит В момент t,0 выходные сигналы делителя частоты импульсов на пять повторяют выходные сигналы перед подачей первого импульса Очевидно, что далее работа делителя частоты импульсов на пять повторяется.

Для установки триггеров 1 - 3 делителя частоты импульсов на пять в исходное нулевое состояние, на шину 8 подается нулевой сигнал, предшествующий во времени входным импульсам делителя.

5

0

5

0

Формула изобретения

Делитель частоты импульсов на пять, содержащий однотактный Т-триг- гер, вход синхронизации которого соединен с входной шиной устройства, а первый и второй инверсные выходы соединены соответственно с первым и вто- Рым входами синхронизации двухтактного Т-триггера с перекрывающимися тактами, асинхронный RS-триггер и первый, второй и третий элементы И-НЕ, первый вход первого элемента И-НЕ соединен с входной шиной устройства, второй вход - с выходом второго элемента И-НЕ, а выход - с первым входом второго элемента И-НЕ и первым входом установки в О RS-триггера,

выход третьего элемента F--HE соединен с первым информационным входом однотактового Т-триггера, входы установки в О однотактного и двухтактного с переключающимися тактами Т-триггерОв и RS-триггера соединены с вторым входом установки О RS- триггера и с входом установки начального состояния устройства, о тл

имеющийся тем, что,

целью повышения надежности работы

делителя за счет обеспечения возможности предотвращения сбоев, выход первого элемента И-НЕ соединен с вторым информационным входом однотактового Т-триггера, первый .вход третьего элемента И-НЕ соединен с прямым выходом RS-триггера, а второй вход -- с входом установки 1 RS-триггера и выходом двухтактного Т-триггера, а выход - с вторым входом второго элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов на пять на потенциальных элементах и-не/ или-не | 1974 |

|

SU525250A1 |

| Распределитель сигналов на десять каналов | 1986 |

|

SU1325683A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| Способ формирования частотно-импульсных сигналов датчика перемещения и устройство для его осуществления | 1976 |

|

SU905993A1 |

| Делитель частоты импульсов | 1988 |

|

SU1653152A1 |

| САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ (ВАРИАНТЫ) | 2009 |

|

RU2427955C2 |

| Устройство для выделения и вычитания импульсов из серии | 1987 |

|

SU1431056A1 |

| Троичное счетное устройство | 1988 |

|

SU1580535A2 |

| Троичное счетное устройство | 1988 |

|

SU1506547A1 |

| Троичное счетное устройство | 1989 |

|

SU1598127A1 |

Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике. Цель изобретения - повышение надежности работы устройства - достигается в результате введения новых связей, исключающих сбои в работе устройства. Устройство содержит однотактный Т-триггер 1, двухтактный Т-триггер 2 с перекрывающимися тактами, асинхронный RS-триггер 3, три элементы И-НЕ 4,5,6, входную шину 7 устройства и шину 8 установки начального состояния устройства. Однотактный Т-триггер 1 содержит шесть элементов И-НЕ 9-14, двухтактный Т-триггер 2 содержит пять элементов И-НЕ 15-19, RS-триггер 3 содержит два элемента И-НЕ 20 и 21. 2 ил.

t,tt Ыц t9ts Ы8 t$tm

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-07—Публикация

1987-11-13—Подача