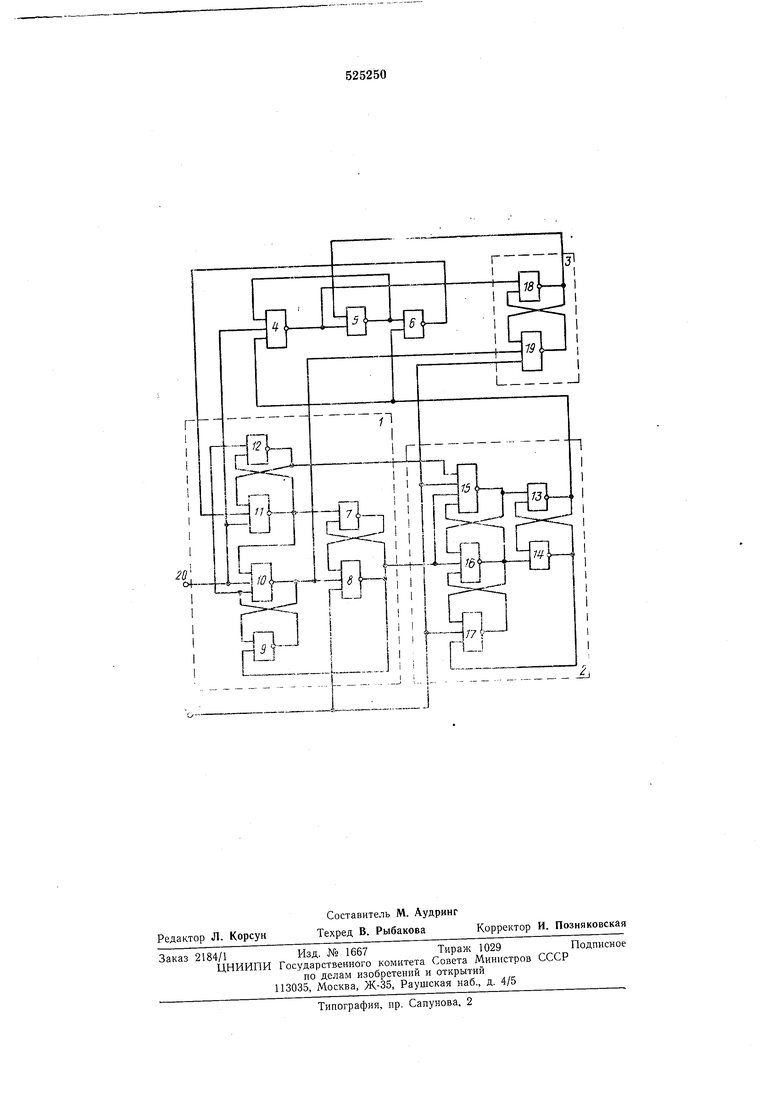

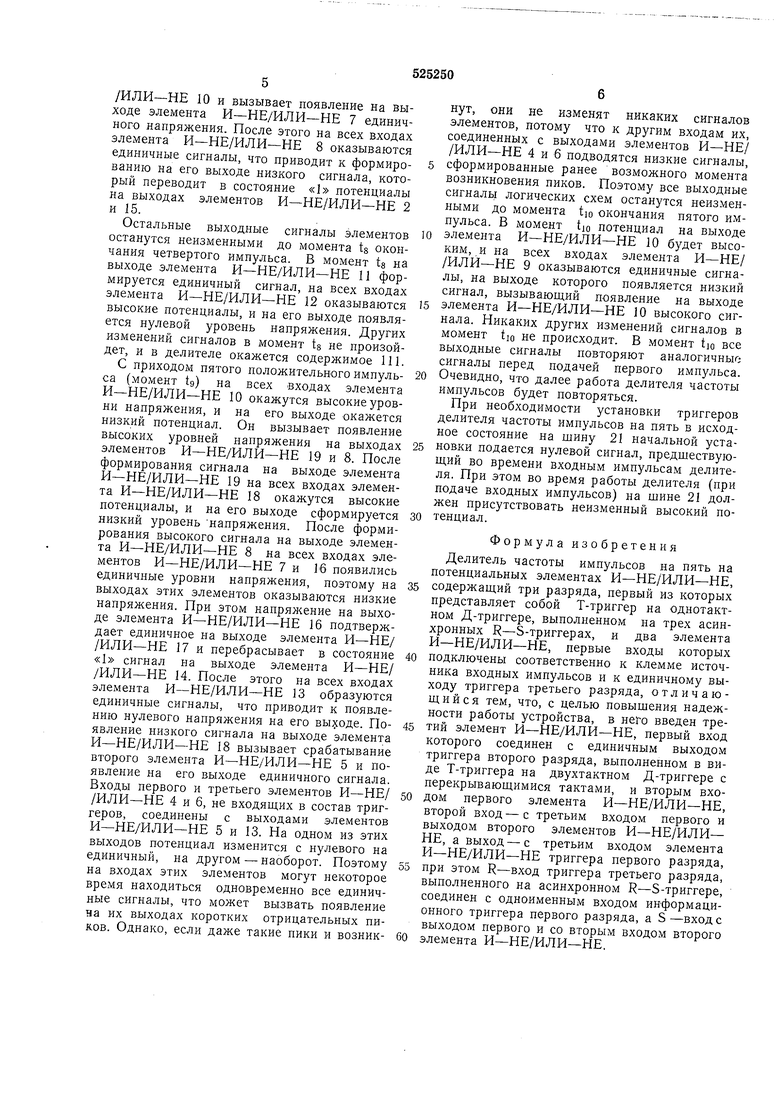

установлено содержимое «О. При этом первый разряд, образованный элементами И- -НЕ/ИЛИ-НЕ 7-12 имеет на выходе элемента И-НЕ/ИЛИ-НЕ 7, который является единичным выходом первого разряда 1, нулевой сигнал. Низкий уровень напряжения присутствует также на выходе элемента И-НЕ/ /ИЛИ-НЕ 9. На остальных выходах элементов, входящих в состав первого разряда, в том числе на нулевом выходе элемента И-НЕ/ИЛИ-НЕ, присутствуют единичные сигналы. Второй разряд, состоящий из элементов И-НЕ/ИЛИ-НЕ 13-17, имеет на выходе элемента Н-НЕ/ИЛИ-НЕ 13, который является единичным выходом второго разряда, нулевой потенциал. Низкий сигнал присутствует и на выходе элемента Н-НЕ/ /ИЛИ-НЕ 16. На остальных выходах элементов, в том числе на нулевом выходе второго разряда присутствуют единичные сигналы. Третий разряд из элементов И-НЕ/ /ИЛИ-НЕ 18 и 19 имеет на единичном выходе (элемент И-НЕ/ИЛИ-НЕ 18) нулевой сигнал, а на единичном выходе (элемент И-НЕ/ИЛИ--НЕ 19) единичный сигнал. При этом на выходах элементов И-НЕ/ИЛИ-НЕ 4-6, не входящих в разряды, устанавливаются единичные потенциалы.

С приходом первого положительного импульса (момент ti) на клемму 20, являющуюся счетным входом первого разряда, на всех входах элемента И-НЕ/ИЛИ-НЕ 11 оказываются единичные потенциалы, и на его выходе формируется низкий сигнал. Он подтверждает высокий сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 10 И переводит в единицу сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 7. После этого на всех входах элемента И-НЕ/ИЛИ-НЕ 8 оказались высокие потенциалы, на выходе которого образуется низкое напряжение, которое подтверждает высокий сигнал на выходе элемента И-НЕ/ /ИЛИ-НЕ 15 и переводит в единицу сигналы на выходах элементов И-НЕ/ИЛИ-НЕ 9 и 19. Такие сигналы сохранятся до момента iz окончания первого импульса. В момент t2 сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 11 становится высоким, что вызывает наличие обоих высоких сигналов на входах элемента И-НЕ/ИЛИ-НЕ 12. Это приводит к появлению низкого сигнала на выходе элемента И-НЕ/ИЛИ-НЕ 12. Других изменений выходных потенциалов схем в момент 12 не будет. Таким образом, после первого импульса в делителе окажется содержимое 001.

После начала второго импульса (момент ts) на всех входах элемента И-НЕ/ИЛИ-НЕ 10 окажутся высокие уровни напряжения, и на его выходе появится низкий потенциал. Он подтверждает высокие сигналы на выходах элементов И-НЕ/ИЛИ-НЕ 19 и 9 и вызывает появление высокого сигнала на выходе элемента И-НЕ/ИЛИ-НЕ В. После этого на всех входах элемента И-НЕ/ИЛИ-НЕ 7 оказываются единичные потенциалы, и на

его выходе образуется нулевой сигнал. Остальные выходные сигналы элементов остаются неизменными до момента t окончания второго импульса. В момент t сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 10 становится высоким. Вследствие этого ко всем входам элемента И-НЕ/ИЛИ-НЕ 9 оказываются приложены высокие сигналы, и на его выходе образуется нулевой сигнал, переводищий в состояние «1 потенциал на выходе элемента И-НЕ/ИЛИ-НЕ 12. После этого на все входы элемента И-НЕ/ИЛИ-НЕ 15 будут поданы высокие уровни напряжения. Таким образом, на его выходе появится нулевой потенциал. Он переводит в состояние «1 сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 13 (на единичном выходе второго разряда) и подтверждает высокий сигнал на выходе элемента И-НЕ/ИЛИ-НЕ 16. После этого на

всех входах элемента И-НЕ/ИЛИ-НЕ 14 и третьего элемента И-НЕ/ИЛИ-НЕ 6, не входящих в какой-либо триггер, оказываются единичные уровни напряжения, вследствие чего на их выходах формируются нулевые

сигналы. Сигнал с выхода элемента И-НЕ/ /ИЛИ-НЕ 14 переводит потенциал на выходе элемента И-НЕ/ИЛИ-НЕ 17 в состояние «1. Других изменений сигналов на выходах схем в момент i не произойдет, и в нем окажется содержимое 010.

С приходом третьего положительного импульса (момент ts) на всех входах первого элемента И-НЕ/ИЛИ-НЕ 4 оказываются все высокие сигналы, что вызывает появление

на его выходе низкого сигнала. Он подтверждает наличие высокого сигнала на выходе второго элемента И-НЕ/ИЛИ-НЕ 5 и попадает на вход элемента И-НЕ/ИЛИ-НЕ J8 (вход Rd третьего разряда). Вследствие

этого на его выходе (единичный выход третьего разряда) образуется высокий сигнал, а затем на пулевом выходе третьего разряда- низкий. Далее, в течение действия третьего импульса сигналы на выходах элементов делителя частоты импульсов на пять останутся без изменений. В момент tg окончания третьего импульса на выходе первого элемента И-НЕ/ИЛИ-НЕ 4 появляется высокий сигнал, и на обоих входах второго элемента

И-НЕ/ИЛИ-НЕ 5 оказываются единичные уровни напряжения. Таким образом на выходе второго элемента И-НЕ/ИЛИ-НЕ 5 образуется низкий сигнал. Попадая на третий элемент И-НЕ/ИЛИ-НЕ 6, он переводит

сигнал на его выходе в состояние «1. Других изменений сигналов на выходах схем делителя частоты в момент te не произойдет и в его разрядах по окончании третьего импульса оказывается содержимое ПО.

После начала четвертого импульса (момент ty) на всех входах элемента И-НЕ/ /ИЛИ-НЕ 11 окажутся высокие потенциалы, что приведет к появлению низкого сигнала на его выходе. От подтверждает наличие высокого напряжения на выходе элемента И-НЕ/

/ИЛИ-НЕ 10 и вызывает появление на выходе элемента И-НЕ/ИЛИ-НЕ 7 единнчного напряжения. После этого на всех входах элемента И-НЕ/ИЛИ-НЕ 8 оказываются единичные сигналы, что приводит к формированию на его выходе низкого сигнала, который переводит в состояние « потенциалы на выходах элементов И-НЕ/ИЛИ-НЕ 2 и 15.

Остальные выходные сигналы элементов останутся неизменными до момента ts окончания четвертого импульса. В момент ts на выходе элемента И-НЕ/ИЛИ-НЕ II формируется единичный сигнал, на всех входах элемента И-НЕ/ИЛИ-НЕ 12 оказываются высокие потенциалы, и на его выходе появляется нулевой уровень напряжения. Других изменений сигналов в момент ts не произойдет, и в делителе окажется содержимое 111.

С приходом пятого положительного импульса (модмент tg) на всех -входах элемента И-НЕ/ИЛИ-НЕ 10 окажутся высокие уровни напряжения, и на его выходе окажется низкий потенциал. Он вызывает появление высоких уровней напряжения на выходах элементов И-НЕ/ИЛИ-НЕ 19 и 8. После формирования сигнала на выходе элемента И-НЕ/ИЛИ-НЕ 19 на всех входах элемента И-НЕ/ИЛИ-НЕ 18 окажутся высокие потенциалы, и на его выходе сформируется низкий уровень напряжения. После формирования высокого сигнала на выходе элемента И-НЕ/ИЛИ-НЕ 8 на всех входах элементов И-НЕ/ИЛИ-НЕ 7 и 16 появились единичные уровни напряжения, поэтому на выходах этих элементов оказываются низкие напряжения. При этом напряжение на выходе элемента И-НЕ/ИЛИ-НЕ 16 подтверждает единичное на выходе элемента И-НЕ/ /ИЛИ-НЕ 17 и перебрасывает в состояние «1 сигнал на выходе элемента И-НЕ/ /ИЛИ-НЕ 14. После этого на всех входах элемента И-НЕ/ИЛИ-НЕ 13 образуются единичные сигналы, что приводит к появлению нулевого напряжения на его выходе. Появление низкого сигнала на выходе элемента И-НЕ/ИЛИ-НЕ 18 вызывает срабатывание второго элемента И-НЕ/ИЛИ-НЕ 5 и появление на его выходе единичного сигнала. Входы первого и третьего элементов И-НЕ/ /ИЛИ-НЕ 4 и 6, не входящих в состав триггеров, соединены с выходами элементов И-НЕ/ИЛИ-НЕ 5 и 13. На одном из этих выходов потенциал изменится с нулевого на единичный, на другом - наоборот. Поэтому на входах этих элементов могут некоторое время находиться одновременно все единичные сигналы, что может вызвать появление на их выходах коротких отрицательных пиков. Однако, если даже такие пики и возникнут, они не изменят никаких сигналов элементов, потому что к другим входам их, соединенных с выходами элементов И-НЕ/ /ИЛИ-НЕ 4 и 6 подводятся низкие сигналы, сформированные ранее возможного момента возникновения пиков. Поэтому все выходные сигналь логических схем останутся неиз.менными до момента tio окончания пятого импульса. В момент tio потенциал на выходе

элемента И-НЕ/ИЛИ-НЕ 10 будет высоким, и на всех входах элемента И-НЕ/ /ИЛИ-НЕ 9 оказываются единичные сигналы, на выходе которого появляется низкий сигнал, вызывающий появление на выходе

элемента И-НЕ/ИЛИ-НЕ 10 высокого сигнала. Никаких других изменений сигналов в момент не происходит. В момент tjo все выходные сигналы повторяют аналогичные сигналы перед подачей первого импульса.

Очевидно, что далее работа делителя частоты импульсов будет повторяться.

При необходимости установки триггеров делителя частоты импульсов на пять в исходное состояние на щину 21 начальной установки подается нулевой сигнал, предществующий во времени входным импульсам делителя. При этом во время работы делителя (при подаче входных импульсов) на шине 21 должен присутствовать неизменный высокий потенциал.

Формула изобретения

Делитель частоты импульсов на пять на потенциальных элементах И-НЕ/ИЛИ-НЕ,

содержащий три разряда, первый из которых представляет собой Т-триггер на однотактном Д-триггере, выполненном на трех асинхронных R-S-триггерах, и два элемента И-НЕ/ИЛИ-НЕ, первые входы которых

подключены соответственно к клемме источника входных импульсов и к единичному выходу триггера третьего разряда, отличающийся тем, что, с целью повышения надежности работы устройства, в него введен третий элемент И-НЕ/ИЛИ-НЕ, первый вход которого соединен с единичным выходом триггера второго разряда, выполненном в виде Т-триггера на двухтактном Д-триггере с перекрывающимися тактами, и вторым входом первого элемента И-НЕ/ИЛИ-НЕ, второй вход - с третьим входом первого и выходом второго элементов И-НЕ/ИЛИ- НЕ, а выход - с третьим входом элемента И-НЕ/ИЛИ-НЕ триггера первого разряда,

при этом R-вход триггера третьего разряда, выполненного на асинхронном JR-S-триггере, соединен с одноименным входом информационного триггера первого разряда, а S-входе выходом первого и со вторым входом второго

элемента И-НЕ/ИЛИ-НЕ.

4/4-1-1-I

L J i

L.

I r

I LJ-l

1 сЯ-

-j/tff-f- H r J J

ЕНИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Распределитель сигналов на десять каналов | 1986 |

|

SU1325683A1 |

| Устройство пересчета на три | 1980 |

|

SU869067A2 |

| Устройство для выделения и вычитания импульсов из серии | 1987 |

|

SU1431056A1 |

| Д-триггер | 1985 |

|

SU1264312A1 |

| Устройство для выделения и вычитания первого импульса из последовательности импульсов | 1989 |

|

SU1686441A1 |

| Устройство для выделения и вычитания первого импульса из последовательности импульсов | 1984 |

|

SU1223228A1 |

| Устройство для выделения и вычитания первого импульса из последовательности импульсов | 1989 |

|

SU1679485A2 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1985 |

|

SU1272504A1 |

| Устройство для получения разности двух импульсных последовательностей | 1990 |

|

SU1798904A1 |

Авторы

Даты

1976-08-15—Публикация

1974-11-06—Подача