01

ел

со

СО

о

00

Изобретение относится к электротехнике, в частности к системам вторичного электропитания (СВЭП).

Целью изобретения является обеспечение устойчивости работы при малых токах нагрузки вплоть до нуля при сохранении высокого значения КПД.

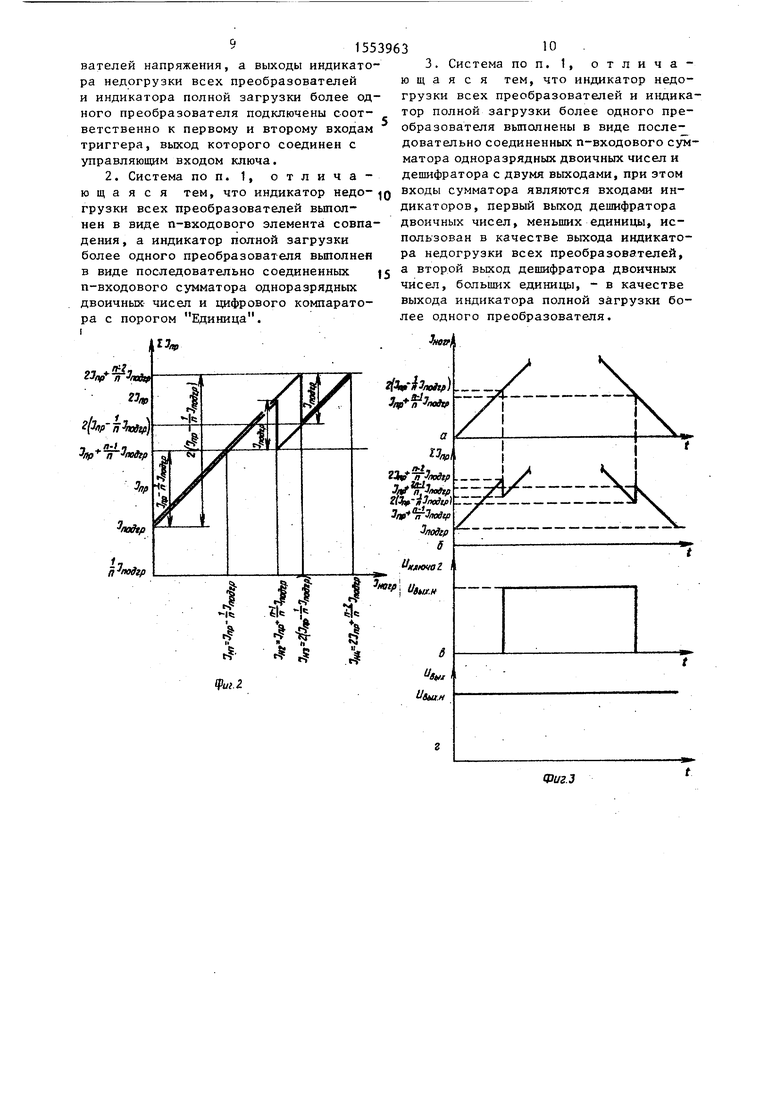

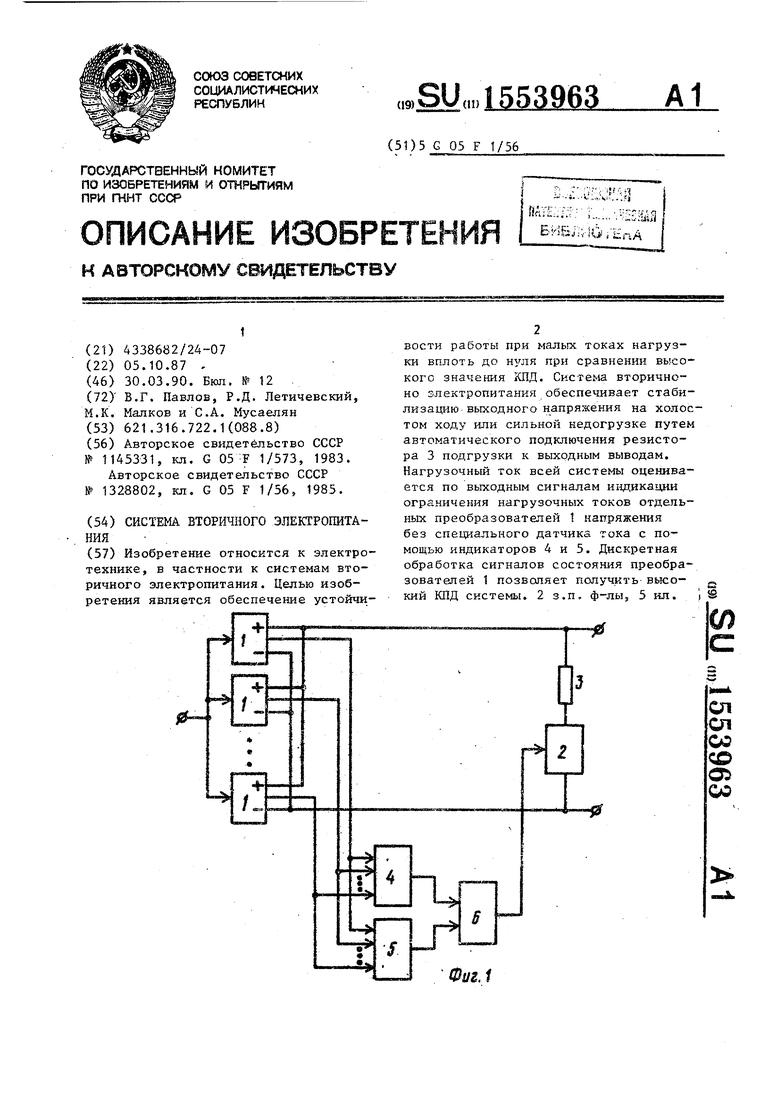

На фиг. 1 приведена блок-схема системы вторичного электропитания; на фиг, 2 и 3 - диаграммы, поясняющие работу системы на фиг. 4 - схема индикатора недогрузки всех преобразователей; на фиг. 5 схема индикатора полной загрузки более одного преобразователя.

СВЭП содержит п параллельно соединенных стабилизированных преобразователей 1 напряжения с ограничением нагрузочных токов, включенных между входными и выходными выводами, к выходным выводам через ключ 2 подключен резистор 3 подгрузки, п входов индикатора 4 недогрузки всех преобразователей и п входов индикатора 5 полной загрузки более одного преобразователя соединены соответственно с выходами индикации ограничения нагрузочных токов п преобразователей 1 напряжения, а выходы индикаторов 4 и 5 подключены соответственно к первому и второму входам триггера 6, выход которого соединен с управляющим входом ключа 2.

На фиг. 2 приведена зависимость суммарной величины тока преобразоватёлей 1 напряжения ны тока нагрузки I

пр

от величиXI

н«гр с учетом коммутируемого тока подгрузки I

ПОДГр.

Величина 1ЛОдгр выбрана меньше мак-

симально допустимой величины нагру- эфчного тока одного преобразователи 1пр.

СВЭП работает следующим образом.

При токе нагрузки IHe,rp, равном нулю, все преобразователи напряжения индицируют отсутствие полной нагрузк Индикатор 4 недогрузки всех преобразователей вырабатывает сигнал, устанавливающий триггер 6 в такое состоя ние, при котором ключ 2 удерживается открытым и, следовательно, резистор подгрузки оказывается подключенным к выходным выводам системы. При этом

ный преобразователь 1 будет нагружен примерно на 1/10 1П(МГр Если ток нагрузки I

н.

I

И« Р

1

Н,

пр

-1 /п ПоАгр),го суммарный

(где I

ток нагрузки преобразователей 1 на- пр

пряжения inp Inp + n-1/n 1полГр.

При этом ток нагрузки каждого преобразователя 2 напряжения в отдельности оказывается меньше Iпр.

ИНдикатор 4 нагрузки всех преобразователей продолжает вырабатывать сигнал установки триггера 6 в состояние, при котором ключ 2 удерживается открытым и резистор 3 подгрузки остается подключенным к выходным выводам системы.

При увеличении тока нагрузки в

Q 5

пределах I

1„р-1/п

MI

ныгр нз

(где I

2 (I

HI

ПОД Гр Д 4J- Пр

-1/п 1полгр) суммарный ток нагрузки преобразователей 1 напряжения оказывается больше 1П1, I

подгр,

но

0

5

токе нагрузки I

®

45 . JQ

меньше величины 2ln +n-2/n 1ПОЛГ. При этом один из преобразователей 1, выходное напряжение которого оказывается несколько больше, чем выходные напряжения других преобразователей ввиду разброса выходного номинала, берет на себя максимально допустимый нагрузочный ток и индицирует полную загрузку При этом ни индикатор 4 недогрузки всех преобразователей, ни индикатор 5 полной загрузки более одного преобразователя не вырабатывает сигналы установки триггера 6, поэтому последний сохраняет свое предыдущее состояние. Так, если триггер 6 удерживал ключ 2 открытым, то при

1м«гР 1Н3 триггер 6 также удерживает ключ 2 открытым и резистор 3 подгрузки остается подключенным к выходным выводам системы. i

При увеличении тока нагрузки до 1Наг- Iw суммарный ток нагрузки преобразователей 1 напряжения оказывается равным 21 пр + n-2/n 1п„дгр.При этом два из преобразователей 1, выходные напряжения которых оказываются несколько больше, чем выходные напряжения других преобразователей ввиду разброса выходного номинала, берут на себя максимально допустимый ток

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник питания постоянного напряжения | 1977 |

|

SU705434A1 |

| Источник питания постоянного напряжения | 1983 |

|

SU1145331A1 |

| Система вторичного электропитания | 1981 |

|

SU964903A1 |

| Источник питания постоянного напряжения | 1978 |

|

SU888084A2 |

| Многоразрядный сумматор по модулю | 2024 |

|

RU2831626C1 |

| Источник питания постоянного напряжения | 1984 |

|

SU1188715A1 |

| Стабилизатор постоянного напряжения | 1982 |

|

SU1032437A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1990 |

|

SU1777225A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2829093C1 |

| Способ обнаружения и локализации отказов вентильного электродвигателя | 1988 |

|

SU1640798A1 |

Изобретение относится к электротехнике, в частности к системам вторичного электропитания. Целью изобретения является обеспечение устойчивости работы при малых токах нагрузки вплоть до нуля при сохранении высокого значения КПД. Система вторичного электропитания обеспечивает стабилизацию выходного напряжения на холостом ходу или сильной недогрузке путем автоматического подключения резистора 3 подгрузки к выходным выводам. Нагрузочный ток всей системы оценивается по выходным сигналам индикации ограничения нагрузочных токов отдельных преобразователей 1 напряжения без специального датчика тока с помощью индикаторов 4 и 5. Дискретная обработка сигналов состояния преобразователей 1 позволяет получить высокий КПД системы. 2 з.п. ф-лы, 5 ил.

преобразователи 1 напряжения оказыва- и индицируют полную загрузку. На выются нагруженными на ток подгрузки In0ftrp (фиг. 2), достаточный для обеспечения стабилизации выходного напряжения системы. Каждый стабилизированходе индикатора 5 полной загрузки более одного преобразователя появляется сигнал, который устанавливает триггер 6 в противоположное состояние

ходе индикатора 5 полной загрузки более одного преобразователя появляется сигнал, который устанавливает триггер 6 в противоположное состояние,

515539636

при котором ключ 2 удерживается за- допустимый .нагрузочный ток, на выкрытым. При этом резистор 3 подгрузим отключается от выходных выводов системы и суммарный ток нагрузки преобразователей 1 напряжения уменьшается на величину тока подгрузки 1полгр и становится равным IНз 2(1пр- - 1/п 1пвдгр) . При этом на выходе индикатора 5 полной загрузки одного преобразователя исчезает сигнал установки триггера 6, Однако триггер 6 продолжает сохранять свое состояние,

10

ходе индикатора 4 недогрузки всех преобразователей исчезает сигнал установки триггера 6. Однако триггер 6 продолжает сохранять свое исходное состояние, при котором ключ 2 удерживается открытым, а резистор 3 подгрузки - подключенным к выходным выводам системы.

При дальнейшем уменьшении тока нагрузки системы суммарный-ток нагрузки преобразователей 1 X I пр больше тока нагрузки системы IWarp на величину

При дальнейшем уменьшении тока нагрузки системы суммарный-ток нагрузки преобразователей 1 X I пр больше тока нагрузки системы IWarp на величину

при котором ключ 2 удерживается закрытым, а резистор 3 подгрузки отклю-is тока П°ДГРУЗКИ 1 подгр,триггер 6 на- ченным от выходных выводов системы. ходится в исходном состоянии, при коПри дальнейшем увеличении тока тором ключ 2 замкнут и резистор 3 нагрузки суммарный ток нагрузки преобразователей 1 напряжения Zlnpравен

1нвгр,триггер 6 находится в таком состоянии, при котором ключ 2 закрыт, резистор 3 подгрузки отключен от выходных выводов системы. При токе нагрузки IMQrp IH4 (где Г + n-2/n I

Н4 21Пр +

подгр на выходе индикатора 25 5 полной загрузки более одного преобподгрузки подключен к выходным выводам системы.

20 На фиг. 3, где приведены эпюры напряжений и токов по узловым точкам схемы, приняты следующие обозначения: а - ток нагрузки 1нагр б - суммарный ток преобразователей lЈp j в - напряжение на ключе 2 U клюразователя вновь появляется сигнал, однако он не влияет на состояние триггера 6.

При изменении тока нагрузки в обратном направлении (уменьшении тока нагрузки системы) от номинальной величины до 1Нагр 1Н4 на выходе индикатора 5 полной загрузки более одного преобразователи исчезает сигнал установки триггера 6. Однако триггер 6 также продолжает сохранять свое состояние. При этом ключ 2 удерживается закрытым, а резистор 3 подгрузки - отключенным от выходных выводов системы.

ча 2, г напряжение на выходных выводах

U 8Ых На фиг. 4 показан пример реализа- 30 ции индикатора 4 недогрузки всех преобразователей в виде 7-входового элемента совпадения, а индикатора 5 полной загрузки более одного преобразователя в виде последовательно соеди- 35 ненных 7-входового сумматора однозарядных двоичных чисел и цифрового компаратора с порогом единица.

При уменьшении тока нагрузки системы до величины менее 1нг ни один из

ток 1пр, поэтому все преобразователи 1 напряжения индицируют отсутствие

Здесь лог. О на входе соответствует недогруженному состоянию, а 40 лог о 1 - состоянию ограничения нагрузочного тока преобразователя 1.

7-входовой элемент совпадения выполнен на двух элементах 4 ИЛИ-НЕ и

преобразователей 1 напряжения не будет одном 2И. Состояние лог. 1 на вы- нагружен на максимально допустимой д ходе индикатора 4 возможно только в

том случае, если все сигналы индика-- ции ограничения нагрузочных токов пре- полной загрузки. При этом на выходе индикатора 4 недогрузки всех преобразователей вырабатывается сигнал, ко- 50 °ДИН иэ семи сигналов индикации огра- торый возвращает триггер 6 в исходное ничения нагрузочных токов преобразо- состояние, при котором ключ 2 открыва- вателей 1 напряжения является лог 1, ется и резистор 3 подгрузки подключа- на выходе индикатора 4 будет лог. О, ется к выходным выводам системы. Сум- 7-входовой сумматор одноразрядных марный ток нагрузки преобразователей „ двоичных чисел выполнен на двух пол- 1 напряжения IrtA увеличивается скач- ных одноразрядных сумматорах 2ТИ /L4 ком на величину тока подгрузки IpoArf. и одном двухразрядном сумматоре5 3, При этом один из преобразователей 1 Индикатор 5 работает следующим об- напряжения берет на себя максимально разом.

образователен 1 напряжения находятся в состоянии лог. О. Если хотя бы

ходе индикатора 4 недогрузки всех преобразователей исчезает сигнал установки триггера 6. Однако триггер 6 продолжает сохранять свое исходное состояние, при котором ключ 2 удерживается открытым, а резистор 3 подгрузки - подключенным к выходным выводам системы.

При дальнейшем уменьшении тока нагрузки системы суммарный-ток нагрузки преобразователей 1 X I пр больше тока нагрузки системы IWarp на величину

s тока П°ДГРУЗКИ 1 подгр,триггер 6 на- ходится в исходном состоянии, при котором ключ 2 замкнут и резистор 3

подгрузки подключен к выходным выводам системы.

На фиг. 3, где приведены эпюры напряжений и токов по узловым точкам схемы, приняты следующие обозначения: а - ток нагрузки 1нагр б - суммарный ток преобразователей lЈp j в - напряжение на ключе 2 U ключа 2, г напряжение на выходных выводах

U 8Ых На фиг. 4 показан пример реализа- ции индикатора 4 недогрузки всех преобразователей в виде 7-входового элемента совпадения, а индикатора 5 полной загрузки более одного преобразователя в виде последовательно соеди- ненных 7-входового сумматора однозарядных двоичных чисел и цифрового компаратора с порогом единица.

том случае, если все сигналы индика-- ции ограничения нагрузочных токов пре °ДИН иэ семи сигналов индикации огра- ничения нагрузочных токов преобразо- вателей 1 напряжения является лог 1 на выходе индикатора 4 будет лог. О 7-входовой сумматор одноразрядных двоичных чисел выполнен на двух пол- ных одноразрядных сумматорах 2ТИ /L4 и одном двухразрядном сумматоре5 3, Индикатор 5 работает следующим об- разом.

образователен 1 напряжения находятся в состоянии лог. О. Если хотя бы

На входы каждого одноразрядного полного сумматора 2L 1 и 5 (фиг. 4) подаются по три сигнала индикации ограничения нагрузочных токов от преобразователей 1 напряжения. На выходах этих сумматоров получаются два 2-разрядных двоичных числа , и S2.jS17. Далее эти числа складываются на двухразрядном сумматоре седьмым сиг- налом индикации ограничения нагрузочного тока седьмого преобразователя 1 напряжения. На выходе сумматора получаем 3-разрядное двоичное число S33S23Slj, отображающее количество полностью загруженных по току преобразователей t. Например, при одном (любом) загруженном преобразователе на выходе сумматора присутствует код 001, при трех -011, при пяти 101 и т.д.

Этот код поступает на входы первого числа (А) микросхемы цифрового компаратора. На входы второго числа (В) постоянно подается код 001. В таком включении микросхема цифрового Компаратора сравнивает число А с чис- Лом 001 и определяет знак неравенства вызывая сигнал лог. 1 на соответствующем выходе при А В. Так как В 001, а число А равно числу полностью загруженных по току преобразователей 1, то на выходе цифрового компаратора лог. 1 появляется, если число полностью загруженных по току преобразователей 1 будет больше Одного, т.е. этот выход и является выходом индикатора 5.

На фиг. 5 приведен гример реализации индикатора 4 недогрузки всех преобразователей и индикатора 5 полной загрузки более одного преобразователя в виде последовательно соединенных п-входового сумматора IE одноразрядных двоичных чисел и дешифратора ДС с двумя выходами (). Структура, работа и выходные сигналы сумматора описаны выше применительно к схеме фиг. 4.

На схеме фиг о 5 двоичное число S3S2S1, отображающее количество пол- ностью загруженных по току преобразователей 1, поступа ет с выхода сумматора на выходы дешифратора ДС, выполненного, в частности, на элементах 3 ИЛИ-НЕ и 2 ИЛИ.

Здесь лог. 1 на выходе индикатора 4 появляется лишь в том случае, если двоичное число S3S2S1 равно 0000 (т.е. количество полностью загру

„ )

5 5 0

0

0

5

женных по току преобразователей 1 равно нулю).

Если хотя бы один из разрядов двоичного числа S3S2S1 равен 1, на вы ходе индикатора 4 будет лог. О.

К входам логического элемента 2 ИЛИ подключены выходы старших разрядов S3 и S2 сумматора Ц .

При количестве полностью загруженных по току преобразователей 1, равном нулю или одному, значения обоих разрядов S3 и S2 двоичного числа S3S2S1 равны О. При большем количестве полностью загруженных по току преобразователей 1 хотя бы в одном из разрядов S2 или S3 будет лог„ 1 и, следовательно s на выходе индикатора 5 также будет лог 1.

Таким образом, предлагаемая система вторичного электропитания обеспечивает стабилизацию выходного напряжения на холостом ходу или сильной недогрузке путем автоматического подключения резистора 3 подгрузки к выходным вьюодам.

Высокий КПД в СВЭП обеспечен за счет дискретной обработки сигналов состояния стабилизированных преобразователей 1 напряжения, позволяющий оценить величину тока нагрузки системы без резистивиого датчика суммарного тока, на котором дополнительно теряется мощность.

Формула изобретения

вателей напряжения, а выходы индикатора недогрузки всех преобразователей и индикатора полной загрузки более одного преобразователя подключены соответственно к первому и второму входам триггера, выход которого соединен с управляющим входом ключа.

ю щ а я с я тем, что индикатор недо- JQ входы сумматора являются входами ингрузки всех преобразователей выполнен в виде n-входового элемента совпадения, а индикатор полной загрузки более одного преобразователя выполнен в виде последовательно соединенных 15 n-входового сумматора одноразрядных двоичных чисел и цифрового компаратора с порогом Единица.

дикаторов, первый выход дешифратора двоичных чисел, меньших единицы, использован в качестве выхода индикатора недогрузки всех преобразователей, а второй выход дешифратора двоичных чисел, больших единицы, - в качестве выхода индикатора полной загрузки более одного преобразователя.

3

10

дикаторов, первый выход дешифратора двоичных чисел, меньших единицы, использован в качестве выхода индикатора недогрузки всех преобразователей, а второй выход дешифратора двоичных чисел, больших единицы, - в качестве выхода индикатора полной загрузки более одного преобразователя.

Ситыы индикации ограничения tm- рузочныл /шо9&& weofytaofame- o|- лей напряжения о4- rtJL

Составитель А.Волкова Редактор Л.Веселовская Техред А.Кравчук

Заказ 456

Тираж 652

ВНШПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, JK-35, Раушская наб., д. 4/5

0

вшод

о

индю&зтор&5

Корректор М.Кучерявая

Подписное

| Механизм для вращения навойника в гильзовых машинах | 1925 |

|

SU5331A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Система вторичного электропитания | 1985 |

|

SU1328802A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-03-30—Публикация

1987-10-05—Подача