ел ел

00

со

00 00

31553988

Изобретение относится к автоматике и вычислительной технике и может быть использовано в электроизмерительных устройствах.с

Цель изобретения - повышение быстродействия при сохранении точности интегрирования.

На фиг. 1 представлена схема аналогового интегратора напряжения; на JQ фиг. 2 - вариант выполнения блока выделения постоянной составляющей, выполненной на пассивных фильтрах нижних частот.

К;(Р)

P4R,CHR10C,a-f PC12(R9 + R(0) + 1

где R сопротивление резисторов с соответствующим его номеру индексом;

€„,€,Ј- емкость конденсаторов с со ответствующим его номеру индексом.

Из выражения (2) следует, что для постоянного тока () K;(p)K-(t и К(р),т,е. постоянная составляю щая передается без изменения. Пере.„/ .i менная составляющая каждый фильтром

Аналоговый интегратор (см. фиг. 1) t.о,Jнизких частот ослабляется. Выбрав

содержит информационный вход 1, ин- н

соответствующее число N фильтров мо но добиться сколь угодно малого зна чения переменного напряжения на выхо де блока 6. Напряжение с выхода бло 6 через делитель 4, имеющий коэффици ент передачи ,5, поступает на н инвертирующий вход сумматора 5i инв тирующий вход которого соединен с в ходом интегрирующего усилителя 2. На ряжение на выходе интегратора

тегрирующий усилитель 2 с разрядным ключем 3 в цепи обратной связи, делитель k напряжения,.сумматор 5 напря25

дом интегратора, и блок 6 выделения постоянной составляющей, состоящий из N последовательно соединенных фильтров 7 нижних частот (ФНЧ).

Фильтр 7 нижних частот содержит операционный усилитель 8, два резистора 9,to и два интегрирующих конденсатора 11,12.

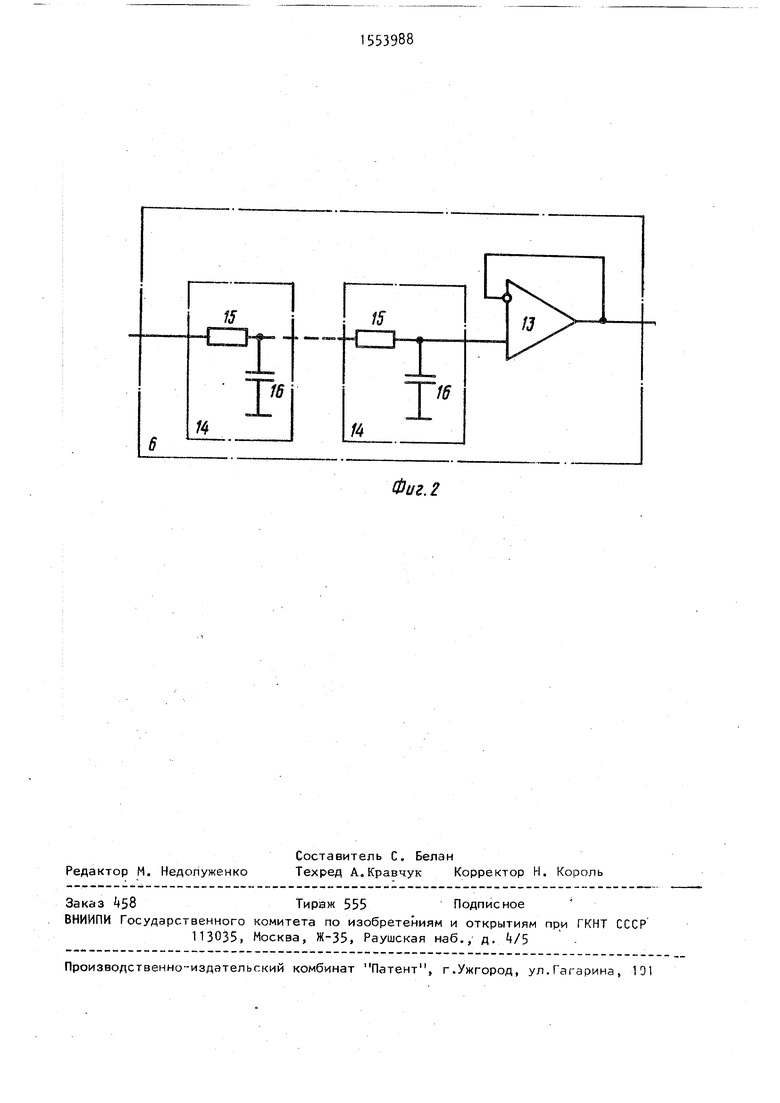

Один из вариантов выполнения блока 6 (см„ фиг. 2} содержит операцией- 30 ный усилитель 13 и 11 фильтров нижних частот 14, состоящих из резистора 15 и конденсатора 16.

Аналоговый интегратор работает сле- дующим образом.

Напряжение с входа 1 интегрируется интегрирующим усилителем 2, на выходе которого кроме переменной составляющей содержится паразитная постоянная составляющая, которая вьГделяет- 4Q ся блоком 6 и через делитель 4 поступает на неинвертирующий вход сумматора 5, где вычитается из выходного сигнала инвертирующего усилителя 2, поступающего на инвертирующий вход сум- 45 матора 5«

Активные филыры 7 не влияют друг на друга, так как имеют большое входное и малое выходное сопротивление. $0

Передаточная функция блока 6 выделения постоянной составляющей

К(Р)«К,(Р.) Кй (Р) ,..,,

N чП К;(Р).

К„(Р)

Для активного фильтра НЧ 7 передаточная функция

К;(Р)

P4R,CHR10C,a-f PC12(R9 + R(0) + 1

(2)

где R сопротивление резисторов с соответствующим его номеру индексом;

€„,€,Ј- емкость конденсаторов с соответствующим его номеру индексом.

Из выражения (2) следует, что для постоянного тока () K;(p)K-(t и К(р),т,е. постоянная составляющая передается без изменения. Пере н

5

соответствующее число N фильтров можно добиться сколь угодно малого значения переменного напряжения на выходе блока 6. Напряжение с выхода блока 6 через делитель 4, имеющий коэффициент передачи ,5, поступает на неинвертирующий вход сумматора 5i инвертирующий вход которого соединен с выходом интегрирующего усилителя 2. Напряжение на выходе интегратора

ивыГ ()Кс. де (U +U)

+ ILK,

к

с

и

«О Ке выходное напряжение интегрирующего усилителя 2 (tlv,- переменная, а U - постоянная составляющие) ;

выходное напряжение блока 6;

коэффициенты передачи сумматора 5 соответственно по инвертирующему и неинвертирующему входам.

4Q45

$0

55

Из выражения (3) видно, что при К -1, К 2 происходит компенсация постоянного напряжения на выходе интегратора, поскольку и U.

Так как в предлагаемом устройстве блок 6 вынесен из цепи обратной связи и все блоки соединены последовательно, то очевидно, что быстродействие устройства определяется быстродействием блока 6, которое можно оценить, найдя полюсы передаточной функции (1).

Так как передаточная функция блока 6 (1) определяется произведением передаточных функций фильтров нижних частот при равенстве параметров всех активных фильтров и имеет действительный корень Р- кратности 2N, то переходныи процесс описывается выражением (6):

еР

-2N

Z

B;t

г-«

- постоянные интегрирования, а его длительность определяется полюсом Р; . выражения (3) видно, что посто- ю ройств.

времени блока 6

Возможн стродей преимущ 5 ред дру в котор составл связи, возраст

ю ройств.

Возможность обеспечения высокого быстродействия является существенным преимуществом данного интегратора пе- 5 ред другими известными устройствами, в которых блок выделения постоянной составляющей включен в цепь обратной связи, что приводит к существенному возрастанию инерционности таких уст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения модуля (его варианты) | 1983 |

|

SU1354212A1 |

| Интегратор | 1989 |

|

SU1615752A1 |

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Аналоговый интегратор переменного напряжения | 1986 |

|

SU1336047A1 |

| ПЕРЕСТРАИВАЕМЫЙ ARC-ФИЛЬТР | 1995 |

|

RU2110140C1 |

| Коррелятор | 1980 |

|

SU894733A1 |

| ИНТЕГРАТОР С БОЛЬШИМ ВРЕМЕНЕМ ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2034331C1 |

| ФИЛЬТР ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2001 |

|

RU2204883C1 |

| АКТИВНЫЙ RC-ФИЛЬТР | 1990 |

|

RU2019024C1 |

| Аналоговый интегратор | 1980 |

|

SU886010A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в электроизмерительных устройствах. Цель изобретения - повышение быстродействия при сохранении точности интегрирования. Аналоговый интегратор содержит интегрирующий усилитель 2, делитель напряжения 4, сумматор 5 и блок выделения 6 постоянной составляющей. Блок выделения постоянной составляющей включен в прямую цепь, поэтому интегратор имеет высокое быстродействие и малую инерционность при сохранении точности интегрирования. 1 з.п. ф-лы, 2 ил.

Ј- -1. Р;Г

Формула изобретения

ния, отличающийся

ратора0 Это вывод справедлив и при

С

При выполнении блока 6 на пассив 2°

ных фильтрах низких часто уменьшает- 25 интегрирующего усилителя, соединен- ся количество OY, однако для получения передаточной функции вида (1) необходимо выполнение условия

ному с входом блока выделения постоянной составляющей, выход которого через делитель напряжения подключен к второму входу сумматора.

z, :

«- г

п

где Z,,,.., Zn- импедансы ФНЧ.

Таким образом, положительный эффект, получаемый при использовании предлагаемого устройства, заключается в компенсации постоянной составляющей, имеющейся на выходе основного OY 6 при интегрировании переменных сигналов. Причем предлагаемое решение уменьшает постоянные времени, что позволяет сохранить высокое быстродействие при подаче напряжения на вход устройства, и, кроме того, снижает влияние длительного переходного

через первый интегрирующий конденса- процесса при уменьшении входного нап- 45 тор подключен к выходу операционного ряжения, так как в этом случае проис- усилителя, неинвертирующий вход кото- ходит компенсация на выходе интегра-Р°го через второй интегрирующий контора и медленно изменяющейся постоян- денсатор соединен с шиной нулевого ной {квазипостоянной} составляющей..потенциала.

Формула изобретения

ния, отличающийся

ния, в него введен сумматор, выход которого является выходом интегратора, первый вход подключен к выходу

интегрирующего усилителя, соединен-

ному с входом блока выделения постоянной составляющей, выход которого через делитель напряжения подключен к второму входу сумматора.

15

15

П

Фиг, 2

| Волгин Л.И., Матча к A.I | |||

| Интегрирующие устройства без накопления погрешности от смещения нуля | |||

| - Измерения, контроль, автоматизация, 1975, № 2, с | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Интегрирующее устройство | 1984 |

|

SU1239731A1 |

Авторы

Даты

1990-03-30—Публикация

1987-11-18—Подача