(54) АНАЛОГОВЫЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегрирующее устройство | 1983 |

|

SU1105903A1 |

| ИНТЕГРАТОР С ОБНУЛЕНИЕМ | 1991 |

|

RU2015556C1 |

| Интегратор | 1978 |

|

SU748439A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Интегрирующее устройство | 1984 |

|

SU1195362A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841056A1 |

| Коррелятор | 1980 |

|

SU894733A1 |

| Интегратор | 1979 |

|

SU834715A1 |

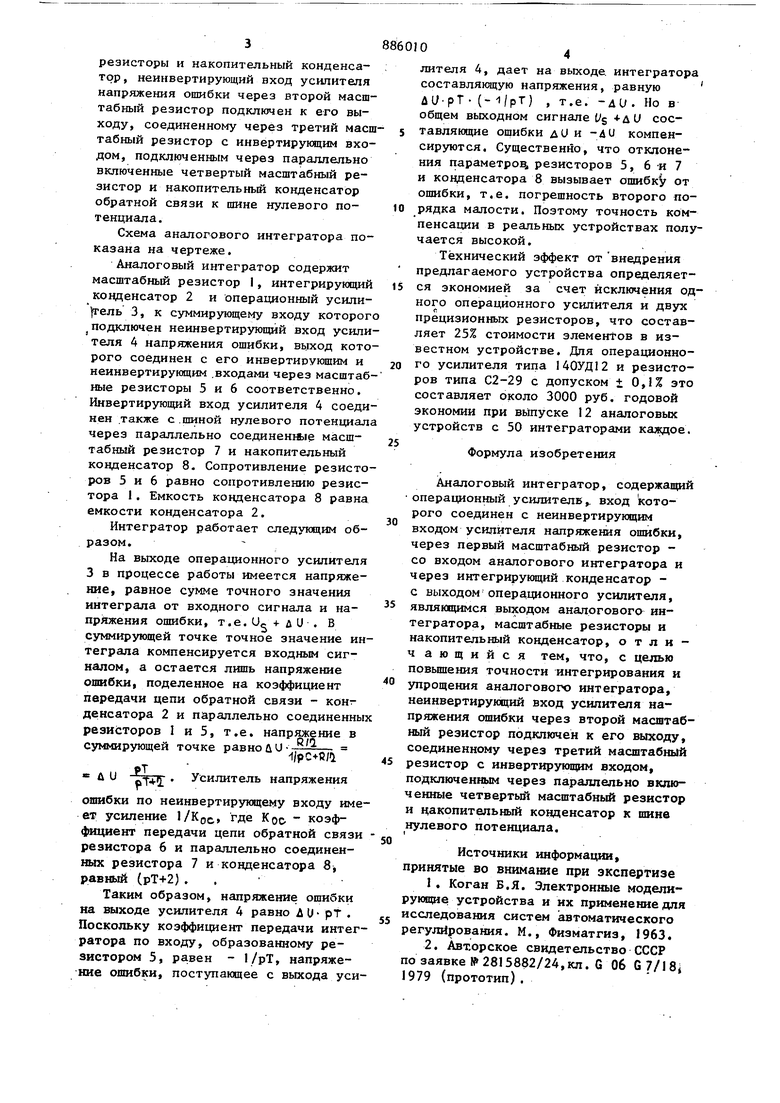

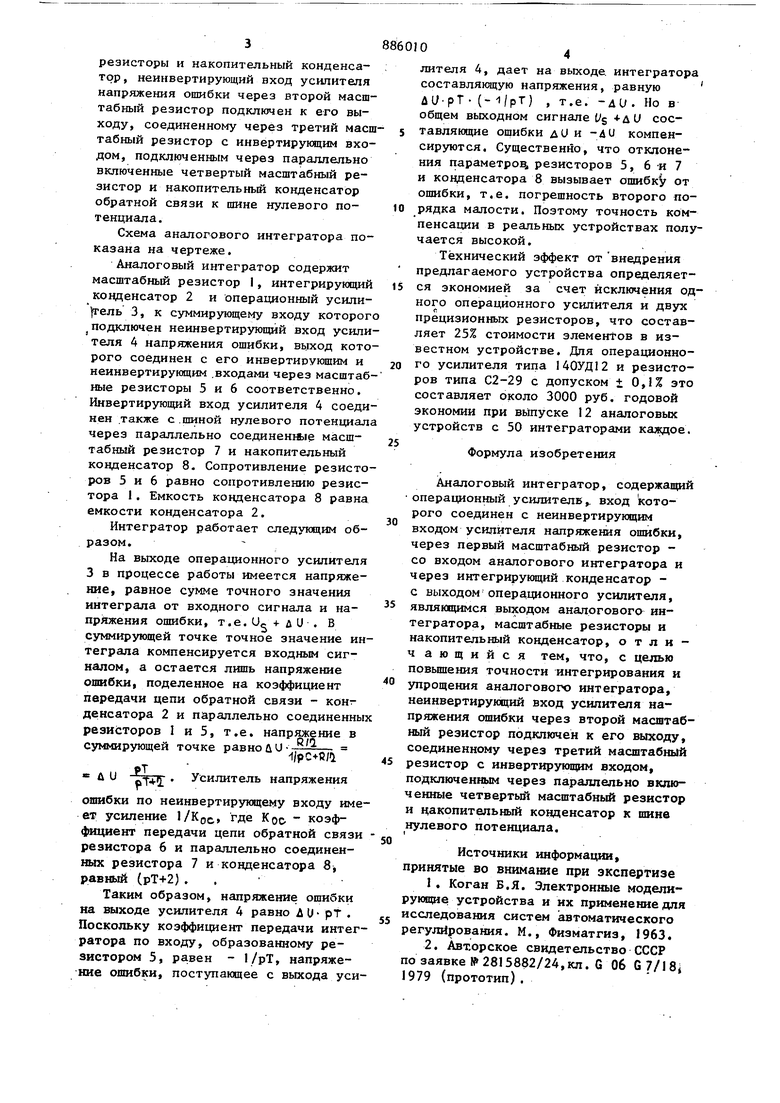

Изобретение относится к аналоговым измерительным и вычислительным устройствам, а именно к решающим блокам таких устройств - аналоговым интеграторам. Известен аналоговый интегратор, состоящий из входного резистора, конденсатора обратной связи и операцион ного усилителя l. Известный интегратор характеризует ся увеличением ошибки интегрирования при недостаточном коэффициенте усиления, операционного усилителя, например, при повьшенной частоте входного сигнала. Наиболее близким по технической сущности к предлагаемому является ин тегратор, содержащий интегрирующий усипитель, усипитель напряжения ошиб ки и дополнительный масштабный усилитель 2.. Однако существенный недостаток указанного интегратора состоит в необходимости применения дополнительно го масштабного усилителя с двумя прецизионными входными резисторами. Относительная погрешность этих резисторов заметно ухудшает компенсацию ошибки интегрирования. Цель изобретения - повьш1ение точности интегрирования и упрощение аналогового интегратора за счет устранения дополнительного масштабного усилителя и вычитания соответствующим образом сформированного сигнала ошибки непосредственно на входе интегратора. Указанная цель достигается тем, что в аналоговом интеграторе, содержащем операционнь1й усилитель, вход которого соединен с неинвертируюпцш входом усилителя напряжения опшбки, через первый масштабный резистор - со входом аналогового интегратора и через интегрирующий конденсатор - с выходом операционного усилителя, являющимся выходом аналогового интегратора, масштабные резисторы и накопительный конденсатор, неинвертирующий вход усилителя напряжения ошибки через второй масштабный резистор подключен к его выходу, соединенному через третий масш табный резистор с инвертирующим входом, подключенным через параллельно включенные четвертый масштабный резистор и накопительный конденсатор обратной связи к шине нулевого потенциала. Схема аналогового интегратора показана на чертеже. Аналоговый интегратор содержит масштабный резистор I, интегрирующий ковденсатор 2 и операционный усили ель 3, к суммирующему входу которог подключен неинвертирующий вход усили теля 4 напряжения ошибки, выход кото рого соединен с его инвертирующим и неинвертирующим .входами через масштаб иые резисторы 5 и 6 соответственно. Инвертирующий вход усилителя 4 соеди нен .также с.шиной нулевого потенциал через параллельно соадиненгые масштабный резистор 7 и накопительный конденсатор 8. Сопротивление резисто ров 5 и 6 равно сопротивлению резистора 1. Емкость конденсатора 8 равна емкости конденсатора 2. Интегратор работает следующим образом. На выходе операционного усилителя 3 в процессе работы имеется напряжение, равное сумме точного значения интеграла от входного сигнала и напряжения ошибки, т.е. и + д и . В суммирующей точке точное значение ин теграла компенсируется входным сигналом, а остается лишь напряжение ошибки, поделенное на коэффициент передачи цепи обратной связи - конде;нсатора 2 и параллельно соединенны резисторов I и 5, т.е. напряжение в суммирующей точке равно и U . р.;. -bvfJj:. Усилитель напряжения ошибки по неинвертирующему входу име ет усиление l/Kpe,, где Кос- коэффициент передачи цепи обратной связи резистора 6 и параллельно соединенных резистора 7 и конденсатора 8, равный (рТ+2). , Таким образом, напряжение ошибки на выходе усилителя 4 равно Л U рТ . Поскольку коэффициент передачи интег ратора по входу, образованному резистором 5, равен - 1/рТ, напряжение ошибки, поступающее с выхода уси лителя 4, дает на выходе, интегратора составляклцую напряжения, равную uUpT-(-i/pT) ,т.е. -ди.Новобщем выходном сигнале fg составляющие ошибки дО и -ли компенсируются. Существенно, что отклонения параметров резисторов 5, 6 -и 7 и конденсатора 8 вызывает ошибк от ошибки, т.е. погрешность второго порядка малости. Поэтому точность компенсации в реальных устройствах получается высокой. Технический эффект от внедрения предлагаемого устройства определяется экономней за счет исключения одного операционного усилителя и двух прецизионных резисторов, что составляет 25% стоимости элементов в известном устройстве. Для операционного усилителя типа 140УД12 и резисторов типа С2-29 с допуском ± 0,1% это составляет около 3000 руб. годовой экономии при выпуске 12 аналоговых устройств с 50 интеграторами каждое. Формула изобретения Аналоговый интегратор, содержащий операционный усилителе,, вход Которого соединен с неинвертирующим входом усилителя напряжения ошибки, через первый масштабный резистор со входом аналогового интегратора и через интегрирующий конденсатор с выходом операционного усилителя, ЯВЛЯК1ЦИМСЯ выходом аналогового интегратора, масштабные резисторы и накопительный конденсатор, о т л и - ч ающийся тем, что, с целью повьшгения точности интегрирования и упрощения аналогового интегратора, неинвертирующий вход усилителя напряжения ошибки через второй масштабный резистор подключен к его выходу, соединенному через третий масштабный резистор с инвертирующим входом, подключенным через параллельно включенные четвертьп1 масштабный резистор и накопительный ковденсатор к шине нулевого потенциала. Источники информации, ринятые во внимание при экспертизе 1.Коган Б.Я. Электронные моделиующие устройства и их применение для сследования систем автоматического егулирования. М., Физматгиз, 1963. 2.Авторское свидетельство СССР о заявке 2815882/24, кл. G Об G 7/18i 1979 (прототип).

выдг

Авторы

Даты

1981-11-30—Публикация

1980-02-06—Подача