Изобретение относится к электротехнике и может быть использовано в электроприводе турбомеханизмов, конвейеров И ТоДо

Цель изобретения - улучшение энергетических показателей электропривода.

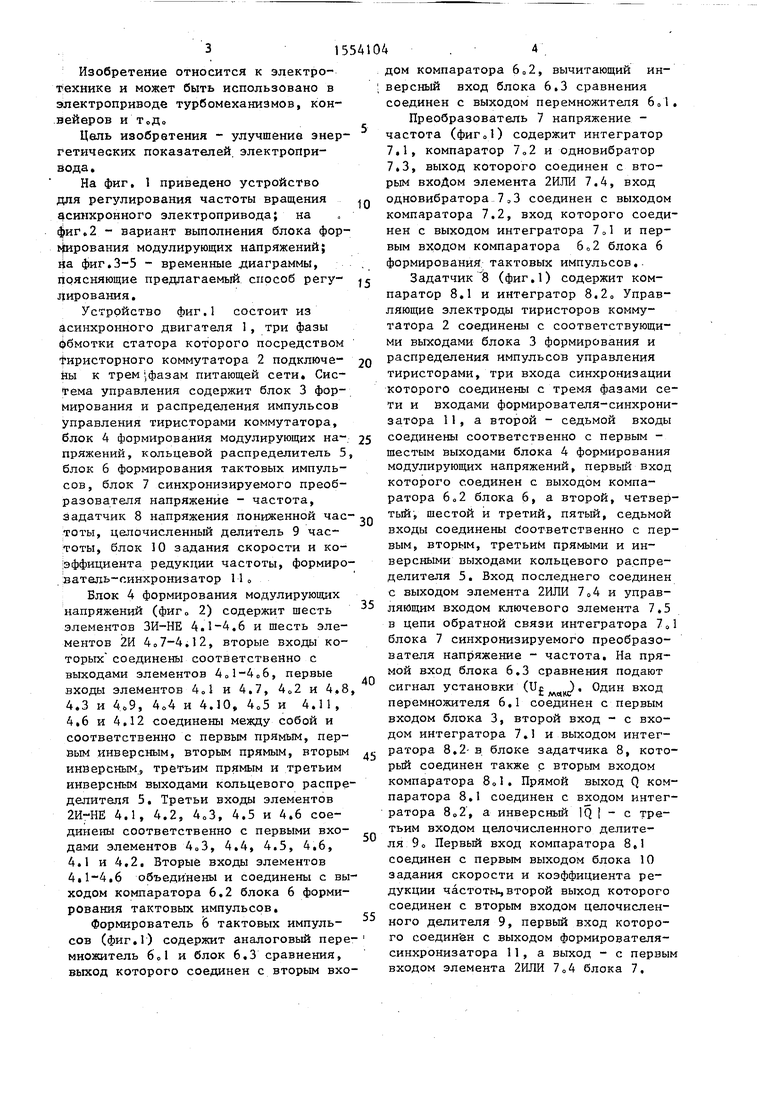

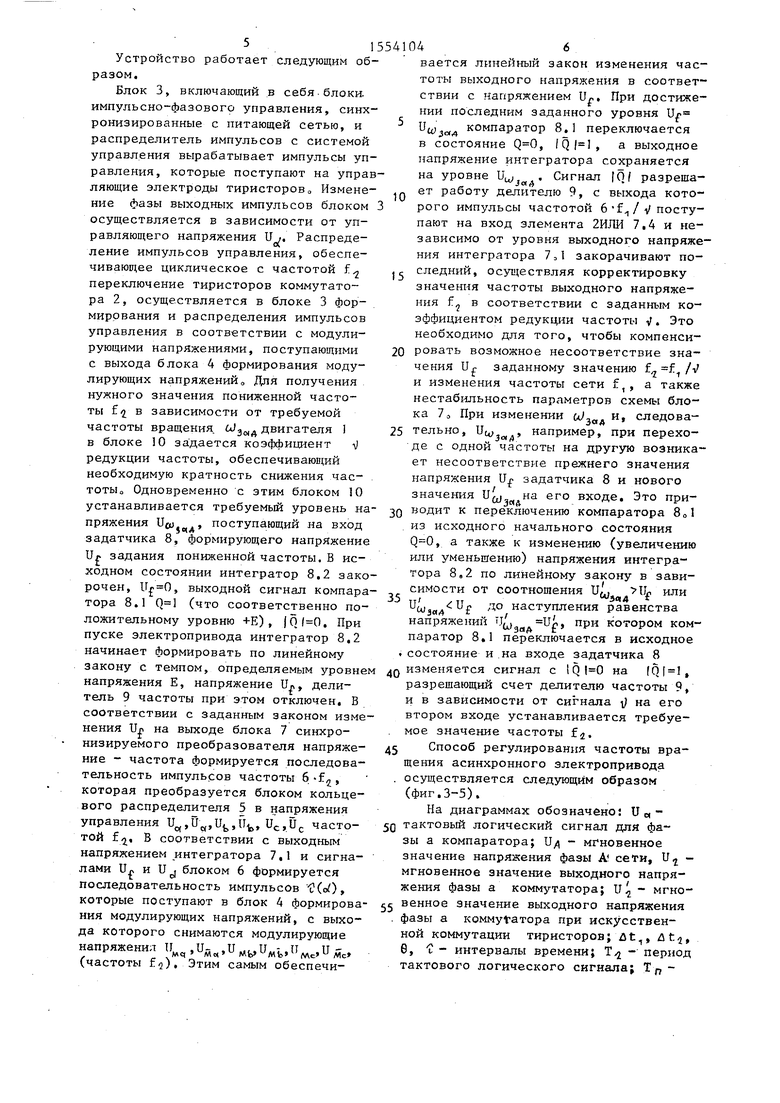

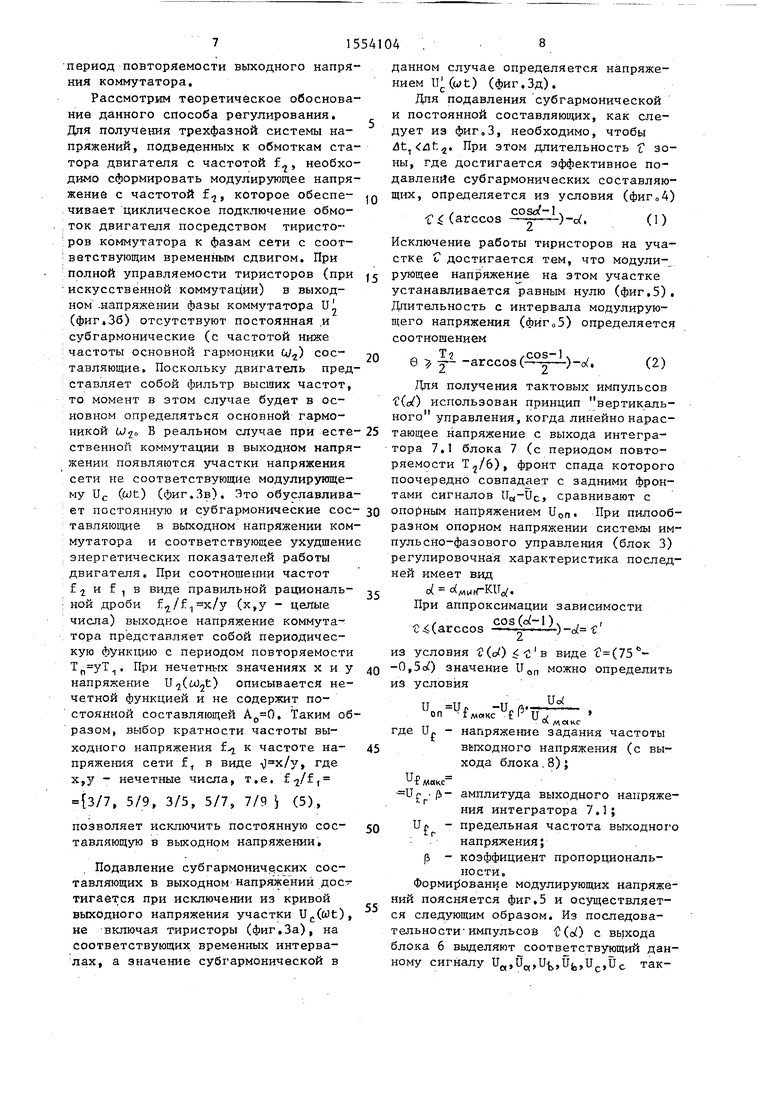

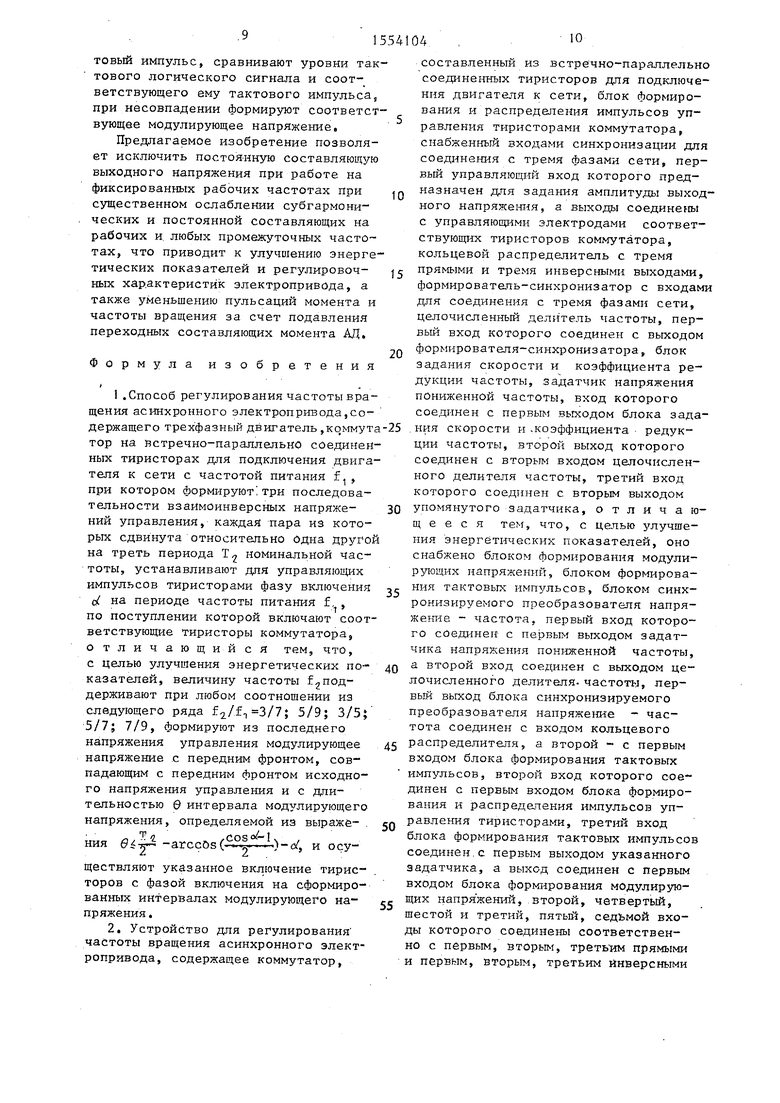

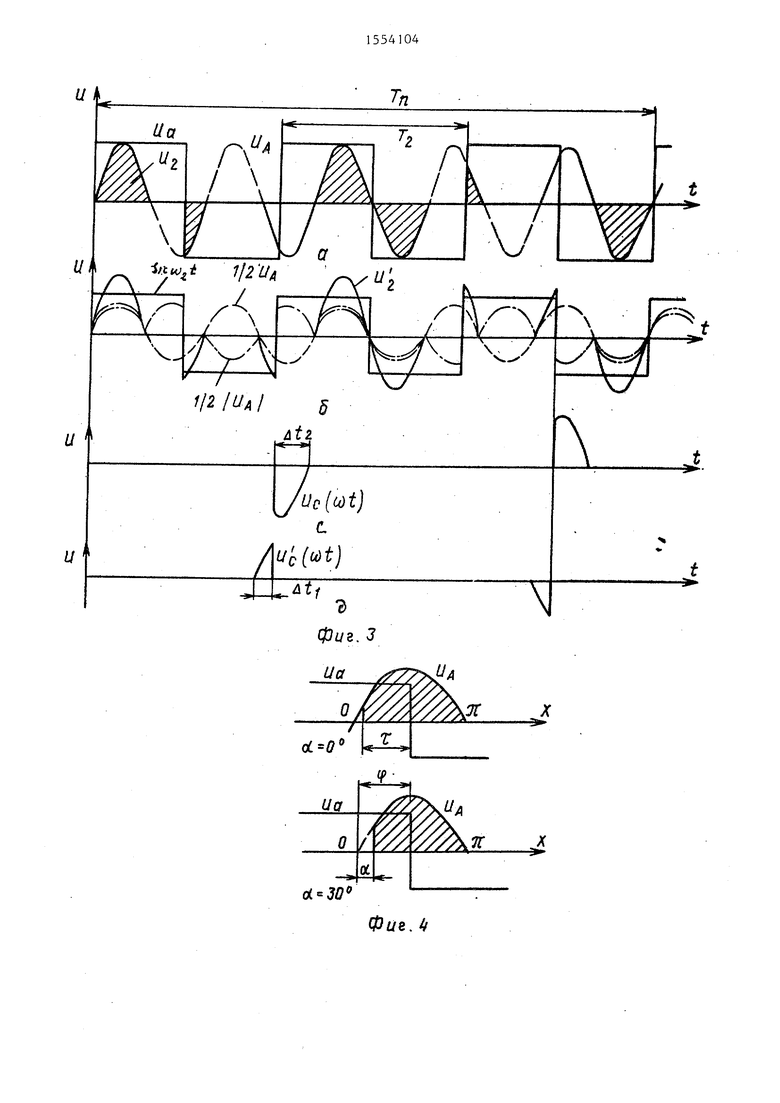

На фиг. 1 приведено устройство для регулирования частоты вращения синхронного электропривода; на фиг.2 - вариант выполнения блока фор- 1 ирования модулирующих напряжений; на фиг.3-5 - временные диаграммы, поясняющие предлагаемый способ регу- .ирования.

Устройство фиг.1 состоит из асинхронного двигателя 1, три фазы Обмотки статора которого посредством тиристорного коммутатора 2 подключены к трем )фазам питающей сети. Система управления содержит блок 3 формирования и распределения импульсов управления тиристорами коммутатора, блок 4 формирования модулирующих напряжений, кольцевой распределитель 5, блок 6 формирования тактовых импульсов, блок 7 синхронизируемого преобразователя напряжение - частота,

10

15

20

25

дом компаратора 6„2, вычитающий инверсный вход блока 6,3 сравнения соединен с выходом перемножителя 6„1

Преобразователь 7 напряжение - частота (фиг„1) содержит интегратор 7.1, компаратор 7„2 и одновибратор 7,3, выход которого соединен с вторым вхоДом элемента 2ИЛИ 7.4, вход одновибратора 7,3 соединен с выходом компаратора 7,2, вход которого соединен с выходом интегратора 701 и первым входом компаратора 6„2 блока 6 формирования тактовых импульсов.

Задатчик 8 (фиг.1) содержит компаратор 8.1 и интегратор 8.2„ Управляющие электроды тиристоров коммутатора 2 соединены с соответствующими выходами блока 3 формирования и распределения импульсов управления тиристорами, три входа синхронизации которого соединены с тремя фазами сети и входами формирователя-синхронизатора 11, а второй - седьмой входы соединены соответственно с первым - шестым выходами блока 4 формирования модулирующих напряжений, первый вход которого соединен с выходом компаратора 6„2 блока 6, а второй, четверзадатчик 8 напряжения пониженной час-,п тый шестой и третий, пятый, седьмой

тоты, целочисленный делитель 9 частоты, блок 10 задания скорости и коэффициента редукции частоты, формирователь-синхронизатор 11 о

Блок 4 формирования модулирующих напряжений (фиг„ 2) содержит шесть элементов ЗИ-НЕ 4.1-4.6 и шесть элементов 2И 4о7-4.12, вторые входы которых соединены соответственно с выходами элементов 401-406, первые входы элементов 401 и 4.7, 4„2 и 4.8, 4.3 и 4о9, 404 и 4.30, 405 и 4.11, 4.6 и 4,12 соединены между собой и соответственно с первым прямым, первым инверсным, вторым прямым, вторым инверсным, третьим прямым и третьим инверсным выходами кольцевого распределителя 5. Третьи входы элементов 2И-НЁ 4.1, 4.29 4„3, 4.5 и 4.6 соединены соответственно с первыми входами элементов 4„3, 4.4, 4.5, 4,6, 4.1 и 4.2. Вторые входы элементов 4.1-4.6 объединены и соединены с выходом компаратора 6.2 блока 6 формирования тактовых импульсов.

Формирователь 6 тактовых импульсов (фиг.1) содержит аналоговый перемножитель 6„1 и блок 6.3 сравнения, выход которого соединен с вторым вхо35

40

45

50

55

входы соединены «Соответственно с первым, вторым, третьим прямыми и инверсными выходами кольцевого распределителя 5. Вход последнего соединен с выходом элемента 2ИЛИ 704 и управляющим входом ключевого элемента 7,5 в цепи обратной связи интегратора 7„ блока 7 синхронизируемого преобразователя напряжение - частота. На прямой вход блока 6.3 сравнения подают сигнал установки (Up ), Один вход

перемножителя 6.1 соединен с первым входом блока 3, второй вход - с входом интегратора 7.1 и выходом интегратора 8.2 в блоке задатчика 8, который соединен также с вторым входом компаратора 8„1. Прямой выход Q компаратора 8.1 соединен с входом интегратора 8„2, а инверсный 1Q - с третьим входом целочисленного делителя 9о Первый вход компаратора 8,1 соединен с первым выходом блока 10 задания скорости и коэффициента редукции частоты, второй выход которого соединен с вторым входом целочисленного делителя 9, первый вход которого соединён с выходом формирователя- синхронизатора 11, а выход - с первым входом элемента 2ИЛИ 704 блока 7,

5

0

5

дом компаратора 6„2, вычитающий инверсный вход блока 6,3 сравнения соединен с выходом перемножителя 6„1.

Преобразователь 7 напряжение - частота (фиг„1) содержит интегратор 7.1, компаратор 7„2 и одновибратор 7,3, выход которого соединен с вторым вхоДом элемента 2ИЛИ 7.4, вход одновибратора 7,3 соединен с выходом компаратора 7,2, вход которого соединен с выходом интегратора 701 и первым входом компаратора 6„2 блока 6 формирования тактовых импульсов.

Задатчик 8 (фиг.1) содержит компаратор 8.1 и интегратор 8.2„ Управляющие электроды тиристоров коммутатора 2 соединены с соответствующими выходами блока 3 формирования и распределения импульсов управления тиристорами, три входа синхронизации которого соединены с тремя фазами сети и входами формирователя-синхронизатора 11, а второй - седьмой входы соединены соответственно с первым - шестым выходами блока 4 формирования модулирующих напряжений, первый вход которого соединен с выходом компаратора 6„2 блока 6, а второй, четвер5

0

5

0

5

входы соединены «Соответственно с первым, вторым, третьим прямыми и инверсными выходами кольцевого распределителя 5. Вход последнего соединен с выходом элемента 2ИЛИ 704 и управляющим входом ключевого элемента 7,5 в цепи обратной связи интегратора 7„1 блока 7 синхронизируемого преобразователя напряжение - частота. На прямой вход блока 6.3 сравнения подают сигнал установки (Up ), Один вход

перемножителя 6.1 соединен с первым входом блока 3, второй вход - с входом интегратора 7.1 и выходом интегратора 8.2 в блоке задатчика 8, который соединен также с вторым входом компаратора 8„1. Прямой выход Q компаратора 8.1 соединен с входом интегратора 8„2, а инверсный 1Q - с третьим входом целочисленного делителя 9о Первый вход компаратора 8,1 соединен с первым выходом блока 10 задания скорости и коэффициента редукции частоты, второй выход которого соединен с вторым входом целочисленного делителя 9, первый вход которого соединён с выходом формирователя- синхронизатора 11, а выход - с первым входом элемента 2ИЛИ 704 блока 7,

Устройство работает следующим образом.

Блок 3, включающий в себя блоки, импульсно-фазового управления, синхронизированные с питающей сетью, и распределитель импульсов с системой управления вырабатывает импульсы управления, которые поступают на управляющие электроды тиристоров„ Изменение фазы выходных импульсов блоком осуществляется в зависимости от управляющего напряжения U. Распределение импульсов управления, обеспечивающее циклическое с частотой f переключение тиристоров коммутатора 2, осуществляется в блоке 3 формирования и распределения импульсов управления в соответствии с модулирующими напряжениями, поступающими с выхода блока 4 формирования модулирующих напряжений о Для получения нужного значения пониженной частоты в зависимости от требуемой частоты вращения Л$ЫА двигателя 1 в блоке 10 задается коэффициент V редукции частоты, обеспечивающий необходимую кратность снижения частоты Одновременно с этим блоком 10

устанавливается требуемый уровень на- 0 водит к переключению компаратора 801

пряжения UCD А, поступающий на вход задатчика 8, формирующего напряжение Иг задания пониженной частоты. В исходном состоянии интегратор 8.2 закорочен, , выходной сигнал компара- ,«. тора 8.1 (что соответственно положительному уровню +Е), (. При пуске электропривода интегратор 8.2 начинает формировать по линейному закону с темпом, определяемым уровнем напряжения Е, напряжение Un, делитель 9 частоты при этом отключен, В соответствии с заданным законом изменения TJr на выходе блока 7 синхронизируемого преобразователя напряжение - частота формируется последовательность импульсов частоты 6-f2, которая преобразуется блоком кольцевого распределителя 5 в напряжения

из исходного начального состояния , а также к изменению (увеличению или уменьшению) напряжения интегратора 8.2 по линейному закону в зависимости от соотношения U, Цр или U/,i U г. до наступления равенства

r / i

напряжений Uw -Up, при котором ком паратор 8.1 переключается в исходное . состояние и на входе задатчика 8

IQ изменяется сигнал с Q на IQ 1 разрешающий счет делителю частоты 9, и в зависимости от сигнала на его втором входе устанавливается требуемое значение частоты Ј%.

45 Способ регулирования частоты вращения асинхронного электропривода . осуществляется следующим образом (фиг.3-5).

На диаграммах обозначено: U«

управления U ,11Я,

uk ufc uc,uc частотой f, В соответствии с выходным напряжением интегратора 7,1 и сигналами U f. и U блоком 6 формируется последовательность импульсов С(оО

вается линейный закон изменения частоты выходного напряжения в соответствии с напряжением U. При достижении последним заданного уровня U Uw компаратор 8.1 переключается в состояние , , а выходное напряжение интегратора сохраняется на уровне U, . , Сигнал 101 раэреша laf,

ет работу делителю ч, с выхода которого импульсы частотой 6 поступают на вход элемента 2ИЛИ 7.4 и независимо от уровня выходного напряжения интегратора 7а1 закорачивают последний, осуществляя корректировку значения частоты выходного напряжения г в соответствии с заданным коэффициентом редукции частоты . Это необходимо для того, чтобы компенси- 0 ровать возможное несоответствие зна

чения U г заданному значению

f, -f t /V

и изменения частоты сети f, , а также нестабильность параметров схемы блока 7о При изменении cJ3e. и, следова- тельно, Uw , например, при переходе с одной частоты на другую возникает несоответствие прежнего значения

напряжения Up задатчика 8 и нового i

значения U на его входе. Это приводит к переключению компаратора 801

«.

из исходного начального состояния , а также к изменению (увеличению или уменьшению) напряжения интегратора 8.2 по линейному закону в зависимости от соотношения U, Цр или U/,i U г. до наступления равенства

r / i

напряжений Uw -Up, при котором компаратор 8.1 переключается в исходное . состояние и на входе задатчика 8

Q изменяется сигнал с Q на IQ 1 разрешающий счет делителю частоты 9, и в зависимости от сигнала на его втором входе устанавливается требуемое значение частоты Ј%.

5 Способ регулирования частоты вращения асинхронного электропривода . осуществляется следующим образом (фиг.3-5).

На диаграммах обозначено: U«

0 тактовый логический сигнал для фазы а компаратора; 11д - мгновенное значение напряжения фазы А сети, U - мгновенное значение выходного напряжения фазы а коммутатора; 17 - мгно

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

| Асинхронный электропривод | 1986 |

|

SU1339864A1 |

| ГЕНЕРАТОР СИГНАЛОВ СЛОЖНОЙ ФОРМЫ | 1991 |

|

RU2019908C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДЕБАЛАНСНЫМ ВИБРОВОЗБУДИТЕЛЕМ | 2015 |

|

RU2579456C1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| Электропривод переменного тока | 1987 |

|

SU1517109A1 |

| Устройство для широтно-импульсного управления тиристорным преобразователем частоты | 1987 |

|

SU1554093A1 |

| Способ ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором | 1986 |

|

SU1517107A1 |

| Устройство для управления трехфазно-трехфазным однополупериодным циклоконвертором | 1983 |

|

SU1169111A1 |

| Вентильный двигатель | 1988 |

|

SU1594658A1 |

Изобретение относится к электротехнике. Целью изобретения является улучшение энергетических показателей. С этой целью в способе регулирования частоты вращения асинхронного электропривода формируют три последовательности взаимоинверсных модулирующих импульсов для управления коммутатором 2, к которому подключен асинхронный двигатель 1, при этом каждая пара модулирующих напряжений сдвинута на 1/3 периода частоты F2, которая по отношению к частоте питания выбирается из следующего ряда F2 / F1 = 3/7

5/9

3/5

5/7

7/9, а фронт импульса модулирующего напряжения совпадает с передним фронтом исходного синхронизирующего напряжения. Устройство содержит формирователь синхронизирующих импульсов 11, задатчик частоты 8, блок преобразования напряжения в частоту 7, кольцевой распределитель импульсов 5, блок формирования модулирующего напряжения 4, формирователь и распределитель импульсов 3. Положительный эффект достигается за счет исключения постоянной составляющей и ослабления субгармонических составляющих тока. 5 ил.

которые поступают в блок 4 формирова-55 венное значение выходного напряжения

ния модулирующих напряжений, с выхо-фазы a KOMMytaTopa при искусственда которого снимаются модулирующиеной коммутации тиристоров; At,,, /3t5,

напряжения UMq ,,U Муимь иМс и мо6, - интервалы времени; Т - период

(частоты f2). Этим самым обеспечи-тактового логического сигнала; Тппериод повторяемости выходного напря- ния коммутатора.

Рассмотрим теоретическое обоснование данного способа регулирования. Для получения трехфазной системы напряжений, подведенных к обмоткам статора двигателя с частотой f , необходимо сформировать модулирующее напряжение с частотой f -2, которое обеспе- чивает циклическое подключение обмоток двигателя посредством тиристоров коммутатора к фазам сети с соответствующим временным сдвигом. При полной управляемости тиристоров (при искусственной коммутации) в выходном .напряжении фазы коммутатора U (фиг,36) отсутствуют постоянная и субгармонические (с частотой ниже частоты основной гармоники о/2) сое- тавляющие. Поскольку двигатель представляет собой фильтр высших частот, то момент в этом случае будет в основном определяться основной гармоникой W2o В реальном случае при есте- ственноп коммутации в выходном напряжении появляются участки напряжения сети не соответствующие модулирующему Uc (wt) (фиг.Зв). Это обуславливает постоянную и субгармонические сое- тавляющие в выходном напряжении коммутатора и соответствующее ухудшение энергетических показателей работы двигателя. При соотношении частот f1 и f 1 в виде правильной рациональ- ной дроби f-j/f x/y (x,y - целые числа) выходное напряжение коммутатора представляет собой периодическую функцию с периодом повторяемости При нечетных значениях X и у напряжение U7(w2t) описывается нечетной функцией и не содержит постоянной составляющей . Таким образом, выбор кратности частоты выходного напряжения Ј к частоте на- пряжения сети Ј, в виде х/у, где х,у - нечетные числа, т.е. ,

{3/7, 5/9, 3/5, 5/7, 7/9 (5),

позволяет исключить постоянную составляющую в выходном напряжении.

Подавление субгармонических составляющих в выходном напряжении дос-г тигается при исключении из кривой выходного напряжения участки Uc(Wt), не включая тиристоры (фиг,За), на соответствующих временных интервалах, а значение субгармонической в

данном случае определяется напряжением U(wt) (фиг.Зд).

Для подавления субгармонической и постоянной составляющих, как следует из фигвЗ, необходимо, чтобы . При этом длительность Ј зоны, где достигается эффективное подавление субгармонических составляющих, определяется из условия (фиг„4)

(О

, cosof-K , Ъ ; (arccos -я)-с/.

Q 5 0 5 0 5

0

5

Исключение работы тиристоров на участке С достигается тем, что модулирующее напряжение на этом участке устанавливается равным нулю (фиг.5), Длительность с интервала модулирующего напряжения (фиг„5) определяется соотношением

е } Y- -arccos ()-. (2)

Для получения тактовых импульсов Ј(00 использован принцип вертикального управления, когда линейно нарастающее напряжение с выхода интегратора 7.1 блока 7 (с периодом повторяемости Т ,j/6), фронт спада которого поочередно совпадает с задними фронтами сигналов Uy-Uc, сравнивают с опорным напряжением Uon, При пилообразном опорном напряжении системы им- пульсно-фазового управления (блок 3) регулировочная характеристика последней имеет вид

d o(Mntf-KU.

При аппроксимации зависимости

€4(агссовЈ2ЈСЈЛ)-ч.

Ј

из условия 2(оО -с в виде Ј(756- -0,5сО значение 1ГОП можно определить из условия

Uoi

Uc,Kc-UЈP u;

Ј макс где U-. - напряжение задания частоты

выходного напряжения (с выхода блока 8);

Ufwc,

иЈг Р амплитуда выходного напряжения интегратора 7.1; Up - предельная частота выходного

напряжения;

(1 - коэффициент пропорциональности

Формирование модулирующих напряжений поясняется фиг,5 и осуществляется следующим образом. Из последовательности- импульсов Ј(оО с выхода блока 6 выделяют соответствующий данному сигналу U0(,U0(,Ut,Ufa,Uc,Uc тактовый импульс, сравнивают уровни тактового логического сигнала и соответствующего ему тактового импульса, при несовпадении формируют соответствующее модулирующее напряжение.

Предлагаемое изобретение позволяет исключить постоянную составляющую выходного напряжения при работе на фиксированных рабочих частотах при существенном ослаблении субгармонических и постоянной составляющих на рабочих и любых промежуточных частотах, что приводит к улучшению энергетических показателей и регулировоч- ных характеристик электропривода, а также уменьшению пульсаций момента и частоты вращения за счет подавления переходных составляющих момента АД,

Формула изобретения

ния -arccos( )-d, и осуществляют указанное включение тиристоров с фазой включения на сформированных интервалах модулирующего на- пряжения.

2, Устройство для регулирования частоты вращения асинхронного электропривода, содержащее коммутатор,

составленный из встречно-параллельно соединенных тиристоров для подключения двигателя к сети, блок формирования и распределения импульсов управления тиристорами коммутатора, снабженный входами синхронизации для соединения с тремя фазами сети, первый управляющий вход которого предназначен для задания амплитуды выходного напряжения, а выходы соединены с управляющими электродами соответствующих тиристоров коммутатора, кольцевой распределитель с тремя прямыми и тремя инверсными выходами, формирователь-синхронизатор с входам для соединения с тремя фазами сети, целочисленный делитель частоты, первый вход которого соединен с выходом формирователя-синхронизатора, блок задания скорости и коэффициента редукции частоты, задатчик напряжения пониже,нной частоты, вход которого соединен с первым выходом блока задания скорости и -коэффициента редукции частоты, второй выход которого соединен с вторым входом целочисленного делителя частоты, третий вход которого соединен с вторым выходом упомянутого задатчика, о т л и ч а го- щ е е с я тем, что, с целью улучшения энергетических показателей, оно снабжено блоком формирования модулирующих напряжений, блоком формирования тактовых импульсов, блоком синхронизируемого преобразователя напря- жение - частота, первый вход которого соединен с первым выходом задатчика напряжения пониженной частоты, а второй вход соединен с выходом целочисленного делителя, частоты, первый выход блока синхронизируемого преобразователя напряжение - частота соединен с входом кольцевого распределителя, а второй - с первым входом блока формирования тактовых импульсов, второй вход которого соединен с первым входом блока формирования и распределения импульсов управления тиристорами, третий вход блока формирования тактовых импульсов соединен с первым выходом указанного эадатчика, а выход соединен с первым входом блока формирования модулирующих напряжений, второй, четвертый, шестой и третий, пятый, седьмой входы которого соединены соответственно с первым, вторым, третьим прямыми и первым, вторым, третьим инверсными

выходами кольцевого распределителя,ветственно с первым, вторым, третьим,

второй, третий, четвертый, пятый,четвертым, пятым, шестым выходами блошестой, седьмой входы блока формиро-ка формирования модулирующих напряжевания и распределения импульсов уп-,- ний„ равления тиристорами соединены соотФиг. Z

r о

f ш

1Л

Фиг. 5

| Способ управления трехфазно-трехфазным циклоконвертором и устройство для его осуществления | 1978 |

|

SU720662A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-03-30—Публикация

1987-06-10—Подача