Изобретение относится к вычислительной технике и может быть использовано в измерительных устройствах с аппаратурной линеаризацией функции преобразования,

Целью изобретения является повышение быстродействия.

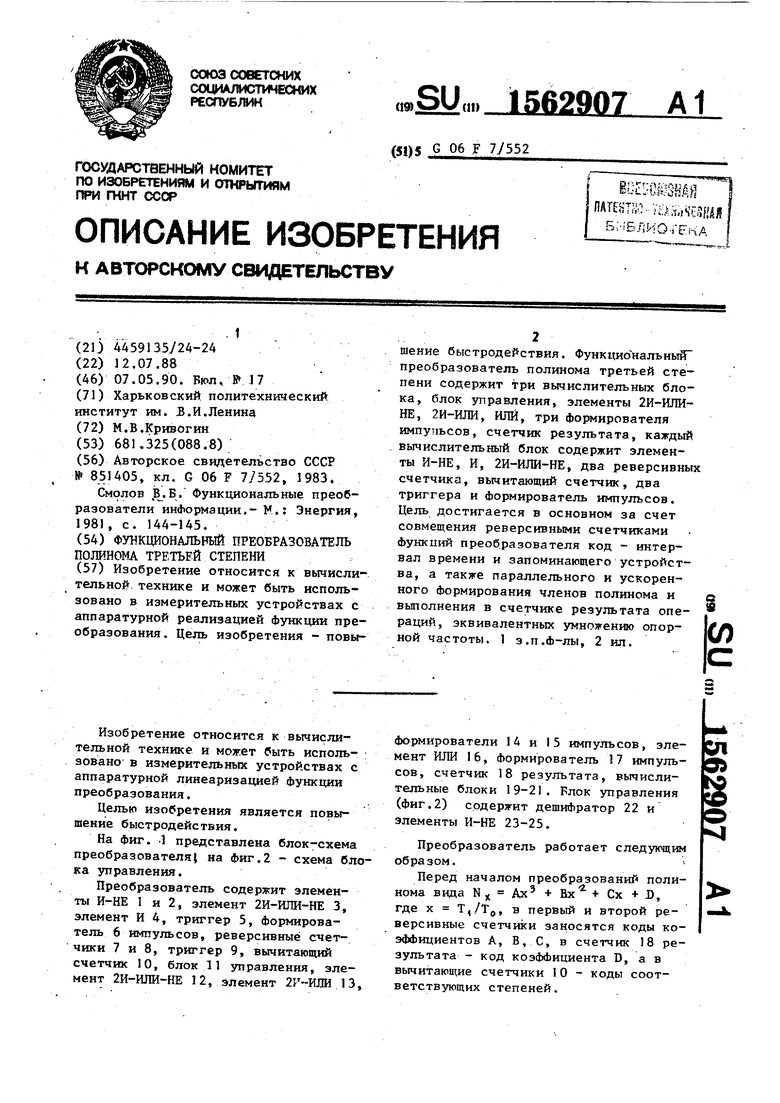

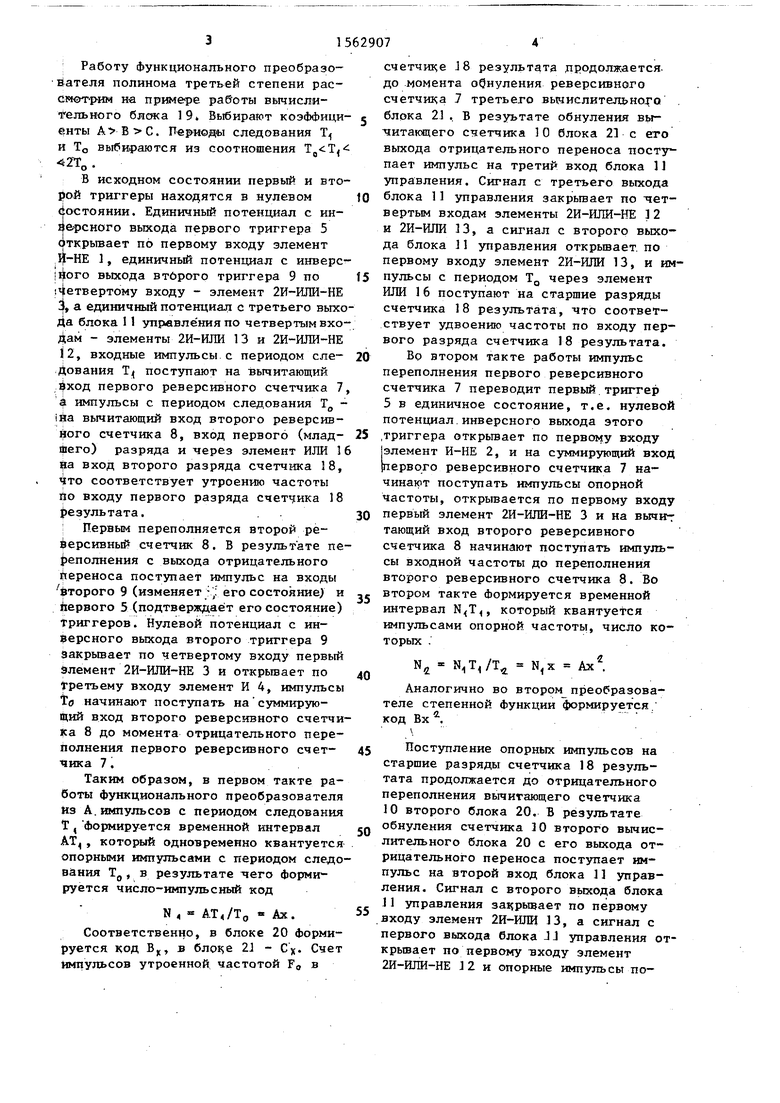

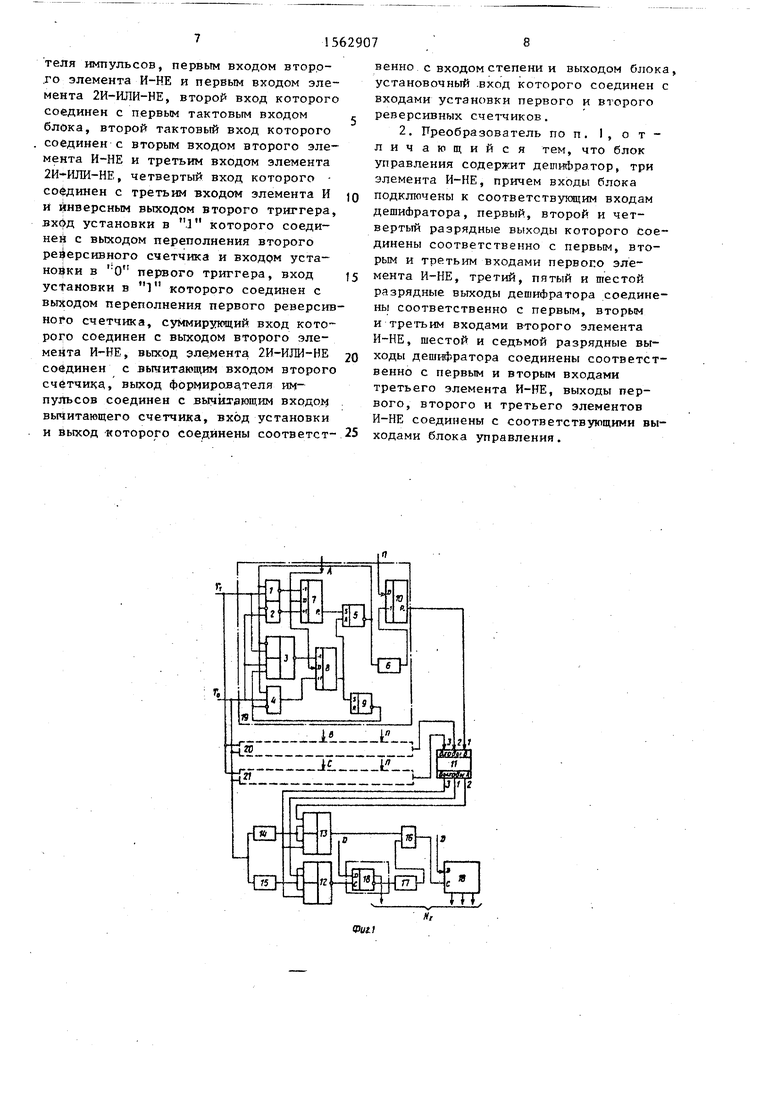

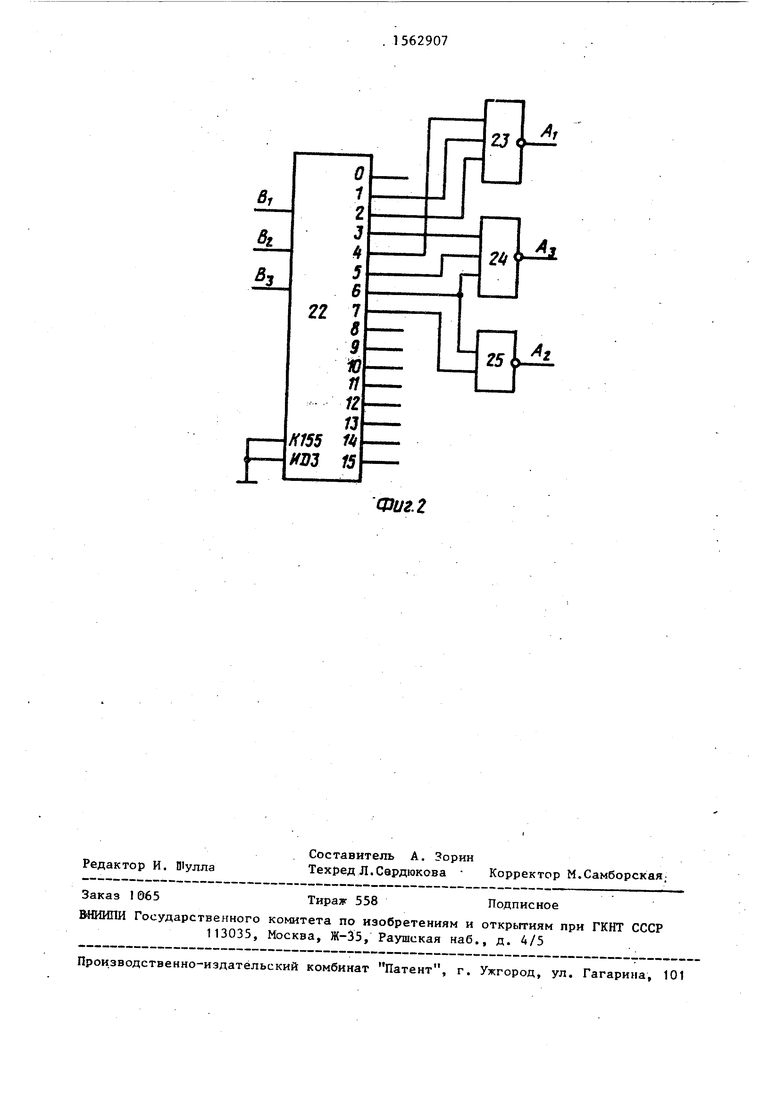

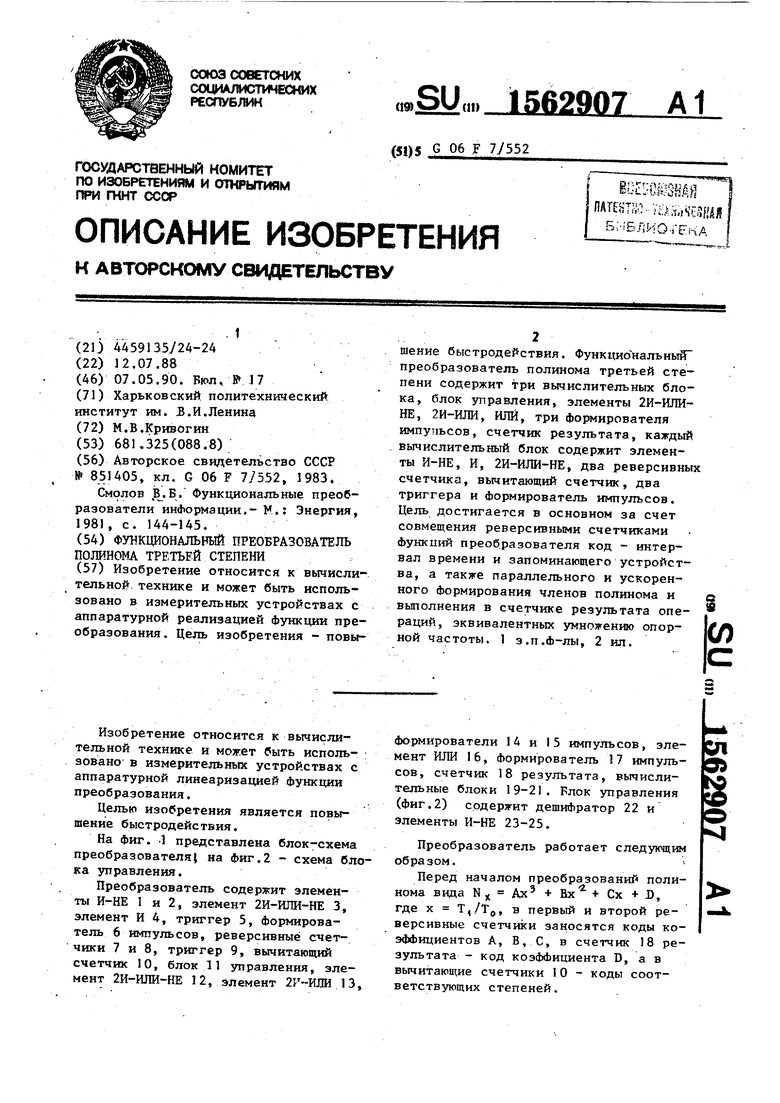

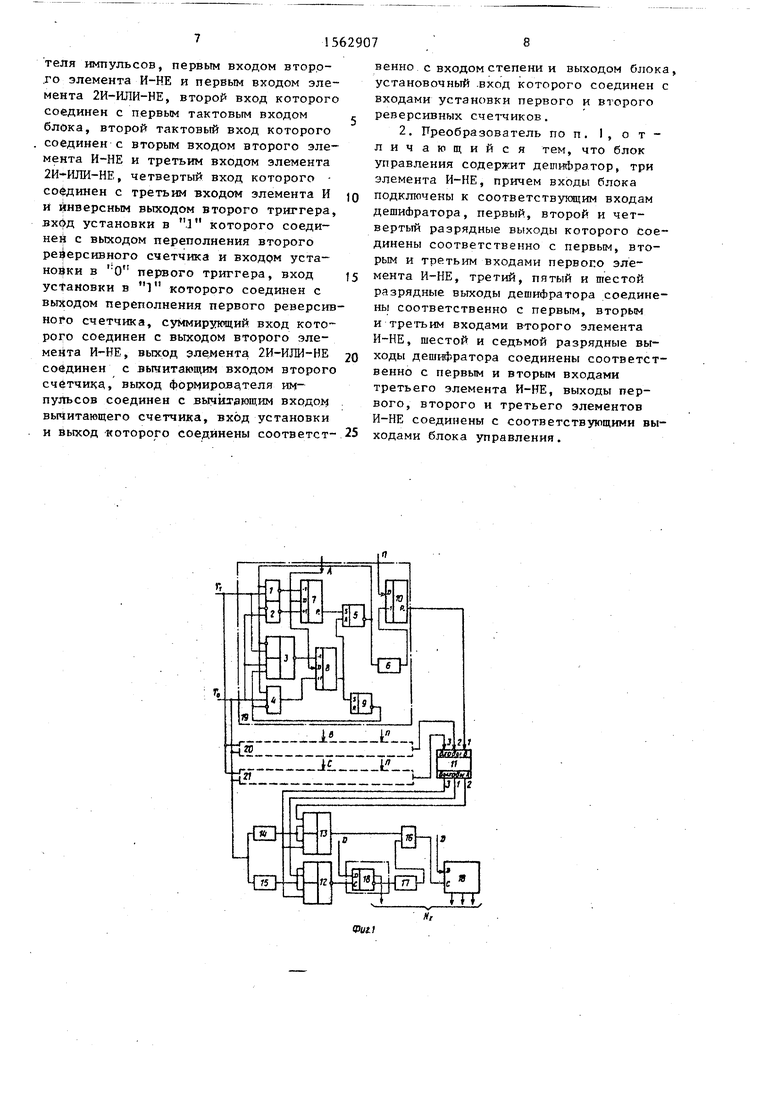

На фиг. -1 представлена блок-схема преобразователяI на фиг.2 - схема блока управления.

Преобразователь содержит элементы И-НЕ 1 и 2, элемент 2И-ИЛИ-НЕ 3, элемент И 4, триггер 5, формирователь 6 импульсов, реверсивные счетчики 7 и 8, триггер 9, вычитающий счетчик 10, блок 11 управления, элемент 2Й-ИЛИ-НЕ 12, элемент 2Г--ИЛИ 13,

формирователи 14 и 15 импульсов, элемент ИЛИ 16, формирователь 17 импульсов, счетчик 18 результата, вычислительные блоки 19-21. Рлок управления (Фиг.2) содержит дешифратор 22 и элементы И-НЕ 23-25.

Преобразователь работает следующим образом.

Перед началом преобразований полинома вида Nx Ах3 + Вх + Сх + Б, где х Т,/Т0, в первый и второй реверсивные счетчики заносятся коды коэффициентов А, В, С, в счетчик 18 результата - код коэффициента D, а в вычитающие счетчики 10 - коды соответствующих степеней.

Работу функционального преобразователя полинома третьей степени рассмотрим на примере работы вычислительного блока 19 Выбирают коэффици- енты А . Периода следования Т и Т0 выбираются из соотношения tZT0.

В исходном состоянии первый и второй триггеры находятся в нулевом состоянии. Единичный потенциал с инверсного выхода первого триггера 5 дткрывает по первому входу элемент Й-НЕ 1, единичный потенциал с инверс- ного выхода втброго триггера 9 по Четвертому входу - элемент 2И-ИЛИ-НЕ 3, а единичный потенциал с третьего выхода блока 1 1 упрдвле ния по четвертым входам - элементы 2И-ИЛИ 13 и 2И-ИЛЙ-НЕ 12, входные импульсы с периодом еле- дования Т поступают на вычитающий йход первого реверсивного счетчика 7, а импульсы с периодом следования Т0 - iHa вычитающий вход второго реверсивного счетчика 8, вход первого (млад- Шего) разряда и через элемент ИЛИ 16 на вход второго разряда счетчика 18, что соответствует утроению частоты по входу первого разряда счетчика 18 результата.

Первым переполняется второй реверсивный счетчик 8. В результате переполнения с выхода отрицательного переноса поступает импульс на входы второго 9(изменяет;, его состояние) и Первого 5(подтверждает его состояние) триггеров. Нулевой потенциал с инверсного выхода второго триггера 9 Закрывает по четвертому входу первый элемент 2И-ИЛИ-НЕ 3 и открывает по Третьему входу элемент И 4, импульсы То начинают поступать на суммирующий вход второго реверсивного счетчика 8 до момента отрицательного переполнения первого реверсивного счет- пика 7.

Таким образом, в первом такте работы функционального преобразователя из А.импульсов с периодом следования Т , Формируется временной интервал

АТ, который одновременно квантуется опорными импульсами с периодом следования Т0 , в результате чего формируется число-импульсный код

N« - АТ,/Т0 - Ах. Соответственно, в блоке 20 формируется код Вх, в блоке 21 - Сх. Счет импульсов утроенной частотой F0 в

0 5 0

. 0 5

0

5

счетчике J8 результата дродолжается до момента обнуления реверсивного счетчика 7 третьего вычислительного блока 21. В резуьтате обнуления вычитающего счетчика 10 блока 23 с его выхода отрицательного переноса поступает импульс на третий вход блока 11 управления. Сигнал с третьего выхода блока 11 управления закрывает по четвертым входам элементы 2И-ИЛИ-НЕ 12 и 2И-ИЛИ 13, а сигнал с второго выхода блока 11 управления открывает по первому входу элемент 2И-ЙЛИ 13, и импульсы с периодом Т0 через элемент ИЛИ 16 поступают на старшие разряды счетчика 18 результата, что соответствует удвоению частоты по входу первого разряда счетчика 18 результата.

Во втором такте работы импульс переполнения первого реверсивного счетчика 7 переводит первый триггер 5 в единичное состояние, т.е. нулевой потенциал инверсного выхода этого .триггера открывает по первому входу (элемент И-НЕ 2, и на суммирующий вход первого реверсивного счетчика 7 начинают поступать импульсы опорной частоты, открывается по первому входу первый элемент 2И-ИЛИ-НЕ 3 и на вычитающий вход второго реверсивного счетчика 8 начинают поступать импульсы входной частоты до переполнения второго реверсивного счетчика 8. Во втором такте Формируется временной интервал , который квантуется импульсами опорной частоты, число которых .

N4 N,x Ах2.

Аналогично во втором преобразователе степенной Функции формируется

код Вх.

Поступление опорных импульсов на старшие разряды счетчика 18 результата продолжается до отрицательного переполнения вычитающего счетчика

10второго блока 20. В результате обнуления счетчика 0 второго вычислительного блока 20 с его выхода отрицательного переноса поступает импульс на второй вход блока 11 управления. Сигнал с второго выхода блока

11управления закрывает по первому входу элемент 2И-ГОШ 13, а сигнал с первого выхода блока JJ управления открывает по первому -входу элемент 2И-ИЛИ-НЕ 12 и опорные импульсы по10

ступают на вуод первого разряда счетчика 18 результата. Поступление импульсов на вход первого разряда счетчика 18 результата продолжается до момента переполнения вычитающего счетчика 10 первого блока 19.

В третьем такте работы импульс переполнения второго реверсивного счетчика 8 поступает на вход первого триггера 5 и единичный потенциал с его инверсного выхода открывает по первому входу первый элемент И-НЕ 1, нулевой потенциал на выходе второго триггера 9 открывает по третьему входу элемент И 4.

Таким образом, на вычитающий вход первого реверсивного счетчика 7 поступают импульсы входной частоты, на суммирующий вход второго реверсивного счетчика 8 - импульсы опорной частоты до переполнения первого реверсивного счетчика 7. Импульс отрицательного переполнения проходит через первый Формирователь на вычитающий вход вычитающего счетчика 10 и на его выходе появляется импульс отрицательного переполнения, поступающий на первый вход блока 11 управления.

При этом первый вычислительный30

блок 19 Фиксирует число импульсов з

торого соединен с первым тактовым входом первого вычислительного блока, второй тактовый вход которого соединен с вторым входом элемента И, о т- личающийся тем, что, с целью повышения быстродействия, в него введены второй и третий вычислитель ные блоки, с первого по третий фор15

20

N3 Ах

В счетчике 18 результата Фиксируется число импульсов, равное Ах + Вх + +Сх + D. В моменты окончания работы соответствующих вычислительных блоков блок 1 1 управления выдает команду запрета на их работу, например на R-входы реверсивных счетчиков ны) .

Формула изобретения

1. Функциональный преобразователь полинома третьей степени, содержащий первый вычислительный блок и блок управления, причем вход первой тактовой последовательности преобразователя

мирователи импульсов,,элемент 2И-ИЛИ- НЕ и элемент 2И-ИЛИ, элемент ИЛИ к счетчик результата, причем выходы с первого по третий вычислительных блоков соединены с входами соответственно признаков переполнения с первого по третий блока управления, вход первой тактовой последовательности преобразователя соединен с первыми тактовыми входами второго и третьего вычислительных блоков, вторые тактовые входы которых соединены с входом второй тактовой последовательности преобразователя и входами первого и второго Формирователей импульсов, пер25 вый и второй выходы блока управления соединены с первыми входами соответственно элементов 2И-ИЛИ и 2И-ИЛИ-НЕ, вторые и третьи входы которых соединены с выходами соответственно первого и второго Формирователей импульсов, третий выход блока управления соединен с четвертыми входами элементов 2И-ИЛИ и 2И-ИЛИ-НЕ, выходы которых соединены соответственно с первым входом элемента ИЛИ и счетным входом первого разряда счетчика результата, инверсный выход которого соединен с входом третьего формирователя, выход которого соединен с вторым входом эле7 и 8 (не показа- 40 мента ИЛИ, выход которого соединен со

счетным входом второго разряда счетчика результата, входы с третьего по нулевой коэффициентов полинома преобразователей соединены с установочными

45 входами соответственно первого, второго, третьего вычислительных блоков и счетчика результата, выход которого соединен с выходом преобразователя, входы кодов с третьей по первую сте35

торого соединен с первым тактовым входом первого вычислительного блока, второй тактовый вход которого соединен с вторым входом элемента И, о т- личающийся тем, что, с целью повышения быстродействия, в него введены второй и третий вычислитель ные блоки, с первого по третий фор10

15

20

25

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения символов на экране электронно-лучевой трубки | 1991 |

|

SU1800475A1 |

| Устройство для управления вентильным преобразователем | 1990 |

|

SU1753561A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для управления электродвигателем постоянного тока | 1987 |

|

SU1608776A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Устройство для контроля двух импульсных последовательностей | 1988 |

|

SU1569834A1 |

| Устройство для сортировки двоичных чисел | 1984 |

|

SU1182509A1 |

| ГЕНЕРАТОР ФУНКЦИЙ УОЛША | 1996 |

|

RU2115951C1 |

| Устройство для сравнения чисел | 1979 |

|

SU938280A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительных устройствах с аппаратурной реализацией функции преобразования. Цель изобретения - повышение быстродействия. Функциональный преобразователь полинома третьей степени содержит три вычислительных блока, блок управления, элементы 2 И-ИЛИ-НЕ, 2 И-ИЛИ, ИЛИ, три формирователя импульсов, счетчик результата, каждый вычислительный блок содержит элементы И-НЕ, И, 2И-ИЛИ-НЕ, два реверсивных счетчика, вычитающий счетчик, два триггера и формирователь импульсов. Цель достигается в основном за счет совмещения реверсивными счетчиками функций преобразователя код-интервал времени и запоминающего устройства, а также параллельного и ускоренного формирования членов полинома и выполнения в счетчике результата операций, эквивалентных умножению опорной частоты. 1 з.п. ф-лы, 2 ил.

соединен с первым тактовым входом пер-50 пеней преобразователя соединены с

вого вычислительного блока, второй тактовый вход которого соединен с входом второй тактовой последовательности преобразователя, первый вычисливходами степени соответственно с первого по третий вычислительных блоков, причем в каждый вычислительный блок введены второй элемент П-НЕ, элемент

тельный блок содержит элемент И, пер- 55 2И-ИЛИ-НЕ, первый и второй триггеры, вый элемент И-HF, первый и второй ре- Формирователь импульсов и вычитающий

счетчик, первый вход первого элемента И-НЕ соединен с инверсным выходом

версивные счетчики, первый вход элемента И соединен с первым входом первого элемента И-НЕ, второй вход копервого триггера, входом формировавходами степени соответственно с первого по третий вычислительных блоков, причем в каждый вычислительный блок введены второй элемент П-НЕ, элемент

первого триггера, входом формирователя импульсов, первым входом второго элемента И-НЕ и первым входом элемента 2И-ИЛИ-НЕ, второй вход которого соединен с первым тактовым входом блока, второй тактовый вход которого соединен с вторым входом второго элемента И-НЕ и третьим входом элемента 2И ИЛИ-НЕ, четвертый вход которого - соединен с третьим входом элемента И и инверсным выходом второго триггера, вход установки в 3 которого соединен с выходом переполнения второго реверсивного счетчика и входом установки в 0 первого триггера, вход yctaHOBKH в 1 которого соединен с выходом переполнения первого реверсивного счетчика, суммирующий вход кото рого соединен с выходом второго элемента И-НЕ, выход элемента 2И-ИЛИ-НЕ соединен с вычитающим входом второго счетчика,, выход формирователя импульсов соединен с вычитающим входом вычитающего счетчика, вход установки и выход которого соединены соответственно с входом степени и выходом блока, установочный вход которого соединен с входами установки первого и второго

, реверсивных счетчиков.

Ю подключены к соответствующим входам дешифратора, первый, второй и четвертый разрядные выходы которого соединены соответственно с первым, вторым и тпетьим входами первого эле15 мента И-НЕ, третий, пятый и тестой разрядные выходы дешифратора соединены соответственно с первым, вторым и третьим входами второго элемента И-НЕ, шестой и седьмой разрядные вы20 ходы дешифратора соединены соответственно с первым и вторым входами третьего элемента И-НЕ, выходы первого, второго и третьего элементов И-НЕ соединены с соответствующими вы25 ходами блока управления.

Фиг.2

| Устройство для воспроизведения квадратичныхпОлиНОМОВ | 1979 |

|

SU851405A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Смолов В.Б | |||

| Функциональные преобразователи информации.- V.: Энергия, 1981, с | |||

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-12—Подача