Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве элементов связи аналоговых объектов с ЭВМ,

Целью изобретения является повышение надежности и точности преобразователя перемещения в-код.

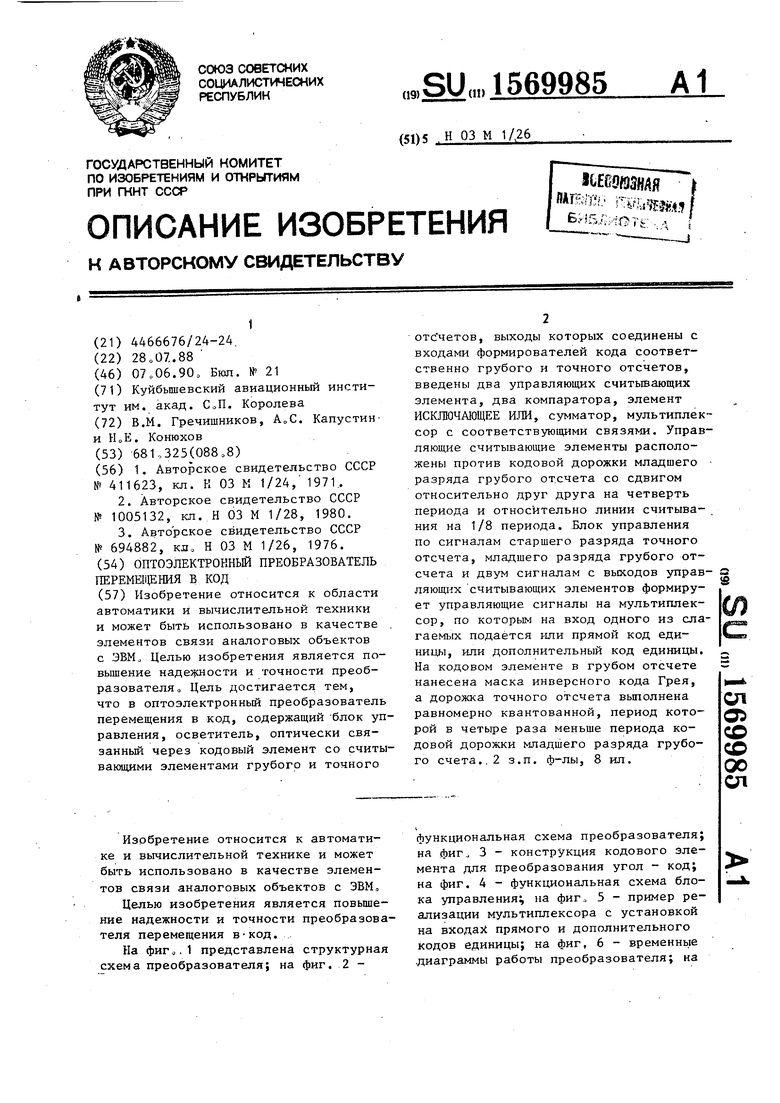

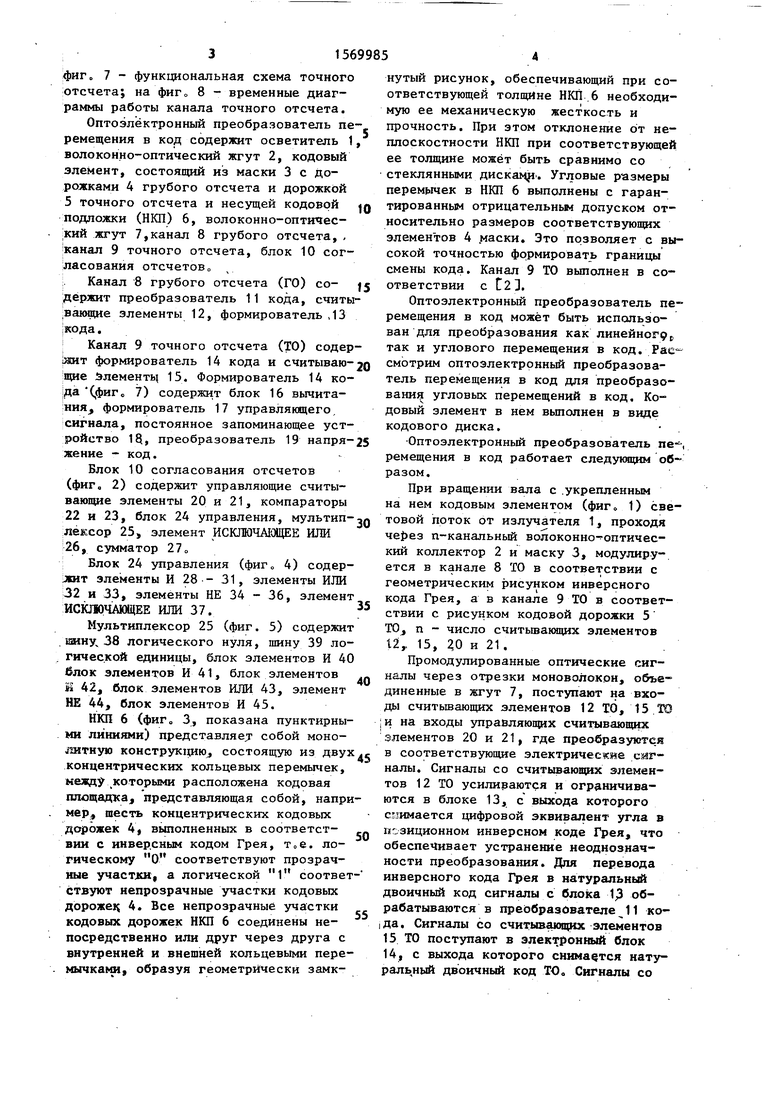

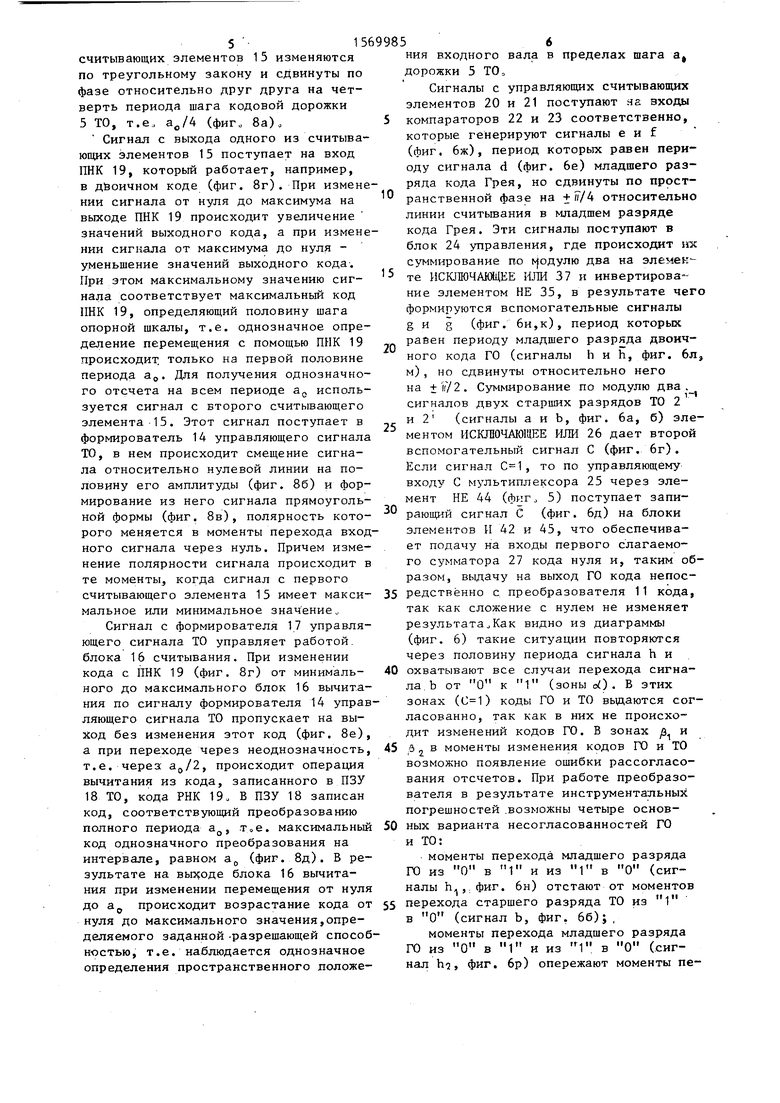

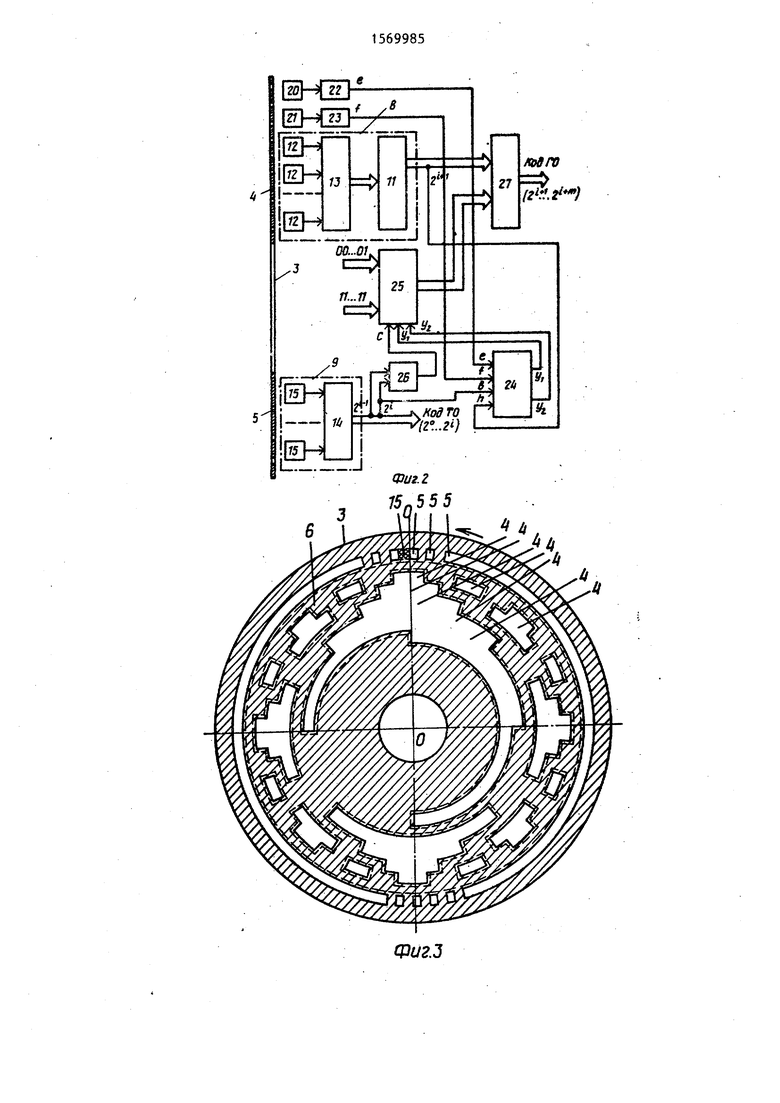

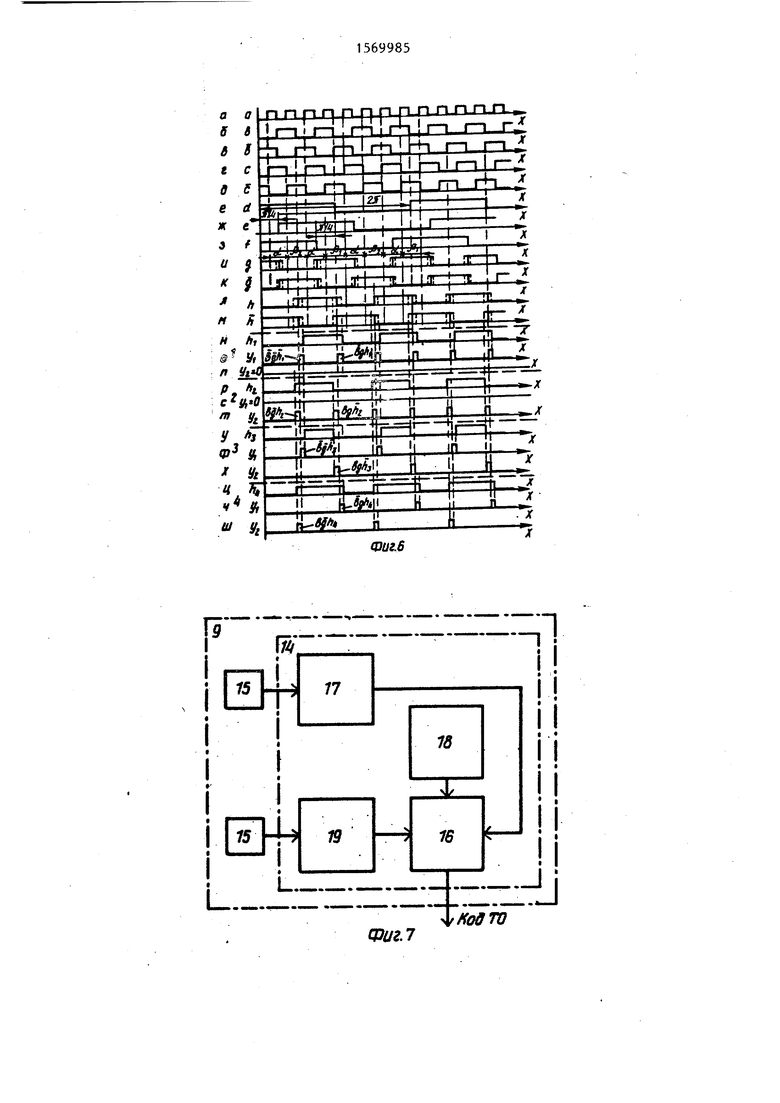

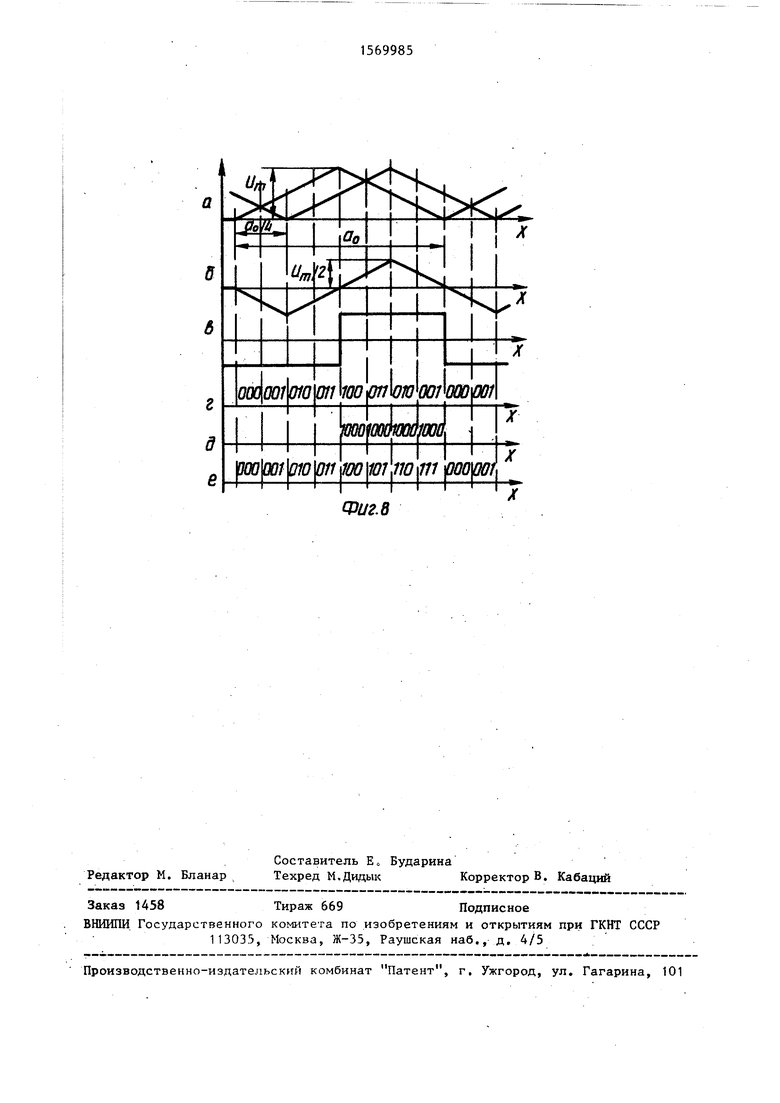

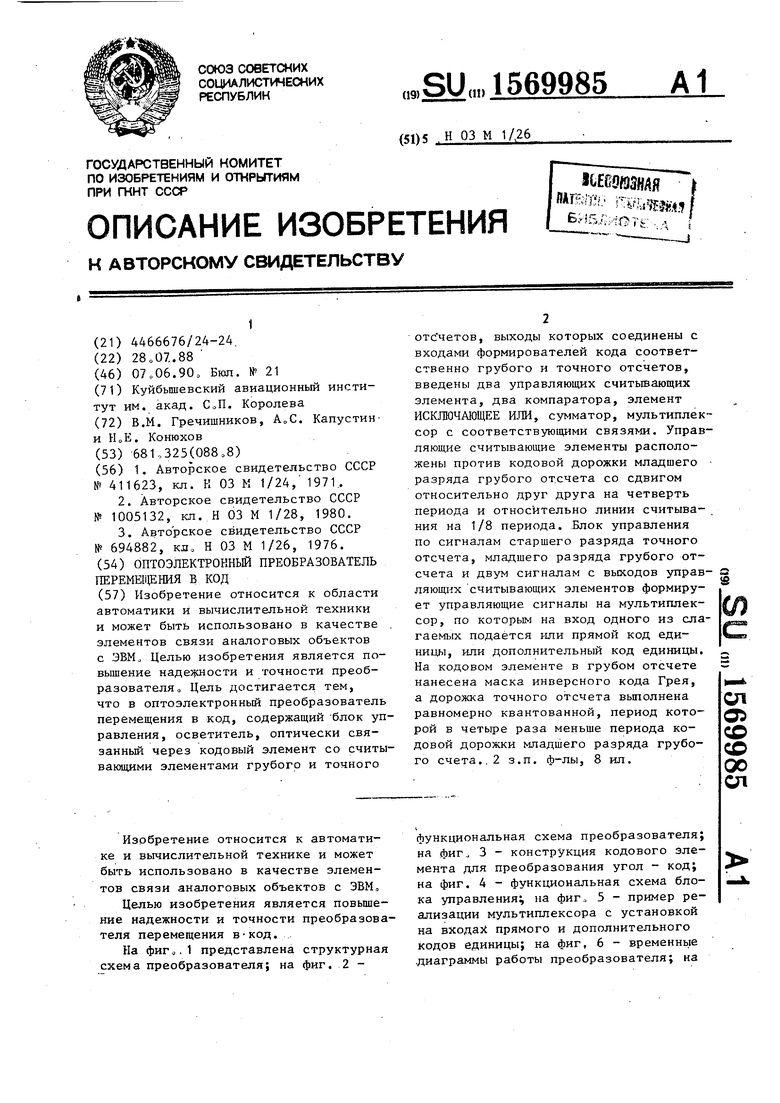

На фиг 1 представлена структурная схема преобразователя; на фиг. 2 функциональная схема преобразователя; на фиг о 3 - конструкция кодового элемента для преобразования угол - код; на фиг. 4 - функциональная схема блока управления на фиг, 5 - пример реализации мультиплексора с установкой на входах прямого и дополнительного кодов единицы; на фиг, 6 - временные диаграммы работы преобразователя; на

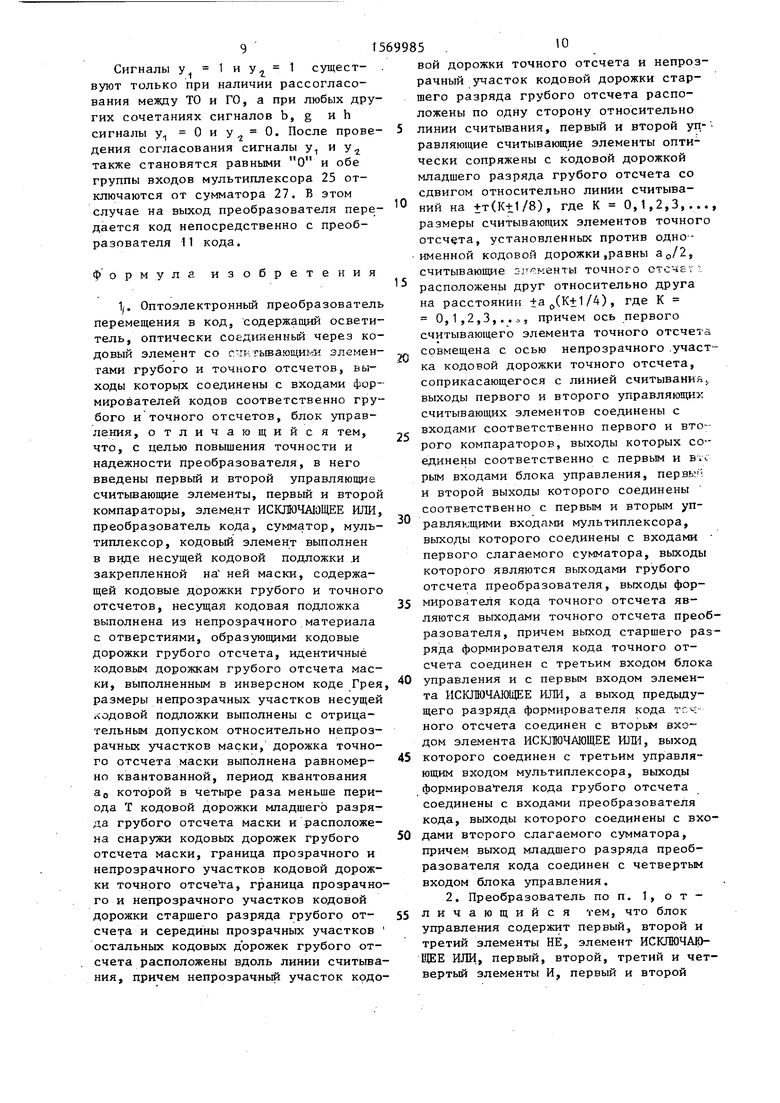

фиг о 7 - функциональная схема точного отсчета; на фиг 8 - временные диаграммы работы канала точного отсчета.

Оптоэлектронный преобразователь перемещения в код содержит осветитель 1, волоконно-оптический жгут 2, кодовый элемент, состоящий из маски 3 с дорожками 4 грубого отсчета и дорожкой 5 точного отсчета и несущей кодовой J подложки (НКП) 6, волоконно-оптический жгут 7,канал 8 грубого отсчета, , канал 9 точного отсчета, блок 10 согласования отсчетово

Канал 8 грубого отсчета (ГО) со- j держит преобразователь 11 кода, считывающие элементы 12, формирователь ,13 кода.

Канал 9 точного отсчета (ТО) содержит формирователь 14 кода и считываю- 2 щие Злементц 15. Формирователь 14 кода (фиг« 7) содержит блок 16 вычита- ния формирователь 17 управляющего сигнала, постоянное запоминающее устройство 18., преобразователь 19 напря-2 жение - код.

Блок 10 согласования отсчетов (фиг. 2) содержит управляющие считывающие элементы 20 и 21, компараторы 22 и 23, блок 24 управления, мультип-э лексор 25, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26, сумматор 27о

Блок 24 управления (фиг„ 4) содержит элементы И 28 - 31, элементы ИЛИ 32 и 33, элементы НЕ 34 - 36, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 37.3

Мультиплексор 25 (фиг. 5) содержит шину, 38 логического нуля, шину 39 логической единицы, блок элементов И 40 блок элементов И 41, блок элементов 4 К 42, блок элементов ИЛИ 43, элемент НЕ 44, блок элементов И 45.

НКП 6 (фиго 3, показана пунктирными линиями) представляем собой монолитную конструкцию состоящую из двух концентрических кольцевых перемычек, между которыми расположена кодовая площадка, представляющая собой, например, шесть концентрических кодовых дорожек 4, выполненных в соответст- вии с инверсным кодом Грея, . логическому О соответствуют прозрачные участки, а логической 1 соответствуют непрозрачные участки кодовых дороже 4. Все непрозрачные участки кодовых дорожек НКП 6 соединены непосредственно или друг через друга с внутренней и внешней кольцевыми перемычками, образуя геометрически замкнутый рисунок, обеспечивающий при соответствующей толщине НКП 6 необходимую ее механическую жесткость и прочность. При этом отклонение от неплоскостности НКП при соответствующей ее толщине может быть сравнимо со стеклянными дисками.. Угловые размеры перемычек в НКП 6 выполнены с гарантированным отрицательным допуском относительно размеров соответствующих элементов 4 маски. Это позволяет с высокой точностью формировать границы смены кода. Канал 9 ТО выполнен в соответствии с С2.

Оптоэлектронный преобразователь перемещения в код может быть использован для преобразования как линейног9Р так и углового перемещения в код. Рассмотрим Оптоэлектронный преобразователь перемещения в код для преобразован угловых перемещений в код. Кодовый элемент в нем выполнен в виде кодового диска.

Оптоэлектронный преобразователь пе ремещения в код работает следующим об разом.

При вращении вала с укрепленным на нем кодовым элементом (фиг 1) световой поток от излучателя 1, проходя через n-канальный волоконно-оптический коллектор 2 и маску 3, модулируется в канале 8 ТО в соответствии с геометрическим рисунком инверсного кода Грея, а в канале 9 ТО в соответствии с рисунком кодовой дорожки 5 TOj n - число считывающих элементов 12Г 15, 20 и 21.

Промодулированные оптические сигналы через отрезки моноволокон, объединенные в жгут 7, поступают на входы считывающих элементов 12 ТО, 15 ТО ,и на входы управляющих считывающих элементов 20 и 21, где преобразуются в соответствующие электрические сигналы. Сигналы со считывающих элементов 12 ТО усиливаются и ограничиваются в блоке 13, с выхода которого сминается цифровой эквивалент угла в позиционном инверсном коде Грея, что обеспечивает устранение неоднозначности преобразования. Для перевода инверсного кода Грея в натуральный двоичный код сигналы с блока 13 обрабатываются в преобразователе 11 ко- ,да. Сигналы со считывающих элементов 15 ТО поступают в электронный блок 14, с выхода которого снимается натуральный двоичный код ТОо Сигналы со

считывающих элементов 15 изменяются по треугольному закону и сдвинуты по фазе относительно друг друга на четверть периода шага кодовой дорожки 5 ТО, т.е., а0/4 (фиг0 8а) 0

Сигнал с выхода одного из считывающих элементов 15 поступает на вход ПНК 19, который работает, например, в двоичном коде (фиг. 8г). При изменении сигнала от нуля до максимума на выходе ПНК 19 происходит увеличение значений выходного кода, а при изменении сигнала от максимума до нуля - уменьшение значений выходного кода. При этом максимальному значению сигнала соответствует максимальный код ИНК 19, определяющий половину шага опорной шкалы, т.е. однозначное определение перемещения с помощью ПИК 19 происходит только на первой половине периода а„. Для получения однозначнопределах шага ад

10

ния входного вала в дорожки 5 TOD

Сигналы с управляющих считывающих элементов 20 и 21 поступают яа входы компараторов 22 и 23 соответственно, которые генерируют сигналы е и f (фиг. 6ж), период которых равен пери оду сигнала d (фиг. бе) младшего раз ряда кода Грея, но сдвинуты по прост ранственной фазе на +/Г/4 относительн линии считывания в младшем разряде кода Грея. Эти сигналы поступают в блок 24 управления, где происходит т суммирование по модулю два на элемек 15 те ИСКЛЮЧАЮЩЕЕ ИЛИ 37 и инвертирование элементом НЕ 35, в результате че формируются вспомогательные сигналы g и g (фиг. 6и,к), период которых равен периоду младшего разряда двоич ного кода ГО (сигналы h и h, фиг. 6 м), но сдвинуты относительно него

20

25

30

го отсчета на всем периоде а0 исполь- на +и/2. Суммирование по модулю два . зуется сигнал с второго считывающего элемента 15. Этот сигнал поступает в формирователь 14 управляющего сигнала ТО, в нем происходит смещение сигнала относительно нулевой линии на половину его амплитуды (фиг. 86) и формирование из него сигнала прямоугольной формы (фиг. 8в), полярность которого меняется в моменты перехода входного сигнала через нуль. Причем изменение полярности сигнала происходит в те моменты, когда сигнал с первого считывающего элемента 15 имеет максимальное или минимальное значение.

Сигнал с формирователя 17 управляющего сигнала ТО управляет работой блока 16 считывания. При изменении кода с ПНК 19 (фиг. 8г) от минимального до максимального блок 16 вычитания по сигналу формирователя 14 управляющего сигнала ТО пропускает на выход без изменения этот код (фиг. 8е), а при переходе через неоднозначность,

35

40

45

сигналов двух старших разрядов ТО 2 и 2 (сигналы а и Ь, фиг. 6а, б) эл ментом ИСКЛЮЧАЮЩЕЕ ИЛИ 26 дает второй вспомогательный сигнал С (фиг. 6г). Если сигнал , то по управляющему входу С мультиплексора 25 через элемент НЕ 44 (фиго 5) поступает запирающий сигнал С (фиг. 6д) на блоки элементов И 42 и 45, что обеспечивает подачу на входы первого слагаемого сумматора 27 кода нуля и, таким об разом, выдачу на выход ГО кода непосредственно с преобразователя 11 кода так как сложение с нулем не изменяет результата0Как видно из диаграммы (фиг. 6) такие ситуации повторяются через половину периода сигнала h и охватывают все случаи перехода сигнала Ъ от О к 1 (зоны еО . В этих зонах () коды ГО и ТО выдаются сог ласованно, так как в них не происходит изменений кодов ГО. В зонах и Ь г в моменты изменения кодов ГО и ТО возможно появление ошибки рассогласования отсчетов. При работе преобразователя в результате инструментальных погрешностей возможны четыре основных варианта несогласованностей ГО и ТО:

т.е. через а0/2, происходит операция вычитания из кода, записанного в ПЗУ 18 ТО, кода РНК 19, В ПЗУ 18 записан код, соответствующий преобразованию полного периода а0, т„е. максимальный 50 код однозначного преобразования на интервале, равном а0 (фиг. 8д). В результате на выходе блока 16 вычитания при изменении перемещения от нуля до а происходит возрастание кода от 55 перехода старшего разряда ТО из 1

сигналов двух старших разрядов ТО 2 и 2 (сигналы а и Ь, фиг. 6а, б) э ментом ИСКЛЮЧАЮЩЕЕ ИЛИ 26 дает втор вспомогательный сигнал С (фиг. 6г). Если сигнал , то по управляющему входу С мультиплексора 25 через эле мент НЕ 44 (фиго 5) поступает запи рающий сигнал С (фиг. 6д) на блоки элементов И 42 и 45, что обеспечива ет подачу на входы первого слагаемо го сумматора 27 кода нуля и, таким разом, выдачу на выход ГО кода непо редственно с преобразователя 11 код так как сложение с нулем не изменяе результата0Как видно из диаграммы (фиг. 6) такие ситуации повторяются через половину периода сигнала h и охватывают все случаи перехода сигн ла Ъ от О к 1 (зоны еО . В этих зонах () коды ГО и ТО выдаются с ласованно, так как в них не происхо дит изменений кодов ГО. В зонах Ь г в моменты изменения кодов ГО и Т возможно появление ошибки рассоглас вания отсчетов. При работе преобраз вателя в результате инструментальны погрешностей возможны четыре основных варианта несогласованностей ГО и ТО:

моменты перехода младшего разряд

ГО из О в 1 и из Г

в

О (сиг

налы h,, фиг. 6н) отстают от момент

1

нуля до максимального значения,определяемого заданной разрешающей способностью, т.е. наблюдается однозначное определения пространственного положепределах шага ад

ния входного вала в дорожки 5 TOD

Сигналы с управляющих считывающих элементов 20 и 21 поступают яа входы компараторов 22 и 23 соответственно, которые генерируют сигналы е и f (фиг. 6ж), период которых равен периоду сигнала d (фиг. бе) младшего разряда кода Грея, но сдвинуты по пространственной фазе на +/Г/4 относительно линии считывания в младшем разряде кода Грея. Эти сигналы поступают в блок 24 управления, где происходит тс суммирование по модулю два на элемек- 5 те ИСКЛЮЧАЮЩЕЕ ИЛИ 37 и инвертирование элементом НЕ 35, в результате чего формируются вспомогательные сигналы g и g (фиг. 6и,к), период которых равен периоду младшего разряда двоичного кода ГО (сигналы h и h, фиг. 6л, м), но сдвинуты относительно него

0

на +и/2. Суммирование по модулю два .

перехода старшего разряда ТО из 1

сигналов двух старших разрядов ТО 2 и 2 (сигналы а и Ь, фиг. 6а, б) элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 26 дает второй вспомогательный сигнал С (фиг. 6г). Если сигнал , то по управляющему входу С мультиплексора 25 через элемент НЕ 44 (фиго 5) поступает запирающий сигнал С (фиг. 6д) на блоки элементов И 42 и 45, что обеспечивает подачу на входы первого слагаемого сумматора 27 кода нуля и, таким образом, выдачу на выход ГО кода непосредственно с преобразователя 11 кода, так как сложение с нулем не изменяет результата0Как видно из диаграммы (фиг. 6) такие ситуации повторяются через половину периода сигнала h и охватывают все случаи перехода сигнала Ъ от О к 1 (зоны еО . В этих зонах () коды ГО и ТО выдаются согласованно, так как в них не происходит изменений кодов ГО. В зонах и Ь г в моменты изменения кодов ГО и ТО возможно появление ошибки рассогласования отсчетов. При работе преобразователя в результате инструментальных погрешностей возможны четыре основных варианта несогласованностей ГО и ТО:

моменты перехода младшего разряда

перехода старшего разряда ТО из 1

ГО из О в 1 и из Г

в

О (сигперехода старшего разряда ТО из 1

налы h,, фиг. 6н) отстают от моментов

1

в О (сигнал Ь, фиг. 66);,

моменты перехода младшего разряда ГО из О в 1 и из Т1 в О (сигнал , фиг. 6р) опережают моменты перехода старшего разряда ТО из 1 в

моменты перехода младшего разряда ГО из О в 1 отстают от моментов перехода сигнала b из 1 в О, а переходы младшего разряда ГО из в О

it «и

Ч1

опережают моменты перехода сигнала b из 1 в О (фиг. 6у);

моменты перехода младшего разряда ГО из О в 1 опережают моменты перехода сигнала b из 1 в О, а переводы младшего разряда ТО из 1 в О отстают от моментов перехода сигнала b из 1 в О (фиг. 6ц).

Все остальные комбинации несогла- сованностей являются частными случаями отмеченных вариантов,

При постоянном отстаивании моментов перехода старшего разряда ТО, в зонах Ь и /ij, должен формироваться сигнал, обеспечивающий прибавление недостающей единицы в разрядную сетку ГО. Этот сигнал формируется из вспомогательных сигналов Ъ, g, g, hlS h, (фиг. 4 и 6 в, и, к, лл м, н) по алгоритму: в зоне /ь1 .,, а в зоне

/згУ gh.,. Таким образом,общий управляющий сигнал у ,5 которьй обеспечивает при сигнале подачу прямого кода единицы ГО(00...01) с первой группы входов мультиплексора 25 на вход первого слагаемого сумматора 27 (фиг о 1), определяется логическим уравнением (фиг. 6о)

У, bgh1 + bgh,.

Сигнал управления у г при этом не формируется и равен О (фиг. 6п).

При полном опережении моментов перехода младшего разряда ГО из О в

тов перехода старшего разряда ТО из 1 в О должен происходить процесс

И

лишних единиц из кода ГО,

II 4 II

вычитания

что равносильно сложению 1 в дополнительном коде , (11...11) с кодом ГО. Этим процессом управляет сигнал у4, который формируется по алгоритму в J зоне fa , в зонерг (фиг. 4 и 6т) и общий управляющий сигнал определяется выражением

уг bgh4+ bghj.

Этот сигнал при управляющем сигнале обеспечивает подачу на вход сумматора 27 (фиг. 1) с второй группы входов мультиплексора 25 дополни0

5

0

25

тельного кода единицы ГО (11.011). Сигнал управления у, при этом не формируется и равен О (фиг. 6с).

Когда момент перехода сигнала Ь3 из О в 1 отстает от момента перехода сигнала, Ь из 1 в О, а момент перехода сигнала h, из 1 в Ч) опе1- реясает момент перехода сигнала b из 1 в О, должен формироваться управляющий сигнал (фиг. 6), обеспечивающий в зоне Ј, вычитание единицы, а в .зоне суммирование единицы с кодом ГО, Таким образом, при сигнале управления в зоне yJ1 формируется сигнал у Ј bgh3, обеспечивающий подачу на сумматор 27 дополнительного ко- да единицы (11... 11) с второй группы входов мультиплексора 25Х а в зоне /$ формируется сигнал у b-gh,, обеспеЪ

чивающий подачу на.сумматор 27 прямого кода единицы (00...01) с. первой группы входов мультиплексора 25. При этом общее выражение для управляющего сигнала (фиг. 6ф,х) принимает вид

U - у - b gh3.

0

0

5

5

5

Q Когда момент перехода Ьл из О

л

II л Н

происходит раньше перехода сигнала b из 1 в О, а момент перехо- 1 в О отстает от момента перехода сигнал b из 1 в О

да сигнала п. из

, должен формироваться управляющий сигнал, обеспечивающий в зоне /s, прибавление единицы к коду ГОЛ а в зоне |Ьг вычитание единицы из кода ГО. При сигнале управления (фиг. 6) в зоне /i( формируется сигнал у bgh+, который обеспечивает подключение к сумматору 27 (фиг. 1) прямого кода единицы (00...01) с первой группы входов мультиплексора 25, а в зоне ,%г формируется- сигнал , обеспечивающий подачу дополнительного ко да единицы (11,„ „ 11) на вход первого слагаемого сумматора 27 с второй группы входов мультиплексора 25S. Общее ш- ражение управляющего сигнала (фиг.6ч, ь) в этом случае принимает вид

Гу, bght; уг bghf.

Во всех случаях при формировании соответствующих управляющих сигналов у, и у,j происходит согласование точного и грубого отсчетов преобразова- теля.перемещения в код.

9 и у.

15

1 сущестСигналы у 1 вуют только при наличии рассогласования между ТО и ГО, а при любых других сочетаниях сигналов b, g и h сигналы у., 0иу.. После проведения согласования сигналы у1 и уг также становятся равными О и обе группы входов мультиплексора 25 отключаются от сумматора 27. В этом случае на выход преобразователя передается код непосредственно с преобразователя 11 кода.

Формула изобретения

. Оптоэлектронный преобразователь перемещения в код, содержащий осветитель, оптически соединенный через кодовый элемент со г п- ывающигли элементами грубого и точного отсчетов, выходы которых соединены с входами Формирователей кодов соответственно грубого и точного отсчетов, блок управления, отличающийся тем, что, с целью повышения точности и надежности преобразователя, в него введены первый и второй управляющие считывающие элементы, первый и второй компараторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь кода, сумматор, мультиплексор, кодовый элемент выполнен в виде несущей кодовой подложки и закрепленной на ней маски, содержащей кодовые дорожки грубого и точного отсчетов, несущая кодовая подложка выполнена из непрозрачного материала с отверстиями, образующими кодовые дорожки грубого отсчета, идентичные кодовым дорожкам грубого отсчета маски, выполненным в инверсном коде Грея, размеры непрозрачных участков несущей ладовой подложки выполнены с отрицательным допуском относительно непрозрачных участков маски, дорожка точного отсчета маски выполнена равномерно квантованной, период квантования а0 которой в четыре раза меньше периода Т кодовой дорожки младшего разряда грубого отсчета маски и расположена снаружи кодовых дорожек грубого отсчета маски, граница прозрачного и непрозрачного участков кодовой дорожки точного отсчета, граница прозрачного и непрозрачного участков кодовой дорожки старшего разряда грубого отсчета и середины прозрачных участков остальных кодовых дорожек грубого отсчета расположены вдоль линии считывания, причем непрозрачный участок кодо1569985

10

0

5

0

5

0

5

0

5

0

5

вой дорожки точного отсчета и непрозрачный участок кодовой дорожки старшего разряда грубого отсчета расположены по одну сторону относительно линии считывания, первый и второй управляющие считывающие элементы оптически сопряжены с кодовой дорожкой младшего разряда грубого отсчета со сдвигом относительно линии считываний на ±т(К-Н/8), где К 0,1,2,3,..., размеры считывающих элементов точного отсчета, установленных против одноименной кодовой дорожки .равны а0/2, считывающие с менты точного стече., расположены друг относительно друга на расстоянии ±а0(К+1/4), где К 0,1,2,3,..о, причем ось первого считывающего элемента точного отсчет совмещена с осью непрозрачного участка кодовой дорожки точного отсчета, соприкасающегося с линией считывания выходы первого и второго управляющие считывающих элементов соединены с входами соответственно первого и второго компараторов, выходы которых соединены соответственно с первым и в ч. рым входами блока управления, первь1 и второй выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выходы которого соединены с входами первого слагаемого сумматора, выходы которого являются выходами грубого отсчета преобразователя, выходы формирователя кода точного отсчета являются выходами точного отсчета преобразователя, причем выход старшего разряда формирователя кода точного отсчета соединен с третьим входом блока управления и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход предыдущего разряда формирователя кода т-. ного отсчета соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с третьим управляющим входом мультиплексора, выходы формирователя кода грубого отсчета соединены с входами преобразователя кода, выходы которого соединены с входами второго слагаемого сумматора, причем выход младшего разряда преобразователя кода соединен с четвертым входом блока управления.

2. Преобразователь по п. I, отличающийся тем, что блок управления содержит первый, второй и третий элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и четвертый элементы И, первый и второй

Йыход которого соединен с вторыми вхо-|5 ключены к шине логического нуля,

дами второго и третьего элементов.И, $ход третьего элемента НЕ является f-ретьим входом блока управления и Объединен с третьими входами второго и четвертого элементов И, выход третьего элемента НЕ соединен с третьими входами первого и третьего элементов И, выходы которых соединены с- входами первого элемента ИЛИ, выход которого является первым выходом бло- н.а управления, выходы второго и. четвертого элементов И соединены с входами второго элемента ИЛИ, выход которого является вторым выходом блока управления.

3. Преобразователь по п0 t отличающийся тем, что муль КодГО

20

25

30

вторые входы элементов И второго б ка и второй вход элемента И младше разряда первого блока подключены к шине логической единицы, выходы эл ментов И первого и второго блоков динены с первыми входами элементов соответственно третьего и четверт го блоков, выходы одноименных элем тов И третьего и четвертого блоков соединены с входами .одноименных э ментов ИЛИ блока, выходы которых я ляются выходами мультиплексора, вх элемента НЕ является третьим управ ющим входом мультиплексора, а выхо соединен с вторыми входами -элемент И третьего и четвертого блоков.

КООГО

S. /Л

: T f-j

вторые входы элементов И второго блока и второй вход элемента И младшего разряда первого блока подключены к шине логической единицы, выходы элементов И первого и второго блоков соединены с первыми входами элементов И соответственно третьего и четвертого блоков, выходы одноименных элементов И третьего и четвертого блоков соединены с входами .одноименных элементов ИЛИ блока, выходы которых являются выходами мультиплексора, вход элемента НЕ является третьим управляющим входом мультиплексора, а выход соединен с вторыми входами -элементов И третьего и четвертого блоков.

КООГО

-J

| название | год | авторы | номер документа |

|---|---|---|---|

| Многооборотный преобразователь угол-код | 1980 |

|

SU1080179A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1120388A1 |

| Многоотсчетный фотоэлектрический преобразователь перемещения в код | 1980 |

|

SU997065A1 |

| Преобразователь угол-код | 1982 |

|

SU1016807A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ - КОД | 1991 |

|

RU2029428C1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312735A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ - КОД | 2014 |

|

RU2550553C9 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Устройство для преобразования перемещений в код | 1983 |

|

SU1144192A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1049948A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в качестве элементов связи аналоговых объектов с ЭВМ. Целью изобретения является повышение надежности и точности преобразователя. Цель достигается тем, что в оптоэлектронный преобразователь перемещения в код, содержащий блок управления, осветитель, оптически связанный через кодовый элемент со считывающими элементами грубого и точного отсчетов, выходы которых соединены с входами формирователей кода соответственно грубого и точного отсчетов, введены два управляющих считывающих элемента, два компаратора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор, мультиплексор с соответствующими связями. Управляющие считывающие элементы расположены против кодовой дорожки младшего разряда грубого отсчета со сдвигом относительно друг друга на четверть периода и относительно линии считывания на 1/8 периода. Блок управления по сигналам старшего разряда точного отсчета, младшего разряда грубого отсчета и двум сигналам с выходов управляющих считывающих элементов формирует управляющие сигналы на мультиплексор, по которым на вход одного из слагаемых подается или прямой код единицы, или дополнительный код единицы. На кодовом элементе в грубом отсчете нанесена маска инверсного кода Грея, а дорожка точного отсчета выполнена равномерно квантованной, период которой в четыре раза меньше периода кодовой дорожки младшего разряда грубого счета. 2 з.п. ф-лы, 8 ил.

it

/

Ј

т

BLIiL-BiJI

.L; .iu

i /

ШВ

.iu

i /

ШВ

У

22

FMTT

7F

V

f«, л„

IlL-.

0,

n...n сгф

Й51

.

I .jg«; L.

iirirr

S

гZ7

К08ГО

n

№.#)

25

c E

«

A

ft

Фиг. г

4

bit.

Фиг.з

S8669SI

д-гпш

т

1 j I 1 I I д

LHiLr LТ У т

J j Ц-l | j j-I i 1-1 |

TJuTj4J iJ4 ri ruri f

5866951

Фиг. в

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1971 |

|

SU411623A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-28—Подача