Изобретение относится к вычислительной технике и может быть использовано для определения эксплуатационно- технических характеристик сложных систем, в частности для определения одного из показателей стратегии контроля - очередности контроля технического состояния, очередности восстановления по сетевому графику, оптимальной нагрузки и т.д.

Цель изобретения - расширение функциональных возможностей за счет учета случайного воздействия возмущающих факторов на технические объекты, объединенные в систему.

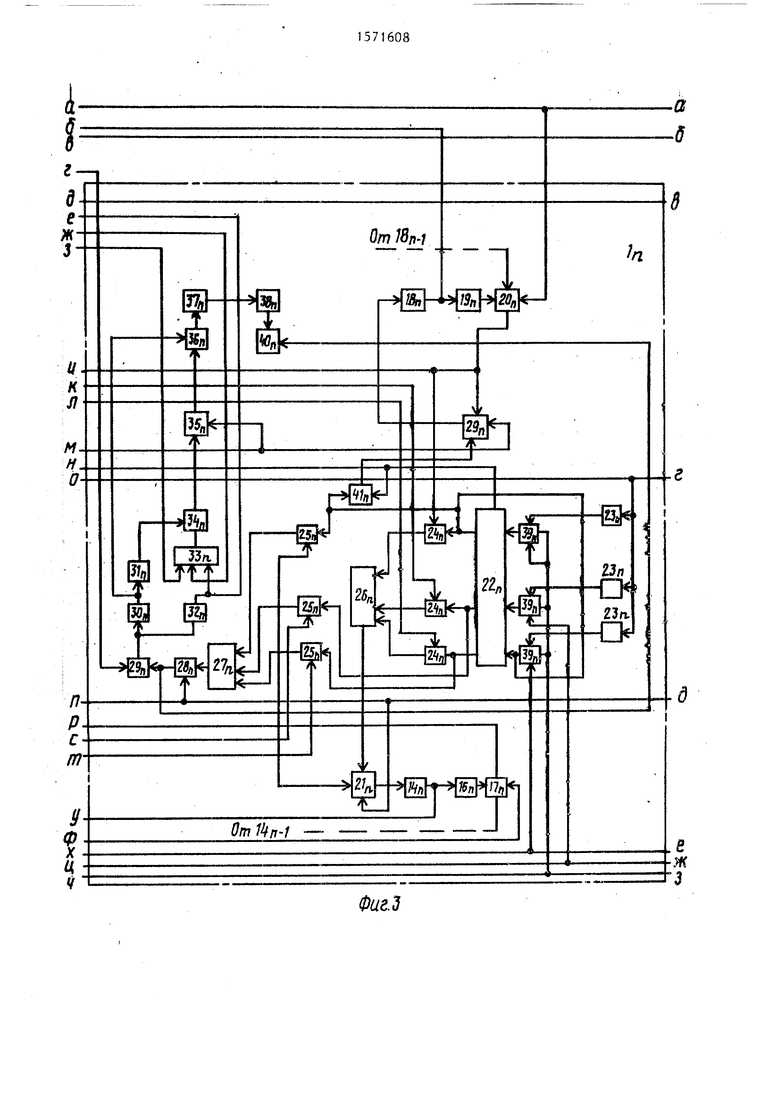

На фиг. 1 - 4 представлена схема предложенного устройства.

Устройство содержит вычислительные блоки 1, датчики 2 контроля функционирования, дешифратор 3, дифференцирующие элементы 4, генератор 5 пакетов импульсов, элемент ИЛИ 6, элемент 7 задержки, генератор 8 тактовых импульсов, элемент И 9, реверсивный счетчик 10, элемент НЕ If, элемент И 12, генератор 13 чисел, дешифратор 14, элемент И 15, элемент НЕ 16, элемент И 17, дешифратор 18, элемент НЕ 19, реверсивные счетчики 20 и 21, регистр 22 сдвига, узел 23 переключателей, группы 24,25 элементов И, элементы ИЛИ 26 и 27, счетчик 28, элемент 29 сравнения, элемент 30 задержки, элемент НЕ 31, дифференцирующий элемент 32, элемент ИЛИ 33, переключатель 34, счетчик 35, переключатель 36, дешифратор 37, узел 38 контроля, группу 39 элементов И , деыпф-

На

сл J

о о

00

ратор 40 , элемент II 41 , одно- вибратор 42.

Устройство работает следующим образом.

По входу установки запускается генератор 5 и предварительно в реверсивный счетчик 10 записывается число, соответствующее количеству разрядов в регистрах 22. Количество этих разрядов также соответствует числу регистров по максимальной размерности матрицы смежности, т.е. максимальному количеству технических объектов (ТО), входящих в сложную систему. Затем при помощи узла 23 переключателей (например, перемычка, переключатель и т.д.) на первые входы только тех элементов И группы 39 коммутируется выход элемента 7 задержки, которые соответствуют разрядам регистров 22, в которых должны быть записаны единицы исходной матрицы смежности. На вто рые и третьи входы элементов И группы 29 поданы потенциалы логической 1 с выходов датчиков 2, так как в исходном состоянии все ТО исправны и задействованы.

Каждый регистр сдвига соответствует одной соответствующей строке матри ;цы смежности, а i-й разряд всех регистров соответствуе-т i-му столбцу этой матрицы. После коммутации соответствующих разрядов к выходу элемента 7 задержки по входу установки подается импульс сбрбса на соответствующие установочные входы регистров

22сдвига, реверсивных счетчиков 21, счетчиков 28 для приведения их в нуле вое состояние. Задержанный элементом 7 задержки импульс записывает через скоммутированные переключатели узла

23и через группу 39 элементов И в регистры 22 матрицу смежности исследуемого графа. После окончания этой операции устройство готово к работе.

При подаче разрешающего потенциала по шине Пуск на вход пуска на выходе элемента И 9 появляются импульсы с генератора 8 тактовых импульсов, так как на входе элемента И 9 находится единичный потенциал с выхода элемента НЕ 11, который пропадает лишь при нулевом состоянии счетчика 10 последнего. Тактовые импульсы поступают на управляющие входы регистров 22 сдвига и на входы элементов И 41. Информация с выхода каждого регистра подается на его вход, а также

через элемент И 41 на суммирующий вход соответствующего реверсивного счетчика 20. После прихода n-го тактового импульса на вычитающий вход ре- версивного счетчика 10 он переходит в нулевое состояние, так как в исходном состоянии в него записано число, соответствующее максимальной размёр0

ности матрицы смежности. На выходе

реверсивного счетчика 10 появляется напряжение логической 1, которое через элементы НЕ 11 запрещает дальнейшее прохождение тактовых импульсов

,. через элемент И 9. За п тактов информация в регистрах переписывается полностью и соответствует исходной матрице смежности. В соответствующих реверсивных счетчиках 20 записывается

Q число единиц, содержащихся в соответствующей строке матрицы смежности. На этом заканчивается первый шаг итерации.

I

5 (п+1)-й импульс с генератора 8 тактовых импульсов поступает через элемент И 15 первого блока 1 на вычитающий вход реверсивного счетчика 20, так как элемент И 15 открыт единичным Q потенциалом с выхода реверсивного счетчика 10 и выхода дешифратора 18 через элемент НЕ 19, а счетчик 20 находится в нулевом состоянии и на его выходе напряжение логического О. 5 Дешифраторы 18 и 14 выдают на своем выходе напряжение логической 1 лишь в случае нулевого состояния соответствующего реверсивного счетчика. Тактовые импульсы, начиная с (п+1)-го, о через элемент И 15 начинают поступать на вычитающий вход реверсивного счетчика 20 первого блока , а также на входы элементов И 24 всех блоков 1, соответствующих первым разрядам всех 45 регистров 22 сдвига. На входы элементов И 24 подаются сигналы с выходов первых разрядов соответствующих регистров сдвига. Поэтому если в первом разряде соответствующего регист- CQ ра сдвига 22 записана единица, соответствующий ему элемент И 24 открывается и тактовые импульсы через соответствующий элемент И 24, элемент ИЛИ 26 поступают на суммирующий вход core ответствующего реверсивного счетчика 21, После того, как на вычитающий вход реверсивного счетчика 20 первого блока 1 поступает количество тактовых импульсов, соответствующее чис515

лу единиц в первой строке матрицы смежности, счетчик переходит в нулевое состояние, на выходе дешифратора 18 появляется напряжение логической 1, которое через элемент НЕ 19 запрещает прохождение тактовых импульсов через элемент И 15. В соотнетст- вующих реверсивных счетчиках 20 записывается число, равное количеству еди ниц в первой строке матрицы смежности анализируемого графа. Напряжение логической 1 с выхода дешифратора 18 первого блока 1 открывает элемент И 15 второго блока 1, так как на вход этого элемента подается напряжение логической 1 с элемента НЕ 19. Тактовые импульсы через элемент И 15 второго блока 1 с выхода генератора 8 поступают на вычислительный вход реверсивного счетчика 20, а также на входы элементов И 24 всех блоков 1, соответствующих вторым разрядам всех регистров сдвига 22. Если в них записана единица, то тактовые импульсы через соответствующий элемент ИЛИ 26 поступают,на суммирующий вход соответ ствующего реверсивного счетчика 21.

После прохождения тактовых импульсов, количество которых соответствует числу единиц во второй строке матрицы смежности, т.е. числу, записанному в реверсивном счетчике 20 второго бло ка 1, на выходе дешифратора 18 появляется напряжение логической 1, которое через элемент НЕ 19 запрещает прохождение тактовых импульсов через элемент И 15 второго блока 1 и разрешает прохождение тактовых импульсов через элемент И 15 третьего блока 1. В дальнейшем работа устройства происходит аналогично до тех пор, пока информация из последнего n-го реверсивного счетчика 20 не переписывается в соответствующие реверсивные счетчики 21 блоков 1. На этом заканчивается второй шаг итерации.

Единичные сигналы с выходов дешифраторов 18 поступают на входы элемента И 12, напряжение с выхода которого открывает элемент И 17 первого блока 1 для прохождения импульсов с выхода генератора 8 тактовых импульсов, так как на другой вход элемента И 17 поступает напряжение логической 1 с выхода элемента НЕ 16, на вход которого подается напряжение логического О выхода дешифратора 14. Тактовые импульсы с выхода генерато16086

р,ч 8 поступают через элемент И 17 н,ч вычитающий вход реверсивного счетчика 21, а также на входы элементов 25 всех блоков 1. На другие входы элементов И 25 подключены выходы первых разрядов регистров 22 сдвига. Элементы И 25, которым соответствуют первые разряды соответствующих регистров 22 JQ сдвига, в которых записана единица, открываются и тактовые импульсы через них и соответствующие элементы ИЛИ 27 записываются в соответствующие счетчики 28. При прохождении через эле)5 мент И 17 первого блока 1 импульсов, количество которых соответствует числу, записанному в счетчике 21, последний переходит в нулевое состояние и на выходе дешифратора 14 появляется

20 напряжение логической 1. Поэтому на выходе элемента НЕ 16 появляется напряжение логического нуля, которое запрещает дальнейшее прохождение тактовых импульсов через элемент И 17.

25 Одновременно напряжение логической 1 с выхода дешифратора 14 первого блока 1 подается на вход и открывает элемент И 17 второго блока 1. Тактовые импульсы начинают поступать на

30 вычитающий вход реверсивного счетчика 21 второго блока 1 и первые входы элементов И 25, соответствующие вторым разрядам всех регистров 22 (второму столбцу матрицы смежности). На

,,. вторые входы подключены элементы И выходов соответствующих вторых разрядов регистров 22 сдвига. Напряжение логической 1 с трех разрядов, в которых записана единица, открывает со4Q ответствующне элементы И 25 и импульсы с их выхода через соответствующие элементы ИЛИ 27 поступают на запись в соответствующие счетчики 28. Тактовые импульсы через элемент И 17 про45 ходят до тех пор, пока реверсивный счетчик 21 второго блока 1 не проходит в нулевое состояние и не закрывает через дешифратор 14 и элемент НЕ 16,элемент И 17. Напряжение логичес0 кой 1 с выхода дешифратора 14 открывает элемент И 17 третьего блока 1 для прохождения тактовых импульсов, и цикл работы протекает аналогично. Устройство функционирует до тех

5 П°Р пока информация из последнего реверсивного счетчика 21 не переписывается в соответствующие счетчики 23 (третий шаг итерации). После этого прохождение тактовых импульсов на ка7157

кие-либо элементы устройства запрещается элементами 15,17 и 9. Информация, записанная в каждом счетчике, соответствует рангу соответствующей вершины исследуемого графа. Эта информация дешифрируется соответствующим дешифратором 40 и отображается на соответствующем узле 38. При появлении единицы на выходе элемента 1 последнего блока 1, свидетельствующей о завершении цикла вычислений, запускается генератор 13 чисел. Числовые значения с его выхода поступают на вход элементов 29 сравнения. При равенстве значений на выходе генератора 13 и счетчика 28 на выходе соответствующего элемента 29 появляется потенциал логической 1, который через элемент 32 и элемент ИЛИ 33 запишется в счетчики 35 через переключатели 34. После чего потенциал, поступивший через элемент 30 задержки на вход элемента НЕ 31, закроет переключатель 34, предотвращая тем самым

ложную запись 1 с выходов элементов 32, и этим же напряжением открывается переключатель 36, разрешая про хождение информации со счетчика 35 на дешифратор 37 и узел 38. На узле отоб разится значение ранга i-й вершины и ее приоритет в системе - первый. По мере уменьшения значений на выходе генератора 13 в какой-то момент времени сработает элемент 29, а так как в счете 35 уже была записана единица, то на узле 38.- отобразится ранг j-й вершины и ее приоритет в системе второй. В дальнейшем устройство работает аналогичным образом, пока не отобразятся значения приоритетов всех ТО.

В случае отказа или отключения какого-то, например k-го, ТО на выходе блока 2, потенциал логического О, на выходе дешифратора 3 меняется кодовая комбинация и импульс с выхода элемента ИЛИ 6 сбрасывает всю исходную информацию в регистрах 22, счет- . чиках 20, 21, 28, 35. Закрываются элементы 39 k-й строки и k-ro столбца матрицы смежности. В счетчик 10 с выхода генератора 5 заносится число п. После чего с выхода элемента 7 записывается в регистры 22 матрица смежности (элементы k-й строки и k-ro столбцов равны нулю), а со второго выхода элемента 7 разрешается прохождение импульсов с выхода генератора 8

16088

Начинается новый цикл определения новых рангов и новых приоритетов вершин нового графа по описанному алгоритму.

-1 Формула изобретения

10

15

20

25

Ю

40

35

Устройство для определения приоритета объектов в системах с изменяющейся структурой, содержащее первый и второй элементы И, первый элемент задержки, генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, первый реверсивный счетчик, выход которого через первый элемент НЕ соединен с вторым входом первого элемента И, а вычитающий вход соединен с выходом первого элемента И, вычислительные блоки, каждый из которых включает регистр сдвига, узел переключателей, первую и вторую группы элементов И, два элемента ИЛИ, три дешифратора, два реверсивных счетчика, два элемента НЕ, первый счетчик, два элемента И, узел контроля, причем в каждом вычислительном блоке выходы разрядов регистра сдвига подключены к первым входам элементов И первой и второй групп, выходы элементов И первой группы соединены с входами первого элемента ИЛИ соответственно, выход которого соединен с суммирующим входом второго реверсивного счетчика, выход которого через первый дешифратор подключен к входу второго элемента НЕ, выход которого подключен к первому входу третьего элемента И, выход которого соединен с вычитающим входом второго реверсивного счетчика и с вторым входом 1-го элемента И второй группы каждого вычислительного блока, выходы элементов И второй группы соединены с входами второго элемента ИЛИ соответственно, выход которого подключен к информационному входу первого счетчика, выход старшего разряда регистра сдвига соединен с установочным входом его первого разряда, вычитающий, вход третьего реверсивного счетчика соединен с выходом четвертого элемента И, первый вход которого соединен -с выходом третьего элемента НЕ, вход которого подключен к выходу второго дешифратора, вход которого соединен с выходом третьего реверсивного счетчика, вход сдвига регистра сдвига каждого вычислительного блока полк-цочен к выходу первого элемента Ч, РЫ:;ОД первого де-

45

50

55

9

шифратора предыдущего вычислительного блока соединен с вторым входом третьего элемента И последующего вычислительного блока, выход второго дешифратора предыдущего, вычислительного блока соединен с вторым входом четвертого элемента И последующего вычислительного блока, выход четвертого элемента И соединен с вторым входом i-rp элемента И первой группы вычислительных блоков, выход второго деши- фратора каждого вычислительного блока подключен к соответствующему входу второго элемента И, выход которого соединен с вторым входом третьего элемента И первого вычислительного блока установочные входы регистров сдвига, первых счетчиков, вторых и третьих реверсивных счетчиков вычислительных блоков соеди-нены с шиной Сброс устройства и с входом первого элемента задержки, первый выход которого соединен с входами переключателей узла каждого вычислительного блока, выход генератора тактовых импульсов соединен с третьими входами третьего и четвертого элементов И каждого вычислительного блока, отличающееся тем, что, с целью расширения фунцио- нальных возможностей за счет учета случайного воздействия возмущающих факторов на технические объекты, объединенные в систему, в него введены датчики контроля функционирования, четвертый дешифратор, группа дифференцирующих элементов, генератор пакетов импульсов, третий элемент ИЛИ, одно- вибратор, генератор чисел, а в каждый вычислительный блок введены элемент сравнения, второй элемент задержки, четвертый элемент НЕ, дифференцирующий элемент, четвертый элемент ИЛИ, два переключателя, второй счетчик, пятый дешифратор, третья группа элементов И, пятый элемент И, причем входы датчиков контроля функционирования являются контрольными входами устройства, а выходы соединены с входами четвертого дещифратора соответственно, выход 1-го датчика контроля функционирования соединен с первыми входами элементов И третьей группы 1-го вычислительного блока и вторыми входами i-x элементов И третьей труппы каждого вычислительного блока, выходы четвертого дешифратора подключе

160810

ны к входам соответствующих дифференцирующих элементов группы, выходы ко- торых соединены с входами третьего элемента ИЛИ, выход которого подключен

к входу первого элемента задержки и к входу генератора пакетов импульсов, выход которого соединен с суммирующим входом первого реверсивного счетчика,

. - второй выход первого элемента задержки соединен с шиной Пуск устройства и с входом одновибратора, выход которого подключен к третьему входу первого элемента И, выход старшего разряда

5 регистра сдвига в каждом вычислительном блоке подключен к первому входу пятого элемента И, выход которого подключен к суммирующему входу третьего реверсивного счетчика, второй вход

20 пятого элемента И соединен с выходом первого элемента И, третьи входы элементов И третьей группы соединены с выходами соответствующих переключателей узла, а выходы соединены с входа25 ми разрядов регистра сдвига соответственно, первый вход элемента сравнения соединен с выходом генератора чисел, второй вход соединен с входом третьего дешифратора и с выходом первого счет30 чика, выход элемента сравнения соединен с входами дифференцирующего элемента и второго элемента задержки, выход которого соединен с управляющим входом первого переключателя и входом четвертого элемента НЕ, выход которого подключен к управляющему входу второго переключателя, информационный вход которого соединен с выходом четвертого элемента ИЛИ, а .выход соеди40 нен с информационным входом второго счетчика, установочный вход которого соединен с шиной Сброс устройства, а выход соединен с информационным входом первого переключателя, выход ко45 торого соединен с входом пятого дешифратора, выход которого подключен к второму входу узла контроля, первый вход которого соединен с выходом Третьего дешифратора, выходы дифферен5Q цирующих элементов всех вычислительных блоков соединены .с соответствующими входами четвертых элементов ИЛИ всех вычислительных блоков, запускающий вход генератора чисел соединен с

г выходом первого дешифратора последнего вычислительного блока.

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования параметров графа | 1983 |

|

SU1120341A1 |

| Устройство для определения параметров графа | 1985 |

|

SU1374237A1 |

| Устройство для исследования нечетких графов | 1986 |

|

SU1325503A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2020 |

|

RU2723288C1 |

| Устройство для анализа параметров графа | 1988 |

|

SU1681312A1 |

| Вероятностный автомат | 1982 |

|

SU1045232A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных гиперкубических циклических системах | 2019 |

|

RU2718166C1 |

| Устройство для поиска минимального значения интенсивности размещения в многопроцессорных гиперкубических системах при направленной передаче информации | 2022 |

|

RU2783489C1 |

| Устройство для перебора сочетаний,размещений и перестановок | 1983 |

|

SU1124319A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

Изобретение относится к вычислительной технике и может быть использовано для определения эксплуатационно-технических характеристик сложных систем. Целью изобретения является расширение функциональных возможностей за счет учета случайного воздействия возмущающих факторов на технические объекты, объединенные в систему. Устройство содержит вычислительные блоки, датчики контроля функционирования, дешифраторы, дифференцирующие элементы, генератор пакетов импульсов, элементы ИЛИ, элемент задержки, генератор тактовых импульсов, элементы И, реверсивные счетчики, элементы НЕ, генератор чисел, узел переключателей, группы элементов И, счетчики, элемент сравнения, переключатели, узел контроля, одновибратор, регистр сдвига. 4 ил.

809 US I

Фиг.3

а б

r-JlTk-JI

42

«-

/7уг

е-

//

Сброс

OmW

| Устройство для исследования путей в графах | 1980 |

|

SU943738A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для исследования параметров графа | 1983 |

|

SU1120341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-07-20—Подача