Изобретение относится к измерительной технике и может быть использовано для поверки цифровых измерителей девиации фазы,

Известно устройство для поверки цифровых приборов, содержащее источник эталонного сигнала, модулятор, клеммы для подключения поверяемого прибора, блок вычитания кодов, блок регистрации, генератор тактовых импульсов, реверсивный счетчик импульсов, дешифратор, триггер реверса, первый и второй элементы И, управляемый делитель частоты, синхронный делитель частоты, источник логического сигнала и три переключателя.

Недостатком известного устройства является непроизвольное изменение постоянной составляющей параметра выходного сигнала при изменении оператором максимального размаха переменной составляющей параметра сигнала в процессе поверки, а также невозможность целенаправленного воспроизведения любых необходимых значений этой постоянной составляющей. В результате оказывается затрудненным определение погрешностей измерения разных значений максимального размаха пере- менной составляющей при различных значениях постоянной составляющей параметра сигнала. То есть, достоверность поверки измерителей максимального размаха переменной составляющей параметра сигнала снижается.

Кроме того, в известном устройстве частота генератора тактовых импульсов не связана с частотой источника эталонного сигнала (то есть, эти сигнальные последовательности непрерывно смещаются относиN

:оо

СЛ

тельно друг друга во времени) и отсутствует привязка момента изменения кода на входе управления модулятором к переходам через ноль его входного (эталонного) сигнала.

В результате, устройство работает нормально только тогда, когда период изменения кода управления модулятором превышает период напряжения, вырабатываемого источником эталонного сигнала. В этом случае всегда обеспечивается воспроизведение заданного значения максимального размаха переменной составляющей (в нашем примере фазы) сигнала ( Д р max), то есть полное соответствие максимального отклонения параметра (фазы) сигнала установленному кодом управления значению.

Когда же в устройстве, при определен ных сочетаниях независимо задаваемых в процессе поверки цифровых приборов значений максимального размаха и частоты повторения переменной составляющей параметра выходного сигнала модулятора, период изменения кода управления модулятором оказывается меньше периода напряжения, вырабатываемого эталонного сигнала, возникает периодическое (с периодом биения частот источника эталонного сигнала и генератора тактовых импульсов) несоответствие фактического размаха отклонения переменной составляющей параметра (фазы) выходного сигнала ( Ду ) модулятора заданному кодом управления значению (на фиг 2 Лу Лу max) Тем самым снижена точность воспроизведения максимального размаха переменной составляющей фазового сдвига у данного устройства.

Известно устройство, содержащее источник эталонного сигнала в виде преобразователя частоты, модулятор, клеммы для подключения поверяемого прибора, блок вычитания кодов, блок регистрации генератор тактовых импульсов, реверсивный счетчик импульсов, дешифратор триггер реверса, два элемента И, управляемый делитель частоты, синхронный делитель частоты, источник логического сигнала и три переключателя, блок коммутации и два формирователя коротких импульсов

У этого устройства повышена точность воспроизведения максимального размаха переменной составляющей фазового сдвига, однако недостатком устройства, как и устройства, является низкая достоверность поверки.

Наиболее близким по технической сущности к изобретению является устройство для поверки цифровых приборов которое содержит источник эталонного сигнала, выход которого подключен к входу модулятора, клеммы для подключения поверяемого прибора, соединенные с выходом модулятора, кодовый выход которого подключен к

первому входу основного блока вычитания кодов, блок регистрации, вход которого соединен с выходом основного блока вычитания кодов, реверсивный счетчик импульсов и дешифратор, выход и вход которых порэз0 рядно объединены триггер реверса, у которого первый вход соединен с выходом дешифратора, второй вход через первый переключатель соединен с выходом реверсивного счетчика импульсов, прямой выход

5 через первый элемент И подключен к входу суммирования, а инверсный выход через второй элемент И - к входу вычитания реверсивного счетчика, управляемый делитель частоты, вход которого соединен с

0 выходом генератора тактовых импульсов, синхронный делитель частоты, вход которого соединен с выходом управляемого делителя частоты, а выход через второй переключатель подключен ко вторым вхо5 дам обоих элементов И, и источник логического сигнала, выход которого через третий переключатель подключен ко второму входу основного блока вычитания кодов А также содержит дополнительный блок вычитания

0 кодов, четвертый переключатель и блок сложения кодов, выход которого подключен к управляющему входу модулятора, первый вход поразрядно соединен с выходом реверсивного счетчика импульсов, а второй

5 вход соединен с выходом дополнительного блока вычитания кодов, у которого первый вход поразрядно объединен со вторым входом основного блока вычитания кодов, а второй вход через четвертый переключатель

0 соединен с выходом источника логического сигнала к которому через третий переключатель подключен установочный вход реверсивного счетчика.

Данное устройство, как и известное ус5 тройство, за счет того, что частота генератора тактовых импульсов не связана с частотой источника эталонного сигнала (то есть эти сигнальные последовательности непрерывно смещаются относительно друг

0 друга во времени), и отсутствует привязка момента изменения кода на входе управления модулятором к переходам через ноль его входного (эталонного) сигнала, оказывается нормально работающим только в ограниченном диапазоне возможных сочетаний

5 одновременно воспроизводимых значений максимального размаха и частоты повторения (изменения) переменной составляющей параметра (фазы) выходного сигнала модулятора А именно, лишь тогда, когда величина периода изменения кода управления модулятором превышает (чем больше, тем лучше) величину периода напряжения источника эталонного сигнала.

В данном устройстве, при использовании его для поверки измерителей максимального размаха переменной составляющей фазы сигнала (девиации фазы), в качестве модулятора могут быть использованы дискретные или цифровые кодоуправляемые фазовращатели.

Применение дискретных кодоуправляе- мых фазовращателей в устройстве-прототи- пе не нарушает работоспособности поверяемых измерителей девиации фазы, в частности и при переходе воспроизводимого фазового сдвига через 0 или 360°. Однако использование дискретных кодоуправляе- мых фазовращателей затрудняет получение воспроизводимого фазового сдвига с высокой точностью и стабильностью, так как для указанных фазовращателей требуется достаточно сложная реализация блоков задержки на ж /2 и инвертора (я ) , которые должны обеспечить стабильность фазового сдвига на л /2 и . а для блока задержки на я/2, кроме того, необходимо поддержание равенства амплитуды выходного сигнала амплитуде входного сигнала с высокой точностью, для широкого диапазона частот аналогового сигнала.

Более высокую точность и стабильность обеспечивают цифровые кодоуправляемые фазовращатели, основанные на триггерных делителях частоты, вследствие чего их применение является более предпочтительным.

Однако его применение в устройстве- прототипе приводит к нарушению работоспособности поверяемого цифрового измерителя девиации фазы при переходе значения воспроизводимого фазового сдвига через 0 или 360°.

Нарушение работоспособности происходит из-за того, что цифровые кодоуправляемые фазовращатели обладают конечной величиной задержки сигнала. При этом в процессе работы устройства при нарастании значения кода управления происходит увеличение величины задержки цифрового кодоуправляемого фазовращателя, а при убывании кода управления величина задержки уменьшается.

При этом, если суммарный код (относительно какой-то постоянной величины, определяемой входным кодом блока 19 вычитания и кодом реверсивного счетчика 7) увеличивается и переходит через нулевое значение, задержка цифрового кодоуправ0 ляемого фазовращателя 2 постоянно увеличивается до своего максимального значения, а затем скачком принимает нулевое значение. В результате, в задержанной периодической импульсной последовательно5 сти на выходе цифрового кодоуправляемого фазовращателя 2 возникает в этот момент наложение импульсов. Такая ситуация еще не приводит к сбою в работе измерителя 3 девиации фазы.

0 В том случае, когда суммарный код (относительно какой-то постоянной величины, определяемой выходным кодом блока 19 вычитания и кодом реверсивного счетчика 7) уменьшается и переходит через нулевое

5 значение, задержка цифрового кодоуправляемого фазовращателя 2 постепенно уменьшается до нуля, а затем скачком принимает максимальное значение. В результате, в задержанной периодической

0 импульсной последовательности на выходе цифрового кодоуправляемого фазовращателя 2 возникает в этот момент пауза большая периода сигнала. Эта пауза приводит к сбою в работе измерителя 3 девиации фазы,

5 структурная схема которого приведена за счет того, что в этом случае формирователь временных интервалов поверяемого фазометра вместо нулевого сформирует временной интервал, пропорциональный 180°.

0 Кроме того, устройству-прототипу присуща нелинейность фазовой характеристики за счет получающейся разной длины у формируемых ступенек.

Все этого вместе взятое снижает точ5 ность воспроизведения максимального размаха переменной составляющей фазового сдвига.

Цель изобретения - повышение точности воспроизведения максимального раз0 маха переменной составляющей фазового сдвига, соответствующего заданной величине девиации фазы во всем диапазоне возможных сочетаний одновременно воспроизводимых постоянных фазовых

5 сдвигов, а также значений максимального размаха и частоты повторения переменной составляющей фазового сдвига.

Указанная цель достигается тем, что в устройстве, содержащее источник эталонного сигнала, выход которого подключен к входу основного цифрового кодоуправляемого фазовращателя и клемме опорного канала поверяемого фазометра, блок регистрации, вход которогохоединен с выходом первого блока вычитания кодов, реверсивный счетчик импульсов и дешифратор, выход и вход которых поразрядно объединены, триггер реверса, у которого первый вход соединен с выходом

дешифратора, второй вход через первый переключатель соединен с выходом реверсивного счетчика импульсов, прямой выход через первый элемент И подключен к входу суммирования, а инверсный выход через второй элемент И - к входу вычитания реверсивного счетчика, управляемый делитель частоты, вход которого соединен с выходом генератора тактовых импульсов, синхронный делитель частоты, вход которого соединен с выходом управляемого делителя частоты, а выход через второй переключатель подключен ко вторым входам обоих элементов И, второй блок вычитания, у которого первый вход поразрядно объединен со вторым входом первого блока вычитания кодов и через третий переключатель подключен к выходу источника логического сигнала, который через четвертый переключатель соединен со вторым входом второго блока вычитания кодов а через третий переключатель подключен к установочному входу реверсивного счетчика импульсов, введены дополнительный цифровой кодоуправляемый фазовращатель, регистр памяти и формирователь коротких импульсов, причем вход дополнительного цифрового кодоуправляемого фазовращателя соединен с выходом основного цифрового кодоуправляемого фазовращателя, вход управления подключен к выходу второго блока вычитания кодов, тактовый вход объединен с тактовым входом основного цифрового кодоуправляемого фазовращателя и подключен к выходу генератора тактовых импульсов, а выход соединен с клеммой фазопеременного канала поверяемого фазометра, вход регистра памяти соединен с выходом реверсивного счетчика импульсов, выход соединен с управляющим входом основного цифрового кодоуправляемого фазовращателя, а вход управления подключен к выходу источника эталонного сигнала, выполненного в виде преобразователя частоты, вход которого соединен с выходом генератора тактовых импульсов, вход формирователя коротких импульсов соединен с выходом дешифратора, а выход подключен к установочным входам источника эталонного сигнала, управляемого делителя частоты и синхронного делителя частоты.

Преобразователь частоты выполнен в виде делителя или умножителя частоты, счетный вход которого является входом, выход старшего разряда - выходом, а установочный вход - установочным входом преобразователя частоты.

Для получения синусоидального опорного и фазопеременного сигналов на выходе устройства к выходам преобразователя

частоты и дополнительного цифрового кодоуправляемого фазовращателя могут быть подключены фильтры.

Авторами не обнаружено технических

решений, имеющих признаки, сходные с признаками, отличающими заявляемое решение от прототипа, что позволяет сделать вывод о соответствии заявляемого решения критерию существенные отличия

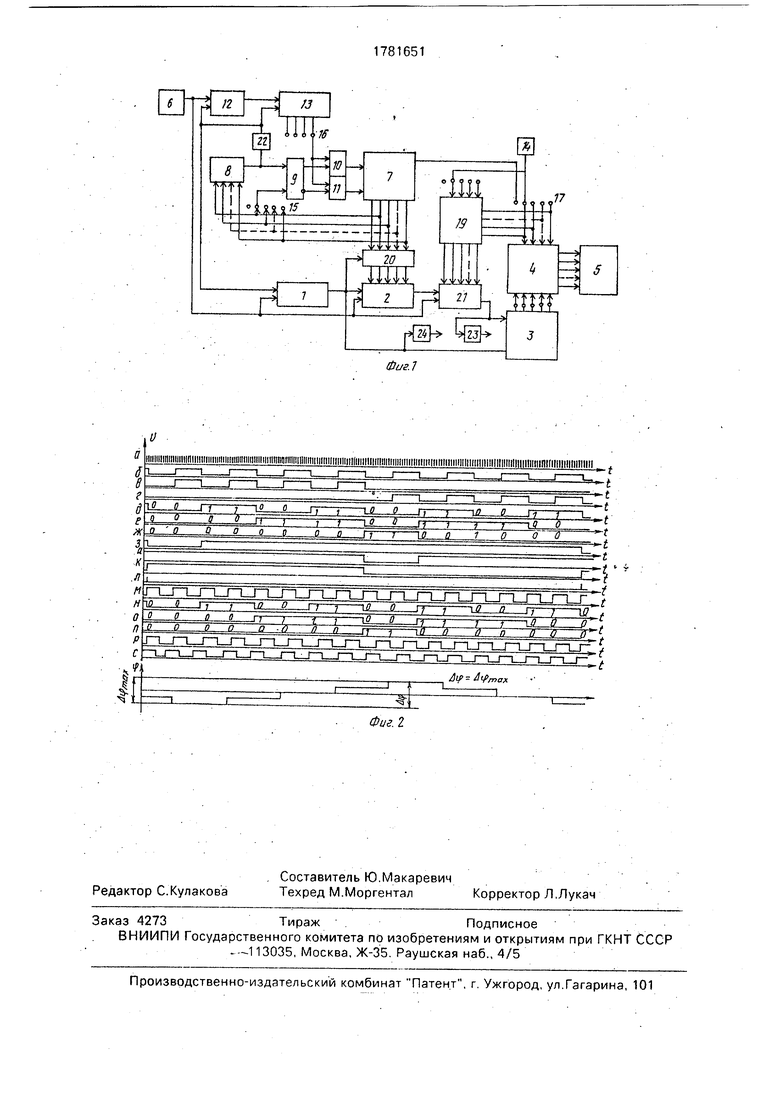

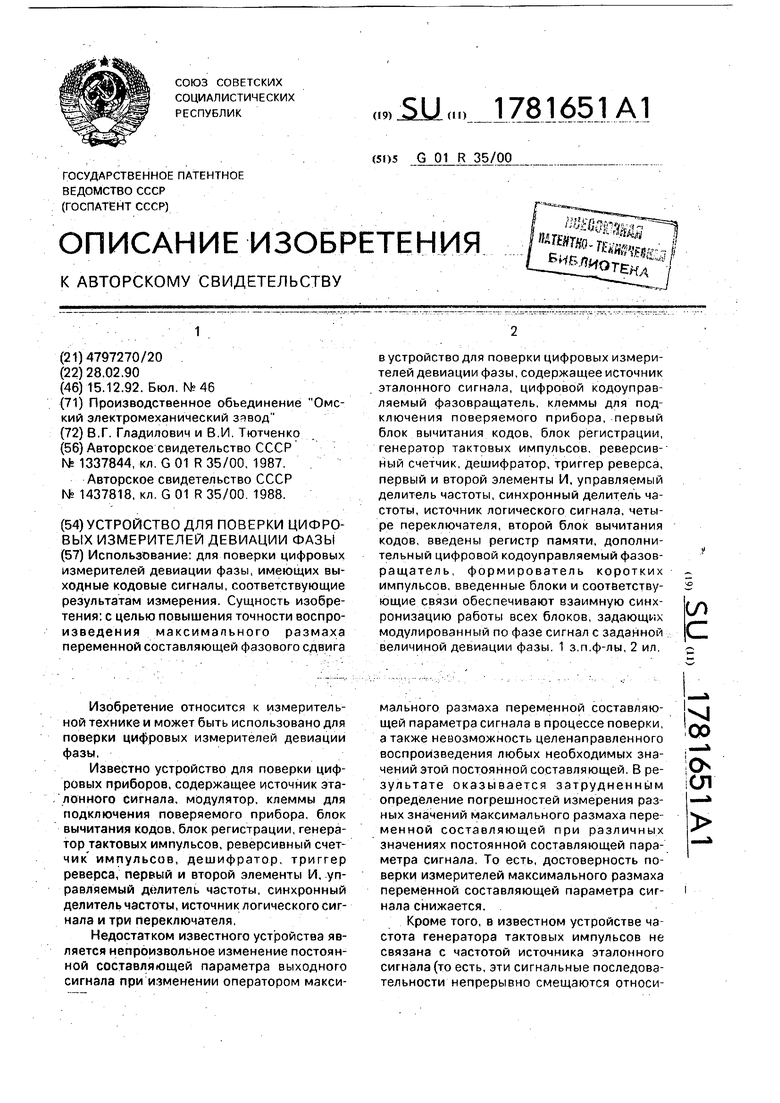

0На фиг. 1 представлена структурная схема устройства для поверки цифровых измерителей девиации фазы, на фиг. 2 - временные диаграммы, поясняющие работу устройства.

5 Устройство содержит преобразователь 1 частоты, цифровой кодоуправляемый фазовращатель 2, клеммы для подключения поверяемого прибора 3, первый блок А вычитания кодов, блок 5 регистрации, генера0 тор б тактовых импульсов, реверсивный счетчик 7 импульсов, дешифратор 8, триггер 9 реверса, первый 10 и второй 11 элементы И, управляемый делитель 12 частоты, синхронный делитель 13 частоты источник 14

5 логического сигнала, четыре переключателя 15-18, второй блок 19 вычитания кодов, регистр 20 памяти, дополнительный цифровой кодоуправляемый фазовращатель 21, формирователь 22 коротких импульсов, фильт0 ры 23, 24. причем выход преобразователя 1 частоты подключен к входу цифрового кодоуправляемого фазовращателя 2 выход которого соединен с входом цифрового кодоуправляемого фазовращателя 21, кодо5 вый вход которого подключен к выходу блока 19 вычитания кодов, выход цифрового кодоуправляемого фазовращателя 21 соединен с входом поверяемого прибора 3, кодовый выход которого подключен к первому

0 входу блока 4 вычитания кодов, вход блока 5 регистрации соединен с выходом блока 4 вычитания кодов, выход реверсивного счетчика 7 импульсов поразрядно объединен с входом дешифратора 8 и через триггер 20

5 памяти подключен к управляющему входу цифрового кодоуправляемого фазовращателя 2, первый вход триггера 9 реверса соединен с выходом дешифратора 8, второй вход через первый переключатель 15 соеди0 нен с выходом реверсивного счетчика 7 импульсов, прямой выход через первый элемент 10 И подключен к входу суммирования, а инверсный выход через второй элемент 11 И - к входу вычитания реверсивного

5 счетчика 7 импульсов, вход управляемого делителя 12 частоты соединен с выходом генератора 6 тактовых импульсов, вход синхронного делителя 13 частоты соединен с выходом управляемого делителя 12 частоты, а выход через второй переключатель 16 подключей ко вторым входам первого 10 и второго 11 элементов И соответственно, выход источника 14 логического сигнала через третий переключатель 17 подключен к установочному входу реверсивного счетчика 7 импульсов и ко второму входу блока 4 вычитания кодов и через четвертый переключатель 18 подключен к первому входу блока 19 вычитания кодов, у которого второй вход поразрядно объединен со вторым входом блока 4 вычитания кодов, тактовые входы преобразователя 1 частоты, цифровых кодо- управляемых фазовращателей 2 и 21 объединены и подключены к выходу генератора тактовых импульсов, вход формирователя .22 коротких импульсов подключен к выходу дешифратора 8, а выход - к установочным входам управляемого делителя 12 частоты, синхронного делителя 13 частоты и преобразователя 1 частоты, выход которого в свою очередь подключен к управляющему входу регистра 20 памяти.

Преобразователь 1 частоты выполнен в виде делителя или умножителя частоты, счетный вход которого является входом, вы- ход старшего разряда - выходом, а установочный вход - установочным входом преобразователя частоты.

Для получения синусоидального опорного и фазопеременного сигналов на выхо- де устройства к выходам преобразователя 1 частоты и дополнительного цифрового кодо- управляемого фазовращателя 21 могут быть подключены фильтры 23, 24

Преобразователь 1 частоты предназначен для формирования опорного сигнала из импульсного напряжения на выходе генератора 6 и, в зависимости от соотношения требуемых частот на выходе генератора б и преобразователя 1, содержит либо делитель, либо умножитель частоты Если в качестве преобразователя 1 частоты используется делитель частоты, то он, как и делитель 13 может быть выполнен на микро- схемах 155 ИЕ5, 155 ИЕ2, 155 ИЕ8 с переключателем (в случае необходимости изменения частоты опорного напряжения), Если же в качестве преобразователя 1 частоты используется умножитель частоты, то он может представлять собой управляемый напряжением мультивибратор, выход которого, являющийся выходом умножителя, соединен со счетным входом делителя частоты, выход которого соединен со вхо- дом импульсного детектора, второй вход которого соединен с выходом генератора 6 тактовых импульсов, а выход через интегрирующую RS-цепочку подключен ко входу управления мультивибратора

В качестве цифрового кодоуправляемо- го фазовращателя 2 может быть использовано устройство управляемой задержки импульсов 7. Для этого достаточно подать на управляющие входы реверсивного счетчика 7 устройства управляемой задержки импульсов код соответствующий величине требуемой задержки сигнала, а на управляющие входы реверсивного счетчика 6 устройства управляемой задержки импульсов - код, соответствующий величине полупериода задерживаемого сигнала и исключить вентили 2, 4 устройства управляемой задержки импульсов со своими связями.

Блок 4 вычитания кодов предназначен для вычисления кода, соответствующего величине погрешности поверяемого прибора 3, и может быть реализован на логических элементах 155 ИМЗ, 155ЛА36. 155 ЛЕ1 и др.

Блок 5 регистрации содержит дешифратор и цифровые индикаторы. Блок регистрации может представлять собой цифропечатающее устройство или блок сопряжения с ЭВМ.

В качестве генератора б тактовых импульсов может быть применен генератор прямоугольных импульсов, частота которого стабилизирована с помощью кварцевого резонатора.

Реверсивный счетчик 7 импульсов может быть выполнен на микросхемах, например 155 ИЕ7 или 155 ИЕ6.

Дешифратор 8 выдает сигнал для опрокидывания триггера 9 реверса в момент обнуления реверсивного счетчика 7 импульсов и представляет собой многовходной элемент И (И-НЕ),

В качестве триггера 9 реверса используется RS-триггер. .

Управляемый делитель 12 частоты может быть реализован на микросхемах, например, 155 ИЕ8, коэффициент деления которых изменяется по внешним командам управления, вырабатываемым, например, с помощью переключателя.

Синхронный делитель 13 частоты может быть выполнен на микросхемах, например, 155ИЕ5или 155 ИЕ2.

Источник 14 логического сигнала выдает на своем выходе постоянные напряжения с уровнями лог.О или лог.1,

В качестве переключателей 15-17 может быть использован один общий переключатель на N положений и 3 направления.

В качестве переключателя 18 может быть использован переключатель на N положений и одно направление.

Блок 19 вычитания кодов может бытъ реализован на логических элементах 155 ИМЗ, 155 ЛАЗ. 155 ЛЕ и др.

Регистр 20 памяти представляет собой набор D-триггеров, выходы которых также являются выходом блока 20, D-входы - его входом, а тактовые входы объединены и являются входом управления регистра памяти. При этом, код управления не только пропускается на вход цифрового кодоуправ- ляемого фазовращателя 2, но и сохраняется на выходе регистра 20 памяти до прихода следующего импульса с преобразователя 1 частоты.

Цифровой кодоуправляемый фазовращатель 21 выполняется аналогично фазовращателю 2.

Формирователь 22 коротких импульсов обеспечивает обнуление преобразователя 1 частоты, управляемого двигателя 12 частоты и синхронного делителя 13 частоты по сигналу дешифратора 8, появляющемуся в момент обнуления реверсивного счетчика 7. Такая синхронизация делителей 12, 13 и преобразователя 1 частоты между собой исключает возможность фазового рассогласо- вания канала формирования кода управления цифровым кодоуправляемым фазовращателем 2 относительно канала формирования эталонного напряжения на входе фазовращателя 2. Формирователь 22 коротких импульсов также может быть выполнен в виде одновибратора 10.

Фильтры 23, 24 могут быть выполнены в виде активных фильтров нижних частот.

Устройство для поверки цифровых измерителей девиации фазы работает следующим образом.

Генератор 6 тактовых импульсов вырабатывает непрерывную последовательность прямоугольных импульсов (фиг 2. а), которая через преобразователь 1 частоты (фиг. 2, м) поступает на вход цифрового ко- доуправляемого фазовращателя 2, а также через делители 12, 13 и переключатель 16 (фиг. 2, б) - на входы элементов 10 и 11. В зависимости от состояния триггера 9 реверса (фиг. 2, к) эта последовательность подается либо на вход суммирования (фиг. 2, в), либо на вход вычитания (фиг. 2, г) реверсивного счетчика 7 импульсов. Предположим, что на прямом выходе триггера 9 присутствует лог.1 (фиг. 2, к) и реверсивный счетчик 7 работает в режиме сложения. По мере заполнения емкости счетчика 7 на его параллельных выходах (первом - фиг. 2, д. втором - фиг, 2, е, третьем - фиг. 2, ж) последовательно появляются сигналы в виде перепадов уровней напряжения один из которых через переключатель 15 (фиг. 2, и) опрокидывает триггер 9 (фиг 2, к). При этом, лог.1 устанавливается на инверсном

выходе триггера 9 реверса и реверсивный счетчик 7 импульсов начинает работать в режиме вычитания. В момент обнуления счетчика 7 на выходе дешифратора 8 появляется сигнал (фиг. 2, з), снова опрокидывающий триггер 9 (фиг. 2, к) и переводящий реверсивный счетчик 7 в режим сложения. В результате, с помощью реверсивного счетчика 7 импульсов вырабатывается цик0 лическая последовательность кодов управления цифровым кодоуправляемым фазовращателем 2, изменяющихся от нуля до некоторого максимального значения, задаваемого с помощью переключателя 15 и

5 соответствующего заданной величине переменной составляющей фазы сигнала, а затем снова до нуля.

Управляемый делитель 12 частоты предназначен для измерения периода повторе0 ния кода управления, вырабатываемого с помощью реверсивного счетчика 7 импульсов

Синхронный делитель 13 частоты обеспечивает неизменность периода повторе5 ния вырабатываемого кода управления во время изменения оператором величины размаха переменной составляющей сигнала. При этом, с помощью переключателя 16, синхронно с изменением задаваемой вели0 чины переменной составляющей фазы сигнала изменяется коэффициент деления у делителя 13. Так, если величина переменной составляющей фазы сигнала уменьшается, например, в два раза (движок

5 переключателя 15 перемещается влево на одно деление), то коэффициент деления у синхронного делителя 13 частоты должен быть увеличен в два раза (движок переключатель 16 одновременно перемещается

0 вправо на одно деление).

Код управления передается на вход цифрового кодоуправляемого фазовращателя 2 через регистр 20 памяти только по переднему фронту импульсов, поступающих с выхода

5 преобразователя 1 частоты (фиг. 1, н, о, п).

Выходной сигнал с цифрового кодоуправляемого фазовращателя 2 (фиг, 2, р) с циклически изменяющейся в заданных пределах фазой сигнала поступает на вход циф0 рового кодоуправляемого фазовращателя 21, кодом управления, для которого служит выходной сигнал блока 19 вычитания кодов. На выходе блока 19 вычитания кодов формируется результирующий код управления

5 цифровым кодоуправляемым фазовращателем 21, значение которого равно разности постоянной (задаваемой переключателем 18) и половины переменной (задаваемой переключателем 17) составляющих выходного сигнала устройства.

Подача кода, соответствующего половине заданной с помощью переключателей 15 и одновременно 17 величины максимального размаха переменной составляющей фазового сдвига выходного сигнала устройства на второй вход блока 19 вычитания кодов может быть осуществлена путем смещения соединительных связей между вторым входом блока 4 и первым входом блока 19 вычитания кодов на один двоичный разряд. При этом последний, самый старший, (К)-й двоичный разряд второго входа блока 4 объединяется с (К-1)-м двоичным разрядом первого входа блока 19, предпоследний {К-1)-й разряд блока 4 объединяется с(К-2)-м разрядом блока 19 вычитания кодов и т.д.

Выходной сигнал цифрового кодоуправ- ляемого фазовращателя 21 (фиг. 2, с) с циклически изменяющейся фазой подается на клемму фазопеременного канала поверяемого измерителя девиации фазы 3. На кодовом выходе измерителя 3 получается результат измерения величины размаха переменной составляющей фазы сигнала, который поступает на первый вход блока 4 вычитания кодов. На другой вход блока 4 с выхода источника 14 логического сигнала- через переключатель 17 подается код, значение которого соответствует заданной величине размаха переменной составляющей фазы сигнала. Разность между измеренными и действительными значениями величины переменной фазы, соответствующая погрешности поверяемого прибора 3, с выхода блока 4 вычитания кодов поступает в блок 5 регистрации.

С помощью сигнала, появляющегося на выходе формирователя 22 коротких импульсов (фиг. 2, л) в момент полного обнуления реверсивного счетчика 7 импульсов, осуществляется дополнительная синхронизация каналов формирования кода управления (делители 12, 13 частоты и реверсивный счетчик 7) и эталонного сигнала (преобразователь 1 частоты) между собой.

С помощью фильтров 23, 24 формируются синусоидальные сигналы на выходе фазо- задающего устройства. Для подачи на входы поверяемого измерителя девиации фазы синусоидальных сигналов необходимо выход фильтра 23 подключить к клемме фазопеременного канала, а выход фильтра 24 - к клемме опорного канала поверяемого измерителя. Компенсацию разности фазовых набегов в фильтрах 23, 24 можно осуществить при этом путем введения компенсирующего узла задержки в один из каналов устройства, или путем соответствующей коррекции кода.подаваемого от переключателя 18 ко второму входу блока 19 вычитания кода.

Устройство позволяет воспроизводить и какую-нибудь одну (либо постоянную, ли- 5 бо переменную) фазу выходного сигнала. Для этого нужно переключатель 17 или 18 установить в крайнее левое положение. Для того, чтобы (когда переключатель 17 установлен в крайнее левое положение и восп0 роизводится только постоянная фаза выходного сигнала устройства) с выхода реверсивного счетчика 7 на вход регистра 20 памяти надежно подавался нулевой код. можно через крайний левый контакт пере5 ключателя 17 подать соответствующий потенциал на установочный вход реверсивного счетчика 7.

Таким образом, преимущество предлагаемого устройства для поверки цифровых

0 измерителей девиации фазы перед прототипом заключается в том, что благодаря введению регистра памяти и выполнению эталонного генератора в виде преобразователя частоты, вход которого соединен с вы5 ходом генератора тактовых импульсов, за счет синхронизации каналов формирования эталонного сигнала и формирования кода управления цифровым кодоуправляемым фазовращателем, обеспечивается нормаль0 ная работа устройства во всем диапазоне возможных сочетаний одновременно воспроизводимых значений максимального размаха и частоты повторения переменной составляющей фазы выходного сигнала уст5 ройства.

При этом, дополнительная синхронизация каналов формирования эталонного сигнала и кода управления цифровым кодоуправлением фазовращателем между

0 собой с помощью формирователя коротких импульсов позволяет полностью исключить возможность их фазового рассогласования, которое могло бы появляться в результате сбоя любого из делителей частоты.

5Кроме того, благодаря введению дополнительного цифрового кодоуправляемого фазовращателя устраняется нарушение работоспособности (сбой) поверяемых цифровых фазометров при переходе значения

0 воспроизводимого фазового сдвига через О или 360°.

В результате повышается точность воспроизведения максимального размаха переменной составляющей фазового сдвига

5 устройства для поверки цифровых измерителей девиации фазы.

Дополнительным достоинством предлагаемого устройства является возможность использования его для поверки серийных фазометров, типа Ф2-34, измеряющих постоянные фазовые сдвиги, в случае необходимости определения их погрешностей при наличии фазового шума во входных сигналах фазометра Для этого достаточно на второй вход блока 4 вычитание кодов вместо кода, соответствующего размаху переменной составляющей фазового сдвига, с переключателя 17 подать код, соответствующий постоянному фазовому сдвигу, с переключателя 18

Формула изобретения 1. Устройство для поверки цифровых измерителей девиации фазы, содержащее источник эталонного сигнала, выход которого подсоединен к входу основного цифрового кодоуправляемого фазовращателя, а также к клемме опорного сигнала поверяемого измерителя, блок регистрации, выходы которого соединены с соответствующими выходами первого блока вычитания кодов, первые входы которого соединены с соответствующими выходными клеммами поверяемого цифрового измерителя девиации фазы, дешифратор и реверсивный счетчик, у которых соответственно входы и выходы поразрядно соединены, а один из разрядов через первый переключатель подсоединен к второму входу триггера реверса, первый вход которого соединен с выходом дешифратора, прямой выход триггера реверса соединен через первый элемент И с входом суммирования реверсивного счетчика, а инверсный выход - через второй элемент И с входом вычитания реверсивного счетчика, последовательно соединенные генератор тактовых импульсов, управляемый делитель частоты и синхронный делитель частоты, один из выходных разрядов которого через второй переключатель соединен с вторыми входами обоих элементов И, источник логического сигнала выходом соединен через третий переключатель с одним из разрядов второго ехида первого блока вычитания кодов, соединенным в свою очередь с соответствующим разрядом первого входа второго блока вычитания кодов, а также через крайнее положение третьего переключателя - с установочным входом реверсивного счетчика, выход источника логического сигнала соединен через четвертый переключатель с соответствующим разрядом второго входа второго блока вычитания кодов, отличающееся тем, что, с целью повышения

точности воспроизведения максимального размаха переменной составляющей фазового сдвига, в него введены дополнительный цифровой кодоуправляемый фазовращатель, регистр памяти и формирователь коротких импульсов, причем дополнительный цифровой кодоуправляемый фазовращатель соединен входом с выходом основного цифрового кодоуправляемого фазовращателя, выходом - с измерительной

клеммой поверяемого измерителя, входом управления - с выходом второго блока вычитания кодов выходы реверсивного счетчика соединены с соответствующими входами регистра памяти, выходы которого

соединены с соответствующими управляющими входами основного цифрового кодоуправляемого фазовращателя, тактовый вход которого, соединенный с тактовыми входами источника эталонного сигнала и дополнительного цифрового кодоуправляемого фазовращателя, соединены с выходом генератора тактовых импульсов, тактовых вход регистра памяти соединен с выходом источника эталонного сигнала, вход формирователя коротких импульсов соединен с выходом дешифратора, а выход подключен к установочным входам источника эталонного сигнала, управляемого делителя частоты и синхронного делителя частоты.

2. Устройство поп. 1,отличающее- с я тем. что источник эталонного сигнала выполнен в виде синтезатора частоты, содержащего делители или умножители частоты

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых приборов | 1987 |

|

SU1437818A1 |

| Устройство для проверки цифровых приборов | 1988 |

|

SU1599817A2 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| Устройство для поверки цифровых приборов | 1985 |

|

SU1337844A1 |

| Цифровой калибратор девиации частоты | 1985 |

|

SU1250975A1 |

| Автоматическое устройство для поверки стрелочных электроизмерительных приборов | 1985 |

|

SU1320783A1 |

| Устройство для поверки измерителей девиации частоты | 1982 |

|

SU1035531A1 |

| Измерительный преобразователь | 1977 |

|

SU636799A1 |

| Калибратор фазы | 1986 |

|

SU1368804A1 |

| Измеритель комплексных параметров СВЧ-четырехполюсника | 1989 |

|

SU1800394A1 |

Использование: для поверки цифровых измерителей девиации фазы, имеющих выходные кодовые сигналы, соответствующие результатам измерения. Сущность изобретения: с целью повышения точности воспроизведения максимального размаха переменной составляющей фазового сдвига в устройство для поверки цифровых измерителей девиации фазы, содержащее источник эталонного сигнала, цифровой кодоупрэв- ляемый фазовращатель, клеммы для подключения поверяемого прибора, первый блок вычитания кодов, блок регистрации, генератор тактовых импульсов, реверсивный счетчик, дешифратор, триггер реверса, первый и второй элементы И, управляемый делитель частоты, синхронный делитель частоты, источник логического сигнала, четыре переключателя, второй блок вычитания кодов, введены регистр памяти, дополнительный цифровой кодоуправляемый фазов- ращатель, формирователь коротких импульсов, введенные блоки и соответствующие связи обеспечивают взаимную синхронизацию работы всех блоков, задающих модулированный по фазе сигнал с заданной величиной девиации фазы. 1 з.п.ф-лы, 2 ил. (Л С

| Устройство для поверки цифровых приборов | 1985 |

|

SU1337844A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для поверки цифровых приборов | 1987 |

|

SU1437818A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-15—Публикация

1990-02-28—Подача