ел i

СЛ

СО

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения задач на графах | 1988 |

|

SU1658171A1 |

| Устройство для исследования параметров графа | 1988 |

|

SU1683036A1 |

| Устройство для решения задач на графах | 1989 |

|

SU1658172A1 |

| Устройство для решения задач на графах | 1988 |

|

SU1587534A1 |

| Устройство для решения задач на графах | 1990 |

|

SU1837314A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НА ГРАФАХ | 1996 |

|

RU2100838C1 |

| Устройство для анализа параметров графа | 1988 |

|

SU1683034A1 |

| Устройство для раскраски графов | 1988 |

|

SU1645970A1 |

| Устройство для решения задач на графах | 1989 |

|

SU1626256A1 |

| Устройство для анализа параметров графа | 1986 |

|

SU1532942A1 |

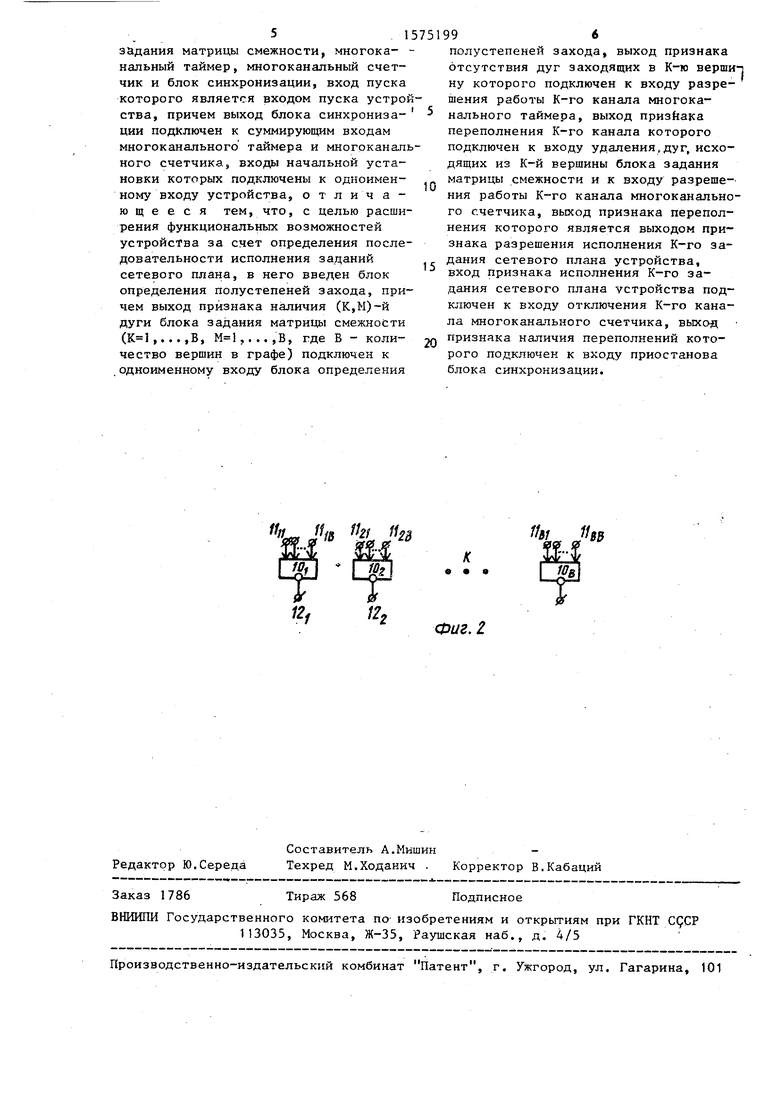

Изобретение относится к вычислительной технике и может быть использовано для распределения заданий процессорам вычислительной системы. Целью изобретения является расширение функциональных возможностей устройства за счет определения последовательности исполнения заданий сетевого плана. Устройство содержит блок 1 задания матрицы смежности, блок 2 определения полустепеней захода, многоканальный таймер 3, блок 4 синхронизации, многоканальный счетчик 5, вход 6 начальной установки устройства, вход 7 пуска, выходы 8 признаков разрешения исполнения заданий сетевого плана устройства и выходы 9 признаков исполнения заданий сетевого плана устройства. Перед началом работы обнуляют счетчик 5, в блок 1 заносят информацию о топологии сетевого графика, каналы многоканального таймера 3 загружают кодами, дополняющими веса вершин сетевого графика до полной емкости каналов. После запуска блок 4 синхронизации формирует последовательность тактовых импульсов. При этом таймер 3 моделирует исполнение заданий сетевого плана, а счетчик 5 определяет последовательность распределения заданий на исполнителей. 2 ил.

Фиг.1

Изобретение относится к вычислительной технике и может быть использ рано для распределения заданий процессором вычислительной системы, Целью изобретения является расширение функциональных возможностей устройства за счет определения последовательности исполнения заданий се- тевого плана.

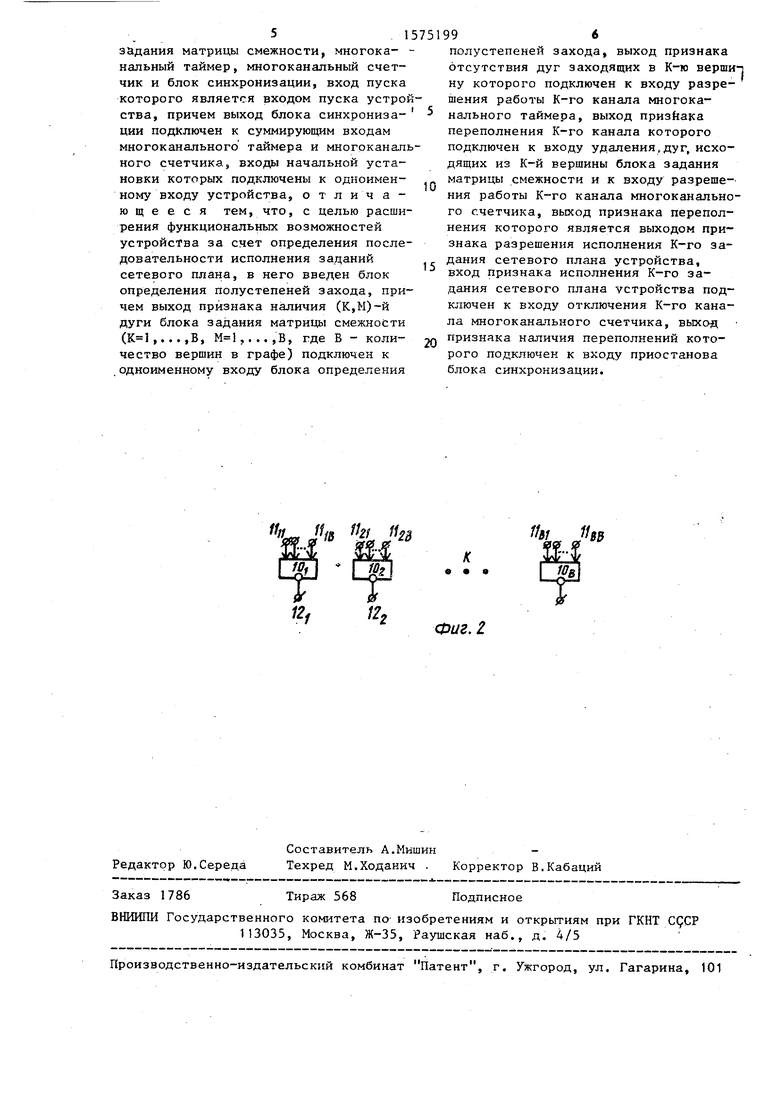

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока определения полустепеней захода. I Устройство содержит блок I зада- |ния матрицы смежности, блок 2 опреде рения полустепеней захода, многоканальный таймер 3, блок 4 синхрониза- Щии, многоканальный счетчик 5, вход начальной установки устройства, |вход 7 пуска, выходы 8 признаков разрешения исполнения заданий сетевого плана устройства, входы 9 признаков исполнения заданий сетевого плана устройства.

Блок 2 определения полустепеней захода содержит группу из В элементов ИЛИ-НЕ 10, причем вход 11 признака наличия (К,М)-й дуги блока 2 (,...,В, ,...,В, где В - количество вершин в графе) подключен к М-му входу Кто элемента ИЛИ-НЕ 10 группы, выход которого является выходом 12 признака отсутствия дуг,заходящих в К-ю вершину.

Устройство работает следующим образом.

Перед началом работы на вход 6 начальной установки устройства подают импульсный сигнал уровня 1. При этом каналы многоканального счетчика 5 обнуляются, выходы признаков переполнения всех каналов подключаются к выходам 8 устройства, обнуляются каналы и признаки их переполнения многоканального таймера З.В блок 1 задания матрицы смежности заносят информацию о топологии сетевог графика. Каналы многоканального таймера 3, номера которшс соответствуют номерам вершин (заданий) сетевого плана, загружают информацией, дополняющей код веса вершины до полной емкости канала (времени исполнения заданий). Цепи загрузки канала таймера 3 на фиг.1 не показаны. На вход 7 пуска устройства подают импульс уровня 1, при этом блок 4 синхронизации формирует последозатель0

5

0

5

0

5

0

5

0

ность тактовых импульсов уровня 1. Блок 2 определения полустепеней захода определяет вершины с нулевой полустепенью захода и разрешает их моделирование в каналах таймера 3. После того, как любой из каналов таймера переполниться (моделирование исполнения задания окончено) на соответствующем ему выходе признака переполнения появляется потенциал уровня 1. При этом блок 1 задания матрицы смежности исключает из топочогии сетевого графика все дуги, исходящие из вершины, моделирование которой окончено и блок 2 определения полустепеней захода разрешает моделирование очередных вершин сетевого графика. Одновременно потенциал с выхода признака переполнения канала таймера разрешает работу соответствующего ему канала счетчика 5. Таким образом, в процессе работы в каналы счетчика 5 будет записана информация о времени, которое прошло с момента окончания моделирования соответствующей каналу вершины сетевого графика. При поступлении на суммирующий вход счетчика 5 тактовых импульсов его каналы переполняются в последовательности, соответствующей последовательности моделирования вершин. При этом ка выходе признака наличия переполнрний и одном из выходов 8 устройства появляется потенциал уровня 1. При этом блок 4 синхронизации приостанавливает формирование тактовых импульсов. После того как задания сетевого плана, определенные потенциалами уровня 1 на выходах 8 устройства выполнены, на соответствующие им входы 9 устройства подают сигналы уровня 1. При этом счетчик 5 отключает соответствующие каналы счетчика 5 от выхода признака наличия переполнений и выходов признаков переполнения каналов. При этом счетчик 5 снимает сигнал уровня 1 с выхода признака наличия переполнений. При этом блок 4 синхронизации продолжает выработку тактовых импульсов. Работа устройства продолжается аналогично до тех пор, пока не будут выполнены все задания сетевого плана.

Формула изобретения

Устройство для решения задач сетевого планирования, содержащее блок

515

задания матрицы смежности, многока- - нальный таймер, многоканальный счетчик и блок синхронизации, вход пуска которого является входом пуска устройства, причем выход блока синхрониза- ции подключен к суммирующим входам многоканального таймера и многоканального счетчикаs входы начальной установки которых подключены к одноименному входу устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет определения последовательности исполнения заданий сетевого плана, в него введен блок определения полустепеней захода, причем выход признака наличия (К,М)-й дуги блока задания матрицы смежности (,...,В, ,...,В, где В - количество вершин в графе) подключен к одноименному входу блока определения

u A %,%

996

полустепеней захода, выход признака отсутствия дуг заходящих в К-ю верши-; ну которого подключен к входу разрешения работы К-го канала многоканального таймера, выход признака переполнения К-го канала которого подключен к входу удаления,дуг, исходящих из К-й вершины блока задания матрицы смежности и к входу разрешения работы К-го канала многоканального счетчика, выход признака переполнения которого является выходом признака разрешения исполнения К-го задания сетевого плана устройства, вход признака исполнения К-го задания сетевого плана устройства подключен к входу отключения К-го канала многоканального счетчика, выход признака наличия переполнений которого подключен к входу приостанова блока синхронизации.

и/ j/w

к

о

Фиг. Z

| Авторское свидетельство СССР № 877553, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для оптимизации плана перевозок в транспортной сети | 1987 |

|

SU1474668A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-05-06—Подача