10

11

fe

ч

k

S4 00

СА О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU960916A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339628A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1425770A2 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Устройство для считывания цветной графической информации | 1989 |

|

SU1695339A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1354243A1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Устройство для отображения алфавитно-цифровой информации на экране телевизионного индикатора | 1986 |

|

SU1410093A1 |

| Устройство для отображения информации | 1978 |

|

SU736144A1 |

Изобретение относится к технике отображения информации и может быть использовано при построении многофункциональных станций индикации графических данных. Целью изобретения является повышение качества отображения информации за счет повышения линейности развертывающих функций. Поставленная цель достигается тем, что в устройство, содержащее первый дискретизатор 1, два вычислительных блока 2, 3, два блока 4, 5 памяти, введены два блока 6, 7 динамической коррекции и второй дискретизатор 8 с соответствующими связями, что позволяет повысить точность вычисления отдельных составляющих развертывающих цифровых функций. 1 з.п. ф-лы, 5 ил.

Ф ие. 1

Изобретение относится к технике отображения информации и может быть использовано при построении многофункциональных станций индикации графических данных.

Целью изобретения является повышение качества отображения информации за счет повышения линейности развертывающих функций.

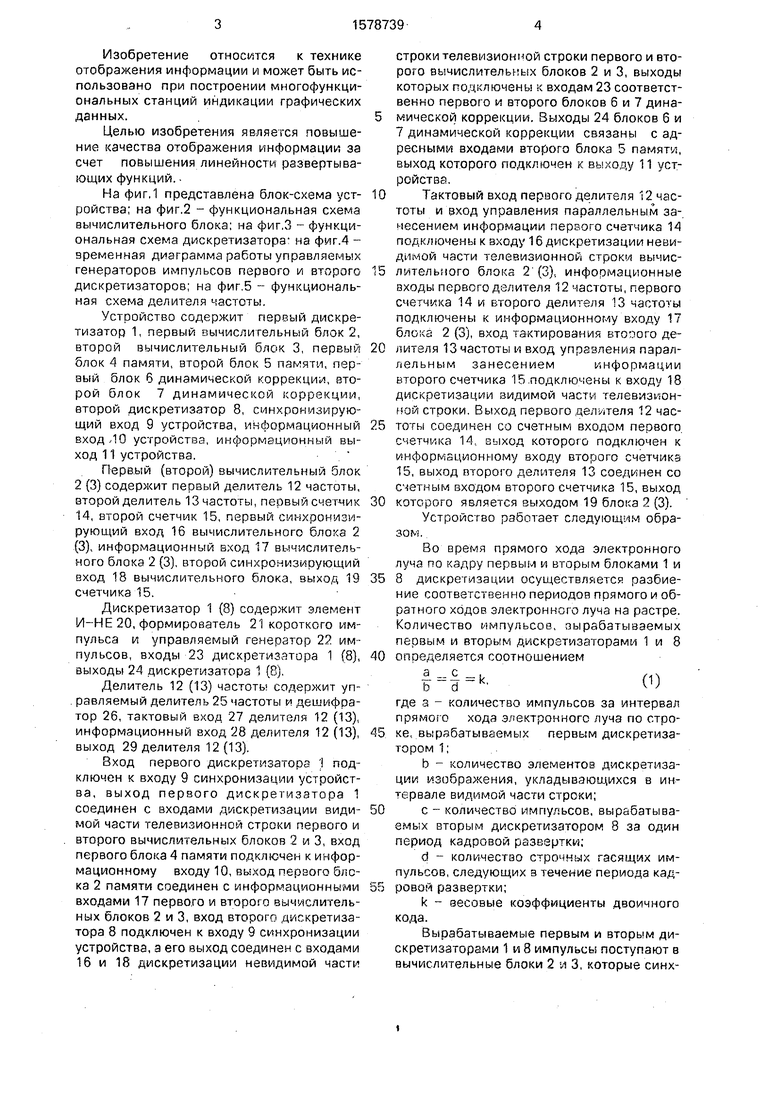

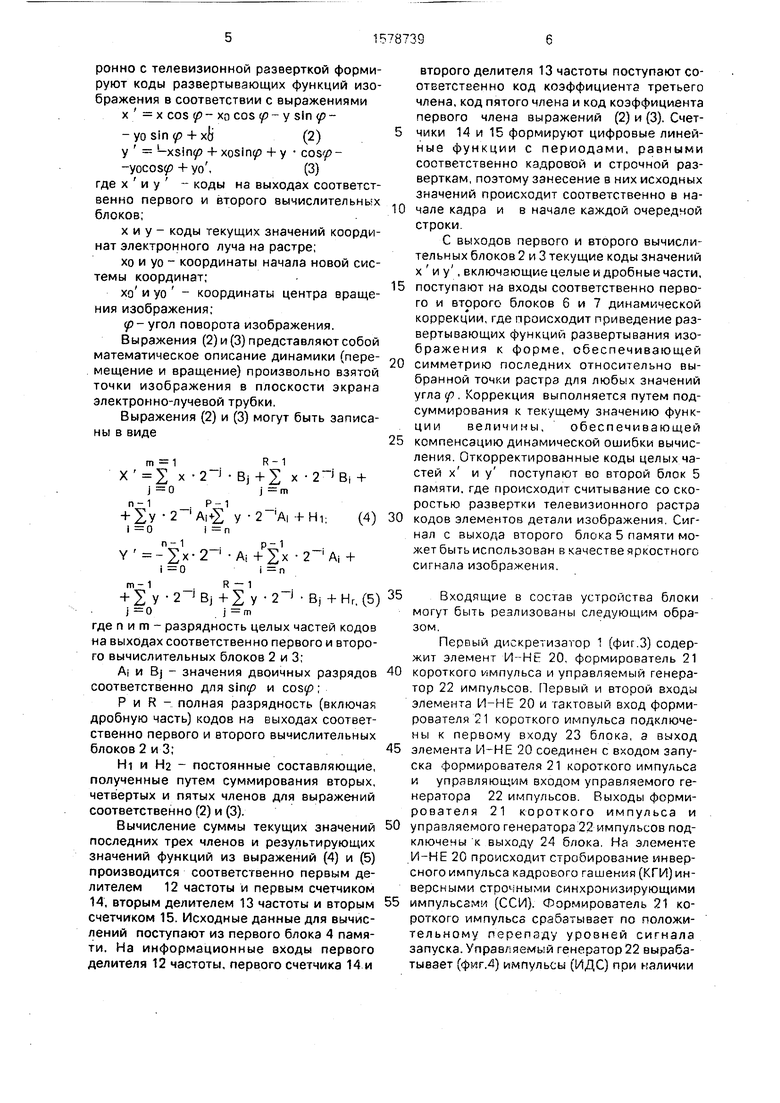

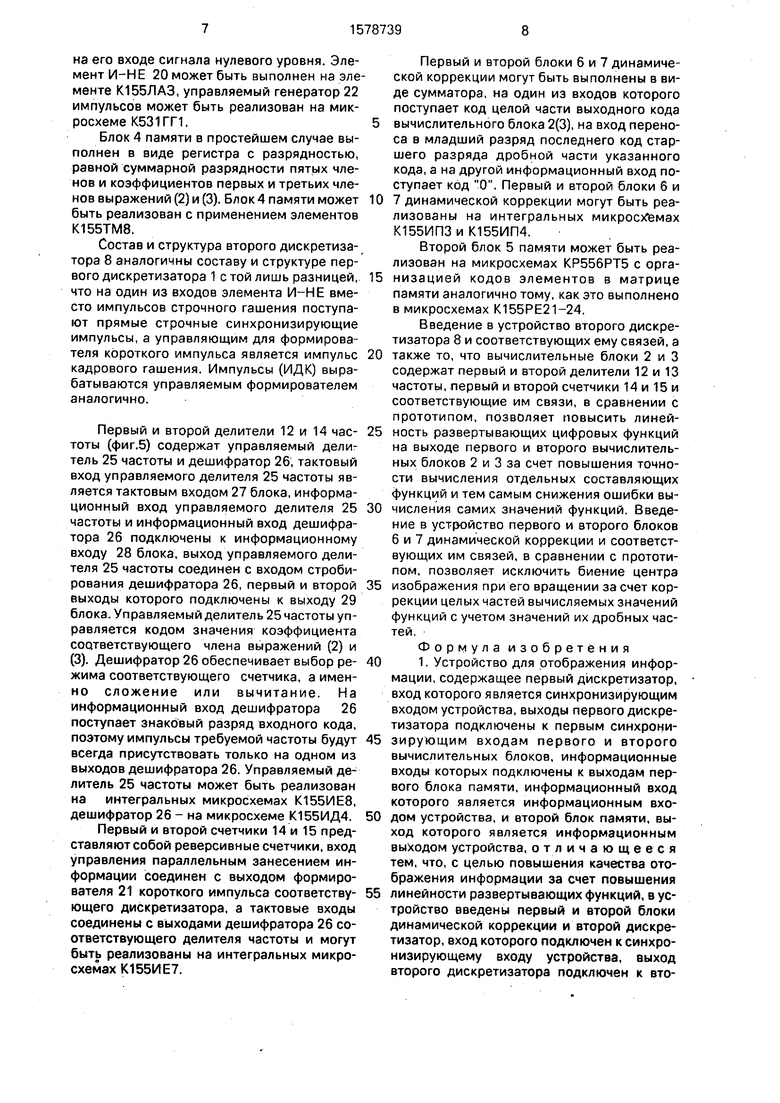

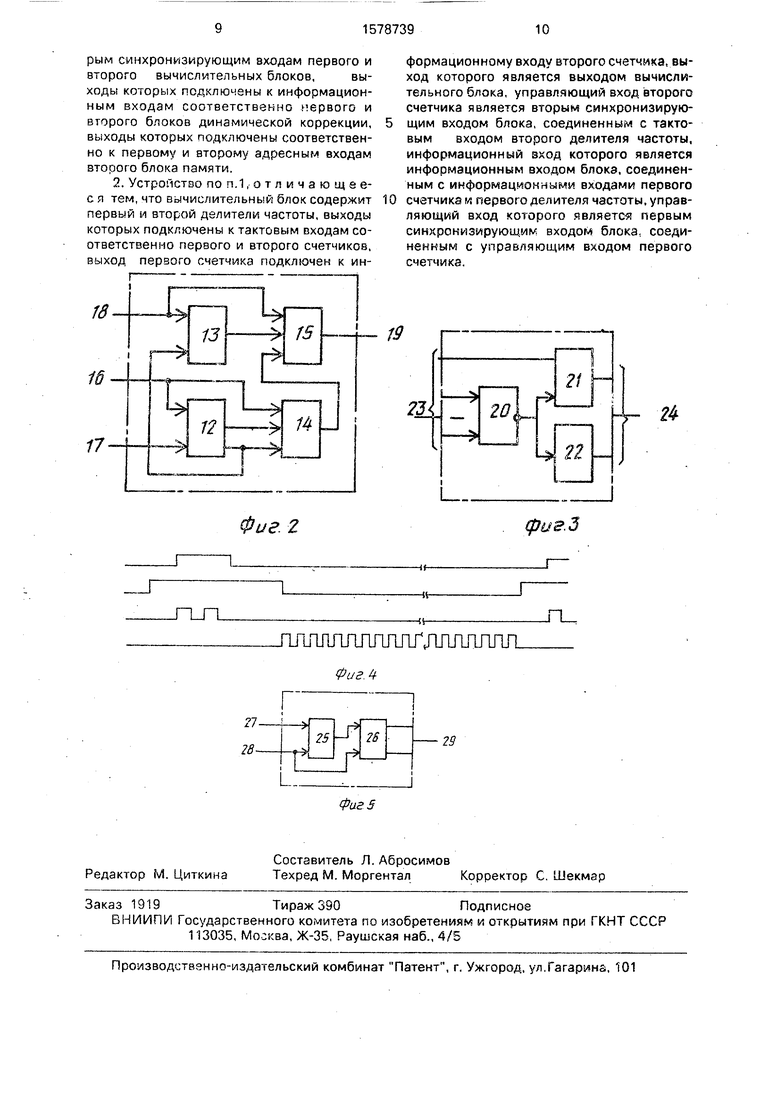

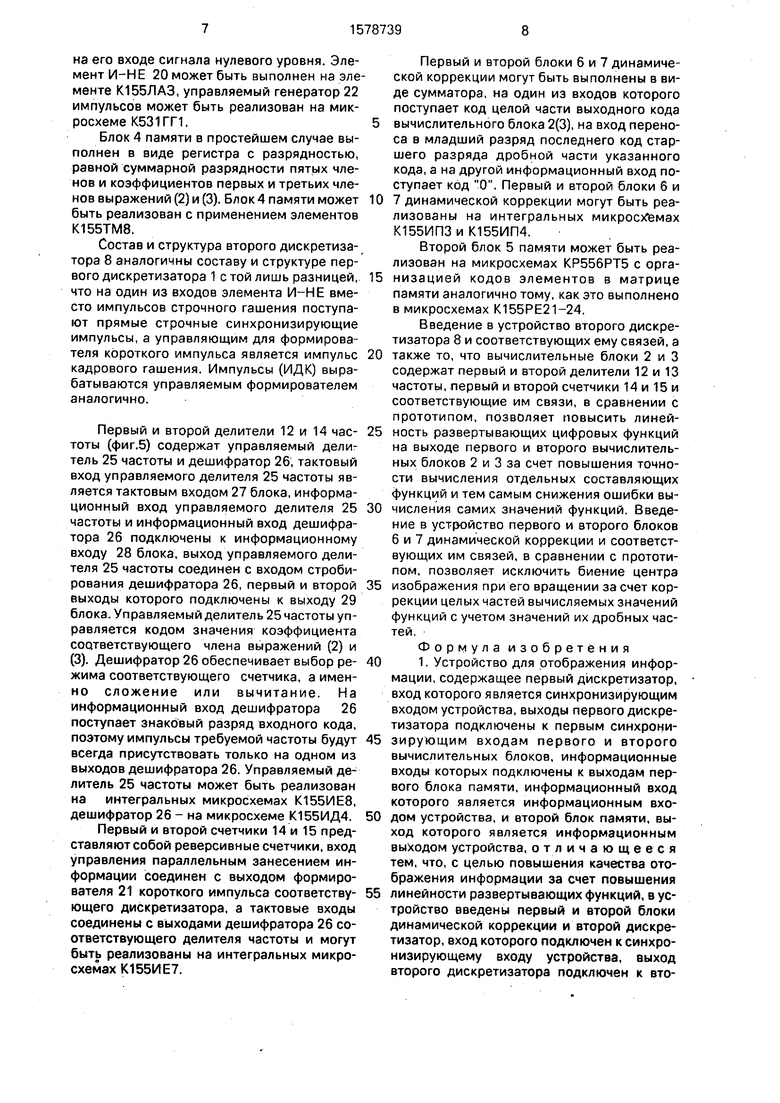

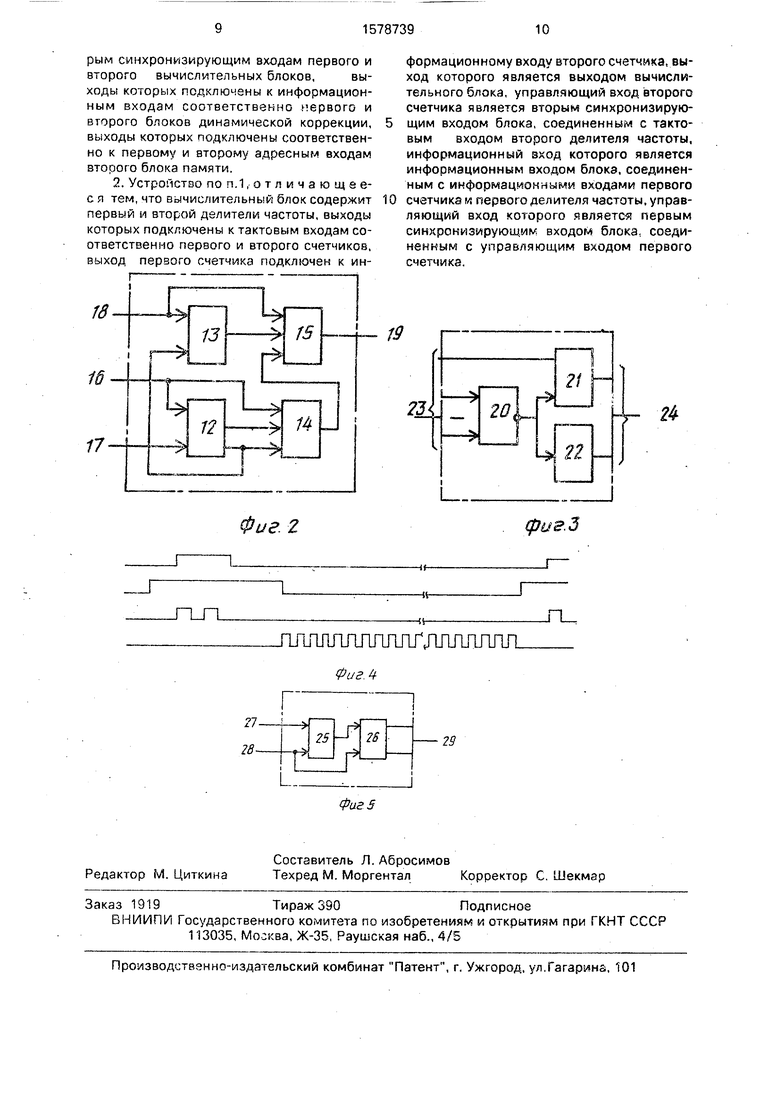

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема вычислительного блока; на фиг.З - функциональная схема дискретизатора на фиг.4 - временная диаграмма работы управляемых генераторов импульсов первого и второго дискретизаторов; на фиг,5 - функциональная схема делителя частоты.

Устройство содержит первый дискре- тизатор 1, первый вычислительный блок 2, второй вычислительный блок 3, первый блок 4 памяти, второй блок 5 памяти, пер- аый блок 6 динамической коррекции, второй блок 7 динамической коррекции, второй дискретизатор 8, синхронизирующий вход 9 устройства, информационный входИО устройства, информационный выход 11 устройства.

Первый (второй) вычислительный блок 2 (3) содержит первый делитель 12 частоты, второй делитель 13 частоты, первый счетчик 14, второй счетчик 15, первый синхронизирующий вход 16 вычислительного блока 2 (3), информационный вход 17 вычислительного блока 2 (3), второй синхронизирующий вход 18 вычислительного блока, выход 19 счетчика 15.

Дискретизатор 1 (8) содержит элемент И-НЕ 20, формирователь 21 короткого импульса и управляемый генератор 22 импульсов, входы 23 дискретизэтора 1 (8), выходы 24 дискретизатора 1 {8.

Делитель 12 (13) частоты содержит управляемый делитель 25 частоты и дешифратор 26, тактовый вход. 27 делителя 12 (13), информационный вход 28 делителя 12 (13), выход 29 делителя 12(13).

Вход первого дискретизатора 1 подключен к входу 9 синхронизации устройства, выход первого дискретизатора 1 соединен с входами дискретизации видимой части телевизионной строки первого и второго вычислительных блоков 2 и 3, вход первого блока 4 памяти подключен к информационному входу 10, выход первого блока 2 памяти соединен с информационными входами 17 первого и второго вычислительных блоков 2 и 3, вход второго дискретизатора 8 подключен к входу 9 синхронизации устройства, а его выход соединен с входами 16 и 18 дискретизации невидимой части

строки телевизионной строки первого и второго вычислительных блоков 2 и 3, выходы которых подключены к входам 23 соответственно первого и второго блоков 6 и 7 динамической коррекции. Выходы 24 блоков 6 и 7 динамической коррекции связаны с адресными входами второго блока 5 памяти, выход которого подключен к выходу 11 устройства.

Тактовый вход первого делителя 12 частоты и вход управления параллельным за-, несением информации первого счетчика 14 подключены к входу 16 дискретизации невидимой части телевизионной строки вычислительпого блока 2(3), информационные входы первого делителя 12 частоты, первого счегчика 14 и второго делителя 13 частоты подключены к информационному входу 17 блока 2 (3), вход тактирования второго делителя 13 частоты и вход управления параллельным занесениеминформации второго счетчика 15 подключены к входу 18 дискретизации видимой части телевизионной строки. Выход первого целителя 12 частоты соединен со счетным входом первого счетчика 14. выход которого подключен к информационному входу второго счетчика 15, выход второго делителя 13 соединен со счетным входом второго счетчика 15, выход

которого является выходом 19 блока 2 (3).

Устройство работает следующим образом.

Во время прямого хода электронного пуча по кадру первым и вторым блоками 1 и

8 дискретизации осуществляется разбиение соответственно периодов прямого и обратного ходов электронного луча на растре. Количество импульсов, аырабатываемых первым и вторым дискретизаторами 1 и 8

определяется соотношением

а - с - ь

-- - |

b d

0)

где а - количество импульсов за интервал прямого хода электронного луча по стро- ке, вырабатываемых первым дискретиза- тором 1;

b - количество элементов дискретизации изображения, укладывающихся в интервале видимой части строки; с количество импульсов, вырабатываемых вторым дискретизатором 8 за один период кадровой развертки;

d - количество строчных гасящих импульсов, следующих э течение периода кад- ровой развертки;

k - аесовые коэффициенты двоичного кода.

Вырабатываемые первым и вторым ди- скретизаторами 1 и 8 импульсы поступают в вычислительные блоки 2 и 3, которые синхронно с телевизионной разверткой формируют коды развертывающих функций изображения в соответствии с выражениями х х cos (р - хо cos (р - у sin р - уо sin p + xjj(2)

у - xsin 4- xosin J + у cos / -yocosЈ + уо ,(3)

где х и у - коды на выходах соответственно первого и второго вычислительных блоков;

х и у - коды текущих значений координат электронного луча на растре;

хо и уо - координаты начала новой системы координат;

хо и уо - координаты центра вращения изображения;

р- угол поворота изображения.

Выражения (2) и (3) представляют собой математическое описание динамики (пере- мещение и вращение) произвольно взятой точки изображения в плоскости экрана электронно-лучевой трубки.

Выражения (2) и (3) могут быть записаны в виде

R-1

Bj + 2 2 j Bi +

j m

m - 1

j o

+ПЈу у -2 +Hi: i 0i n

n-1p-1

,+

(4)

i 0i n

m - 1R - 1

+ 2 У -2 jBj+2y -Bj+Hr,(5) j 0j m

где пит- разрядность целых частей кодов на выходах соответственно первого и второго вычислительных блоков 2 и 3;

AI и В) - значения двоичных разрядов соответственно для и cosip ;

Р и R - полная разрядность (включай дробную часть) кодов на выходах соответственно первого и второго вычислительных блоков 2 и 3;

Hi и На - постоянные составляющие, полученные путем суммирования вторых, четвертых и пятых членов для выражений соответственно (2) и (3).

Вычисление суммы текущих значений последних трех членов и результирующих значений функций из выражений (4) и (5) производится соответственно первым делителем 12 частоты и первым счетчиком 14, вторым делителем 13 частоты и вторым счетчиком 15. Исходные данные для вычислений поступают из первого блока 4 памяти. На информационные входы первого делителя 12 частоты, первого счетчика 14 и

5

1Г.

™

25

30

35

40

45

50 55

второго делителя 13 частоты поступают соответственно код коэффициента третьего члена, код пятого члена и код коэффициента первого члена выражений (2) и (3). Счетчики 14 и 15 формируют цифровые линейные функции с периодами, равными соответственно кадровой и строчной разверткам, поэтому занесение в них исходных значений происходит соответственно в начале кадра и в начале каждой очередной строки.

С выходов первого и второго вычислительных блоков 2 и 3 текущие коды значений х и у , включающие целые и дробные части, поступают на входы соответственно первого и второго блоков 6 и 7 динамической коррекции, где происходит приведение развертывающих функций развертывания изображения к форме, обеспечивающей симметрию последних относительно выбранной точки растра для любых значений угла (р , Коррекция выполняется путем под- суммирования к текущему значению функции величины, обеспечивающей компенсацию динамической ошибки вычисления. Откорректированные коды целых частей х и у поступают во второй блок 5 памяти, где происходит считывание со скоростью развертки телевизионного растра кодов элементов детали изображения. Сигнал с выхода второго блока 5 памяти может быть использован в качестве яркостного сигнала изображения.

Входящие в состав устройства блоки могут быть реализованы следующим образом.

Первый дискретизатор 1 (фиг.З) содержит элемент И-НЕ 20, формирователь 21 короткого импульса и управляемый генератор 22 импульсов. Первый и второй входы элемента И-НЕ 20 и тактовый вход формирователя 21 короткого импульса подключены к первому входу 23 блока, а выход элемента И-НЕ 20 соединен с входом запуска формирователя 21 короткого импульса и управляющим входом управляемого генератора 22 импульсов. Выходы формирователя 21 короткого импульса и управляемого генератора 22 импульсов подключены к выходу 24 блока. На элементе И-НЕ 20 происходит стробирование инверсного импульса кадрового гашения (КГИ) инверсными строчными синхронизирующими импульсами (ССИ). Формирователь 21 короткого импульсз срабатывает по положительному перепаду уровней сигнала запуска. Управляемый генератор 22 вырабатывает (фиг.4) импульсы (НДС) при наличии

на его входе сигнала нулевого уровня. Элемент И-НЕ 20 может быть выполнен на элементе К155ЛАЗ, управляемый генератор 22 импульсов может быть реализован на микросхеме К531ГГ1.

Блок 4 памяти в простейшем случае выполнен в виде регистра с разрядностью, равной суммарной разрядности пятых членов и коэффициентов первых и третьих членов выражений (2) и (3). Блок 4 памяти может быть реализован с применением элементов К155ТМ8.

Состав и структура второго дискретиза- тора 8 аналогичны составу и структуре первого дискретизатора 1 с той лишь разницей, что на один из входов элемента И-НЕ вместо импульсов строчного гашения поступают прямые строчные синхронизирующие импульсы, а управляющим для формирователя короткого импульса является импульс кадрового гашения. Импульсы (ИДК) вырабатываются управляемым формирователем аналогично.

Первый и второй делители 12 и 14 частоты (фиг.5) содержат управляемый делитель 25 частоты и дешифратор 26, тактовый вход управляемого делителя 25 частоты является тактовым входом 27 блока, информационный вход управляемого делителя 25 частоты и информационный вход дешифратора 26 подключены к информационному входу 28 блока, выход управляемого делителя 25 частоты соединен с входом строби- рования дешифратора 26, первый и второй выходы которого подключены к выходу 29 блока. Управляемый делитель 25 частоты управляется кодом значения коэффициента соответствующего члена выражений (2) и (3). Дешифратор 26 обеспечивает выбор режима соответствующего счетчика, а именно сложение или вычитание. На информационный вход дешифратора 26 поступает знаковый разряд входного кода, поэтому импульсы требуемой частоты будут всегда присутствовать только на одном из выходов дешифратора 26. Управляемый делитель 25 частоты может быть реализован на интегральных микросхемах К155ИЕ8, дешифратор 26 - на микросхеме К155ИД4.

Первый и второй счетчики 14 и 15 представляют собой реверсивные счетчики, вход управления параллельным занесением информации соединен с выходом формирователя 21 короткого импульса соответствующего дискретизатора, а тактовые входы соединены с выходами дешифратора 26 соответствующего делителя частоты и могут быть реализованы на интегральных микросхемах К155ИЕ7.

Первый и второй блоки 6 и 7 динамической коррекции могут быть выполнены в виде сумматора, на один из входов которого поступает код целой части выходного кода

вычислительного блока 2(3), на вход переноса в младший разряд последнего код старшего разряда дробной части указанного кода, а на другой информационный вход поступает код О. Первый и второй блоки 6 и

0 7 динамической коррекции могут быть реализованы на интегральных микросхемах К155ИПЗ и К155ИП4.

Второй блок 5 памяти может быть реализован на микросхемах КР556РТ5 с орга5 низацией кодов элементов в матрице памяти аналогично тому, как это выполнено в микросхемах К155РЕ21-24.

Введение в устройство второго дискретизатора 8 и соответствующих ему связей, а

0 также то, что вычислительные блоки 2 и 3 содержат первый и второй делители 12 и 13 частоты, первый и второй счетчики 14 и 15 и соответствующие им связи, в сравнении с прототипом, позволяет повысить линей5 ность развертывающих цифровых функций на выходе первого и второго вычислительных блоков 2 и 3 за счет повышения точности вычисления отдельных составляющих функций и тем самым снижения ошибки вы0 числения самих значений функций. Введение в устройство первого и второго блоков 6 и 7 динамической коррекции и соответствующих им связей, в сравнении с прототипом, позволяет исключить биение центра

5 изображения при его вращении за счет коррекции целых частей вычисляемых значений функций с учетом значений их дробных частей.

Формула изобретения

0 1. Устройство для отображения информации, содержащее первый дискретизатор, вход которого является синхронизирующим входом устройства, выходы первого дискретизатора подключены к первым синхрони5 зирующим входам первого и второго вычислительных блоков, информационные входы которых подключены к выходам первого блока памяти, информационный вход которого является информационным вхо0 дом устройства, и второй блок памяти, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения качества отображения информации за счет повышения

5 линейности развертывающих функций, в устройство введены первый и второй блоки динамической коррекции и второй дискретизатор, вход которого подключен к синхронизирующему входу устройства, выход второго дискретизатора подключен к вторым синхронизирующим входам первого и второго вычислительных блоков, выходы которых подключены к информационным входам соответственно первого и второго блоков динамической коррекции, выходы которых подключены соответственно к первому и второму адресным входам второго блока памяти.

.

11гичляг1Ш1ллглл ъг1паа

Фиг 4

Г

21 28L:

формационному входу второго счетчмка, выход которого является выходом вычислительного блока, управляющий вход второго счетчика является вторым синхронизирующим входом блока, соединенным с тактовым входом второго делителя частоты, информационный вход которого является информационным входом блока, соединенным с информационными, входами первого

счэтчика и первого делителя частоты, управляющий вход которого является первым синхронизирующие входом блока, соединенным с управляющим входом первого счетчика.

19 г-

23

24

22

I

фи&.З

23

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1981 |

|

SU1007118A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU960916A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-07-15—Публикация

1987-03-17—Подача