Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано для снижения потребляемой мощности в динамических запоминающих устройствах.

Известно динамическое запоминающее устройство, содержащее накопитель информации, управляющие входы которого подключены к выходам блока управления, адресные входы - к выходам дещифраторов, а информационные входы - к информационным щинам, при этом входы дещифраторов соединены с выходами коммутаторов, одни входы которых подключены к выходам адресного счетчика регенерации, вторые входы соединены с адресными щинами, а управляющие входы коммутаторов связаны с выходами блока управления 1.

Недостатками данного устройства являются невысокая помехоустойчивость и пониженная надежность работы вследствие осуществления регенерации последовательно по всем БИС ЗУ строка за строкой в соответствии с текущими значениями счетчика адресов регенерации.

Наиболее близким к изобретению по технической сущности и достигаемому результату является динамическое запоминающее устройство, содержащее блок управления, входы которого являются управляющими входами устройства, а выходы соединены с входами соответственно накопителя и первого, второго и третьего формирователей, первый коммутатор, первый и второй управляющие входы которого подключены к выходам соответственно второго и третьего формирователей, второй и третий коммутаторы, управляющие входы которых соединены со счетным входом счетчика, первый и второй дещифраторы, входы которых соединены с соответствующими выходами счетчика, причем входы первой группы первого и второго коммутаторов подключены к выходу соответствующего дещифратора, входы первой группы третьего коммутатора соединены с соответствующими выходами счетчика, третий и четвертый дешифраторы, выходы которых соединены с входами второй группы соответственно первого и второго коммутаторов, а входы являются соответствующими адресными входами устройства, одни из адресных входов накопителя соединены с выходами коммутаторов, а другие являются адресньши входами устройства 2.

Недостатком известного устройства является больщое потребление мощности из-за непрерывной работы схем регенерации в течение всего периода времени работы запоминающего устройства.

Цель изобретения - уменьшение потребляемой мощности устройства.

Поставленная цель достигается тем, что в динамическое запоминающее устройство, содержащее блок управления, входы которого являются управляющими входами устройства, а выходы соединены с входами соответственно накопителя и первого, второго и третьего формирователей, первый коммутатор, первый и второй управляющие входы которого подключены к выходам соответственно второго и третьего формирователей, второй и третий коммутаторы, управляющие входы которых соединены со счетным входом счетчика, первый и второй дещифраторы, входы которых соединены с соответствующими выходами счетчика, причем входы первой группы первого и второго коммутаторов подключены к выходу соответствующего дещифратора, входы первой группы третьего коммутатора соединены с соответствующими выходами счетчика, третий и четвертый дещифраторы, выходы которых соединены с входами второй группы соответственно первого и второго коммутаторов, а входы являются соответствующими адресными входами устройства, одни из адресных входов накопителя соединены с выходами коммутаторов, а другие являются адресными входами устройства, дополнительно введены делитель частоты, триггер, дополнительный формирователь, элементы И, ИЛИ, причем счетный вход делителя частоты соединен с одним из входов блока управления, а установочный вход соединен с установочным входом счетчика, одним из входов элемента ИЛИ и является установочным входом устройства, выход делителя частоты соединен с другим входом элемента ИЛИ, выход которого соединен с одним установочным входом триггера, один из выходов которого соединен с одним из входов первого элемента И, один выход которого соединен со счетным входом счетчика, а другой - с выходом первого формирователя, другой установочный вход триггера соединен с выходом дополнительного формирователя, вход которого соединен с выходом второго элемента И, входы которого соединены с соответствующими выходами счетчика.

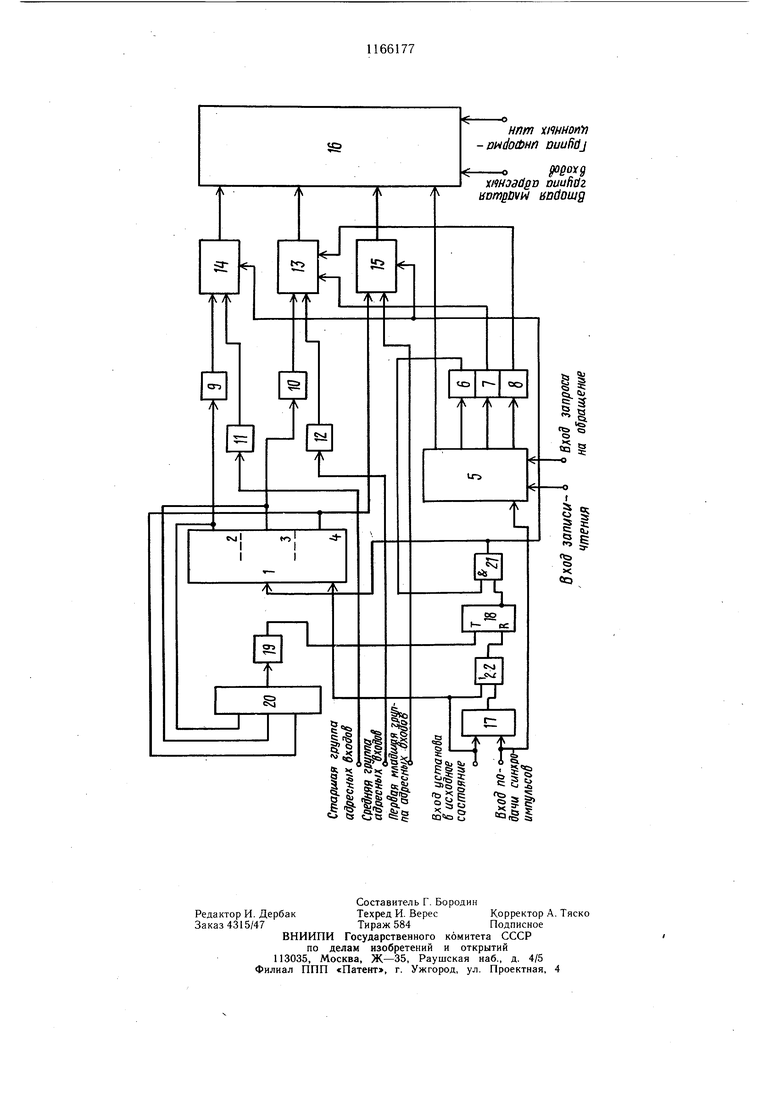

На чертеже приведена структурная схема предлагаемого устройства.

Динамическое запоминающее устройство содержит счетчик 1 адресов регенерации, состоящий из младщей 2, средней 3 и старшей 4 групп разрядов, блок 5 управления (ТЭЗ управления, ЕС-3267.075). Первый 6, второй 7 и третий. 8 формирователи, первый 9, второй 10, третий Ни четвертый 12 дешифраторы, первый 13, второй 14 и третий 15 коммутаторы, накопитель 16, делитель 17 частоты, триггер 18, дополнительный формирователь 19, первый 20 и второй 21 элементы И и элемент ИЛИ 22. Накопитель 16 состоит из матриц и модулей на микросхемах БИС ЗУ.

Устройство может работать в двух режимах: ОБРАЩЕНИЕ и РЕГЕНЕРАЦИЯ.

В режиме ОБРАЩЕНИЕ сигнал записи или чтения поступает на вход записи-чтения устройства, сигнал запроса на обращение - на вход запроса на обращение устройства, а адрес - на первую и вторую младшие, среднюю и старщую группы адресных входов устройства. При этом во время записи на группу информационных входов устройства поступает информация для записи в

накопителе 16, а во время считывания на

,

информационные входы устройства поступает информация из накопителя 16.

Работа устройства в режимах ОБРАЩЕНИЕ и РЕГЕНЕРАЦИЯ синхронизируется с помощью синхроимпульсов, поступающих на соответствующий вход устройства. Всё управляющие сигналы поступают с входов устройства на первый, второй и третий входы блока 5 управления, который формирует в режиме ОБРАЩЕНИЕ сигнал записи или считывания на управляющем входе накопителя 16 и запускает второй формирователь 7, открывающий по первому управляющему входу первый коммутатор 13, для пропускания информации с второй группы входов.

Вторая младщая группа адреса записи или считывания какого-либо числа поступает непосредственно на первую группу управляющих входов накопителя 16, связанных с адресами столбцов микросхем БИС ЗУ. Первая младшая группа адреса записи или считывания поступает на вторую группу входов третьего коммутатора 15, по выходам соединенного с второй группой управл.яющих входов-накопителя 16, связанных с адресами строк микросхем БИС ЗУ. Средняя группа адреса записи или считывания поступает на вторую группу входов первого коммутатора 13 через четвертый дешифратор 12, по выходам соединенного с третьей группой управляющих входов накопителя 16, связанных с адресами выбора строки матрицы модуля памяти. Старшая группа адреса записи или считывания поступает через третий дешифратор 11 на вторую группу входов второго коммутатора 14, по выходам соединенного с четвертой группой управляю щих входов накопителя 16, связанных с адресами выбора строки матрицы накопителя информации. При этом на управляющие входы второго 14 и третьего 15 коммутаторов с выхода второго элемента И 21, закрытого в этот период времени по второму входу от первого формирователя 6, в режиме ОБРАЩЕНИЕ поступает такой уровень напряжения, который разрешает прохождение информации через коммутаторы 14 и 15 с вторых групп входов.

Таким образом, в устройстве осуществляется дещифрация и запись или считывание какого-либо числа, адрес которого поступает на адресные входы устройства.

Период времени регенерации информации в накопнтеле 16 (режим РЕГЕНЕРАЦИЯ) задается делителем 17 частоты. Перед началом работы устройства по входу установа в исходное состояние устанавливаются в нулевое состояние делитель 17 частоты, счетчик 1 адресов регенерации и триггер 18. Затем на делитель 17 частоты начинают непрерывно поступать импульсы с вхО да подачи синхроимпульсов устройства. На выходе делителя частоты формируются импульсы начала каждого цикла РЕГЕНЕРАЦИИ. При этом коэффициент пересчета делителя 17 выбирается исходя из максимально допустимого интервала времени хранения информации в микросхемах БИС ЗУ без подачи питания. Каждый импульс с выхода делителя 17 частоты поступает на второй вход элемента ИЛИ 22 и, далее, на нулевой вход триггера 18, подтверждая каждый раз его нулевое состояние. Таким образом, импульсы с выхода делителя 17 частоты поддерживают второй элемент И 21 по первому входу в открытом состоянии.

Инициализация регенерации информации в накопителе 16 осуществляется либо при отсутствии сигнала .запроса на обращение, либо сразу же после отработки текущего запроса на обращение. Анализ запросов на ОБРАЩЕНИЕ и на РЕГЕНЕРАЦИЮ осуществляется в блоке 5 управления. При этом, если в результате такого анализа разрещен цикл регенерации, первый формирователь 6 вырабатывает разрешающий сигнал на регенерацию, который через открытый по первому входу второй элемент И 21 поступает на вход счетчика 1 адресов регенерации, устанавливая его в состояние очередного текущего адреса регенерации, и на управляющие входы второго 14 и третьего 15 коммутаторов, разрешая прохождение информации через них со стороны первых групп входов.

Счетчик адресов регенерации разделен на три группы разрядов (по числу уровней системы матриц накопителя 16). Младшая группа 2 разрядов счетчика 1 адресов регенерации (например, 2 разряда), содержащая код адреса строки матрицы накопителя 16, через первый дешифратор 9 поступает на первую группу входов второго коммутатора 14. Учитывая, что в режиме РЕГЕНЕРАЦИЯ второй коммутатор 14 открыт со стороны первой группы входов, на четвертую группу управляющих входов наколителя 16 поступает с первого дещифратора 9 соответствующий сигнал для выбора строки матрицы накопителя 16. Средняя группа 3 разрядов счетчика 1 адресов регенерации, содержащая код адреса строки матрицы модуля накопителя 16, через второй дешифратор 10 поступает на первую группу входов первого коммутатора 13. Последний в режиме РЕГЕНЕРАЦИЯ открыт по второму управляющему входу от третьего формирователя 8, что обеспечивает прохождение на

выход первого коммутатора 13 информации с первой группы входов его. Следовательно, на третью группу управляющих входов накопителя 16 для выбора матрицы строки модуля памяти сигнал поступает с выхода второго дешифратора 10.

Старшая группа 4 разрядов счетчика 1 адресов регенерации, содержащая код адреса строки схемы БИС ЗУ, поступает на первую группу входов третьего коммутатора 15. Учитывая, что в режиме РЕГЕНЕРАЦИЯ третий коммутатор 15, как и второй коммутатор 14, открыт со стороны первой группы входов, на вторую группу управляющих входов накопителя 16 поступает код со старшей группы 4 разрядов счетчика 1 адресов регенерации для выбора строки микросхемы БИС ЗУ. Адес столбца микросхемы БИС ЗУ в режиме РЕГЕНЕРАЦИЯ не формируется, так как регенерация в микросхемах БИС ЗУ осуществляется по строкам. Сигналы адреса соответствующей строки на выходе первого 13, и второго 14 коммутаторов представлены в унитарном коде (после соответствующих дешифраторов), а на выходе третьего коммутатора 15 - в позиционном коде.

Таким образом, перебор адресов регенерации происходит так, что, например, первоначально регенерируется информация в ячейках памяти первой строки микросхемы БИС ЗУ первой строки матрицы модуля памяти первой строки матрицы накопителя 16. Затем для регенерации выбирается ячейка памяти в первой строке микросхемы БИС ЗУ первой строки матрицы модуля памяти, но уже второй строки матрицы накопителя 16 и т.д. Кроме того, регенерация информации в устройстве осуществляется одновременно по частям объема памяти, для чего в каждом цикле регенерации адресация строк матрицы накопителя 16 происходит таким образом, что выбирается одновременно сразу несколько строк с помощью второго коммутатора 14.

Циклу регенерации в устройстве осуществляются непрерывно и последовательно в

случае выполнения соответствующих условий в блоке 5 управления до переполнения счетчика 1 адресов регенерации. Цри переполнении счетчика 1 регенерации срабатывает первый элемент И 20, по переднему фронту перепада напряжения которого с помощью дополнительного формирователя 19 формируется импульс, переводящий триггер 18 в единичное состояние. При этом второй элемент И 21 по первому входу блокируется, следовательно, процесс формирования очередных циклов регенерации от первого формирователя 6 прекращается из-за блокировки второго элемента И 21. Последующие циклы регенерации начнутся только по

5 очередному импульсу с делителя 17 частоть, когда по этому импульсу триггер 18 снова переключится в нулевое состояние и будет открыт второй элемент И 21 для пропускания импульсов на счетчик 1 адресов регенерации и управляющие входы второго 14 и

0 третьего 15 коммутаторов.

Технико-экономическое преимущество предлагаемого устройства заключается в снижении потребляемой мощности устройством, поскольку после полного цикла регенерации по всему объему накопителя в случае имющегося запаса времени для сохранения информации в накопителе без подачи питания выдерживается пауза до прихода следующего импульса с делителя частоты (по существу, с электронных часов, фиксирующих гарантированный интервал времени сохранения информации в микросхемах БИС ЗУ без питания).

Учитывая, что чистое время регенерации объема накопителя (без режима ОБРАЩЕНИЕ) составляет единицы процентов от полного времени хранения информации в накопителе без питания, и допуская, что 50% времени работы ЗУ занято обращениями к нему по записи или по считыванию, можно принять приблизительно величину паузы в работе схем регенерации порядка 50-45%/ что приведет к экономии 50-45% потребляемой мощности, а следовательно, и к экономии блоков питания для ЗУ.

нпт тчннолУ)

-DMdOCbHfl DUUROJ

о 9°еоуд

мнзаб ю оиипЕ/г uomgDvh/ bodoujg

S 25

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Динамическое запоминающее устройство и формирователь синхросигналов для него | 1980 |

|

SU936030A1 |

| Устройство для восстановления информацииВ блОКАХ пАМяТи | 1978 |

|

SU849297A1 |

| Устройство для регенерации информации | 1984 |

|

SU1238151A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Оперативное запоминающее устрой-CTBO | 1979 |

|

SU809363A1 |

| Устройство управления регенерацией динамической памяти | 1989 |

|

SU1615727A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блок управления, входы которого являются управляющими входами устройства, а выходы соединены с входами соответственно накопителя, и первого, второго и третьего формирователей, первый коммутатор, первый и второй управляющие входы которого подключены к выходам соответственно второго и третьего формирователей, второй и третий коммутаторы, управляющие входы которых соединены со счетным входом счетчика, первый и второй дещифраторы, входы которых соединены с соответствующими выходами счетчика, причем входы первой группы первого и второго коммутаторов подключены к выходу соответствующего дещифратора, входы первой группы третьего коммутатора соединены с соответствующими выходами счетчика, третий и четвертый дещифраторы, выходы которых соединены с входами второй группы соответственно первого и второго коммутаторов, а входы являются соответствуюу ими адресными входами устройства, одни из адресных входов накопителя соединены с выходами коммутаторов, а другие являются адресными входами устройства, отличающееся тем, что, с целью уменьщения потребляемой мощности устройства, в него введены делитель частоты, триггер, дополнительный формирователь, элементы И, ИЛИ, причем счетный вход делителя частоты соединен с одним из входов блока управления, а установочный вход соединен с установочным входом счетчика, одним из входов элемента ИЛИ и является установочным входом устройства, выход деш (Л лителя частоты соединен с другим входом элемента ИЛИ, выход которого соединен с одним установочным входом триггера, один из выходов которого соединен с одним из входов первого элемента И, один выход которого соединен со счетным входом счетчика, а другой - с выходом первого формирователя, другой установочный вход триггера соединен с выходом дополнительного формирователя, вход которого соединен с выхо05 дом второго элемента И, входы которого О соединены с соответствующими выходами счетчика. 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3790961, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| тип). | |||

Авторы

Даты

1985-07-07—Публикация

1983-12-09—Подача