нТГА -нЭВМ

ел

sl

00 00

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов набора заголовка | 1989 |

|

SU1614124A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2012149C1 |

| Устройство для передачи и приема телеграфных сигналов | 1980 |

|

SU924896A1 |

| Устройство для передачи данных | 1979 |

|

SU773675A1 |

| Устройство для преобразования кодов | 1976 |

|

SU594592A1 |

| Электронный стартстопный распределитель | 1979 |

|

SU966927A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

| Электронное синхронное телеграфное устройство | 1978 |

|

SU860331A2 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1975 |

|

SU562932A1 |

Изобретение относится к технике телеграфной связи. Цель изобретения - повышение точности формирования. Устройство содержит согласующий блок 1, накопитель 2, элемент ИЛИ 3, согласующий блок 4, формирователь 5 импульсов, формирователь 6 телеграфного сигнала, блок 7 дешифраторов, анализатор 8 сигналов, распределитель 9, накопитель 10, формирователь 11 импульсов, элемент ИЛИ 12, накопитель 13. Информационные сигналы в последвательном коде МТК-2 поступают на вход устройства. Признак начала заголовка выделяется в блоке 7. Поступающие знаки формализованной части заголовка контролируются анализатором 8. Сигнал, характеризующий вид нарушения содержимого заголовка, поступает из анализатора 8 в распределитель 9, с выхода которого этот сигнал через накопитель 13, элемент ИЛИ 12 и согласующий блок 1 поступает на выход устройства. 3 з.п. ф-лы, 4 ил.

Фиг. 1

Изобретение относится к технике телеграфной связи и может быть использовано в автоматизированных системах передачи и обработки информа- ции.

Цель изобретения - повышение точности формирования.

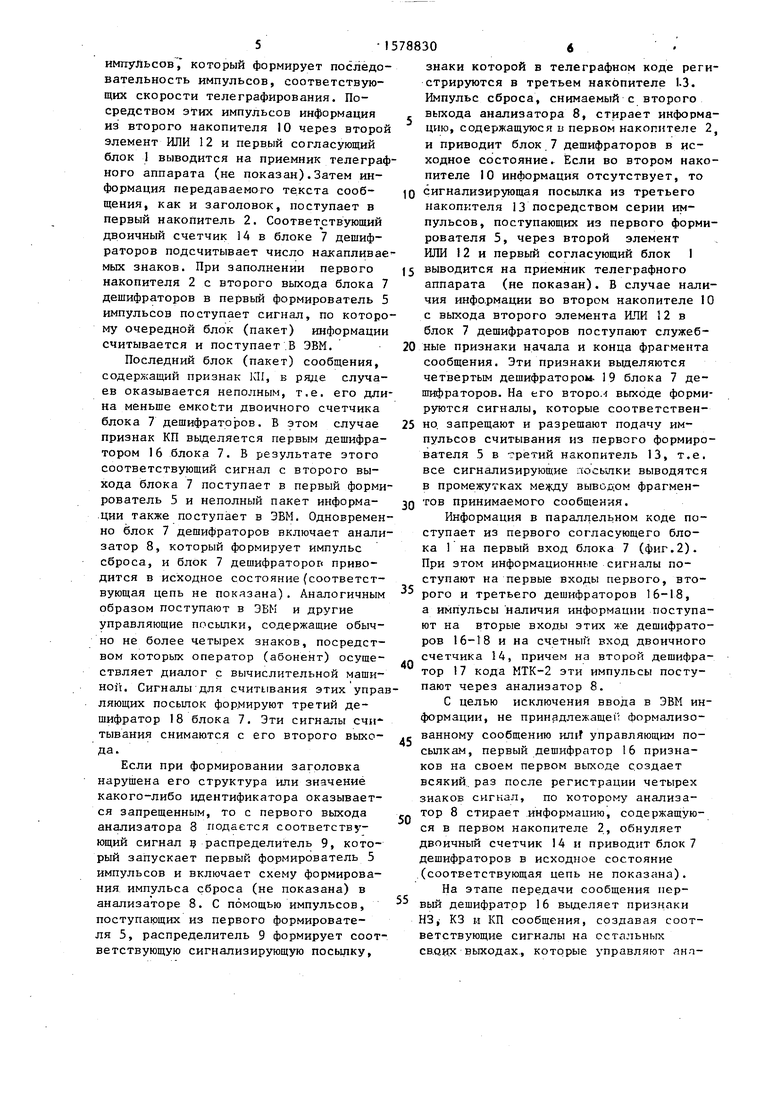

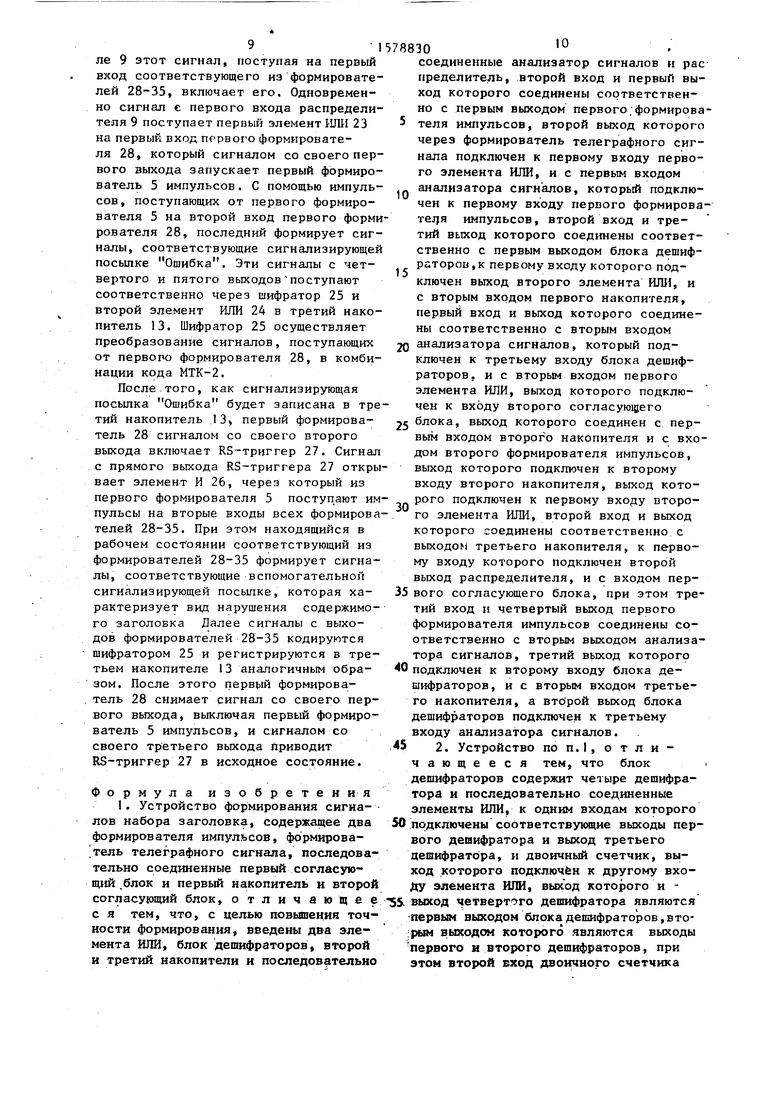

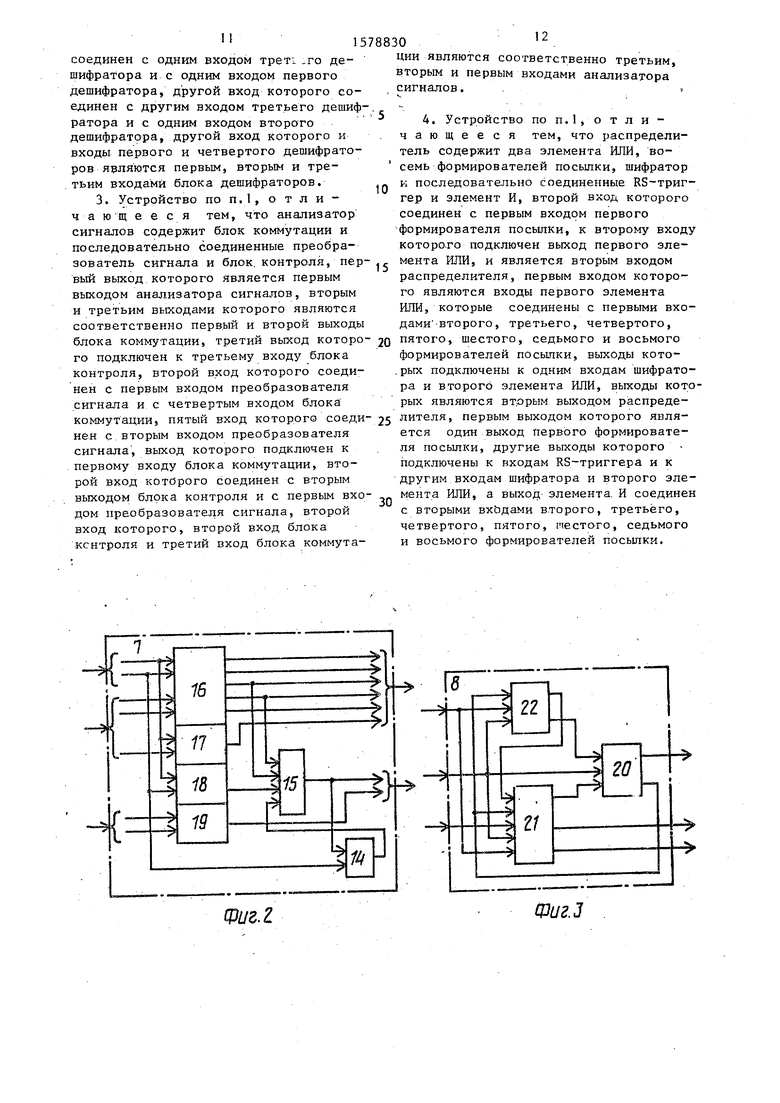

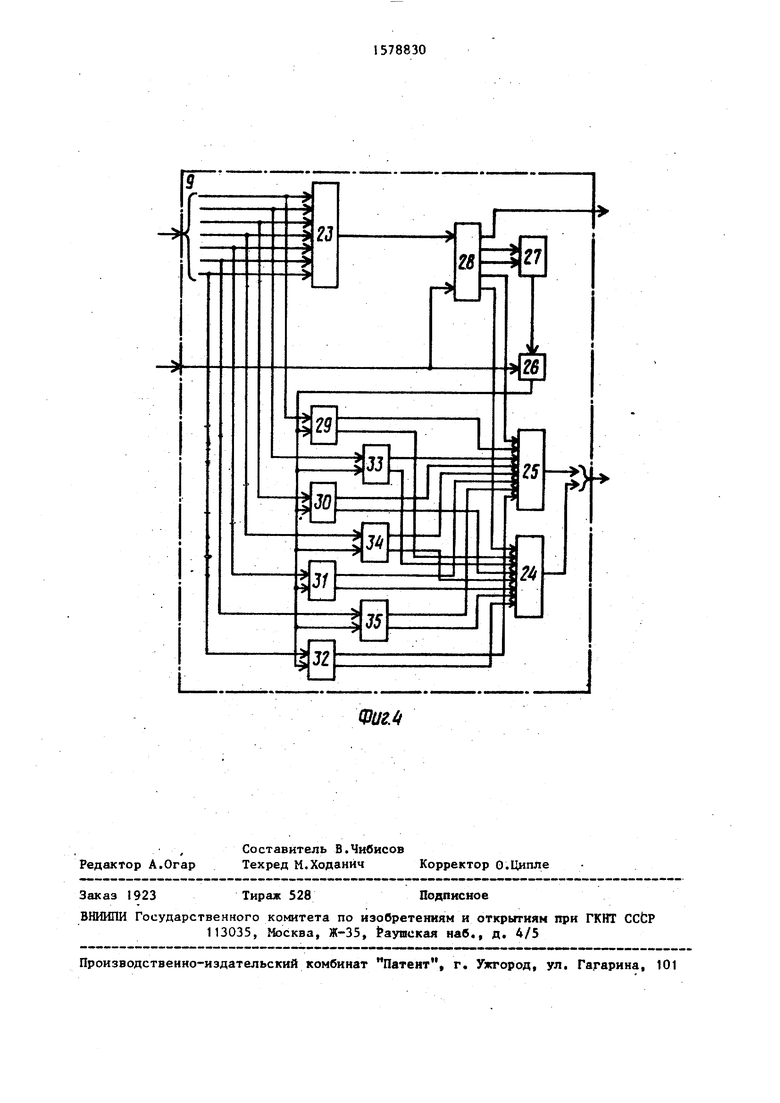

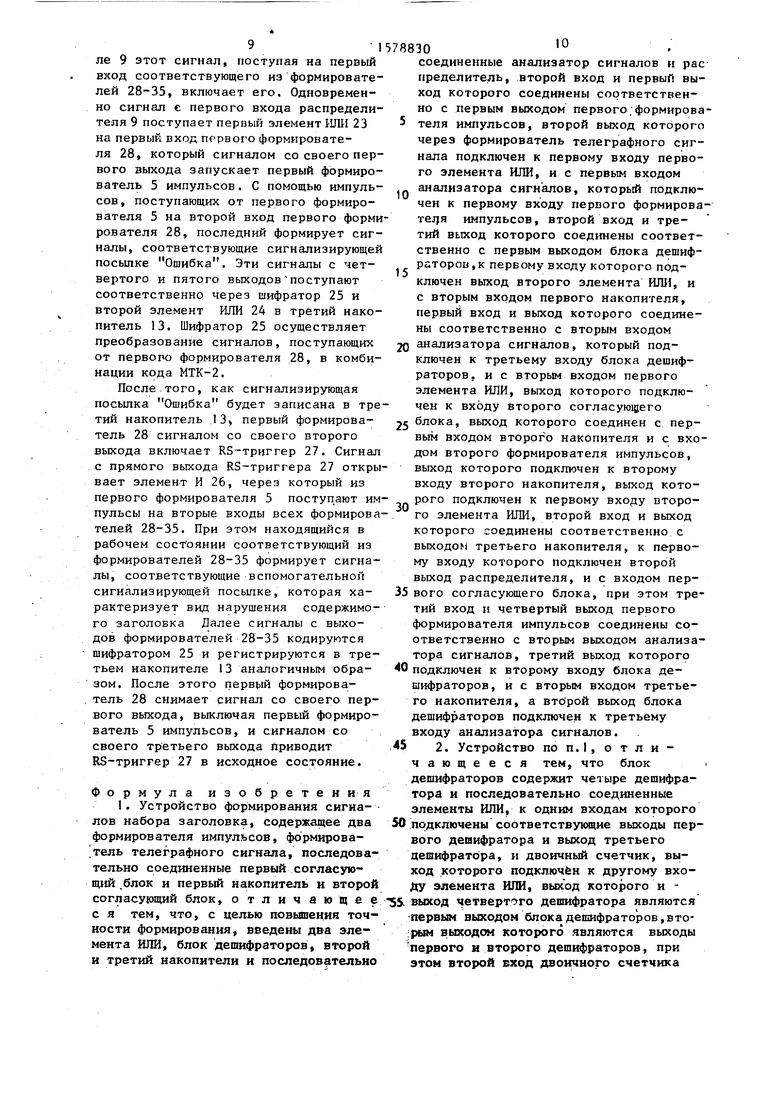

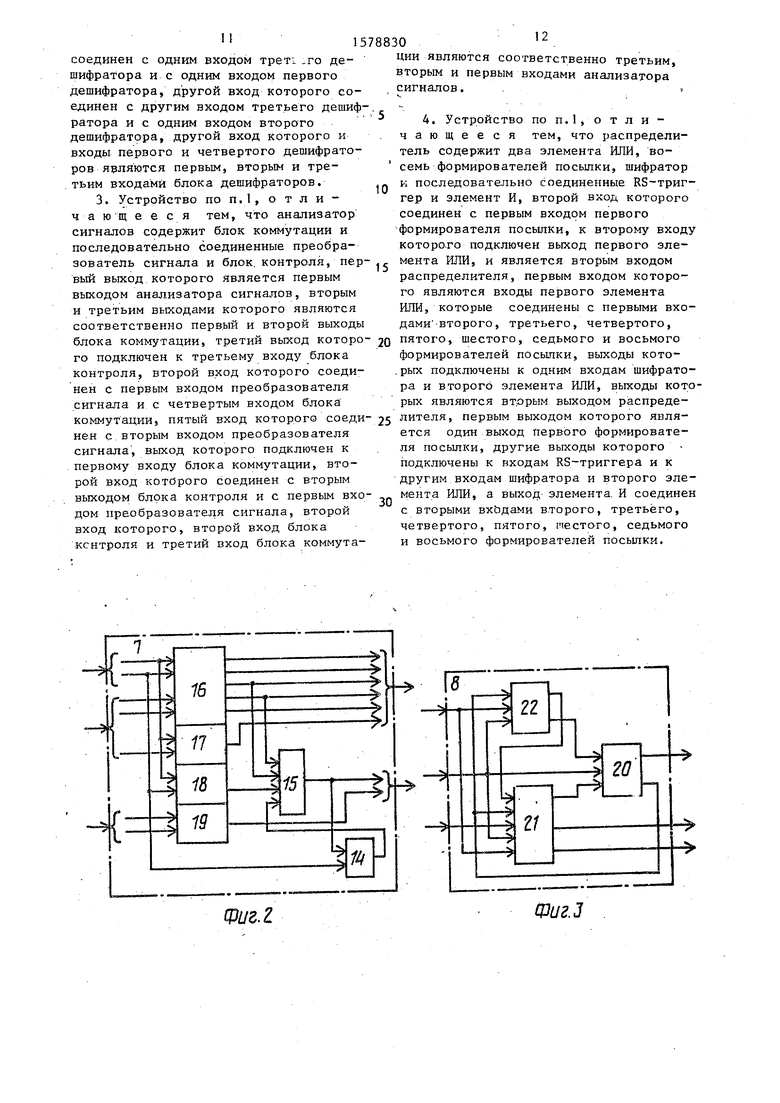

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - схема блока дешифратора, пример исполнения; на фиг.З - схема анализатора сигналов; на фиг.4 - схема распределителя.

Устройство формирования сигналов набора заголовка содержит (фиг.1) первый согласующий блок I, первый накопитель 2, первый элемент ИЛИ 3, второй согласующий блок 4, первый формирователь 5 импульсов, формирова- тель 6 телеграфного сигнала, блок 7 дешифраторов, анализатор 8 сигналов, распределитель 9, второй накопи- .. тель 10, второй формирователь 11 импульсов, второй элемент ИЛИ 12 и тре- тий накопитель 13.

Блок 7 дешифраторов образуют (фиг.2) двоичный счетчик 14, элемент ИЛИ 15 и с первого по четв ер- тый дешифраторы I6-J9.

Анализатор 8 сигналов включает (фиг.З) блок 20 контроля, блок 21 коммутации и преобразователь 22 сигнала.

Распределитель 9 содержит (фиг.4) первый и второй элементы ИЛИ 23 и 24, шифратор 25, элемент И 26, RS-триггер 27 и с первого по восьмой формирователи 28-35 посылки.

Устройство работает следующим об- разом.

Информационные сигналы от передатчика телеграфного аппарата (не показан) в последовательном коде МТК-2 поступают на вход первого согласую- щего блока 1, в котором осуществляется согласование сигналов по уровню и преобразование последовательного кода в параллельный. С выхода первого согласующего блока 1 информацией- ные сигналы вместе с импульсами наличия информации поступают в первый накопитель 2, в котором информация накапливается. Эти же сигналы поступают также на первый вход блока 7 дешифраторов и на второй вход анализтора 8.

При наличии в потоке информации признака начала заголовка (НЗ) он выделяется в блоке 7 первым дешифратором 16 (фиг.2) и соответствующий сигнал поступает на первый вход анализатора 8, с второго выхода которого снимается импульс и подается через первый формирователь 5 импульсов в первый накопитель 2. В результате этого в первом накопителе 2 стирается вся содержащаяся в нем информация, кроме последних четырех знаков. Одновремен- но анализатор 8 проключает свой второй вход, на который поступают импульсы наличия информации, через свой третий выход на второй вход блока 7, в котором включается второй дешифратор 17, а первый дешифратор 16 настраивается на выделение признака конца заголовка (КЗ).

Поступающие знаки формализованной части заголовка , контролируются анализатором 8. Если структура заголовка не нарушена и значения идентификаторов являются разрешенными, w после поступления формализованной части в блоке 7 первым дешифратором 16 выде- . ляется признак КЗ. В случае правильной структуры признака КЗ первый дешифратор 16 блока 7 перестраивается на выделение признака конца передачи (КП) сообщения. По сигналу, поступающему с второго выхода блока 7 дешифраторов, запускается первый формирователь 5 импульсов, который выдает в формирователь 6 телеграфного сигнала и в первый накопитель 2 серию сдвиговых импульсов. При этом осуществляется считывание информации из первого накопителя 2 совместно с адресными признаками, которые вырабатываются формирователем 6 телеграфного сигнала С выхода первого элемента ИЛИ 3 блоки (пакеты) информации, обрамленные в начале и конце адресными признаками поступают через второй согласующий блок 4 в ЭВМ (не показана). Второй согласующий блок 4 реализует функцию интерфейса и преобразование телеграфного кода в код вычислительной машины

После анализа введенного заголовка ЭВМ выдает соответствующую сигнализирующую посылку, которая является разрешением на ввод текста сообщения. При этом сигнализирующая посылка, а также и вся информация,адресованная абоненту, поступает из ЭВМ через второй согласующий блок 4 во второй накопитель 10. По сигналу наличия информации запускается второй формирователь 1

импульсов, который формирует последовательность импульсов, соответствующих скорости телеграфирования. Посредством этих импульсов информация из второго накопителя 10 через второй элемент ИЛИ 12 и первый согласующий блок 1 выводится на приемник телеграфного аппарата (не показан).Затем информация передаваемого текста сообщения, как и заголовок, поступает в первый накопитель 2. Соответствующий двоичный счетчик 14 в блоке 7 дешифраторов подсчитывает число накапливаемых знаков. При заполнении первого J5 выводится на приемник телеграфного накопителя 2 с второго выхода блока 7 аппарата (не показан). В случае наличия информации во втором накопителе 10 с выхода второго элемента ИЛИ 52 в блок 7 дешифраторов поступают служеб- 20 ные признаки начала и конца фрагмента сообщения. Эти признаки выделяются четвертым дешифратором- 19 блока 7 дешифраторов. На его второ.1 выходе формируются сигналы, которые соответствен- 25 но запрещают и разрешают подачу импульсов считывания из первого формиродешифраторов в первый формирователь 5 импульсов поступает сигнал, по которому очередной блок (пакет) информации считывается и поступает В ЭВМ.

Последний блок (пакет) сообщения, содержащий признак КП, в ряде случаев оказывается неполным, т.е. его длина меньше емкости двоичного счетчика блока 7 дешифраторов. В этом случае признак КП выделяется первым дешифратором 16 блока 7. В результате этого соответствующий сигнал с второго выхода блока 7 поступает в первый формирователь 5 и неполный пакет информации также поступает в ЭВМ. Одновременно блок 7 дешифраторов включает анализатор 8, который формирует импульс сброса, и блок 7 дешифраторов приводится в исходное состояние(соответствателя 5 в ретий накопитель 13, т.е. все сигнализирующие -госьшкк выводятся в промежутках между выводом фрагмен- JQ тов принимаемого сообщения.

Информация в параллельном коде поступает из первого согласующего блока 1 на первый вход блока 7 (фиг.2). При этом информационные сигналы поступают на первые входы первого, втовующая цепь не показана). Аналогичным рого и третьего дешифраторов 16-18,

образом поступают в ЭВМ и другие управляющие посылки, содержащие обычно не более четырех знаков, посредством которых оператор (абонент) осуществляет диалог с вычислительной машиной. Сигналы для считывания этих упраляющих посыпок формируют третий дешифратор 18 блока 7. Эти сигналы считывания снимаются с его второго выхода.

Если при формировании заголовка нарушена его структура или значение какого-либо идентификатора оказывается запрещенным, то с первого выхода анализатора 8 подается соответствующий сигнал в распределитель 9, который запускает первый формирователь 5 импульсов и включает схему формирования импульса сброса (не показана) в анализаторе 8. С помощью импульсов, поступающих из первого формирователя 5, распределитель 9 формирует соответствующую сигнализирующую посылку,

знаки которой в телеграфном коде регистрируются в третьем накопителе 1.3. Импульс сброса, снимаемый с второго выхода анализатора 8, стирает информацию, содержащуюся и первом накопителе 2, и приводит блок 7 дешифраторов в исходное состояние. Если во втором накопителе 10 информация отсутствует, то сигнализирующая посылка из третьего накопителя 13 посредством серии импульсов, поступающих из первого формирователя 5, через второй элемент ИЛИ 12 и первый согласующий блок I

вателя 5 в ретий накопитель 13, т.е. все сигнализирующие -госьшкк выводятся в промежутках между выводом фрагмен- тов принимаемого сообщения.

Информация в параллельном коде поступает из первого согласующего блока 1 на первый вход блока 7 (фиг.2). При этом информационные сигналы поступают на первые входы первого, второго и третьего дешифраторов 16-18,

0

5

а импульсы наличия информации поступают на вторые входы этих же дешифраторов 16-18 и на счетный вход двоичного счетчика 14, причем на второй дешифратор 17 кода МТК-2 эти импульсы поступают через анализатор 8.

С целью исключения ввода в ЭВМ информации, не принадлежащей формализованному сообщению или управляющим посылкам, первый дешифратор 16 признаков на своем первом выходе создает всякий раз после регистрации четырех знаков сигнал, по которому анализатор 8 стирает информацию, содержащуюся в первом накопителе 2, обнуляет двоичный счетчик 14 и приводит блок 7 дешифраторов в исходное состояние (соответствующая цепь не показана). На этапе передачи сообщения пер- 5 вый дешифратор 16 выделяет признаки НЗ, КЗ и КП сообщения, создавая соответствующие сигналы на остальных своих выходах, которые управляют анл0

лизатором 8. После выделения первым дешифратором 16 признака НЗ анализатор 8 включает второй дешифратор 17 путем подачк на его второй вход импульсов наличия информации. Сигналы с выхода этого второго дешифратора 17 поступают на дальнейшую обработку в анализатор 8. После выделения признака НЗ анализатор 8 подает соответствую- щий сигнал на третий вход первого дешифратора 16, по которому отключается первый вход первого дешифратора 16 от анализатора 8, т.е. поступающая информация из первого согласующего бло- ка 1 начинает регистрироваться в первом накопителе 2. После выделения признака КЗ из анализатора 8 на четвертый вход первого дешифратора 16 подается сигнал, с помощью которого первый дешифратор 16 перестраивается pa выделение признака КП сообщения.

Сигналы, соответствующие заполнению двоичного счетчика 14, выделению первым дешифратором 16 признака КЗ и КП, а третьим дешифратором 18 - управляющих посылок, являются импульсами считывания информации из первого накопителя 2« Эти сигналы объединяются элементом ИЛИ 15. С выхода этого элемента ИЛИ 15 сигналы поступают на двоичный счетчик 14, который обнуляется, и на первый формирователь 5 импульсов. Последний формирует серию импульсов для считывания информации из первого накопителя 2 и формирователя 6 телеграфного сигнала с последующим вводом ее в ЭВМ.

При выводе информации на приемник телеграфного аппарата информационные сигналы и импульсы наличия информации одновременно поступают соответственно HF первый и второй входы четвертого дешифратора 19, который выделяет служебные признаки начала и конца фраг- мента сообщения. Соответствующие сигналы с его выхода управляют порядком считывания информации из третьего накопителя 13 посредством подачи импульсов считывания из первого формирователя 5.

Сигналы управления, соответствующие различным признакам заголовка (сообщения) , поступают из блока 7 дешифраторов на пятый вход блока 21 коммутации и на второй вход преобразователя 22 (фиг.3).До этапа передачи сообщения, а также после выделения блоком 7 дешифраторов признака НЗ соответствующая схема в блоке 21 всякий раз формирует импульс стирания информации и приведения блока 7 в исходное состояние. Этот импульс снимается с второго выхода блока 21.

Кроме того, после выделения блоком 7 дешифраторов признака НЗ импульсы наличия информации, поступающие на четвертый вход блока 21, нереклю- чаются на его третий выход и включают второй дешифратор 17 в блоке 7. После этого сигналы управления, соответствующие идентификаторам формализованного заголовка, обрабатываются преобразователем 22 и с его выходов подаются непосредственно на первый вход блока 20 контроля либо через блок 21 на третий вход блока 20 контроля. При этом блок 21 осуществляет коммутацию сигналов, поступающих на его второй вход, и распределяет их по соответствующим схемам контроля блок а 20.

Импульсы наличия информации, поступающие на третий вход преобразователя 22, на второй вход блока 20 копр- роля и на четвертый вход блока 21, а также вспомогательные сигналы управления, снимаемые с второго выхода блока 20 контроля, обеспечивают согласованную работу всех блоков анализатора 8.

Если структура заголовка не нарушена и все его идентификаторы являются разрешенными, то после выделения блоком 7 дешифраторов признака КЗ с третьего выхода блока 21 подается соответствующий сигнал в блок 7 для настройки первого дешифратора 16 на выделение признака КП и анализатор 8 отключается. В противном случае соответствующая схема контроля блока 20 вырабатывает сигнал, определяющий характер нарушения содержащейся информации в заголовке, который затем с его первого выхода подается в распределитель 9. Соответствующий сигнал из распределителя .9 поступает на третий вход блока 21, в котором запускается схема формирования импульса стирания информации. Последний снимается с его второго выхода. Блок 7 дешифраторов приводится в исходное состояние и анализатор 8 отключается.

Сигнал, характеризующий вид нарушения содержимого заголовка, поступает из анализатора 8 на первый вход распределителя 9 (фиг.4).В распределите9I

ле 9 этот сигнал, поступая на первый вход соответствующего из формирователей 28-35, включает его. Одновременно сигнал с первого входа распределителя 9 поступает первый элемент ИЛИ 23 на первый вход первого формирователя 28, который сигналом со своего первого выхода запускает первый формирователь 5 импульсов. С помощью импульсов, поступающих от первого формирователя 5 на второй вход первого форми рователя 28, последний формирует сигналы, соответствующие сигнализирующей посылке Ошибка. Эти сигналы с четвертого и пятого выходов поступают соответственно через шифратор 25 и второй элемент ИЛИ 24 в третий накопитель 13. Шифратор 25 осуществляет преобразование сигналов, поступающих от первого формирователя 28, в комбинации кода МТК-2.

После того, как сигнализирующая посылка Ошибка будет записана в третий накопитель 13, первый формирователь 28 сигналом со своего второго выхода включает RS-триггер 27. Сигнал с прямого выхода RS-триггера 27 откры- вает элемент И 26, через который из первого формирователя 5 поступают импульсы на вторые входы всех формирователей 28-35. При этом находящийся в рабочем состоянии соответствующий из формирователей 28-35 формирует сигналы, соответствующие вспомогательной сигнализирующей посылке, которая характеризует вид нарушения содержимого заголовка Далее сигналы с выходов формирователей 28-35 кодируются шифратором 25 и регистрируются в третьем накопителе 13 аналогичным образом. После этого первый формирователь 28 снимает сигнал со своего первого выхода, выключая первый формирователь 5 импульсов, и сигналом со своего третьего выхода приводит RS-триггер 27 в исходное состояние.

Формула изобретения 1. Устройство формирования сигналов набора заголовка, содержащее два формирователя импульсов, формирователь телеграфного сигнала, последовательно соединенные первый согласующий ,блок и первый накопитель н второй согласующий блок, отличающее с я тем, что, с целью повышения точности формирования, введены два элемента ИЛИ, блок дешифраторов, второй и третий накопители и последовательно

10

15

78830|0

соединенные анализатор сигналов н рас пределитель, второй вход и первый выход которого соединены соответственно с первым выходом первого формирова5 теля импульсов, второй выход которого через формирователь телеграфного сигнала подключен к первому входу первого элемента ИЛИ, и с первым входом анализатора сигналов, который подключен к первому входу первого формирователя импульсов, второй вход и третий выход которого соединены соответственно с первым выходом блока дешифраторов, к первому входу которого подключен выход второго элемента ИЛИ, и с вторым входом первого накопителя, первый вход и выход которого соединены соответственно с вторым входом

2Q анализатора сигналов, который подключен к третьему входу блока дешифраторов, и с вторым входом первого элемента ИЛИ, выход которого подключен к входу второго согласующего

25 блока, выход которого соединен с первым входом второго накопителя и с входом второго формирователя импульсов, выход которого подключен к второму входу второго накопителя, выход которого подключен к первому входу второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего накопителя, к первому входу которого подключен второй выход распределителя, и с входом пер35 вого согласующего блока, при этом тре тий вход и четвертый выход первого формирователя импульсов соединены соответственно с вторым выходом анализатора сигналов, третий выход которого

40 подключен к второму входу блока дешифраторов, и с вторым входом третьего накопителя, а второй выход блока дешифраторов подключен к третьему входу анализатора сигналов.

45 2. Устройство по п.отличающееся тем, что блок дешифраторов содержит четыре дешифратора и последовательно соединенные элементы ИЛИ, к одним входам которого

50 подключены соответствующие выходы первого дешифратора и выход третьего дешифратора, и двоичный счетчик, выход которого подключен к другому входу элемента ИЛИ, выход которого и - 35. выход четвертого дешифратора являются первым выходом блока дешифраторов,вторым выходом которого являются выходы первого и второго дешифраторов, при этом второй вход двоичного счетчика

30

10

11157883012

соединен с одним входом трет, .го де- ««и являются соответственно шифратора и с одним входом первого вторым и первым входами анализатор дешифратора, другой вход которого со- А ми ана™затоРа единен с другим входом третьего дешифратора и с одним входом второго дешифратора, другой вход которого и входы первого и четвертого дешифраторов являются первым, вторым и третьим входами блока дешифраторов.

-,/

сигнала, выход которого подключен к первому входу блока коммутации, второй вход которого соединен с вторым выходом блока контроля и с первым входом преобразователя сигнала, второй вход которого, второй вход блока контроля и третий вход блока коммуталя посыпки, другие выходы которого подключены к входам RS-триггера и к другим входам шифратора и второго эле- 30 мента ИЛИ, а выход элемента И соединен с вторыми вхЬдами второго, третьего, четвертого, пятого, пестого, седьмого и восьмого формирователей посылки.

Фиг. г

0

««и являются соответственно вторым и первым входами анализатор А ми ана™затоРа

мента ИЛИ, и является вторым входом распределителя, первым входом которого являются входы первого элемента ИЛИ, которые соединены с первыми вхо- дами второго, третьего, четвертого 0 пятого, шестого, седьмого и восьмого формирователей посылки, выходы кото- рых подключены к одним входам шифрато- ра и второго элемента ИЛИ, выходы кото- рых являются вторым выходом распреде- 5 лителя, первым выходом которого явля- ется один выход первого формироватесигналов.

-,/

Фиг.З

- I

23

&

IB

П

JJ

zs

H

2b

ФигА

| Устройство для передачи и приема телеграфных сигналов | 1980 |

|

SU924896A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-07-15—Публикация

1988-10-10—Подача