сл

00

со сл VJ

о

Изобретение относится к технике защиты различных объектов от доступа постоРС

Нних лиц, в частности к электронным

замкам.

Целью изобретения является повышение удобства использования устройства.

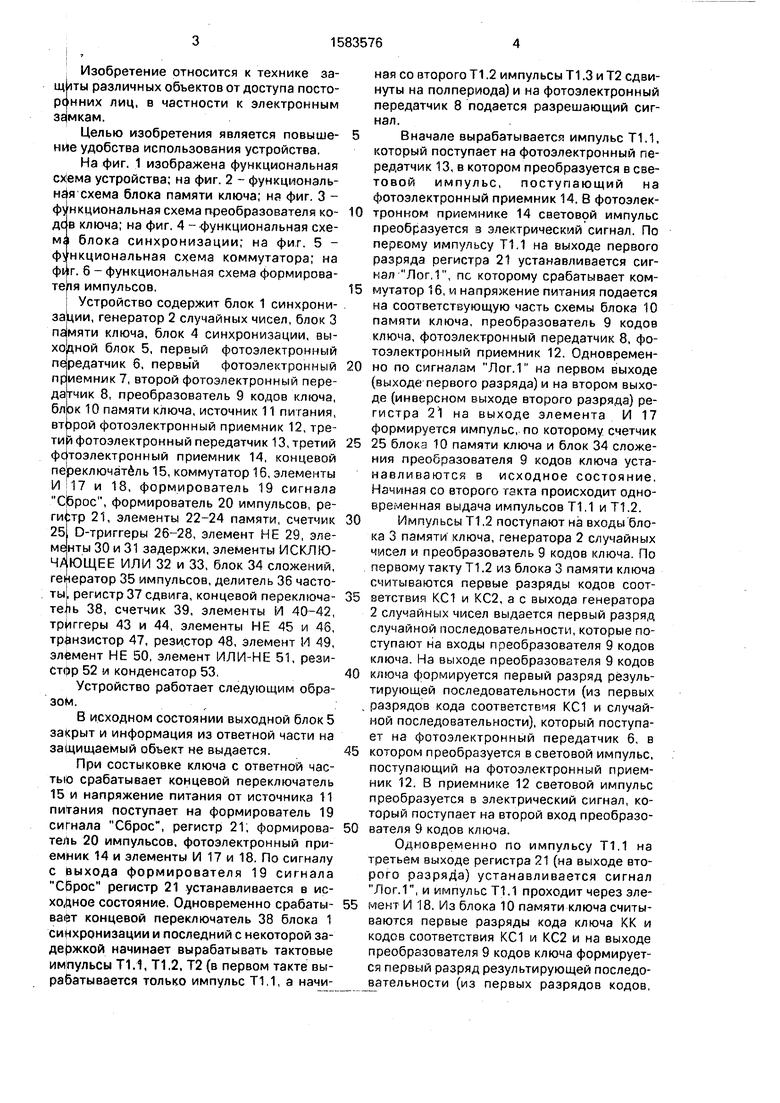

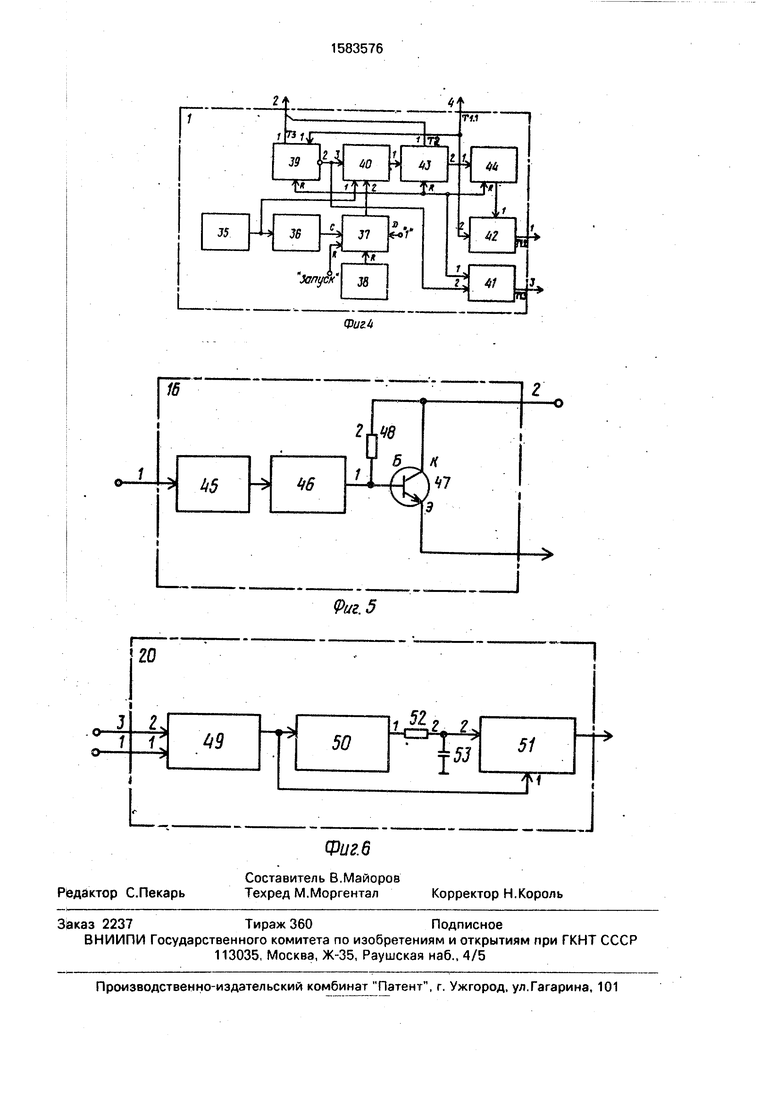

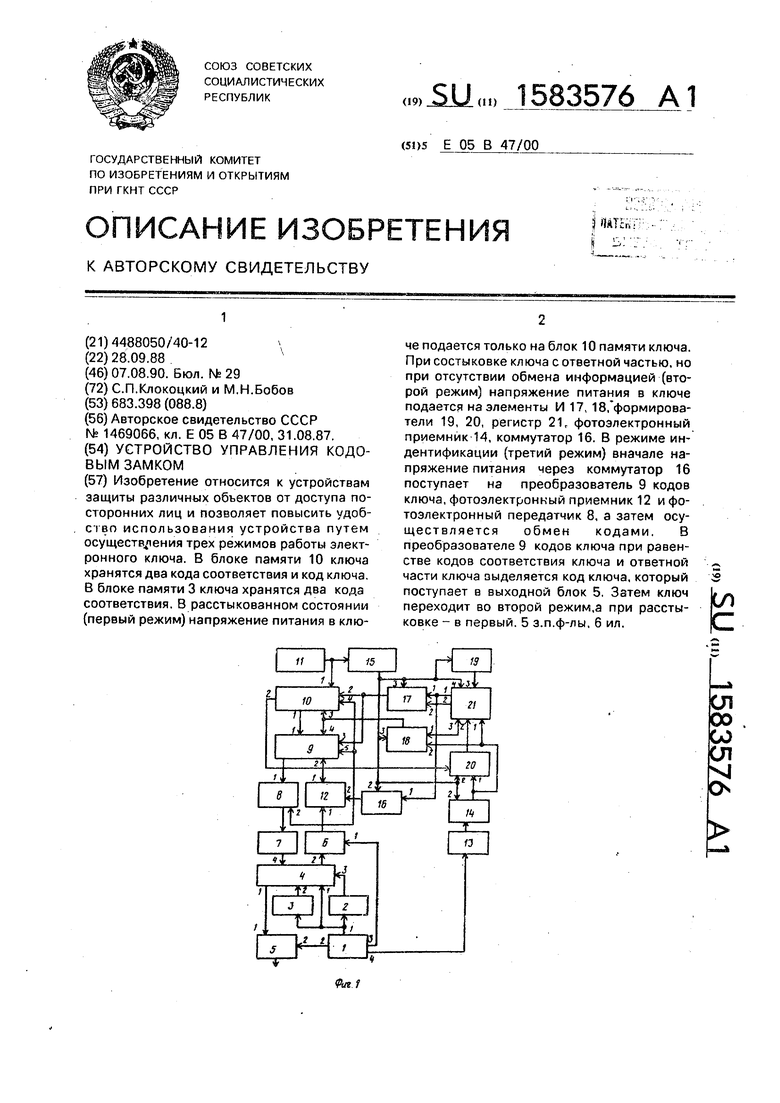

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональна схема блока памяти ключа; на фиг. 3 - функциональная схема преобразователя коде в ключа; на фиг. 4 - функциональная схе- мл блока синхронизации; на фиг. 5 - функциональная схема коммутатора; на фиг. 6 - функциональная схема формирова- тетя импульсов.

Устройство содержит блок 1 синхрони- за|ции, генератор 2 случайных чисел, блок 3 памяти ключа, блок 4 синхронизации, выходной блок 5, первый фотоэлектронный передатчик 6, первый фотоэлектронный приемник 7, второй фотоэлектронный передатчик 8, преобразователь 9 кодов ключа, блок 10 памяти ключа, источник 11 питания, второй фотоэлектронный приемник 12, трети л фотоэлектронный передатчик 13, третий фотоэлектронный приемник 14, концевой переключатель 15, коммутатор 16, элементы И 17 и 18, формирователь 19 сигнала С0рос, формирователь 20 импульсов, регистр 21, элементы 22-24 памяти, счетчик 25 D-триггеры 26-28, элемент НЕ 29, элементы 30 и 31 задержки, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 32 и 33, блок 34 сложений, генератор 35 импульсов, делитель 36 частоты регистр 37 сдвига, концевой переключа- Tejib 38, счетчик 39, элементы И 40-42, триггеры 43 и 44, элементы НЕ 45 и 46, транзистор 47, резистор 48, элемент И 49, элемент НЕ 50, элемент ИЛИ-НЕ 51, резистор 52 и конденсатор 53.

Устройство работает следующим образом.

В исходном состоянии выходной блок 5 закрыт и информация из ответной части на защищаемый объект не выдается.

При состыковке ключа с ответной частью срабатывает концевой переключатель 15 и напряжение питания от источника 11 питания поступает на формирователь 19 сигнала Сброс, регистр 21, формирователь 20 импульсов, фотоэлектронный приемник 14 и элементы И 17 и 18. По сигналу с выхода формирователя 19 сигнала Сброс регистр 21 устанавливается в исходное состояние. Одновременно срабаты- вайт концевой переключатель 38 блока 1 синхронизации и последний с некоторой задержкой начинает вырабатывать тактовые импульсы Т1.1, Т1.2, Т2 (в первом такте вырабатывается только импульс Т1.1, а начиная со второго Т1.2 импульсы Т1.3 и Т2 сдвинуты на полпериода) и на фотоэлектронный передатчик 8 подается разрешающий сигнал.

Вначале вырабатывается импульс Т1.1,

который поступает на фотоэлектронный передатчик 13, в котором преобразуется в световой импульс, поступающий на фотоэлектронный приемник 14. В фотоэлек0 тронном приемнике 14 световрй импульс преобразуется з электрический сигнал. По первому импульсу Т1.1 на выходе первого разряда регистра 21 устанавливается сигнал Лог.1, пс которому срабатывает ком5 мутатор 16, и напряжение питания подается на соответствующую часть схемы блока 10 памяти ключа, преобразователь 9 кодов ключа, фотоэлектронный передатчик 8, фотоэлектронный приемник 12, Одновремен0 но по сигналам Лог.1 на первом выходе (выходе первого разряда) и на втором выходе (инверсном выходе второго разряда) регистра 21 на выходе элемента И 17 формируется импульс, по которому счетчик

5 25 блока 10 памяти ключа и блок 34 сложения преобразователя 9 кодов ключа устанавливаются в исходное состояние. Начиная со второго гакта происходит одновременная выдача импульсов Т1.1 и Т1.2.

0 Импульсы Т1,2 поступают на входы блока 3 памяти ключа, генератора 2 случайных чисел и преобразователь 9 кодов ключа. По первому такту Т1.2 из блока 3 памяти ключа считываются первые разряды кодов соот5 зетствия КС1 и КС2, а с выхода генератора 2 случайных чисел выдается первый разряд случайной последовательности, которые поступают на входы преобразователя 9 кодов ключа. На выходе преобразователя 9 кодов

0 ключа формируется первый разряд результирующей последовательности (из первых , разрядов кода соответствия КС1 и случайной последовательности), который поступает на фотоэлектронный передатчик 6, в

5 котором преобразуется в световой импульс, поступающий на фотоэлектронный приемник 12. В приемнике 12 световой импульс преобразуется в электрический сигнал, который поступает на второй вход преобразо0 вателя 9 кодов ключа.

Одновременно по импульсу Т1.1 на третьем выходе регистра 21 (на выходе второго разряда) устанавливается сигнал Лог.1, и импульс Т1.1 проходит через эле5 мент И 18. Из блока 10 памяти ключа считываются первые разряды кода ключа КК и кодов соответствия КС1 и КС2 и на выходе преобразователя 9 кодов ключа формируется первый разряд результирующей последовательности (из первых разрядов кодов,

считываемых из блока 10, и результирующей последовательности, полученной из ответной части), который поступает на фотоэлектронный передатчик 8. Преобразованный в световой сигнал передатчиком 8 импульс поступает на фотоэлектронный приемник 7, с выхода которого электрический сигнал поступает на преобразователь 9 кодов ключа. В преобразователе 9 кодов ключа из полученного первого разряда результирующей последовательности производится отделение разрядов случайной последовательности и кода соответствия КС2 и выделение первого разряде ключа кода. При этом на первом выходе преобразователя 9 кодов ключа формируется истинное значение разряда кода ключа, если значения первых разрядов соответствия, хранимых в блоках 3 и 10 памяти замка и ключа соответственно, равны, в противном случае на выходе блока 4 формируется ложное значение разрядов кода ключа КК. Затем по такту Т2 разряд кода ключа записывается в выходной блок 5. Аналогичный процесс происходит по следующим тактам Т1.1.Т1.2 иТ2.

После приема всего кода ключа в выходной блок 5 с второго, выхода счетчикз 25 блока 10 памяти ключа на вход формирователя 20 импульсов поступает разрешающий сигнап и по заднему фронту импульса Т1.1 на выходе формирователя 20 формируется импульс, которым производится сброс в О регистра 21. Коммутатор 16 закрывается и напряжение питания снимается с части схемы блока 10 памяти ключа, преобразователя 9 кодов ключа, фотоэлектронного передатчика 8 и фотоэлектронного приемника 12, Одновременно выдается запрещающий сигнал на фотоэлектронный передатчик 6, что приводит к гашению фо- тоизлучателя, и сигнал ТЗ, по которому разрешается выдача принятого в выходной блок 5 кода.

Если коды соответствия ответной части и ключа не совпадают, поступающий в выходной блок 5 код ключа будет искажаться и, следовательно, доступа к защищаемому объекту не произойдет.

После отсоединения ключа от ответной части сигнал ТЗ разрешения с блока 1 синхронизации снимается, выдача кода ключа на защищаемый объект прекращается и в электронном ключе срабатывает концевой переключатель 15 и обесточиваются блоки 19, 21,20, 17 и 18,

Формула изобретения

1. Устройство управления кодовым замком, содержащее блок синхронизации, первый выход которого соединен с входом

генератора случайных чисел, входом блока памяти замка и первым входом преобразователя кодов замка, второй и третий входы которого соединены соответственно с выходамп блока памяти замка л генератора случайных чисел, первый выход преобразователя кодов замка соединен с первым входом выходного блока, второй вход которого соединен с вторым выходом блока синхро0 низации, Е третий выход блока синхронизации соединен с первым входом первого фотоэпектронного передатчика, второй вход первого фотоэлектронного передатчика соединен с вторым выходом преобразо5 зэтеля кодое замка, четвертым входом соединенного с выходом первого фотоэлектронного приемника, вход первого фотоэлектронного приемника соединен с выходом второго фотоэлектронного пере0 датч /ка, первый вход которого соединен с выходом преобразователя кодов ключа. первым входом соединенного с первым выходом блока памяти ключа, первый вход блока памяти ключа соединен с выходом

5 источника питания, второй вход преобразователя кодов ключа соединен с выходом второго фотоэлектронного приемника, первый вход которого соединен с выходом первого фотоэлектронного передатчика, третий фо0 тоэлектронкый передатчик, выход которого соединен с первым входом третьего фотоэлектронного приемника, отличающее- с я тем, что, с целью повышения удобства использования, устройство содержит кон5 цевой переключатель, коммутатор, элемент И, формирователь сигнала сброса, формирователь импульсов, регистр, причем четвертый выход блока синхронизации соединен с входом третьего фотоэлектрон0 ного передатчика, первый выход регистра соединен с первым входом пеового элемента И и первым входом коммутатора, второй выход регистра подключен к второму входу первого элемента И, третий выход регистра

5 соединен с первым входом второго элемента И. причем первый вход регистра соединен с выходом третьего фотоэлектронного приемника, вторым входом второго элемента И и первым входом формирователя им0 пульсов, при этом второй вход регистра подключен к выходу формирователя им- пульсов, третий вход регистра соединен с выходом формирователя сигнала сброса, четвертый вход регистра - с выходом конце5 вого переключателя, входом формирователя сигнала сброса, третьими входами первого и второго элементов И, вторыми входами коммутатора, вторым входом формирователя импульсов и вторым входом третьего фотоэлектронного приемника, выход первого элемента И соединен с вторым входом блока памяти ключа и третьим входом преобразователя кодов ключа, причем выход второго элемента И соединен с четвертым входом преобразователя кодов ключа и третьим входом блока памяти ключа, второй выход которого соединен с третьим входом формирователя импульсов, а вь|ход коммутатора соединен с четвертым вхэдом блока памяти ключа, пятым входом преобразователя кодов ключа, вторыми входами второго фотоэлектронного приемника и второго фотоэлектронного передатчика, при этом выход источника питания соединен с входом концевого переключателя,

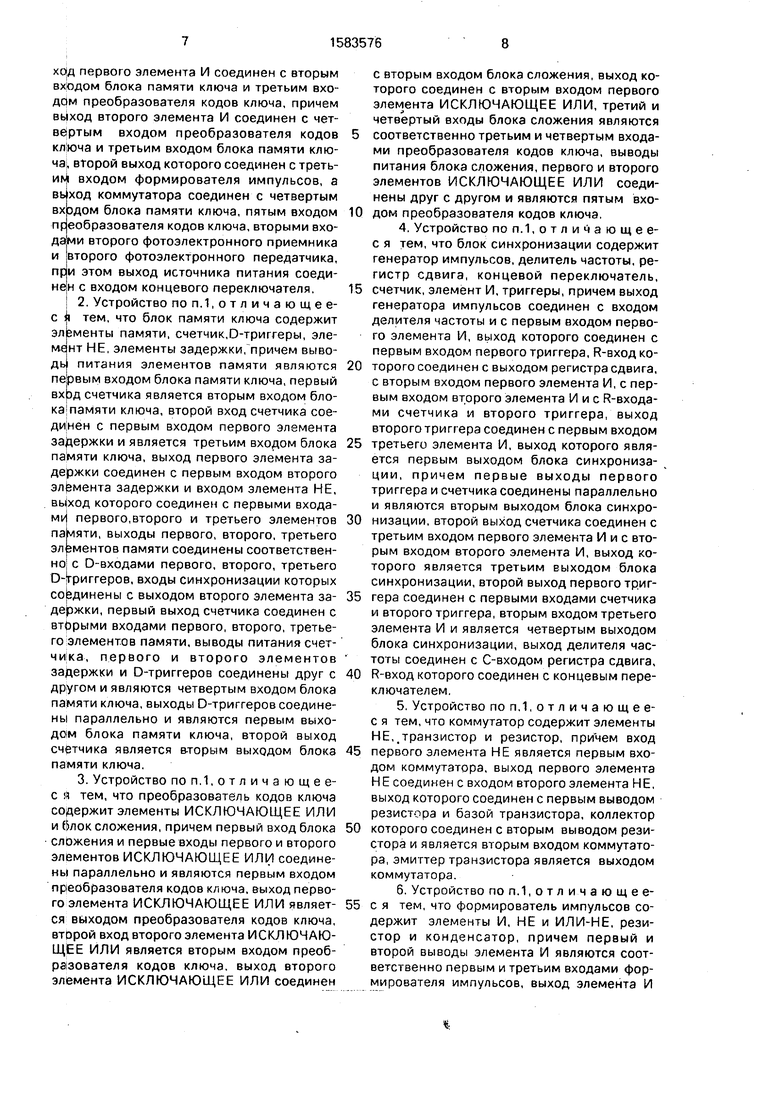

1 2. Устройство по п. 1, о т л и ч а ю щ е е- с л тем, что блок памяти ключа содержит элементы памяти, счетчик,D-триггеры, элемент НЕ, элементы задержки, причем выводы питания элементов памяти являются первым входом блока памяти ключа, первый вхрд счетчика является вторым входом блока памяти ключа, второй вход счетчика соединен с первым входом первого элемента задержки и является третьим входом блока памяти ключа, выход первого элемента задержки соединен с первым входом второго элемента задержки и входом элемента НЕ, вМход которого соединен с первыми входами первого,второго и третьего элементов памяти, выходы первого, второго, третьего элементов памяти соединены соответственно с D-входами первого, второго, третьего D-триггеров, входы синхронизации которых соединены с выходом второго элемента задержки, первый выход счетчика соединен с вторыми входами первого, второго, третьего элементов памяти, выводы питания счетчика, первого и второго элементов задержки и D-триггеров соединены друг с другом и являются четвертым входом блока памяти ключа, выходы D-триггеров соединены параллельно и являются первым выходом блока памяти ключа, второй выход счетчика является вторым выходом блока памяти ключа.

3. Устройство поп.Ч.отличающее- с и тем, что преобразователь кодов ключа содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и блок сложения, причем первый вход блока сложения и первые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены параллельно и являются первым входом преобразователя кодов ключа, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом преобразователя кодов ключа, втррой вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является вторым входом преобразователя кодов ключа, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен

с вторым входом блока сложения, выход которого соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий и четвертый входы блока сложения являются

соответственно третьим и четвертым входами преобразователя кодов кпюча, выводы питания блока сложения, первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены друг с другом и являются пятым вхо0 дом преобразователя кодов ключа,

4.Устройство поп.1,отличающее- с я тем, что блок синхронизации содержит генератор импульсов, делитель частоты, регистр сдвига, концевой переключатель,

5 счетчик, элемент И, триггеры, причем выход генератора импульсов соединен с входом делителя частоты и с первым входом первого элемента И, выход которого соединен с первым входом первого триггера, R-вход ко0 торого соединен с выходом регистра сдвига, с вторым входом первого элемента И, с первым входом второго элемента И и с R-входа- ми счетчика и второго триггера, выход второго триггера соединен с первым входом

5 третьего элемента И, выход которого является первым выходом блока синхронизации, причем первые выходы первого триггера и счетчика соединены параллельно и являются вторым выходом блока синхро0 низации, второй выход счетчика соединен с третьим входом первого элемента И и с вторым входом второго элемента И, выход которого является третьим выходом блока синхронизации, второй выход первого триг5 гера соединен с первыми входами счетчика и второго триггера, вторым входом третьего элемента И и является четвертым выходом блока синхронизации, выход делителя частоты соединен с С-входом регистра сдвига,

0 R-вход которого соединен с концевым переключателем.

5.Устройство по п,1, о т л и ч а ю щ е е- с я тем, что коммутатор содержит элементы НЕ,.транзистор и резистор, причем вход

5 первого элемента НЕ является первым входом коммутатора, выход первого элемента НЕ соединен с входом второго элемента НЕ, выход которого соединен с первым выводом резистора и базой транзистора, коллектор

0 которого соединен с вторым выводом резистора и является вторым входом коммутатора, эмиттер транзистора является выходом коммутатора.

6.Устройство по п.1, о т л и ч а ю щ е е- 5 с я тем, что формирователь импульсов содержит элементы И, НЕ и ИЛИ-НЕ, резистор и конденсатор, причем первый и второй выводы элемента И являются соответственно первым и третьим входами формирователя импульсов, выход элемента И

соединен с первым входом элемента ИЛИ-НЕ, выход которого является выходом фор- НЕ и с входом элемента НЕ, выход элементамирователя импульсов, выводы питания НЕ соединен с первым выводом резистора,элементов И, НЕ, ИЛИ-НЕ соединены межвторой вывод которого соединен с конден-ду собой и являются вторым входом форми- сатором и вторым выводом элемента ИЛИ-5 рователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления кодовым замком | 1989 |

|

SU1663165A1 |

| СПОСОБ УПРАВЛЕНИЯ ОПТОЭЛЕКТРОННЫМ ЗАМКОМ, КЛЮЧ И ОПТОЭЛЕКТРОННЫЙ ЗАМОК | 1993 |

|

RU2081281C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для формирования символов | 1980 |

|

SU934540A1 |

| Устройство для отображения информации | 1979 |

|

SU868822A2 |

| Система передачи и приема информации | 1987 |

|

SU1411795A1 |

Изобретение относится к устройствам защиты различных объектов от доступа посторонних лиц и позволяет повысить удобство использования устройства путем осуществления трех режимов работы электронного ключа. В блоке памяти 10 ключа хранятся два кода соответствия и код ключа. В блоке памяти 3 ключа хранятся два кода соответствия. В расстыкованном состоянии (первый режим) напряжение питание в ключе подается только на блок 10 памяти ключа. При состыковке ключа с ответной частью, но при отсутствии обмена информацией (второй режим) напряжение питания в ключе подается на элементы И 17, 18, формирователи 19, 20, регистр 21, фотоэлектронных приемник 14, коммутатор 16. В режиме индентификации (третий режим) вначале напряжение питания через коммутатор 16 поступает на преобразователь 9 кодов ключа, фотоэлектронный приемник 12 и фотоэлектронный передатчик 8, а затем осуществляется обмен кодами. В преобразователе 9 кодов ключа при равенстве кодов соответствия ключа и ответной части ключа выделяется код ключа, который поступает в выходной блок 5. Затем ключ переходит во второй режим, а при растыковке - в первый. 5 з.п.ф-лы, 6 ил.

L-L..

Фиг. 2

| Устройство управления кодовым замком | 1987 |

|

SU1469066A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-08-07—Публикация

1988-09-28—Подача