Изобретение относится к телемеханике, в частности к системам передачи с информационной обратной связью, и может найти применение в технике связи и телеметрии в условиях с меняющейся помеховой (шумовой) обстановкой.

Известна система передачи информации (1), содержащая на передающей стороне приемник, датчики, коммутатор, аналого-цифровой преобразователь, передатчик, на приемной стороне приемник, передатчик, а также линии прямого и обратного каналов.

Недостатком данной системы является низкая информативность, обусловленная необходимостью перезапросов искаженных слов, вследствие чего возрастает задержка при передачве сигналов, а информативность соответственно уменьшается.

Известна система передачи информации (2), содержащая на передающей стороне два блока аналоговых ключей, триггер, два дифференцирующих импульсно-кодовых модулятора, блок декодирования, блок элементов ИЛИ, блок кодирования, шифратор, на приемной стороне блок обнаружения сбоев, блок декодирования, блок интеграторов, блоки аналоговых ключей, блок кодирования, блок измерения отношения сигнал-шум, пороговый блок, а также прямой и обратный каналы связи.

Недостатком данной системы является низкая помехоустойчивость. В условиях возрастания уровня мощности помех система увеличивает порог квантования и соответственно для передачи канального слова использует меньшее количество канальных посылок. Длительность (а следовательно, и энергия) остается при этом неизменной, что в свою очередь оставляет неизменным отношение сигнал-шум на выходе приемника (5). Поэтому при превышении мощности помех определенного уровня функционирование системы будет нарушено.

Известна система передачи аналоговой информации (3), содержащая дифференциальный импульсно-кодовый модулятор, состоящий из блока вычисления разности, блока квантования, регулятора усиления и блока интегрирования, блок кодирования, прямой канал, дешифратор, блок интегрирования, детектор качества канала, блок кодирования, обратный канал, дешифратор обратного канала, детектор качества обратного канала, блок управления кодированием. В случае роста уровня мощности помех система изменяет длительность канальных посылок в обратном канале, что позволяет повысить энергию полезного сигнала и тем самым помехоустойчивость в обратном (и только в обратном) канале системы. При этом в прямом канале никаких мер по повышению помехозащищенности не принято, и, как следствие этого, при росте уровня помех в прямом канале будет возрастать число искажений канальных слов, эффективность работы системы из-за слабо защищенного в смысле помех прямого канала упадет.

Таким образом, недостатком данной системы является низкая помехоустойчивость передачи сигналов по прямому каналу.

Наиболее близкой по технической сущности (прототипом) следует считать систему передачи информации (4), содержащую на передающей стороне датчики, преобразователь погрешности аппроксимации, сумматор, анализатор погрешности аппроксимации, синхронизатор, шифратор, коммутатор, аналого-цифровой преобразователь, передатчик, приемник, два селектора кода, цифроаналоговый преобразователь, 1-й формирователь импульсов сброса, 1-й блок памяти, два блока ключей, второй блок памяти, второй формирователь импульсов сброса, третий блок ключей, на приемной стороне приемник, передатчик, а также линии прямого и обратного каналов.

Недостатком данной системы является низкая помехоустойчивость передачи информации и, как следствие этого, узкая область ее применения. Данная система преобразует аналоговые сигналы с датчиков в n-разрядный двоичный код, включающий также и адрес отсчета, формируемый шифратором. Сформированный таким образом сигнал длительностью Тк nTc, где Тс длительность одного разряда, модулирует несущую передатчика, излучается в прямой канал, поступает в приемник и на выход системы, а также с выхода системы подается в передатчик приемной стороны, проходит линию обратного канала, принимается, декодируется и сравнивается с аналогичным соответствующим отсчетом, не прошедшим линии связи. Результат сравнения сигнал, равный ошибке передачи суммируется с ошибкой предсказания. Суммарный сигнал ошибки передачи изменяется в соответствии с изменением сигнала ошибки передачи и будучи максимальным среди аналогичных суммарных сигналов всех других каналов, данный канал получает приоритет опроса, т. е. опрашивается чаще, чем и компенсируется действие случайной помехи в данном канале.

Очевидно, что данная известная система передачи информации будет устойчиво и эффективно работать, если в течение не менее одного полного цикла опроса всех канальных датчиков помеха искажает n-разрядную комбинацию не более, чем в одном канале. Величина ошибки при этом будет зависеть от того, какой разряд n-разрядной комбинации был искажен: искажение разряда, имеющего наибольший вес вносит, как известно, максимальную ошибку. Если считать распределение искажения разрядов равномерным, то дисперсия ошибки определится из выражения:

σ2 (2i·d2)P(1-P)n-1

(2i·d2)P(1-P)n-1 (2i·d2)P где d шаг квантования,

(2i·d2)P где d шаг квантования,

Р вероятность искажения одного разряда,

n количество разрядов в канальном интервале (длина канального слова).

При искажении в течение одного полного цикла опроса каналов двух и более канальных слов (n-разрядных комбинаций) данная система предоставит приоритет опроса только одному каналу, имеющему максимальный суммарный сигнал ошибки передачи, хотя при этом может вполне оказаться, что в других каналах, n-разрядные комбинации которых также искажены, ошибки не намного меньше рассматриваемой.

Очевидно также, что данная система информации не способна предоставить приоритет опроса одновременно многим каналам, так как ее пропускная способность (как и любой системы) ограничена и определяется в данном случае тактовой частотой синхронизатора, количеством опрашиваемых каналов, спектром сигналов на выходе датчиков и т.д.

Как известно из теории передачи информации, под помехоустойчивостью понимается способность системы выполнять задачу (с заданной степенью качества) при воздействии помех, это способность противостоять вредному влиянию помех. Поскольку помехоустойчивость зависит от ряда случайных причин, то количественной мерой ее может быть вероятность Рн нарушения функционирования системы (5) (невыполнение заданной задачи) при воздействии помех. Вероятность Рн можно определить как вероятность того, что фактическое значение отношения сигнал-шум на выходе приемника станет меньше некоторого критического qкр, при котором функционирование системы нарушается, т.е. Рн Р(q≅ qкр). Критическое отношение сигнал-помеха на выходе приемника радиолинии, т.е. когда за время полного цикла опроса искажается не более одного канального интервала, можно записать в виде: R·2Eб/νп (1) где Рс мощность сигнала,

R·2Eб/νп (1) где Рс мощность сигнала,

νn- спектральная плотность помехи,

R скорость передачи информации,

Еб энергия сигнала на бит информации.

Для рассматриваемой системы передачи информации существует пороговое значение мощности помехи, при котором она может эффективно функционировать (значение пороговой спектральной плотности νn в формуле 1).

С ростом мощности помехи в радиоканале эффективность данной системы падает вследствие резкого увеличения количества (5,6) искажений канальных n-разрядных слов и соответственно возрастании ошибок передачи информационных сигналов от датчиков.

Таким образом, недостатком данной системы передачи является низкая помехоустойчивость передачи сигналов от датчиков и, как следствие, узкая область применения.

Целью изобретения является повышение помехоустойчивости системы передачи информации путем увеличения энергетических характеристик сигнала без увеличения мощности передачи.

Поставленная цель достигается тем, что в прототип дополнительно вводятся блок изменения сигнала, элемент ИЛИ, счетчик, блок сравнения, два регистра, причем выходы анализатора погрешности аппроксимации соединены с соответствующими входами элемента ИЛИ, выход которого соединен с входом счетчика, выход которого подключен к первому входу блока сравнения, ко второму входу которого подключен выход первого регистра, вход которого является первым установочным входом устройства, вторым установочным входом которого является вход второго регистра, выход которого соединен с установочным входом анализатора погрешности аппроксимации, выход блока сравнения подключен к второму входу БИС, первый вход которого соединен с выходом аналого-цифрового преобразователя, выход БИС подключен к входу передатчика, третий выход блока синхронизации соединен с входом сброса счетчика и синхровходом блока сравнения.

Введение новых отличительных признаков придает известному решению (4) новые свойства, а именно благодаря введению второго регистра, элемента ИЛИ, установочного входа анализатора погрешности аппроксимации появляется способность выделения на интервале полного цикла опроса датчиков числа каналов, ошибка в которых превышает допустимую. В прототипе производился лишь выбор только одного канала с максимальной ошибкой, при этом ошибки в других каналах могли быть немногим меньше максимальной, но тем не менее система на них не реагировала. Введение первого регистра, блока сравнения, БИС сообщает устройству возможность передачи канального слова меньшим (по сравнению с прототипом) числом элементарных разрядов, при этом длительность элементарного сигнала увеличивается, не изменяя длины всего слова, что в свою очередь позволяет повысить энергию элементарной посылки, а, следовательно, повысить помехоустойчивость (5).

Таким образом, свойства предлагаемой системы передачи информации, обусловленные ее отличительными признаками, не совпадают со свойствами прототипа и определяют получение положительного эффекта в виде расширения области применения за счет достижения поставленной цели: повышения помехоустойчивости системы передачи информации. Отсутствие в патентной и технической литературе сведений (рекомендаций) по выполнению заявляемой системы передачи информации в целях достижения описанного в заявке эффекта показывает новизну взаимосвязи между совокупностью существенных признаков заявляемого изобретения и положительным эффектом. Это обеспечивает существенные отличия данного изобретения от всех известных систем аналогичного назначения.

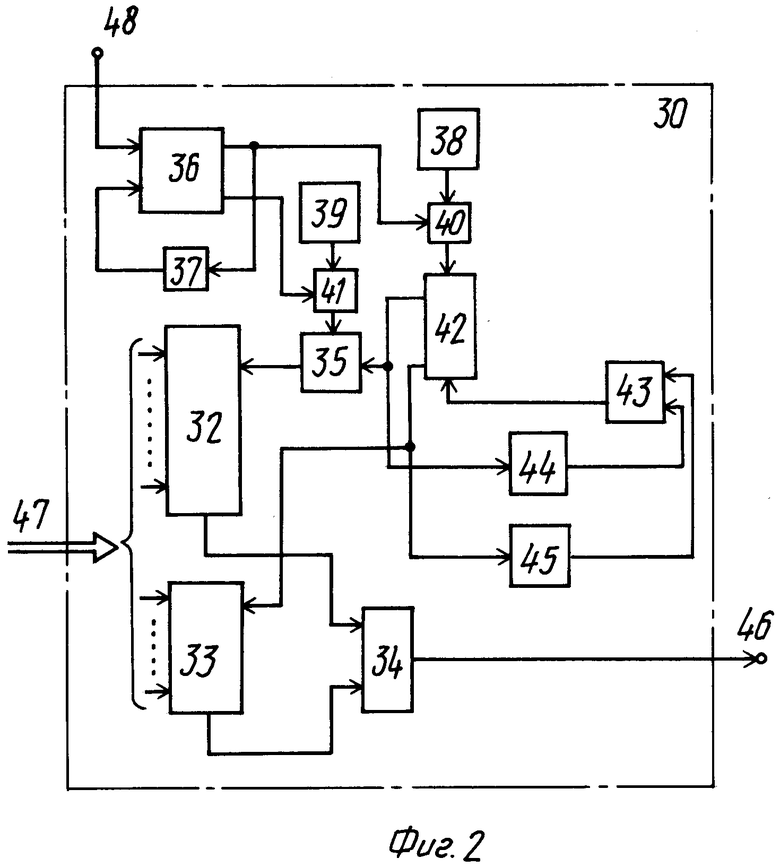

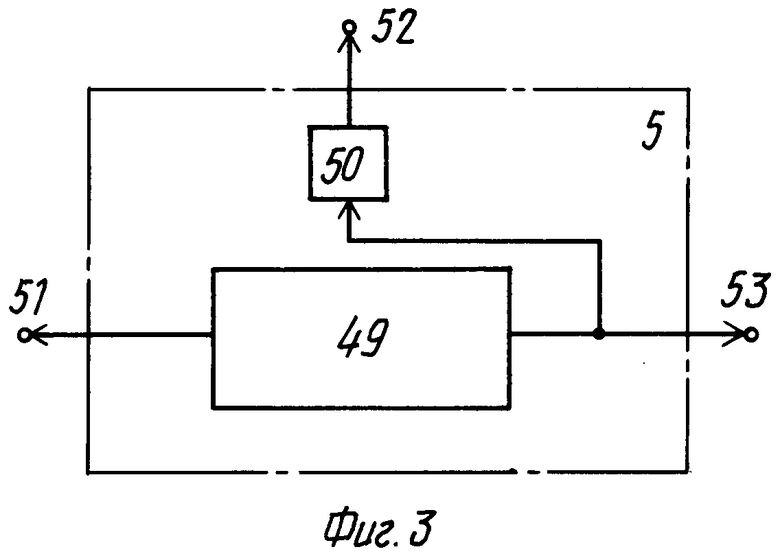

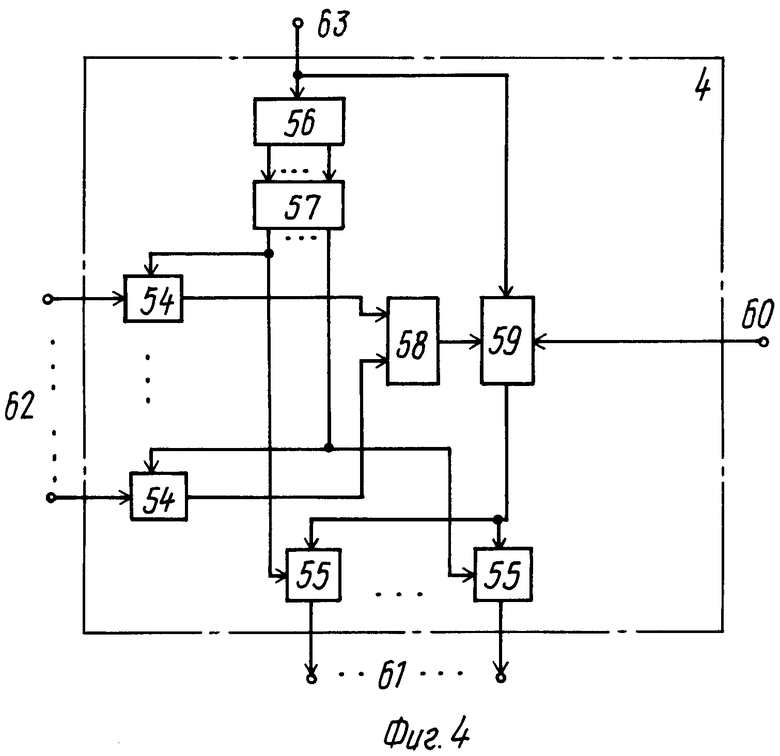

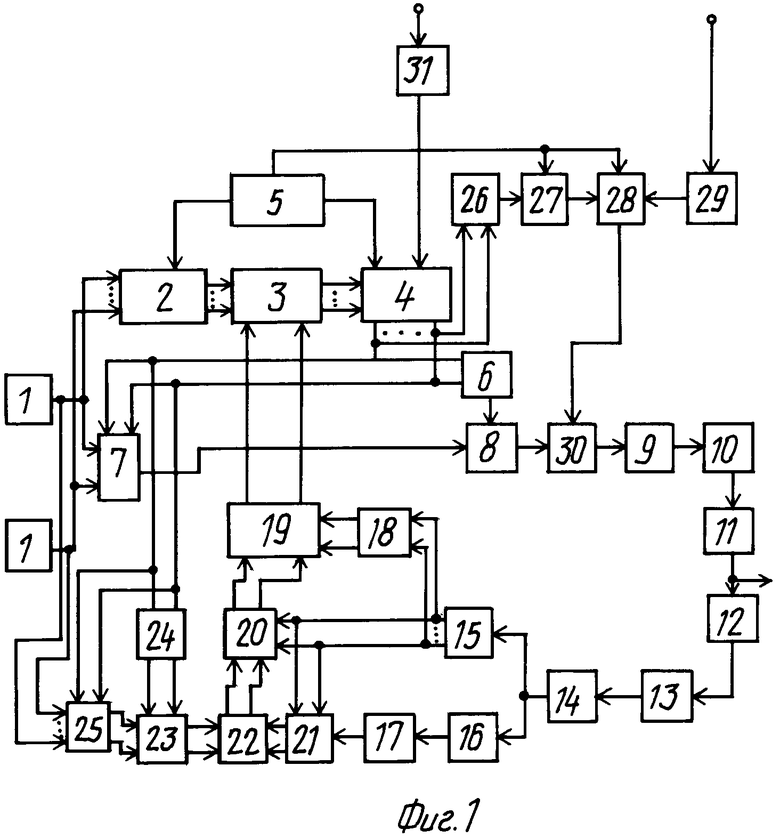

На фиг.1 представлена структурная схема системы передачи информации; на фиг. 2 вариант реализации БИС; на фиг.3 и фиг.4 варианты реализации блока синхронизации и анализатора погрешности аппроксимации соответственно.

Система передачи информации (фиг.1) содержит датчики 1, преобразователь 2 погрешности аппроксимации, сумматор 3, анализатор 4 погрешноси аппроксимации, блок синхронизации 5, шифратор 6, коммутатор 7, аналого-цифровой преобразователь 8, передатчик 9, линию 10 прямого канала, приемник 11, передатчик 12, линию 13 обратного канала, приемник 14, селекторы 15, 16 кода, цифроаналоговый преобразователь 17, 1-й формирователь 18 импульсов сброса, блок 19 памяти, блоки 20, 21 ключей, блок 22 вычитания, блок 23 памяти, 2-й формирователь 24 импульсов сброса, блок 25 ключей, элемент ИЛИ 26, счетчик 27, блок сравнения 28, регистры 29 и 31, БИС 30, причем выходы датчиков 1 подключены к информационным входам коммутатора 7, выход которого подключен к первому входу аналого-цифрового преобразователя 8, выход которого соединен с первым входом БИС 30, второй вход которого подключен к выходу блока 28 сравнения, второй вход которого соединен с выходом первого 29 регистра, вход которого является первым установочным входом системы передачи информации, вторым установочным входом которой является вход второго 31 регистра, выход которого соединен с установочным входом анализатора 4 погрешности аппроксимации, выходы которого соединены с соответствующими управляющими входами первого блока 25 ключей и коммутатора 7, с соответствующими входами шифратора 6 и второго формирователя 24 импульсов сброса, с соответствующими входами элемента ИЛИ 26, выход которого подключен к входу счетчика 27, выход которого соединен с первым входом блока 28 сравнения, синхровход которого соединен с входом сброса счетчика 2Г и третьим выходом блока синхронизации 5, первый и второй выходы которого соединены с тактовыми входами соответственно анализатора 4 погрешности аппроксимации и преобразователя 2 погрешности аппроксимации, выходы которого подключены к вторым входам сумматора 3, выходы датчиков 1 подключены к соответствующим информационным входам преобразователя 2 погрешности аппроксимации и первого 25 блока ключей, выходы последнего из которых соединены с соответствующими информационными входами первого блока 23 памяти, выходы которого подключены к первым входам блока 22 вычитания, выходы которого соединены с соответствующими информационными входами второго блока 20 ключей, выходы которого подключены к соответствующим информационным входам второго блока 19 памяти, выходы которого соединены с первыми входами сумматора 3, выходы которого подключены к информационным входам анализатора 4 погрешности аппроксимации, выходы формирователя 24 импульсов сброса подключены к соответствующим входам сброса первого блока 23 памяти, выходы дешифратора 6 соединены с вторыми входами аналого-цифрового преобразователя 8, выход приемника 14 подключен к входам первого 16 и второго 15 селекторов кода, выходы последнего соединены с соответствующими управляющими входами второго 20 и третьего 21 блока ключей и с соответствующими входами первого формирователя 18 импульсов сброса, выходы которого подключены к соответствующим входам сброса первого блока 19 памяти, выход первого селектора 16 кода через цифроаналоговый преобразователь 17 соединен с информационным входом третьего блока 21 ключей, выходы которого подключены к вторым входам блока вычитания 22, выход БИС 30 соединен с входом 9 передатчика, выход которого через линию прямого канала 10 подключен к входу приемника 11 на приемной стороне, выход которого подключен к входу передатчика 12, выход которого через линию обратного канала 13 соединен с входом приемника 14 передающей стороны, к выходу приемника 11 подключается потребитель информации.

Один из возможных вариантов исполнения блока изменения сигнала 30 представлен на фиг.2. Блок содержит два регистра 22, 23, число разрядов которых n-h и h соответственно, первый 34 и второй 35 элементы ИЛИ, первый RS-триггер 36, элемент задержки 37, первый 38 и второй 39 генераторы импульсов, первый 40 и второй 41 ключи, переключатель 42, второй RS-триггер 43, первый 44 и второй 45 счетчики, модули счета которых равны n-h и h соответственно, выход 46, первый вход 47, второй вход 48.

Блок синхронизации 5 содержит (фиг.3) синхронизатор 49 и делитель частоты 50, выход делителя 50 частоты является третьим 52 выходом блока, первым выходом 51 которого является первый вход синхронизатора 49, второй выход которого подключен к входу делителя 50 частоты и является вторым 53 выходом блока 5. Устройство и работа синхронизатора 5 аналогичны описанному синхронизатору (4).

Вариант реализации блока 4 приведен на фиг.4. Он содержит первую 54 и вторую группу 55 ключей, счетчик 56, дешифратор 57, элемент ИЛИ 58, блок сравнения 59, установочный вход 60, выходы 61, входы 62, тактовый вход 63, входами 62 блока 4 являются первые входы ключей 54 первой группы, выходы которых поключены к соответствующим входам элемента 58 ИЛИ, выход которого соединен с первым входом блока сравнения 50, выход которого подключен к первым входам второй 55 группы ключей, выходы которых образуют выход 61 блока 4, установочным входом которого является второй вход блока 59 сравнения, синхровход которого является тактовым 63 входом блока 4 и подключен к входу счетчика 56, выходы которого соединены с соответствующими входами дешифратора 58, выходы которого соединены с соответствующими вторыми входами ключей первой 54 и второй 55 группы.

Система работает следующим образом.

Сигналы с датчиков 1 через коммутатор 7 поступают в аналого-цифровой преобразователь (АЦП) 8, где амплитуда импульсов преобразуется в n-разрядный двоичный код, включающий и адрес отсчета, поступающий с шифратора 6. Пусть в n-разрядном слове для кодирования адреса источника используется k разрядов, тогда информационная часть слова содержит m n-k разрядов. До начала работы системы в регистр 31 вводят пороговое значение допустимой ошибки истинного и прошедшего прямой и обратный каналы значений сигналов, а в регистр 29 число каналов ζ в которых ошибка может превысить заданную. Таким образом, получают возможность гибко изменять значения порога помехоустойчивости передачи.

Рассмотрим работу системы в двух случаях. Первый из них следующий.

Пусть помеховая обстановка будет такова, что число ошибок не превышает пороговое значение ζ при этом спектральная плотность ν не превышает определенное значение νn С выхода АЦП n-разрядное слово проходит БИС 30, поступает в передатчик 9. Сигнал, прошедший линию 10 прямого канала поступает в приемник 11 и на выход системы. С выхода системы сигнал подается в передатчик 12, проходит линию обратного канала 13, приемник и поступает на селекторы 15, 16, а с последнего через цифроаналоговый преобразователь 17 и блоки 21 ключей подается на соответствующий вход блоков 22 вычитания.

Кроме того, информация с датчиков 1 поступает на информационные входы преобразователя 2 погрешности аппроксимации и блоков 25 ключей. С выходов блоков 25 ключей отсчет, который поступает на передачу, заносится по соответствующему входу в блоки 23 памяти. Перед записью нового отсчета в блоки 23 осуществляется сброс памяти. Выходные сигналы с блоков 23 поступают в блоки 22 вычитания, в которых сравниваются уровни исходных, запомненных в блоках 23 памяти и прошедших линии 10 и 13 сигналов, и выделяются ошибки передачи, которые через блоки 20 ключей заносятся в блоки 19 памяти.

В преобразователе 2 погрешности аппроксимации поканально сравниваются текущие значения параметров сигналов с предсказанными значениями, например, с функцией нулевой экстраполяции сигнала, и выделяются ошибки предсказания. Выделенные сигналы ошибок предсказания каждого канала поступают на вторые входы сумматора 3, на первые входы которого поступают сигналы с выхода блока 19 памяти, а на выходе по каждому каналу формируется суммарный сигнал. Выходные сигналы сумматора ошибок передачи поступают каждый по своей шине на информационные входы анализатора 4 погрешности аппроксимации, на установочный вход которого с регистра 31 поступает максимальное значение приемлемой возможной ошибки, с которым сравниваются ошибки всех каналов. Анализатор 4 погрешности определяет номера каналов, ошибки в которых превосходят заданное значение, на соответствующих его выходах вырабатываются импульсы сравнения. При условии ν<νn ошибки будут редки, их число за один цикл опроса будет меньше ζ Импульсы с выходом анализатора 4 погрешности предназначены для управления коммутатором 7 и блоком 25 ключей, выработки кодов адреса в шифраторе 6 и формирования укороченных импульсов сброса блока 23 памяти, аналогично указанным процессам и прототипе.

Рассмотрим для примера компенсацию влияния помех для данного случая на примере передачи сигнала одного канала.

Отсчет с выхода 23 блока памяти сравнивается в блоке 22 вычитания с отсчетом, прошедшим линии прямого и обратного каналов. Блок 22 производит сравнение аналоговых сигналов. Результат сравнения выделяется с помощью блока 20 ключей в соответствующую ячейку блока 19 памяти. Сигнал с выхода блока 19 памяти суммируется с ошибкой предсказания, поступающей с выхода преобразователя 2 погрешности аппроксимации. Суммарный сигнал ошибки передачи, который изменяется в соответствии с изменением сигнала ошибки передачи сравнивается с допустимым значением, заранее введенным в систему по второму установочному входу. Сравнение производится в анализаторе 4 погрешности аппроксимации, при этом, если ошибка в канале превосходит заданную, то на соответствующем выходе блока 4 появляется импульс считывания для управления коммутатором 7, блоком 25, шифратором 6 и формирования укороченных импульсов сброса блока 23 памяти. При этом в следующем канальном интервале будет опрошен этот же канал, ошибка в котором превысила заданное значение. Таким образом, канал получает приоритет опроса, чем и компенсируется действие помехи.

Теперь рассмотрим случай, когда уровень мощности помех в радиоканале возрастает и выполняется условие ν>νn При этом условии резко возрастает число искажений канальных слоев (так как отношение сигнал-шум не превосходит критическое qкр), за цикл опроса всех датчиков число каналов, ошибка передачи в которых превзойдет заданное значение, увеличится и превысит заданное число, введенное до начала работы системы по первому установочному входу. Счетчик 27 через элемент ИЛИ 26 ведет подсчет числа каналов, ошибка в которых превышает заданное значение в течение одного цикла опроса и по синхроимпульсу, поступающему с третьего выхода блока 5 выдает записанное число в блок сравнения 28, при этом счетчик 27 обнуляется и его цикл работы повторяется. Блок сравнения 28 по приходу синхроимпульса сравнивает число искаженных каналов с заданным, и при превышении порога на его выходе появляется импульс логической единицы, который переводит БИС 30 в режим изменения сигнала, при этом длительность канального слова остается прежней (а, следовательно, скорость передачи; канальная и циклическая синхронизация передатчиков и приемников системы остаются прежними). За счет увеличения порога квантования БИС 30 расширяет длительность элементарного сигнала, в результате чего его энергия возрастает, а следовательно, возрастает отношение сигнал-шум и соответственно помехоустойчивость системы (5).

Блок 30 работает следующим образом.

В регистры 32, 33 заносится n-разрядное цифровое представление аналогового канального сигнала, поступающего на вход блока 8, причем в регистр 33 записываются h младших разрядов. Под действием синхроимпульсов, поступающих с генератора 38 через ключ 40 на вход переключателя 42, а с его второго выхода через элемент ИЛИ 35 на синхровход регистра 32 информация, записанная в последнем, старшими разрядами через элемент ИЛИ 34 поступает на выход 46 блока и на вход передатчика 9. Одновременно со второго выхода переключателя 42 синхроимпульсы поступают на счетчик 44, имеющий модуль пересчета, равный числу разрядов регистра 32. При заполнении счетчика на его выходе появляется импульс, переключающий триггер 43 в единичное состояние, а последний в свою очередь выдает сигнал на управляющий вход переключателя 42, который в свою очередь пропускает импульсы с генератора 38 на свой первый выход, с которого синхроимпульсы поступают на синхровход регистра 33. Под воздействием синхроимпульсов с регистра 33 через элемент ИЛИ 34 на выход поступают оставшиеся младшие разряды цифрового представления канального сигнала. Период следования синхроимпульсов с генератора 38 равен Тс Тк/n, где Тк длительность канального слова, n число разрядов представления АЦП 8.

При превышении уровня мощности помех заданного значения с блока 28 сравнения на второй вход 48 БИС поступает сигнал логической "1", которые изменяет состояние триггера 36 на противоположное и соответственно ключ 40 закрывается, а ключ 41 открывается под действием управляющих сигналов с триггера 36. Теперь синхроимпульсы с генератора 39 через ключ 41 и элемент 35 ИЛИ поступает на синхровход регистра 32, и с него считываются для передачи n-h старших разрядов цифрового представления сигнала. Частота следования импульсов генератора 39 в  раз меньше частоты следования импульсов с генератора 38. Благодаря этому, длительность элементарного сигнала (и его энергия) возрастает в

раз меньше частоты следования импульсов с генератора 38. Благодаря этому, длительность элементарного сигнала (и его энергия) возрастает в  раз, при этом длина канального слова и мощность излучения остаются прежними. Таким образом, при ухудшении помеховой обстановки каждый сигнал передается меньшим количеством разрядов (порог квантования возрастает), благодаря этому появляется возможность увеличить длительность элементарного разряда и соответственно повысить энергию элементарного сигнала, что обеспечивает повышение помехоустойчивости передачи.

раз, при этом длина канального слова и мощность излучения остаются прежними. Таким образом, при ухудшении помеховой обстановки каждый сигнал передается меньшим количеством разрядов (порог квантования возрастает), благодаря этому появляется возможность увеличить длительность элементарного разряда и соответственно повысить энергию элементарного сигнала, что обеспечивает повышение помехоустойчивости передачи.

Через определенный (требуемый, исходя из условий применения системы) промежуток времени, равный величине задержки элемента 37, триггер 36 установится в прежнее состояние, и система будет кодировать канальные слова вновь полными n-разрядными комбинациями. Величина τ3выбирается, исходя из практических соображений.

Блок 5 функционирует следующим образом. С второго выхода синхронизатора 49 импульсы канальной частоты поступают на второй выход 53 блока и вход делителя 50. Коэффициент деления делителя 50 выбран таким образом, чтобы период следования импульсов на его выходе (и третьем выходе 52 блока 5 соответственно) был равен необходимому интервалу времени накопления числа каналов, ошибка в которых превышает заданную, производимого в счетчике 27.

Блок 4 функционирует следующим образом. На его входы 62 непрерывно поступают суммарные сигналы ошибок всех каналов. Дешифратор 57 и счетчик 56 образует распределитель импульсов для поочередного открывания ключей 54 первой группы, на вход счетчика 56 поступают тактовые импульсы с тактового входа блока 4. Ключи 54 последовательно открываются импульсами, поступающими с соответствующего выхода дешифратора 57 и суммарный сигнал ошибки каждого канала поступает через элемент ИЛИ 58 на первый вход блока 59 сравнения, на второй вход которого поступает заданное значение максимальной ошибки с установочного входа 60. В случае превышения суммарной ошибки канала заданной, на выходе блока 59 возникает импульс "1", который подается на вторые входы ключей 55 второй группы, Эта единица проходит только через тот ключ на выходе блока 4, на который в данный момент времени был подан разрешающий сигнал с выхода дешифратора.

Таким образом, в блоке 4 одновременно открываются определенный входной ключ и соответствующий ему выходной ключ канала. Моменты времени сравнения блока 59 засинхронизированы по его синхровходу с синхровхода 63.

Таким образом, после воздействия помех система интервал времени τ3работает с элементарными сигналами повышенной энергии, по истечении которого возвращается в исходное состояние. Выбором величины τ3 можно находить компромисс между точностью передачи и помеховой обстановкой.

При оценке технико-экономического эффекта нетрудно показать, что увеличение длительности элементарного сигнала позволяет на 30% увеличить его энергию. Это приведет к росту отношения сигнал-шум на такую же величину и соответственно к увеличению помехоустойчивости системы. В общем случае выигрыш в увеличении отношения сигнал-шум можно представить в виде:

η  где h количество разрядов, на которое было уменьшено канальное представление слова.

где h количество разрядов, на которое было уменьшено канальное представление слова.

Система передачи, как видно из описания ее работы, не вносит задержек при передаче сигналов за счет перезапросов, так как сформированные существенные отсчеты в передающей части направляются в канал связи непосредственно, а на приемной стороне выдаются потребителю в темпе поступления, что повышает информативность системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ ПАКЕТОВ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043658C1 |

| Устройство для контроля телеметрической информации | 1980 |

|

SU920814A1 |

| Адаптивный коммутатор системы телеизмерений | 1980 |

|

SU886032A1 |

| Передающее устройство телеизмерительной системы | 1986 |

|

SU1483476A1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

| Устройство для исследования сетей Петри | 1990 |

|

SU1709350A2 |

| Передающее устройство адаптивной телеизмерительной системы | 1981 |

|

SU955164A1 |

| Адаптивная телеметрическая система | 1978 |

|

SU765854A1 |

| Устройство для передачи и приема дескретных сообщений | 1990 |

|

SU1786669A1 |

| Устройство для исследования сетей Петри | 1990 |

|

SU1809448A1 |

Изобретение относится к телемеханике, в частности к системам передачи с информационной обратной связью, может найти применение в технике связи и телеметрии в условиях с повышенным уровнем мощности помех. Цель изобретения повышение помехоустойчивости системы передачи информации за счет увеличения энергии канальной посылки без возрастания мощности излучения. Система передачи информации содержит датчики 1, преобразователь 2 погрешности аппроксимации, сумматор 3, анализатор 4 погрешности аппроксимации, синхронизатор 5, шифратор 6, коммутатор 7, аналого-цифровой преобразователь 8, передатчик 9, линию прямого 10 канала, приемник 11, передачтик 12, линию обратного 13 канала, приемник 14, селекторы 15 и 16 кода, цифроаналоговый преобазователь 17, формирователь 18 и 24 импульсов сброса, блоки 19, 23 памяти, блоки 20, 21 и 25 ключей, блок 22 вычитания, элемент ИЛИ 26, счетчик 27, блок 28 сравнения, регистры 29, 31, блок изменения 30 сигнала, содержащий регистры, элементы ИЛИ, два триггера, элемент задержки, генераторы импульсов, ключи, переключатель, счетчики. Система передачи не вносит задержек при передаче сигналов за счет переспросов, так как сформированные существенные отсчеты в передающей части направляются в канал непосредственно, а на приемной стороне выдаются потребителю в темпе поступления, что повышает информативности системы. 2 з. п. ф-лы, 4 ил.

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР N 1501786, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1995-09-10—Публикация

1991-06-24—Подача