Изобретение относится к автоматике и вычислительной технике, а именно к оптоэлектронным элементам матрицы для выделения контура изображения, а также к элементам, выполняющим логические операции, и является усовершенствованием изобретения по авт.св. № 1439637.

Цель изобретения - расширение функциональных возможностей путем выполнения логических операций с двумя изображениями.

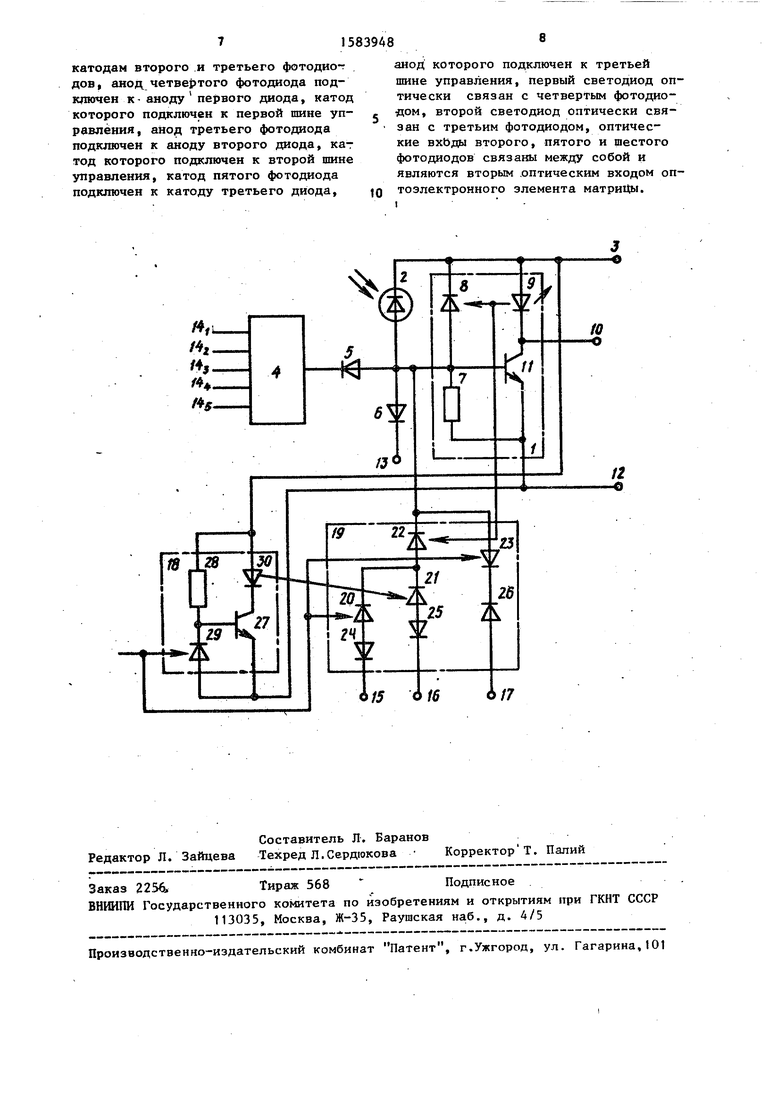

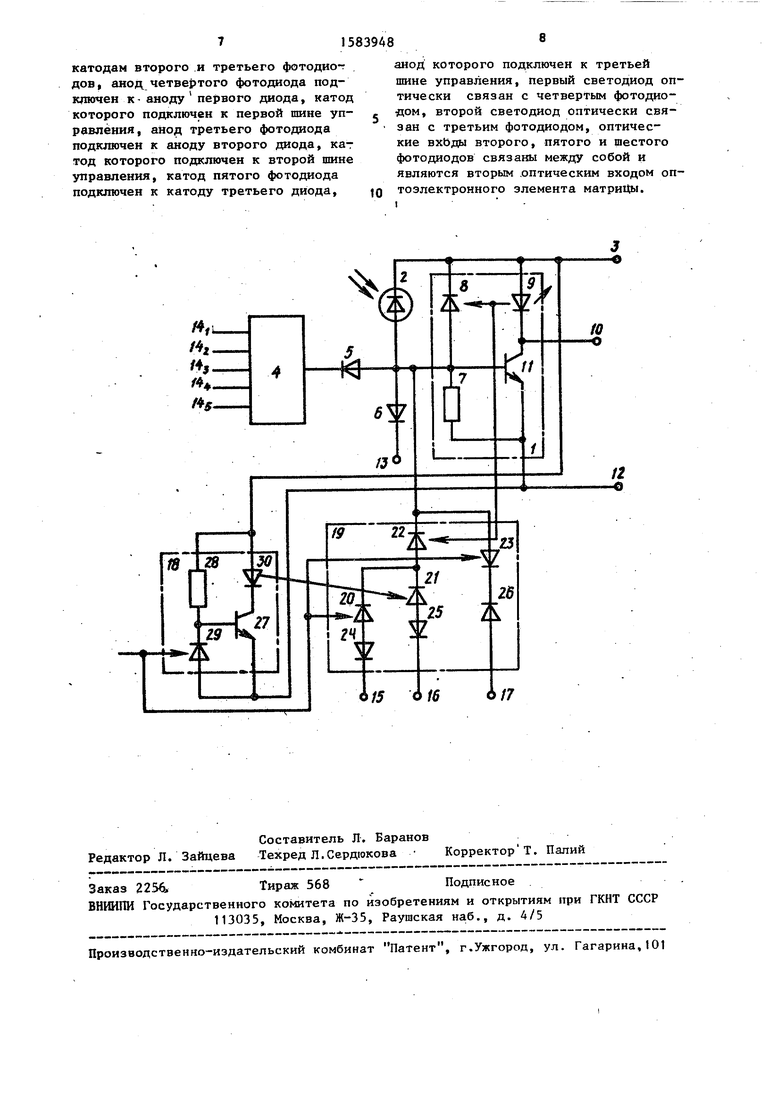

На чертеже представлена функциональная блок-схема устройства.

Оптозлектронный элемент матрицы для выделения контура изображения содержит запоминающий элемент 1, фотоприемный элемент 2, шину 3 питания,

элемент ИЛИ 4, выпрямительные элементы 5 и 6, первый резистор 7, первый фотодиод 8, первый светодиод 9, выходную шину 10, транзистор 11, шину 12 нулевого потенциала, шину 13 установки элемента матрицы в исходное состояние, входы ,-, первые четыре из которых подключаются к выходам смежных оптоэлектронных элементов, а пятый соединяется с входом выделения контура матрицы, три шины ,15-17 управления, блок 18 инвертирования оптического сигнала, блок 19 формирования логических функций, второй - пятый фотодиоды 20-23, три диода 24-26, второй транзистор 27, второй резистор 28, шестой фотодиод 29, второй светодиод 30.

сд

00 00 С.О 4 00

к

Оптоэлектронный элемент матрицы для выделения контура изображения может работать в четырех режимах: режим выделения контура изображения; режим выполнения операции дизъюнкции режим выполнения операции конъюнкции режим выполнения операции сложения пс модулю два.

Выделение контура бинарного изображения осуществляется путем выделения возбужденного оптоэлектронного элемента матрицы, у которого хотя бы один из четырех соседних (смежных ) элементов Является невозбужденным (неосвещенным), В данном режиме на второй оптический вход оптический сигнал не подается, а на шинах 15-17 управления могут присутствовать любые сигналы.

Если на фотоприемный элемент 2 попадает свет, то от шины 3 питания через него начинает протекать ток. В результате на базе транзистора 11 запоминающего элемента 1 создается напряжение, отпирающее его (транзистор 11 открывается ). Светодиод 9, подавая свет на фотодиод 8, включает его, тем самцм реализуя положительную обратную связь. Это приводит к тому, что на базу транзистора 11 че рез фотодиод 8 протекает ток, удерживая транзистор 1 постоянно в режиме смещения. На его коллекторе появляется нулевой сигнал, который подается на выходную шину 10.

Если все смежные с данным опто- электронные элементы матрицы возбуждены (освещены),, то на входах 14 - 14 . элемента 4 ИЛИ присутствуют логические О. Если на пятом входе 14,присутствует логический О1 , то с

ш О, выхода элемента ИЛИ 4 логический О поступает на катод первого выпрямительного элемента 5, в результате чего шунтируется переход база - эмиттер транзистора 11, и данный элемент матрицы обнуляется. Если элемент матрицы не был возбужден, то остается в том же состоянии о В случае присутствия хотя бы на одном входе 14,|-144 элемента 4 ИЛИ логической 1 изменения состояния оптоэлектронного элемента не происходит. Если на пятом входе 14 элемента 4 ИЛИ присутствует логическая 1, то выделение контура не происходит.

Для установки оптоэлектронного элемента в начальное состояние на ши

5

0

5

0

ну 13 подается нулевой потенциал, поступающий на катод второго выпрямительного элемента 6, в результате чего транзистор 11 запирается. Светодиод 9 служит также для внешней индикации результата, а резистор 2 смещения служит для задания напряжения смещения на базе транзистора 11.

В режиме выполнения операции дизъюнкции (логическое сложение) на все три шины 15-17 управления и пятый вход элемента 4 ИЛИ подаются высокие положительные потенциалы. Включение первого и второго диодов 24 и 25 блока 19 формирования логических функций не дает возможности протекания тока в базу транзистора 11 от первой и второй пин 1 5 и 1 6 управления .

Операция дизъюнкции производится с сигналом, поступакщим на второй оптический вход, и с собственным состоянием запоминающего элемента i (сигналом на выходе светодиода 9)9 а результат получается на выходе запоминающего элемента 1 (состояние светодиода 9), Присутствие оптического сигнала на втором оптическом входе либо на светодиоде 9 соответствует логической 1, а отсутствие - логическому О. Если присутствует два логических 0 то элемент матрицы остается в том же состоянии (логичен

кий О). Если на светодиоде 9 присутствует оптический сигнал (логическая ), а на втором оптическом

входе логический О,

то элемент ос0

5

0

5

тается в состоянии логической 1, при этом транзистор 27 блока 18 инвертирования оптического сигнала открыт и первый светодиод 30 этого же блока 18 горит за счет протекания тока от шины 3 питания через резистор 28 в базу транзистора 27.

В случае, если на втором оптическом входе присутствует оптический сигнал, а на светодиоде 9 не присутствует, то запоминающий элемент 1 переходит в состояние логической 1 (светодиод 9 горит) за счет того, что с второго оптического входа на пятый фотодиод 23 поступает оптический сигнал, и ток протекает от третьей шины 17 управления через третий диод 26 и пятый фотодиод 23 в базу транзистора 11, отпирая его.

В случае присутствия двух логичес1 ких 1, элемент матрицы остается в том же состоянии.

В режиме выполнения операции конъюнкции на первую, вторую и третью шины 15-17 управления подаются соответственно единичный, нулевой и нулевой потенциалы напряжения.

Если присутствует два логических О, то элемент матрицы остается в состоянии логического О.

Если на светодиоде 9 присутствует оптический сигнал, а на втором оптическом входе не присутствуем (комбинация 10), то элемент матрицы переходит в состояние логического О, так как оптический сигнал от светодиода 9 поступает на фотодиод 22 блока 19, а транзистор 27 блока 18 открыт, и от светодиода 30 свет -поступает на фотодиод 21 блока 19.

Открытые фотодиоды 21 и 22 блока 19 шунтируют переход база - эмиттер транзистора 11, запирая его. Ток будет протекать не в базу транзистора 11, а через фотодиоды 22 и 21 и второй диод 25 к второй шине 16 управления .

В случае, если на втором оптическом входе присутствует оптический сигнал, а на светодиоде 9 не присутствует (комбинация 01), то элемент матрицы остается в состоянии логического О, а транзистор 27 блока 18 заперт, так как на его фотодиоде 29 присутствует свет, который шунтирует переход база - эмиттер транзистора 27 и запирает его.

Если присутствует комбинация 1 , то элемент матрицы остается в состоянии логической 1, так как третий диод 26 включен так, что не допускает протекания тока к третьей шине 7 управления.

В режиме выполнения операции сложения по модулю два на третью и вторую шины 17 и 16 подается высокий положительный потенциал, а на первую шину 15 управления - нулевой потенг циал.

Если присутствует комбинация 00, то элемент матрицы остается в состоянии логического О. Если присутствует комбинация 10, то элемент матрицы остается в состоянии логической 1, так как нет при данной комбинации цепи обнуления.

В случае присутствия комбинации 015 на фотодиоде 23 присутствует свет и ток Аротекает от третьей шины 17 управления через третий диод 26 и фо

0

0

5

5

0

5

0

5

0

5

тодиод 23 в транзистора 11, отпирая его. Элемент матрицы переходит в состояние логической .

В случае присутствия комбинации 11, на фотодиодах 20 и 22 блока 19 присутствует свет, который переводит их в проводящее состояние. Через них и первый диод 24 протекает ток, запирая транзистор 11. Злемент матрицы переходит в состояние логического О. Блок 18 инвертирования оптического сигнала выполняет инверсию оптического сигнала на втором оптическом входе, а блок 19 формирования логических функций реализует основные логические функции и управляет состоянием транзистора 11.

Под нулевыми потенциалами, подающимися на шкны 15-17 управления, подразумеваются такие, которые достаточны для запирания транзистора 11.

Изобретение по сравнению с известным обладает широкими функциональными возможностями за счет того, что с его помощью появляется возможность параллельно выполнять операции конъюнкции, дизъюнкции и сложения по модулю два с двумя бинарными изображениями, а результат представляется на этой же матрице.

Формула изобретения

Оптоэлектронный элемент матрицы для выделения контура изображения по авт. св. К 1439637, отличающийся тем, что, с целью расширения функциональных возможностей путем выполнения логических операций с двумя изображениями, в него введены блок формирования логических функций, содержащий второй - пятыл фотодиоды и три диода, и блок инвертирования оптического сигнала, содержащий шестой фотодиод7второй резистор, второй светодиод и второй транзистор, коллектор которого подключен к катоду второго светодиода, анод которого подключен к шине питания и к первому выводу второго резистора, другой вывод которого подключен к базе второго транзистора и катоду шестого фотодиода, анод которого подключен к эмиттеру второго транзистора и шине нулевого потенциала, база первого транзистора подключена к аноду пятого фотодиода и катоду четвертого фотодиода, анод которого подключен к

катодам второго и третьего фотодио дов, анод четвертого фотодиода подключен к - аноду первого диода, катод которого подключен к первой шине управления, анод третьего фотодиода подключен к аноду второго диода, кат тод которого подключен к второй шине управления, катод пятого фотодиода подключен к катоду третьего диода,

39488

анод которого подключен к третьей шине управления, первый светодиод оптически связан с четвертым фотодио, дом, второй светодиод оптически свя- зан с третьим фотодиодом, оптические входы второго, пятого и шестого фотодиодов связаны между собой и являются вторым оптическим входом опJQ тоэлектронного элемента матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный элемент матрицы для выделения контура изображения | 1987 |

|

SU1439637A1 |

| Устройство для выделения контуров изображения | 1988 |

|

SU1501106A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1515366A1 |

| Устройство для измерения длины участков контура изображения | 1988 |

|

SU1633435A1 |

| Электронные часы с псевдострелочной индикацией | 1989 |

|

SU1653157A1 |

| Шахматные часы | 1988 |

|

SU1693619A1 |

| Оптоэлектронное устройство для логической обработки информации | 1987 |

|

SU1476503A1 |

| Устройство для логической обработки изображений | 1989 |

|

SU1711201A1 |

| Шкальный индикатор напряжения | 1987 |

|

SU1492295A1 |

| Элемент индикации с памятью | 1983 |

|

SU1133616A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам для обработки изображений. Цель изобретения - расширение функциональных возможностей за счет выполнения логических операций с двумя изображениями. Поставленная цель достигается введением блока формирования логических функций и блока инвертирования оптического сигнала. Оптоэлектронный элемент матрицы для выделения контура изображения работает в четырех режимах: - режим выделения контура

режим выполнения операции дизъюнкции

режим выполнения операции конъюнкции

режим выполнения операции сложения по модулю два. Выбор режима осуществляется комбинацией сигналов на шинах управления и на пятом входе элемента ИЛИ. 1 ил.

| Оптоэлектронный элемент матрицы для выделения контура изображения | 1987 |

|

SU1439637A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-07—Публикация

1988-06-01—Подача