1

Изобретение относится к автоматике и вычислительной технике, а именно к оптоэлектронным устройствам для логической обработки информации. ,

Цель изобретения - расширение области применения устройства за счет увеличения количества решаемых задач.

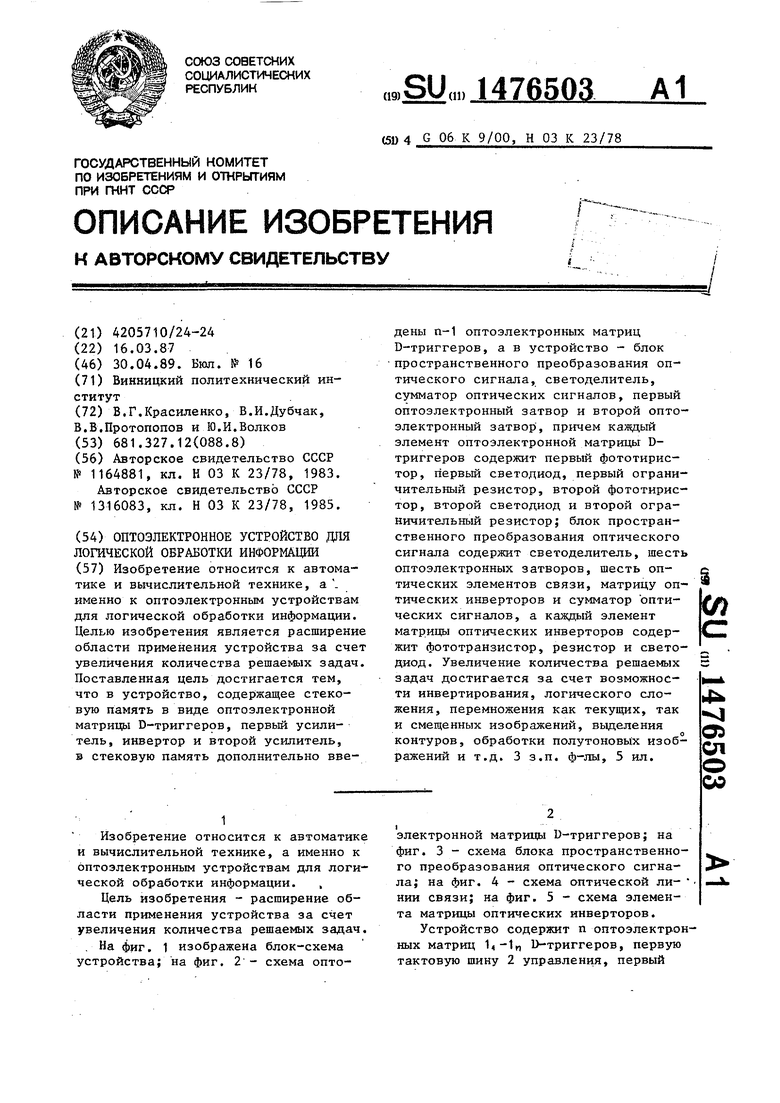

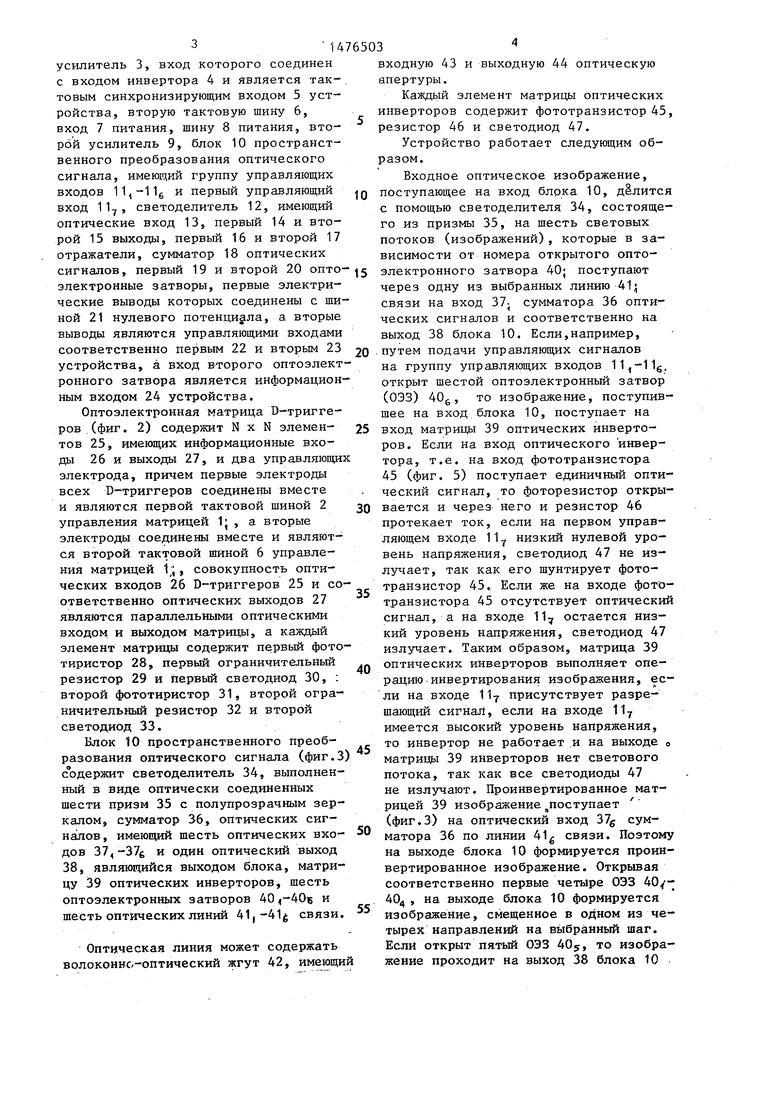

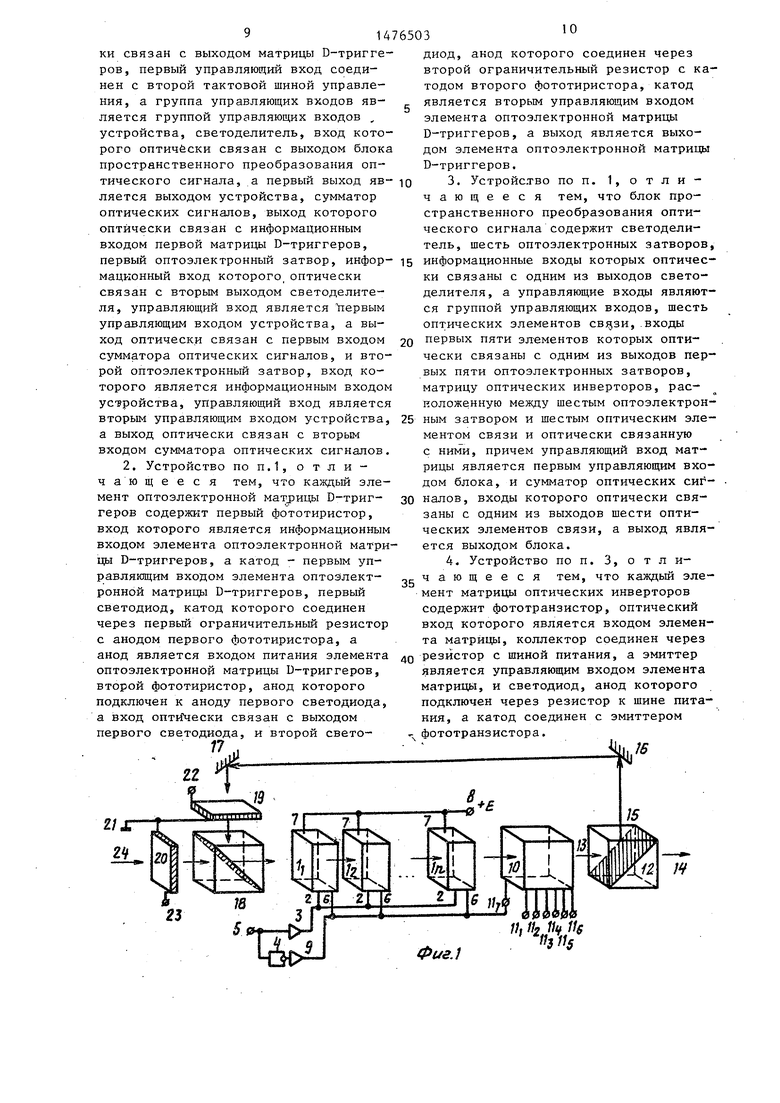

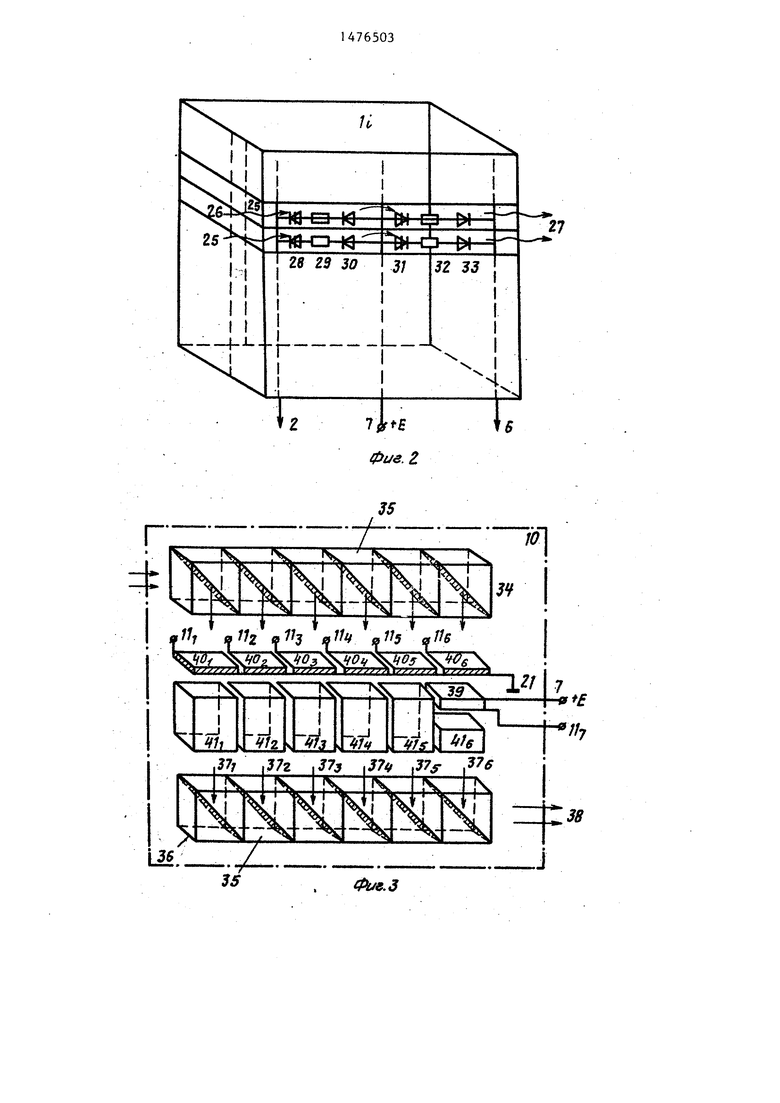

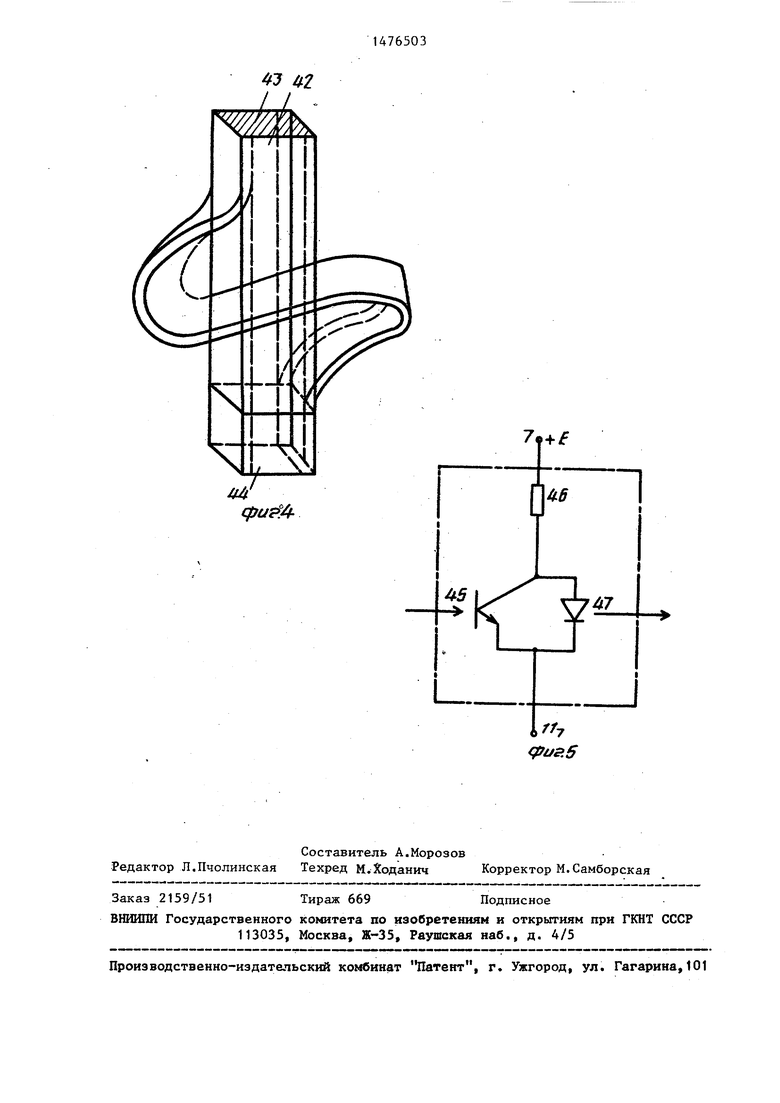

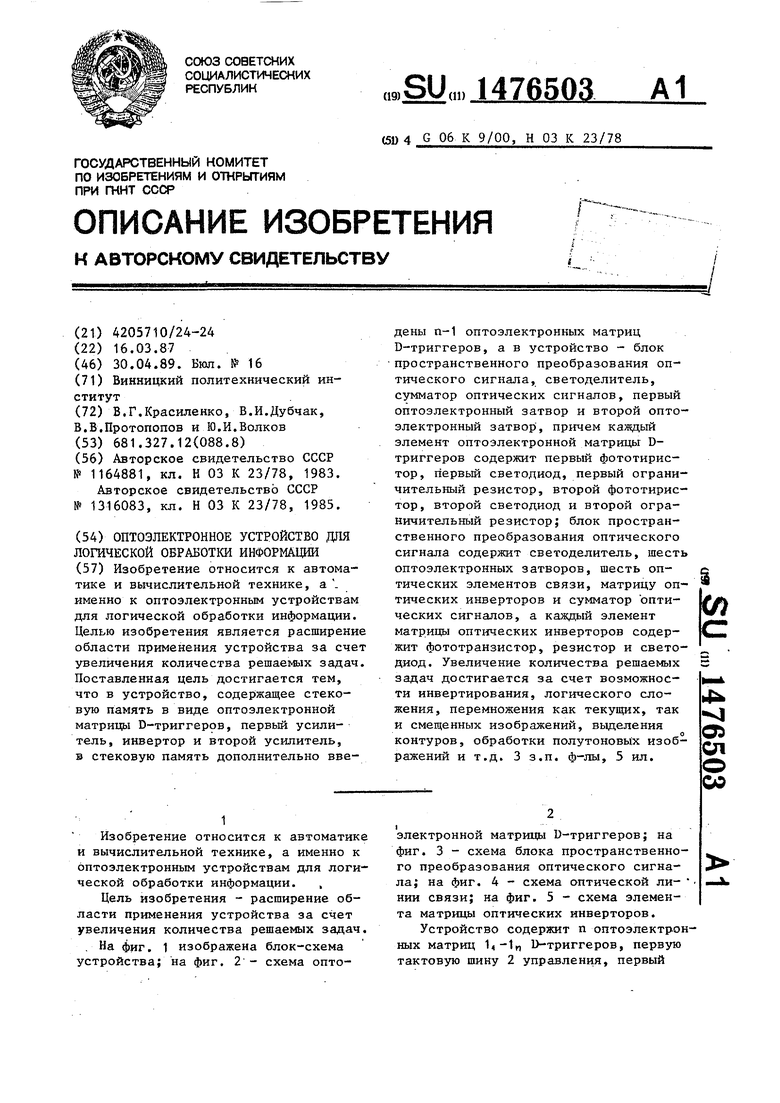

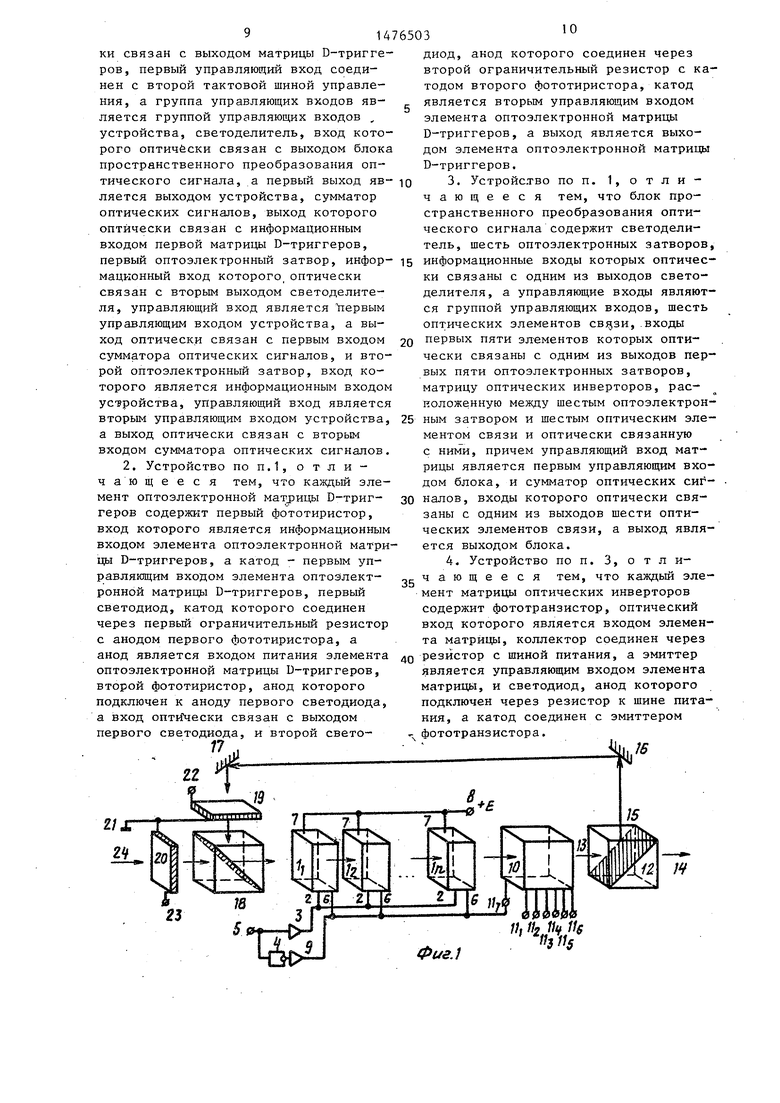

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - схема оптоэлектронной матрицы D-триггеров; на фиг. 3 - схема блока пространственного преобразования оптического сигнала; на фиг. 4 - схема оптической ли- нии связи; на фиг. 5 - схема элемента матрицы оптических инверторов.

Устройство содержит п оптоэлектронных матриц 1«-1п D-триггеров, первую тактовую шину 2 управления, первый

усилитель 3, вход которого соединен с входом инвертора 4 и является тактовым синхронизирующим входом 5 устройства, вторую тактовую шину 6, вход 7 питания, шину 8 питания, второй усилитель 9, блок 10 пространственного преобразования оптического сигнала, имеющий группу управляющих входов 11,-116 и первый управляющий вход 117, светоделитель 12, имеющий оптические вход 13, первый 14 и второй 15 выходы, первый 16 и второй 17 отражатели, сумматор 18 оптических

сигналов, первый 19 и второй 20 опто- jg электронного затвора 40; поступают

электронные затворы, первые электрические выводы которых соединены с шиной 21 нулевого потенциала, а вторые выводы являются управляющими входами соответственно первым 22 и вторым 23 JQ устройства, а вход второго оптоэлект- ронного затвора является информационным входом 24 устройства,

Оптоэлектронная матрица D-триггеров (фиг. 2) содержит N х N элемен- 25 тов 25, имеющих информационные входы 26 и выходы 27, и два управляющих электрода, причем первые электроды всех D-триггеров соединены вместе и являются первой тактовой шиной 2 управления матрицей 1| , а вторые электроды соединены вместе и являются второй тактовой шиной 6 управления матрицей 1;, совокупность оптических входов 26 D-триггеров 25 и соответственно оптических выходов 27 являются параллельными оптическими входом и выходом матрицы, а каждый элемент матрицы содержит первый фототиристор 28, первый ограничительный резистор 29 и первый светодиод 30, : второй фототиристор 31, второй ограничительный резистор 32 и второй светодиод 33.

Блок 10 пространственного преоб30

35

40

через одну из выбранных линию 41 связи на вход 37 сумматора 36 опти ческих сигналов и соответственно на выход 38 блока 10. Если,например, путем подачи управляющих сигналов на группу управляющих входов 11f-11 открыт шестой оптоэлектронный затво (ОЭЗ) 406, то изображение, поступи шее на вход блока 10, поступает на вход матрицы 39 оптических инверторов. Если на вход оптического инвер тора, т.е. на вход фототранзистора 45 (фиг. 5) поступает единичный опт ческий сигнал, то фоторезистор откр вается и через него и резистор 46 протекает ток, если на первом управ ляющем входе 11 низкий нулевой уро вень напряжения, светодиод 47 не из лучает, так как его шунтирует фототранзистор 45. Если же на входе фот транзистора 45 отсутствует оптическ сигнал, а на входе 117 остается низ кий уровень напряжения, светодиод 4 излучает. Таким образом, матрица 39 оптических инверторов выполняет опе рацию инвертирования изображения, е ли на входе 117 присутствует разрешающий сигнал, если на входе 117 имеется высокий уровень напряжения, то инвертор не работает и на выходе

- -к- - х - --сд ППОС. }J J ПО ±iCLU J 1 ОС- I П J1CL J3Oljb.W,U,Cразования оптического сигнала (фиг.З) матрицы 39 инверторов нет светового

содержит светоделитель 34, выполненный в виде оптически соединенных шести призм 35 с полупрозрачным зеркалом, сумматор 36, оптических сигналов, имеющий шесть оптических входов и один оптический выход 38, являющийся выходом блока, матрицу 39 оптических инверторов, шесть оптоэлектронных затворов 40 -40в и шесть оптических линий 41, -41$ связи.

Оптическая линия может содержать волоконно-оптический жгут 42, имеющий

50

55

потока, так как все светодиоды 47 не излучают. Проинвертированное мат рицей 39 изображение опоступает (фиг.З) на оптический вход 37б сумматора 36 по линии 41g связи. Поэтом на выходе блока 10 формируется проин вертированное изображение. Открывая соответственно первые четыре ОЭЗ 40 404, на выходе блока 10 формируется изображение, смещенное в одном из че тырех направлений на выбранный шаг. Если открыт пятый ОЭЗ 405, то изобра жение проходит на выход 38 блока 10

0

входную 43 и выходную 44 оптическую апертуры.

Каждый элемент матрицы оптических инверторов содержит фототранзистор 45, резистор 46 и светодиод 47.

Устройство работает следующим образом.

Входное оптическое изображение, поступающее на вход блока 10, делится с помощью светоделителя 34, состоящего из призмы 35, на шесть световых потоков (изображений), которые в зависимости от номера открытого оптоg электронного затвора 40; поступают

Q

5

0

5

0

через одну из выбранных линию 41 связи на вход 37 сумматора 36 оптических сигналов и соответственно на выход 38 блока 10. Если,например, путем подачи управляющих сигналов на группу управляющих входов 11f-11g. открыт шестой оптоэлектронный затвор (ОЭЗ) 406, то изображение, поступившее на вход блока 10, поступает на вход матрицы 39 оптических инверторов. Если на вход оптического инвертора, т.е. на вход фототранзистора 45 (фиг. 5) поступает единичный оптический сигнал, то фоторезистор открывается и через него и резистор 46 протекает ток, если на первом управляющем входе 11 низкий нулевой уровень напряжения, светодиод 47 не излучает, так как его шунтирует фототранзистор 45. Если же на входе фототранзистора 45 отсутствует оптический сигнал, а на входе 117 остается низкий уровень напряжения, светодиод 47 излучает. Таким образом, матрица 39 оптических инверторов выполняет операцию инвертирования изображения, если на входе 117 присутствует разрешающий сигнал, если на входе 117 имеется высокий уровень напряжения, то инвертор не работает и на выходе „

ППОС. }J J ПО ±iCLU J 1 ОС- I П J1CL J3Oljb.W,U,Cматрицы 39 инверторов нет светового

0

5

потока, так как все светодиоды 47 не излучают. Проинвертированное матрицей 39 изображение опоступает (фиг.З) на оптический вход 37б сумматора 36 по линии 41g связи. Поэтому на выходе блока 10 формируется проин- вертированное изображение. Открывая соответственно первые четыре ОЭЗ 40/- 404, на выходе блока 10 формируется изображение, смещенное в одном из четырех направлений на выбранный шаг. Если открыт пятый ОЭЗ 405, то изображение проходит на выход 38 блока 10

без преобразований и смещений. Если открыты несколько затворов, то на выходе 38 блока 10 формируется изображение, соответствующее суммированию световых потоков, преобразованных в каждом канале изображений. Например, если открыты все четыре ОЭЗ 40,-АОд., то на выходе 38 имеется г

476503о

на входе 5 тактовый сигнал синхронизации отсутствует, шика 2 D-тригге- ра 25 и всей матрицы 1; оторвана от шины 21 нулевого потенциала. Поэтому левое плечо D-триггера 25, состоящее из фототиристора 28, резистора 29 и светодиода 30, находится в непроводящем состоянии, правое плечо, сос

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения квадратных матриц картин-изображений | 1989 |

|

SU1781679A1 |

| Оптоэлектронный модуль | 1987 |

|

SU1432768A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Устройство для коммутации оптических бинарных изображений | 1989 |

|

SU1795439A1 |

| Оптоэлектронный сдвигающий регистр | 1987 |

|

SU1425784A1 |

| Шкальный индикатор напряжения | 1987 |

|

SU1552109A1 |

| Шахматные часы | 1988 |

|

SU1693619A1 |

| Устройство логической обработки изображений | 1988 |

|

SU1645974A1 |

| Оптоэлектронное устройство для логической обработки информации | 1987 |

|

SU1553995A1 |

| Оптоэлектронное устройство для логической обработки изображений | 1989 |

|

SU1691859A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к оптоэлектронным устройствам для логической обработки информации. Целью изобретения является расширение области применения устройства за счет увеличения количества решаемых задач. Поставленная цель достигается тем, что в устройство, содержащее стековую память в виде оптоэлектронной матрицы D-триггеров, первый усилитель, инвертор и второй усилитель, в стековYю память дополнительно введены п-1 оптоэлектронных матриц D-триггеров, и в устройство - блок пространственного преобразования оптического сигнала, светоделитель, сумматор оптических сигналов, первый оптоэлектронный затвор и второй оптоэлектронный затвор, причем каждый элемент оптоэлектронной матрицы D-триггеров содержит первый фототиристор, первый светодиод, первый ограничительный резистор, второй фототиристор, второй светодиод и второй ограничительный резистор, блок пространственного преобразования оптического сигнала содержит светоделитель, шесть оптоэлектронных затворов, шесть оптических элементов связи, матрицу оптических инверторов и сумматор оптических сигналов, а каждый элемент матрицы оптических инверторов содержит фототранзистор, резистор и светодиод. Увеличение количества решаемых задач достигается за счет возможности инвертирования, логического сложения, перемножения как текущих так и смещенных изображений, выделения контуров, обработки полутоновых изображений и т.д. 3 з.п. ф-лы, 5 ил.

изображение, соответствующее логичес- -|0 ТОящее из фототиристора 31, резистокому сложению четырех изображений, смещенных во всех четырех направлениях (аналог операции ИЛИ).

Требуемый режим преобразования ч,, блоком 10 задается комбинацией сигна лов на группе управляющих входов 11,- и первом управляющем входе 11

11,i6 и первом управляющем входе ii7

В блок 10 в некоторых случаях целесообразно вводить усилитель изображения (например, электронно-оптичес- кий преобразователь, преобразователь изображений на основе многослойных фоточувствительных, электрооптических и электрономинесцентных структур) , который необходим для усиления изображения до требуемого уровня, так как блок 10, а именно светоделители, и остальные узлы вносят затухание и значительно ослабляют сигнал. Если фоточувствительность оптических D-триггеров велика и достаточна для его срабатьюания с учетом вносимых затуханий по оптическому тракту, то такого усилителя не требуется. Кроме того, с целью согласования блока 10 с выходом последней матрицы, а также матрицы 39 оптических инверторов в блок 10 могут вводиться объективы с коллиматором, что позволяет устранить эффекты рассеивания пучка света.

Оптоэлектронная матрица D-триггеров (фиг. 2) позволяет записывать, вводить, хранить и передавать на сле- дующую матрицу одно бинарное изображение или один бинарный срез полутонового изображения, представленного срезами.

D-триггер 25 и вся матрица 1; работают следующим образом.

При отсутствии тактового сигнала на входе 5 устройства усилитель 3, работающий в ключевом режиме, формирует на выходе, а значит, и на шине 2 высокий уровень напряжения. Посредством инвертора 4 на выходе второго усилителя 9, а значит, и на шине 6 формируется низкий уровень напряжения, т.е. ключевые усилители 3 и 9 работают как прерыватели тока. Пока

jg

20

25

ра 32 и светодиода 33, может находиться как в проводящем, так и в непроводящем состоянии.

При подаче тактового импульса синхронизации на вход 5 устройства происходит переключение прерывателей тока на основе усилителей 3 и 9. Если на оптическом входе 26 D-триггера присутствовал единичный оптический сигнал и фототиристор 28 был им подготовлен к выключению, то при подаче тактового импульса синхронизации на время его действия включается левое плечо D-триггера 25. При этом фототиристор 28 переходит в проводящее состояние и начинает излучать свето- диод 30. Правое плечо на время действия импульса независимо от предыдущего состояния переходит в непроводя- 30 щее состояние. По заднему фронту тактового импульса синхронизации, поступившему на вход 5 устройства, происходит обратное переключение усилителей 3 и 9, в результате чего информация с левого плеча D-триггера переписывается в правое,так как светодиод 30 оптически связан с фототиристором 31 и подготавливает его к выключению за время действия тактового импульса. D-триггер 25 работает, как MS-двух- тактная структура, что обеспечивает надежность и достоверность функционирования оптоэлектронного D-тритге- ра 25.

Оптоэлектронные матрицы 1,-1„ (фиг. 1) D-триггеров служат для запоминания, хранения и поочередного сдвига п бинарных изображений. Для ввода изображений в устройство открывается ОЭЗ 20 путем подачи соответствующего напряжения на вход 23. Импульсы синхронизации подаются на вход 5 устройства.

После подачи п тактовых импульсов заканчивается ввод п бинарных изображений. Если на информационном входе 24 на время действия всех п тактовых импульсов изображение не изменяется, то в устройство вводятся п одинаковых

35

40

45

50

55

кадров изображения. После ввода изображений посредством подачи сигнала на вход 22 устройства и открывания вследствие этого ОЭЗ 19, закрывания 033 20 и подачи сигналов на группу управляющих входов 11,,-116 устанавливается один из режимов работы устройства по обработке изображений. Если, например, сигналы на входах 11,,- 11б таковы, что блок 10 не преобразует не смещает изображения, то при поаче тактовых импульсов на вход 5 устойства происходит циклический сдвиг сех изображений внутри устройства, результате чего на выходе 16 устойства наблюдается результирующее олутоновое изображение, если частота сдвига выше критической частоты мерцаний. Если частота следования типовых импульсов небольшая, то можно визуально наблюдать все бинарные текущие срезы изображений. Если блок 10 инвертирует изображение, то после требуемого числа сдвигов в матрицы 1j записываются проинвертированные изображения. Аналогично каждое из би- наркых изображений путем установки требуемого режима преобразования блоком 10 в момент прохождения через блок 10 может быть преобразовано по требуемому закону, в частности смещенным в одном из четырех направлений.

Для сдвига всех бинарных изображений или результирующего полутонового на один дискрет в нужном направлении необходимо сделать полный циклический сдвиг всех бинарных изображений за время подачи тактовых импульсов синхронизации на вход 5 устройства. Если же необходимо произвести смещение на большое число дискретов, то описанный цикл из импульсов повторяется соответствующее число раз. Уст- Войство позволяет выполнять операцию ИЛИ над изображением и соответствующими ему смещенными изображениями на требуемое число дискретов посредством соответствующего режима в блоке 10. Наличие операции инвертирования изображений совместно с операцией ИЛИ позволяет выполнять операцию поэле-t ментного умножения текущего и смещенных изображений, что позволяет выполнять такие операции над изображением как выделение контуров, подчеркивание границ изображения, выделение движущихся объектов, выделение фрагментов изображения, вычисление корреляционных функций (автокорреляционной и взаимно корреляционной) изобра- жений. Матрица 39 оптических инверторов имеет первый управляющий вход 117, подключенный к второй тактовой шине 6 управления матрицами 1, обеспечивающую синхронную работу матри- Q цы 39. Это необходимо для того,0чтобы в случае выключения правого плеча D-триггера 25 матрица 39 оптических инверторов также выключалась.

Таким образом, увеличение количе5 ства решаемых задач достигается за счет возможности инвертирования, логического сложения, перемножения как текущих, так и смещенных изображений, выделения контуров, обработки полу0 тоновых изображений и т.д.

Формула изобретения

5 1. Оптоэлектронное устройство для логической обработки информации, содержащее стековую память в виде опто- электронной матрицы D-триггеров, вход питания которой соединен с шиной питания, первый управляющий вход подключен к первой тактовой шине управления, а второй управляющий вход соединен с второй тактовой шиной управления, первый усилитель, вход которого является тактовым синхронизирующим входом устройства, а выход подключен к первой тактовой шине управления, инвертор, вход которого соединен с входом первого усилителя, и второй усилитель, вход которого подключен к выходу инвертора, а выход соединен с второй тактовой шиной управления, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения коли- 0 чества решаемых задач, стековая память дополнительно содержит последовательно расположенные оптически связанные между собой и с первой опто- электронной матрицей D-триггеров п-1 оптоэлектронных матриц D-триггеров, входы питания которых подключены к шине питания, первые управляющие входы соединены с первой тактовой шиной управления, а вторые управляющие вхо5 ды подключены к второй тактовой шине управления, блок пространственного преобразования оптического сигнала, инфопмационный вход которого оптичес0

5

0

5

0

20

25

первый оптоэлектронный затвор, инфор- 15 информационные входы которых оптичес- мацконный вход которого,оптически связан с вторым выходом светоделителя, управляющий вход является первым управляющим входом устройства, а выход оптически связан с первым входом сумматора оптических сигналов, и второй оптоэлектронный затвор, вход которого является информационным входом устройства, управляющий вход является вторым управляющим входом устройства, а выход оптически связан с вторым входом сумматора оптических сигналов.

ки связаны с одним из выходов светоделителя, а управляющие входы являются группой управляющих входов, шесть оптических элементов свя,зи, входы первых пяти элементов которых оптически связаны с одним из выходов первых пяти оптоэлектронных затворов, матрицу оптических инверторов, расположенную между шестым оптоэлектрон- ным затвором и шестым оптическим элементом связи и оптически связанную с ними, причем управляющий вход матрицы является первым управляющим входом блока, и сумматор оптических сиг- 30 налов, входы которого оптически связаны с одним из выходов шести оптических элементов связи, а выход является выходом блока.

а ю щ е е с я тем, что каждый элемент матрицы оптических инверторов содержит фототранзистор, оптический вход которого является входом элемента матрицы, коллектор соединен через резистор с шиной питания, а эмиттер является управляющим входом элемента матрицы, и светодиод, анод которого подключен через резистор к шине питания, а катод соединен с эмиттером

.- фототранзистора.

40

2/JT

23

информационные входы которых оптичес-

ки связаны с одним из выходов светоделителя, а управляющие входы являются группой управляющих входов, шесть оптических элементов свя,зи, входы первых пяти элементов которых оптически связаны с одним из выходов первых пяти оптоэлектронных затворов, матрицу оптических инверторов, расположенную между шестым оптоэлектрон- ным затвором и шестым оптическим элементом связи и оптически связанную с ними, причем управляющий вход матрицы является первым управляющим входом блока, и сумматор оптических сиг- налов, входы которого оптически связаны с одним из выходов шести оптических элементов связи, а выход является выходом блока.

а ю щ е е с я тем, что каждый элемент матрицы оптических инверторов содержит фототранзистор, оптический вход которого является входом элемента матрицы, коллектор соединен через резистор с шиной питания, а эмиттер является управляющим входом элемента матрицы, и светодиод, анод которого подключен через резистор к шине питания, а катод соединен с эмиттером

.- фототранзистора.

Фиг.)

W

щ а м

-ьикэ-й28 29 30

I I

Гi

11r 011Z яЩ q11t qtie

ъ/ру гглуугмл гят , тгг,,,,

l

NS: r r rax

,37,

, J7z ./7j ,Д7 .УУ .5

rvl lrvlrKlr H

-w-&

27

31

J2 35

7ЈtЈ fiue.Z

I

J

Фиг.З

«j м

| Оптоэлектронный модуль | 1984 |

|

SU1164881A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Оптоэлектронный многомерный модуль | 1985 |

|

SU1316083A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-30—Публикация

1987-03-16—Подача