Изобретение относится к электротехнике и может быть использовано для управления сумматором тока электродов магнитогидродинамического генератора (МГДГ).

Цель изобретения - повышение надежности работы сумматоров тока электродов МГДГ.

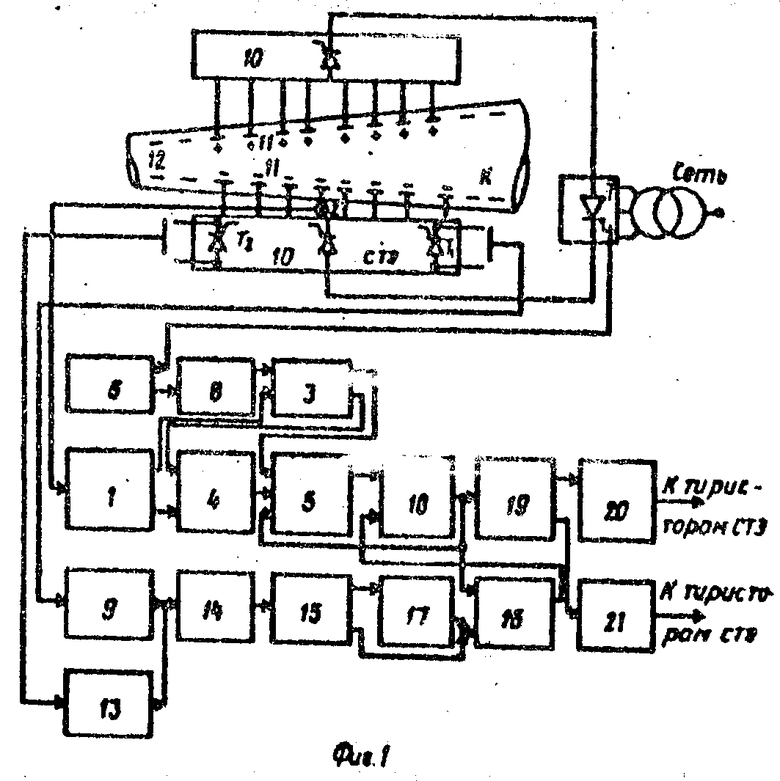

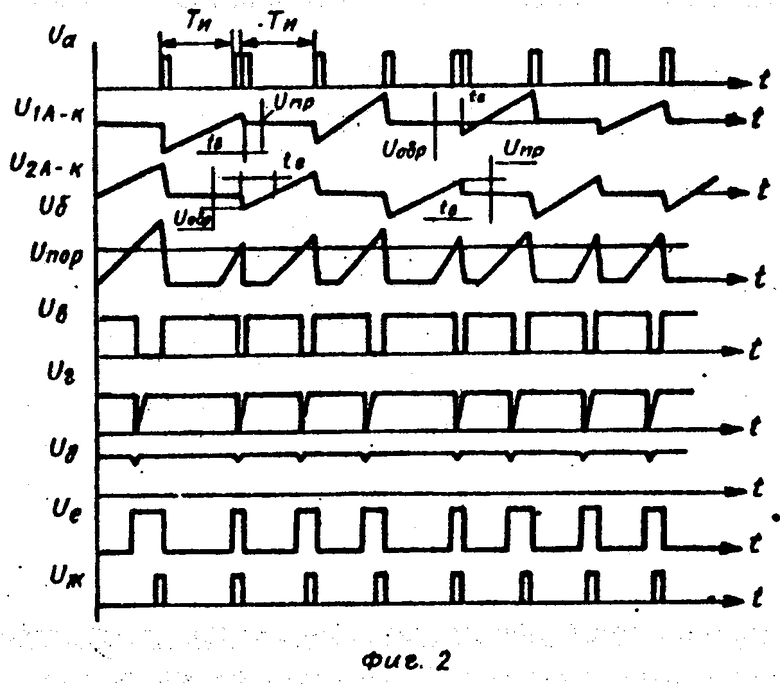

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 даны диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 согласования, вход которого подключен к датчику 2 тока электрода, а первый выход соединен с управляющим входом блока 3 логических переключений, который снабжен импульсным выходом, выходом управления и синхронизирующим входом. Входные и выходные сигналы блока 3 связаны следующими логическими уравнениями:

A +  = C и

= C и  = D где A - сигнал на синхронизирующем входе;

= D где A - сигнал на синхронизирующем входе;

B - сигнал на управляющем входе;

С - cигнал на импульсном выходе;

D - сигнал на выходе управления ключа.

Выход управления блока 3 соединен с управляющим входом ключа 4. Второй выход блока 1 согласования через ключ 4 соединен с регулирующим входом задающего генератора 5, к синхронизирующему входу которого подключен импульсный выход блока 3 логических переключений. Устройство содержит блок 6 формирования импульсов управления сетевым инвертором, первая группа выходов которого предназначена для подключения к управляющим электродам тиристоров сетевого инвертора 7, второй выход через блок 8 формирования синхроимпульсов соединен с синхронизирующим входом блока 3. Первый датчик 9 напряжения, вход которого соединен с анодом и катодом тиристора сумматора 10 тока электродов, включенного в цепь электрода 11, расположенного на одном краю токосъемной зоны МГДГ 12, охватываемой сумматором тока электродов, а второй датчик 13 напряжения подсоединен к аноду и катоду тиристора, работающего в противофазе с первым и включенного в цепь электрода 11, расположенного на другом краю токосъемной зоны МГДГ 12. Выходы датчиков напряжения подключены к входу усилителя 14, выход которого подключен к входу компаратора 15, первый выход которого подключен к входу синхронизации триггера 16. К этому же входу через инвертирующий элемент 17 с задержкой переднего фронта входного импульса подключен второй выход компаратора 15. Выход триггера 16 подключен к первому входу элемента 18 И, к второму входу которого подсоединен выход задающего генератора 5. Выход элемента 18 И подключен к входу делителя 19 частоты на два, к счетному входу триггера 16 и к установочному входу задающего генератора 5.

Причем делитель 19 снабжен двумя выходами, которые через первый выходной каскад 20 и второй выходной каскад 21 предназначены для подключения к управляющим электродам тиристоров сумматора 10 токов электродов.

Устройство работает следующим образом.

Сигнал с выхода блока 6 поступает одновременно на тиристоры инвертора 7 и в блок 8, в котором формируется сигнал, необходимый по длительности и амплитуде для синхронизации задающего генератора 5 через блок 3. Импульсы с выхода задающего генератора 5 поступают через элемент 18 И на делитель 19, который поочередно распределяет их с задающего генератора 5 на выходные каскады 20 и 21, где формируются импульсы управления сумматора 10. Ток от электродов 11 имеющих положительный потенциал, протекает через сумматоры 10, инвертор 7 к электродам 11, имеющим отрицательный потенциал. Сигнал с выхода датчика 2 поступает в блок 1 согласования, где преобразуется в управляющее напряжение Uy, пропорциональное току электрода. Напряжение Uy поступает одновременно в блок 3 и на вход управляющего ключа 4. Последний обеспечивает связь задающего генератора 5 с блоком 1 согласования при достижении током электрода уровня, который определяется блоком 3, в котором напряжение Uyсравнивается с некоторым пороговым значением. В момент равенства указанных величин в блоке 3 отключаются синхроимпульсы блока 8 от входа на задающий генератор 5 и одновременно подключается через управляемый ключ 4 напряжение Uy на вход генератора 5, что обеспечивает работу системы управления в режиме изменения частоты пропорционально току электрода.

На протяжении всей работы сумматора тока контролируется величина обратного напряжения на двух упомянутых тиристорах. Условия работы этих тиристоров в схеме таковы, что прямое напряжение на включающемся тиристоре соответствует обратному напряжению на выключающемся тиристоре. Таким образом, представляется возможным предсказать величину обратного напряжения на выключающемся тиристоре в интервале, когда он проводит ток. Если величина обратного напряжения ниже допустимой, то происходит задержка импульсов управления на включение очередных тиристоров сумматора до тех пор, пока величина обратного напряжения не станет равной заданной. Задержка импульсов осуществляется посредством элемента 18 И по сигналу с выходе триггера 16.

Режим амплитудной модуляции напряжения на тиристорах сумматора.

Напряжения, снимаемые с тиристоров сумматора тока электродов, поступают на входы датчиков положительного напряжения 9 и 13. Развязанные по потенциалу сигналы, пропорциональные положительным напряжениям на тиристорах, поступают на один вход усилителя 14. Усиленный сигнал поступает в компаратор 15, где сравнивается с заданной величиной порогового напряжения.

Если в момент времени t1 (см. фиг. 2) положительное напряжение на выходе усилителя 14 Uб достигает уровня, при котором срабатывает компаратор 15, на выходах компаратора появляются сигналы низкого уровня Uв длительностью t1-t2 и короткий сигнал U2. Последний поступает на вход синхронизации триггера 20, устанавливая его в положение, когда на его выходе формируется сигнал высокого уровня Ue, который поступает на один из входов элемента 18 И. Сигнал Uв, поступая на вход инвертирующего элемента с задержкой переднего фронта входного импульса 17, поддерживает на выходе его сигнал высокого уровня Uд (см. фиг. 2). В момент t2приходит импульс от задающего генератора 5 на второй вход элемента 18 И. Поскольку на обоих входах элемента И - сигналы высокого уровня, на его выходе также формируется сигнал высокого уровня Uж, по которому происходит включение очередных тиристоров сумматора.

Напряжение UA-K включающихся тиристоров становится близким к нулю, компаратор 15 возвращается в исходное состояние, напряжение на его выходе Ub становится равным 1.

По переднему фронту импульса на выходе элемента И (Uж) происходит срыв колебаний в задающем генераторе, и на вход элемента И поступает сигнал низкого уровня (Ua), формируя на выходе И задний фронт импульса. По заднему фронту импульса на выходе элемента И (т. t3) триггер 16 устанавливается в положение, когда на его выходе формируется сигнал низкого уровня (UB).

Поскольку этот сигнал поступает на один из входов элемента И, то в не зависимости от того, что поступает на другой вход элемента И, на его выходе присутствует сигнал низкого уровня, т. е. на интервале t3-t5блокируется включение очередных тиристоров сумматора, до тех пор пока положительное напряжение на них не достигнет заданного уровня, при котором обеспечивается надежное запирание выключающихся тиристоров. Рассмотрим процесс формирования импульса управления на интервале t4-t5.

Предположим, что в момент времени t4 на вход элемента И 18 приходит импульс от задающего генератора. На выход элемента И этот импульс не проходит, поскольку положительное напряжение на тиристоре Т (см. фиг. 1), а следовательно и напряжение на выходе усилителя 14 (Uб) не достигло величины Uпор. В интервале t4-t5 продолжается рост положительного напряжения на тиристоре Т1. В момент времени t5 напряжение на T1достигает значения, при котором обеспечивается необходимая амплитуда обратного напряжения (Uобр) на T2 и необходимое время восстановления запирающей способности (tв). В точке t5 срабатывает компаратор и процессы в устройстве протекают аналогично описанным выше. Вследствие чего происходит задержка импульса управления, поступающего на включение очередных тиристоров сумматора.

Таким образом, устройство позволяет устойчиво работать сумматору тока электродов совместно с инвертором при частотах, близких к частоте первой гармонической составляющей тока инвертора, где наблюдается амплитудная модуляция напряжения на тиристорах сумматора тока электродов за счет увеличения времени, представляемого устройством для восстановления запирающих свойств тиристора. (56) Антонов Б. М. , Султанов А. Т. Влияние пульсаций тока инвертора на коммутационную устойчивость сумматора тока электродов МГД генератора. Электричество. N 6, 1985, с. 37-42.

Авторское свидетельство СССР N 1329548, кл. H 02 K 44/08, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ТИРИСТОРНО-КОНДЕНСАТОРНЫМ СУММАТОРОМ ТОКОВ МГД-ГЕНЕРАТОРА | 1985 |

|

SU1329548A1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Устройство для управления однофазным автономным инвертором | 1987 |

|

SU1615845A1 |

| Устройство для управления группой N статических преобразователей частоты,включенных параллельно по входу и выходу | 1986 |

|

SU1388973A1 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1403281A2 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1399866A2 |

| Источник постоянного тока для дуговой сварки | 1985 |

|

SU1260131A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ТЕХНОЛОГИЧЕСКОГО ПАРАМЕТРА | 1990 |

|

RU1766190C |

| Регулируемый источник реактивной мощности сети переменного тока | 1989 |

|

SU1707690A1 |

| Устройство для регулирования температуры резистивного нагревателя | 1987 |

|

SU1474617A1 |

Изобретение относится к электротехнике и может быть использовано для управления сумматором тока электродов магнитогидродинамического генератора. Цель изобретения - повышение надежности работы сумматора тока электродов. Величина обратного напряжения контролируется первым и вторым датчиками напряжения в момент протекания тока по соответствующему тиристору. Если величина обратного напряжения ниже допустимой, то происходит задержка импульсов управления на включение очередных тиристоров сумматора тока электродов, до тех пор пока величина обратного напряжения не станет равной заданной. Задержка импульсов осуществляется посредством элемента И по сигналу с выхода триггера. 2 ил.

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРНО-КОНДЕНСАТОРНЫМИ СУММАТОРАМИ ТОКА ЭЛЕКТРОДОВ МАГНИТОГИДРОДИНАМИЧЕСКОГО ГЕНЕРАТОРА(МГДГ), содержащее блок согласования, вход которого подключен к датчику тока электрода, а первый выход соединен с управляющим входом блока логических переключений, который снабжен импульсным выходом, выходом управления ключа и синхронизирующим входом, причем входные и выходные сигналы связаны следующими логическими уравнениями:

A + B = C и B = D,

где A - сигнал на синхронизирующем входе;

B - сигнал на управляющем входе;

C - сигнал на импульсном входе;

D - сигнал на выходе управления ключа,

выход управления блока логических переключений соединен с управляющим входом ключа, второй выход блока согласования через ключ соединен с регулирующим входом задающего генератора, к синхронизирующему входу которого подключен импульсный выход блока логических переключений, блок формирования импульсов управления сетевым инвертором, первая группа выходов которого предназначена для подключения к управляющим электродам тиристоров сетевого инвертора, второй выход через блок синхронизации соединен с синхронизирующим входом блока логических переключений, делитель частоты на два, выходы которого предназначены для подключения к управляющим электродам тиристоров сумматора через выходные каскады, отличающееся тем, что, с целью повышения надежности работы сумматора тока электродов, введены первый и второй датчики напряжения, усилитель, компаратор, инвертирующий элемент с задержкой переднего фронта входного импульса, триггер и элемент И, а задающий генератор снабжен третьим входом, причем первый датчик напряжения предназначен для подсоединения входом к аноду и катоду тиристора, включенного в цепь электрода, расположенного на одном краю токосъемной зоны МГДГ, охватываемой сумматором тока электродов, а второй датчики напряжения предназначен для подсоединения к аноду и катоду тиристора, работающего в противофазе с первым, и включенного в цепь электрода, расположенного на другом краю токосъемной зоны МГДГ, выходы датчиков напряжения подключены к входу усилителя, выход которого подключен к входу компаратора, первый выход компаратора подключен к входу синхронизации триггера, к этому же входу триггера через инвертирующий элемент с задержкой переднего фронта входного импульса подключен второй выход компаратора, а выход триггера подключен к первому входу элемента И, к второму входу которого подсоединен выход задающего генератора, выход элемента И подключен к входу делителя частоты на два, к счетному входу триггера и к установочному входу задающего генератора.

Авторы

Даты

1994-05-30—Публикация

1988-10-12—Подача