и

00 00

со

Изобретение относится к преобразовательной технике и может быть использовано в тнристорных комплексах для электроснабжения предприятий на повышенных частотах.

Цель изобретеншг - повьппение , дежности путем исключения токовых перегрузок в пусковых режимах.

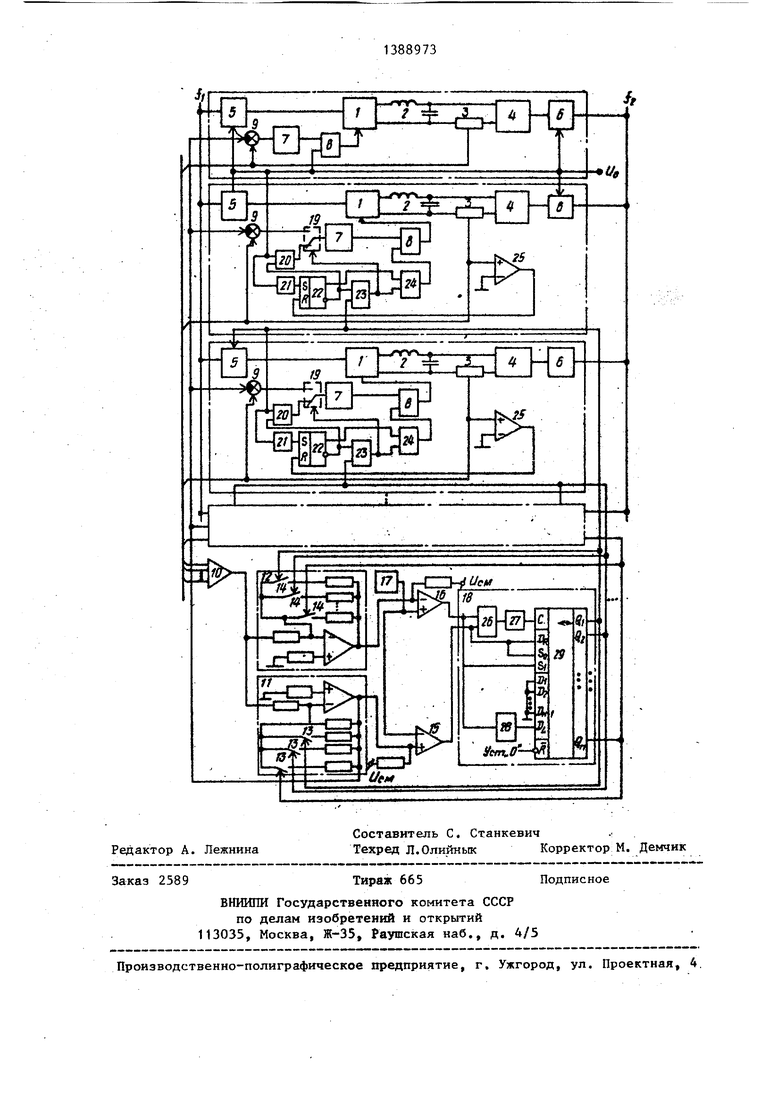

На чертеже представлена схема предлагаемого устройства.

В устройстве для управления группой N статических гфеобразователей частоты,включенных параллельно по входу и выходу, казкдьм из преобразователей содержит управляемый выпрямитель 1, вьгход которого через фильтр 2 и датчик 3 тока подключен к входу инвертора 4, первый силовой ключ 5, соединяющий входные зажимы преобразователя с силовьм входом выпрямителя 1, второй силовой ключ б, соединяющий выход инвертора 4 с выходными зажимами п:реобразователя, блок 7 управления выпрямителем, выход которого подключен к первому входу элемента И И, вых.од которого соединен с управляющим входом управляемого выпрямителя 1, блок 9 сравнения один вход которого соединен с выходом датчика 3 тока, управляющие входы первого 5 и второго 6 силовых ключей и второй вход элемента И 8 первого преобразователя соединены между собой и образуют вход разрешения включения, выход блока 9 сравне;ния первого преобразователя подключен к входу блока 7 управления выпрямителем, сумматор 10, входы которого соединены с выходами датчиков 3 тока каждого преобразо вателя, первый 11 и второй 12 делители, выполненные управляемыми с N-1 управлякнцими входами 13 и 14 и соответственно с N и N-I ступенями деления, выход сумматора 10 через первый делитель 11 подключен к прямому входу первого компаратора 15 и вторым входам блоков 9 сравнения п)еобразова- телей, а через второй делитель 12 - к инверсному входу второго компаратора 16, инверсный вход первого 15 и прямой вход второго 16 компараторов соединены с источником 17 опорного напряжения, выходы первого 15 и второго 16 компараторов подключены соответственно к первому и второму входам логического блока 18. Каждый преобразователь, кроме первого,Дополнительно снабжен управляемым пере0

5

0

5

0

5

0

5

0

5

ключателем 19, генератором 20 линейно изменяющегося напряжения, формирователем 21 узкого импульса, RS-триг- гером 22, вторым элементом И 23, элементом ИЛИ 24, компаратором 25, причем выходы логического блока 18 соединены соответственно с первым входом второго элемента И 23 предьщущего преобразователя, начиная с третьего, и с управляющими входами первого 5 и второго 6 силовых ключей, а также с первым входом генератора 20 линейно изменяющегося напряжения и через формирователь 21 узкого импульса с S входом RS-триггера каждого последующего преобразователя, выход генератора 20 линейно изменяющегося напряжения преобразователей, начиная с второго, подключен к первому входу управляемого переключателя 19, вторым входом подключенного к выходу блока 9 сравнения,а выходом - к входу блока 7 управления выпрямителем, выход второго элемента И 23 соединен с управлякяцим входом переключателя 19 и первым входом элемента ИЛИ 24, выход которого подключен к второму входу первого элемента ИВ, прямой выход RS-триггера 22 подключен к второму входу элемента ИЛИ 24, инверсный выход соединен с вторым входом второго элемента И 23 и вторым управляющим входом генератора 20 линейно изменякщегося напряжения, вход компаратора 25 подключен к выходу датчика 3 тока, а выход - к R- входу RS-триггера 22, выходы логического блока 18 соединены с соответствующими управляющими входами первого 11 и второго 12 делителей напряжения, управляющие входы первого 5 и второго 6 силовых ключей второго преобразователя соединены с входом разрешения включения, первым входом генератора 20 линейно изменяющегося напряжения и через формирователь 21 узкого импульса с В-входОм R,S - триггера 22.

Логический блок 18 содержит элемент ИЛИ 26, элемент 27 временной задержки, элемент НЕ 28 и реверсивньй сдвиговый регистр 29, причем первый вход элемента ИЖ 26 соединен с первым записывающим и первым управля- щим входами регистра 29 и образует первый вход логического блока, второй вход элемента ИЛИ 26 соединен с вторым управляющим входом и через

3

элемейт НЕ 28 с вторым записывающ входом регистра 29 и образует вто вход логического блока 18, выход элемента ИЛИ 26 через элемент 27 менной задержки подключен к синхрнизирующему входу регистра 29, выходы реверсивного сдвигового регистра 29 образуют выходы логического блока 18,

Устройство работает следующим образом.,

Наряду с равномерным делением ности нагрузки между работающими образователями в устройстве осущевляется включение (отключение) отдельных преобразовательных агрега в зависимости от величины нагрузк

Равномерное распределение нагрки мезкду параллельно работающими в данный момент преобразователями осуществляется следующим образом.

Мощности, потребляемые инверто

;ми, равны

PC , (i ) .

|где - входное напряжение i-ro инвертора 4, снимаемое с фильтра 2; Id: среднее значение тока, по-г

требляемого i-м инвертором Так как эквивалентное сопротивление цепи постоянного тока i-ro инвертора 4 мало, то напряжения питания инверторов незначительно отличаются друг от друга. Регулируя их с помощью регуляторов, можно добиться соответствующих значений токов

Информация о величине токов Id; о датчиков 3, выполненных, в частности в виде шунтов, поступает на входы сумматора 10, на выходе которого образуется напряжение

Ud -t U, ,

i-(

где - напряжение, пропорциональное величине потребляемого тока Id i-M преобразователем.

На выходе первого делителя 11 образуется

напряжение

к

и.

-1- 5.

Г

It LS-I

di

К

которое представляет собой текущую автоматически вычисляемую уставку сн стемы распределения токов. Здесь К - число инверторов, включенных к текущий момент времени на параллельную работу.

Блок 9 1-го преобразователя производит сравнение напряжения U, пропорционального величине тока, потребляемого инвертором 4 i-ro преобразователя, с напряжением.текущей уСтавки и, и формирует сигнал рассогласования А U(; -U , пропорциональный отклонению текущего значения тока, потребляемого i-м инвертором 4, от среднеарифметического значения токов, потребляемых работающими в данный момент инверторами.

15

0

30

5

g

Сигнал рассогласования Л с выхода блока 9 поступает в первом преобразователе непосредственно, а в остальных через управляемый ключ 19 на вход блока 7 управления выпрямителем 1.

Из всей совокупности преобразователей первый является ведущим, остальные N-1 ведомыми. Включение преобразователей производится подачей напря- 25 женин Uf, , которое непосредственно включает первый преобразователь в работу и подготавливает следующий к оперативному включению путем пред- варительного заряда конденсатора фильтра 2. Подобная процедура осущег- ствляется.каждый раз при включении очередного преобразователя на параллельную, работу. Преобразователь вводится в работу, следующий готовится к включению., у которого при этом срабатывают силовые ключи 5 и 6, запускается генератор 20 линейно изменяющегося напряжения и через формирователь 21 RS -триггер 22 устанавливается в единичное состояние. Сигнал единичного уровня через логический ;элемент ИЛИ 24 поступает на второй вход первого элемента И 8, подачу управляннцих импульсов с выхода блока 7 управления на выпрямитель 1. Время заряда конденсатора фильтра 2 определяется генератором 20 линейно изменяющегося напряжения. Генератор 20 вырабатывает линейно изменяющееся напряжение, которое через управляемый ключ 19 поступает на вход блока 7. При этом напряжение цепи постоянного тока подготавливаемого к включению блока будет расти, пока в цепи инвертора 4 не появится ток. Это случится в тот момент, когда вы- Jпoлнитcя условие.

Udf , pin (1Ц -л Uj ), (.1 f Д),

0

5

O

где % ,UctА и.

напряжения постоянного тока соответственно работанщих преобразователей и подготавливаемого к работе;

падение напряжения на эквивалентном сопротивлении

10

нальном режиме. Сравнение 1) и U с и осуществляется соответственно первым и вторым компараторами 15 и 16 По мере роста нагрузки выполняется не равенство и. и на выходе первого компаратора 15 формируется сигнал единичного уровня, с появлением которого реализуются алгоритм включения очередного преобразователя на параллельную работу и подготовка к оперативному включ.ению следующего. По мере уменьшения нагрузки выполня/V л,

ется неравенство U ai % и на выПри этом на выходе компаратора 25 появляется сигнал единичного уровня, ;который устанавливает RS-триггер 22 в нулевое состояние. Единичный сигнал

с инверсного выхода RS-триггера сбра ig ходе второго компаратора 16 появляет- сьгоает генератор 20. Нулевой сигнал ся сигнал единичного уровня, который с прямого выхода RS-триггера 22 через :элемент ИЛИ 24 блокщ)ует прохождение импульсов с выхода блока 7 на вход

приводит к отключению одного преобразователя из группы работаюпщх преобразователей снятием импульсов уп

нальном режиме. Сравнение 1) и U с и осуществляется соответственно первым и вторым компараторами 15 и 16. По мере роста нагрузки выполняется неравенство и. и на выходе первого компаратора 15 формируется сигнал единичного уровня, с появлением которого реализуются алгоритм включения очередного преобразователя на параллельную работу и подготовка к оперативному включ.ению следующего. По мере уменьшения нагрузки выполня/V л,

ется неравенство U ai % и на выходе второго компаратора 16 появляет- ся сигнал единичного уровня, который

ходе второго компаратора 16 появляет- ся сигнал единичного уровня, который

приводит к отключению одного преобразователя из группы работаюпщх преобразователей снятием импульсов уп

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| СИСТЕМА РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2019 |

|

RU2723989C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ФОРСИРОВКОЙ И КОРРЕКТОРОМ ПАРАЛЛЕЛЬНОЙ РАБОТЫ | 2023 |

|

RU2811685C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ДВУНАПРАВЛЕННОЙ ФОРСИРОВКОЙ | 2019 |

|

RU2725137C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| УСТРОЙСТВО МНОГОУРОВНЕВОЙ ЗАЩИТЫ ДВУНАПРАВЛЕННОГО ИНВЕРТОРА НАПРЯЖЕНИЯ | 2011 |

|

RU2456739C1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1471181A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Устройство для управления преобразователем постоянного напряжения,включающем резонансный тиристорный инвертор с транзисторным ключем на входе | 1982 |

|

SU1030945A1 |

Изобретение относится к электротехнике и может быть использовано в тиристорных преобразователях. Цель изобретения - повышение надежности. Устройство содержит группу статических преобразователей частоты, вклю- ченньпс параллельно по входу и выходу. Каждый преобразователь содержит управляемый выпрямитель, выход которого через фильтр и датчик тока подключен к инвертору. Изобретение обеспечивает мгновенное включение преобразователя на параллельную работу без перегрузок как работающих -: преобразователей, так и вновь вводимого в работу, путем предварительного заряда конденсатора фильтра. 1 3.п.ф-лы, 1 ил. i (Л

элемент И 8. В результате конденсатор фильтра 2 оказывается заряжен- ным, а преобразователь - готовым к

выпрямителя 1 через первый логический 2о равления с входа вьшрямителя 1, переводя его в состояние готовности к оперативному включению, при этом конденсатор фильтра 2 указанного блока остается заряженным. Одновременно

25 отключается еще один преобразователь, находившийся до этого в состоянии го- товности к включению, посредством размыкания силовьк ключей 5 и 6.Здесь ди , 4 Uj - величины, расширяющие диа30 пазон, характеризуемый постоянством структуры силовой схемы статических преобразователей. Они задаются напряжением смещения , подаваемым на прямой вход первого компаратора 15

35

Iоперативному включению. Включение указанного преобразователя на параллельную работу производится подачей единичного уровня на первый вход второго-элемента И 23, другой вход которого подключен к инверсному вы- |ходу RS-триггера 22. Во время под- I готовки включения нулевой сигнал на ;нем является блокирующим. После за- :ряда конденсатора фильтра 2 он сни- Iмается. Соответствующий сигнал на вы- |ходе элемента И 23 переключает управ- |ляемый ключ 19, обеспечивая поступле- |иие на вход блока 7 управления опорного напряжения, определяемого контуром стабилизации и контуром равномерного распределения нагрузки. При этом сигнал единичного уровня через элемент ИЛИ 24 снимает запрет, разре- Iшая прохождение импульсов управления с выхода блока 7 на вход выпрямителя 1 через первый элемент И 8. Подготовленный к включению преобразователь оперативно вводится в работу, при этом исключается его перегрузка по току.

На выходах первого и второго управ-сд ляемнх делителей 11 и 12 соответствен1

и инверсный вход второго компаратора

40

но формируются сигналы U г- Uj 1 - v к ,,, - И Uj, --Т Д., . Источником 17 опорного напряжения задается сигнал

Лх

V(,j , общий для всех инверторов. Он соответствует значению тока, потребляемого отдельным инвертором в номи16. Введение их вызвано тем, что U и и. обладают некоторой погрешностью, определяемой датчиками 3, сумматором 10 и делителями 11 и 12.

Алгоритм включения отдельного преобразователя агрегата реализуется следующим обризом.

. Сигнал единичного уровня с выхода первого компаратора 15 поступает на

45 первый вход логического блока. 18. При этом реализуются процедура записи логической единицы в младший разряд регистра 29 и сдвиг выходной последовательности влево. Элемент 27 задержки обеспечивает сдвиг синхронизирующего момента записи на время, необходимое для установления необходимых уровней на управляющих Sg, S и записывающих Dn и D, входах регистgglpa 29. Запись очередной единицы в регистр 29 приводит к подключению очередного преобразователя на параллельную работу. При этом уровень логической единицы с соответствующего

и инверсный вход второго компаратора

Алгоритм включения отдельного преобразователя агрегата реализуется следующим обризом.

. Сигнал единичного уровня с выхода первого компаратора 15 поступает на

первый вход логического блока. 18. При этом реализуются процедура записи логической единицы в младший разряд регистра 29 и сдвиг выходной последовательности влево. Элемент 27 задержки обеспечивает сдвиг синхронизирующего момента записи на время, необходимое для установления необходимых уровней на управляющих Sg, S и записывающих Dn и D, входах регистpa 29. Запись очередной единицы в регистр 29 приводит к подключению очередного преобразователя на параллельную работу. При этом уровень логической единицы с соответствующего

вь1кода сдвигового регистра 29 производит переключение управляемого ключа 19 преобразователя, подготовленно .го к оперативному включению, обеспечивая поступление опорного напряжения на вход блока 7 управления выпря мителем 1, определяемого контуром |стабилизации выходного напряжения и контуром равномерного распределения нагрузки. С первого элемента И 8 снимается блокирующий сигнал, и им-/ пульсы управления поступают на выпрямитель 1. Преобразователь включается в работу. Интервал времени между изменением нагрузки и подключением очередного преобразователя определяется только быстродействием систем управления. Из него исключается составляющая, связанная с бесперегрузочным вводом преобразователя на параллельную работу, которое может составлять единицы секунд.

.С вводом очередного преобразователя на параллельную работу реали- зуется также процедура подготовки следукщего.

Отключение преобразователя при сбросе нагрузки осуществляется следующим образом.

Единичный уровень с выхода второг компаратора 16 поступает на второй вход логического блока 18. Этот сигнал инвертируется логическим элементом НЕ 28 и поступает на второй записывающий вход регистра 29. С задержкой, определяемой элементом 27, происходят запись логического нуля в старший разряд регистра 29 и сдвиг выходной последовательности право. При этом старшая единица в выходной последовательности заменяется нулем, снимаются импульсы управления выпрямителем 1 соответствующего преобразователя, который переводится в режим готовности к оперативному вклю

чению, а преобразователь, которьй ранее находился в этом режиме, отключается путем размыкания силовых ключей 5 и 6. Последовательность на .выходе логического блока 18 обеспечивает необходимые коэффициенты деления управляемых делителей и путем замыкания соответствующих ключей. s;

Таким образом, использование изобретения обеспечивает мгновенное включение преобразователя на параллельную работу без перегрузок как работакяцих 1треобразователей, так и вновь вводимого в работу, путем предварительного заряда конденсатора фильтра, что позволяет обеспечить электроснабжение потребителей с высокой надежностью.

Формула изобретения

0

0

5

5

0

5

0

5 целью повышения надежности путем

исключения токовых перегрузок в пусковых режимах, 7саждый преобразователь) кроме первого, снабжен управляемым переключателем, генератором линейно

изменяющегося напряжения, формиро- йателем узкого импульса, RS -триггером, вторьм элементом И, элементом ИЛИ, компаратором, причем выходы ло- ического блока соединены соответ- 4твенно с первым входом второго эле- tjieHTa И предьщущего преобразователя „ Йачиная с третьего, и с управляющими

входами первого и второго силовых клю-|о входом разрешения включения, первым

Чей, а также с первым входом генера- topa линейно изменяющегося напряже- Йия н через формирователь узкого им- йульса с S-входом RS -триггера каждо о последующего преобразователя, вы- з|сод генератора линейно изменяющегося 1 апряжения преобразователей, начиная ф второго, подключен к первому вход управляемого переключателя, вторым йходом подключенного к выходу блока уравнения, а выходом ™ к входу блока : правления выпрямителя, -выход второго элемента И соединен с управляю- 1|(1им входом переключат«ухя и первым входом элемента ИЛИ, выход которого г одключен к второму входу первого Элемента И преобразователя, прямой ыход RS -триггера подключен к второму входу элемента ШШ, инверсный 1|ыход соединен с вторьлм входом вто- iforo элемент а И и вторым управляющим Йходом генератора линейно изменяющегося напряжения, вход компаратора подключен к выходу датчика тока, а выход - к R-входу RS -триггера, выходы логического блока соединены с соответствующими управляющими входами первого и второго делителей напряжения, управляющие входы силовых ключей второго преобразователя соединены с

входом генератора линейно изменяющегося напряжения и через формирователь узкого импульса с S-входом RS - триггера.

2, Устройство по п. 1, отличающееся тем, что логический блок содержит элемент ИЛИ, элемент временной задержки, элемент НЕ, реверсивный сдвиговый регистр, причем первый вход элемента ИЛИ соединен с первым записьшающим и первым управляющим входами регистра и образует первый вход логического блока, второй вход элемента ИЛИ соединен с вторым управляющим входом и через элемент НЕ с вторым записывающим входом регистра и образует второй вход логического блока, выход элемента ИЛИ через элемент временной задержки подключен к синхронизирующему входу регистра, выходы реверсивного сдвигового регистра образуют выходы логического блока.

| Групповой преобразователь | 1980 |

|

SU896724A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Групповой преобразователь частоты | 1984 |

|

SU1267563A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-04-15—Публикация

1986-03-24—Подача