Изобретение относится к фазоизме- рительной технике и может быть использовано для аттестации и поверки электронных фазометров.

Цель изобретения - повьшение точности и ускорение процесса поверки фазометров путем автоматизации определения фазоамплитудной погрешности.

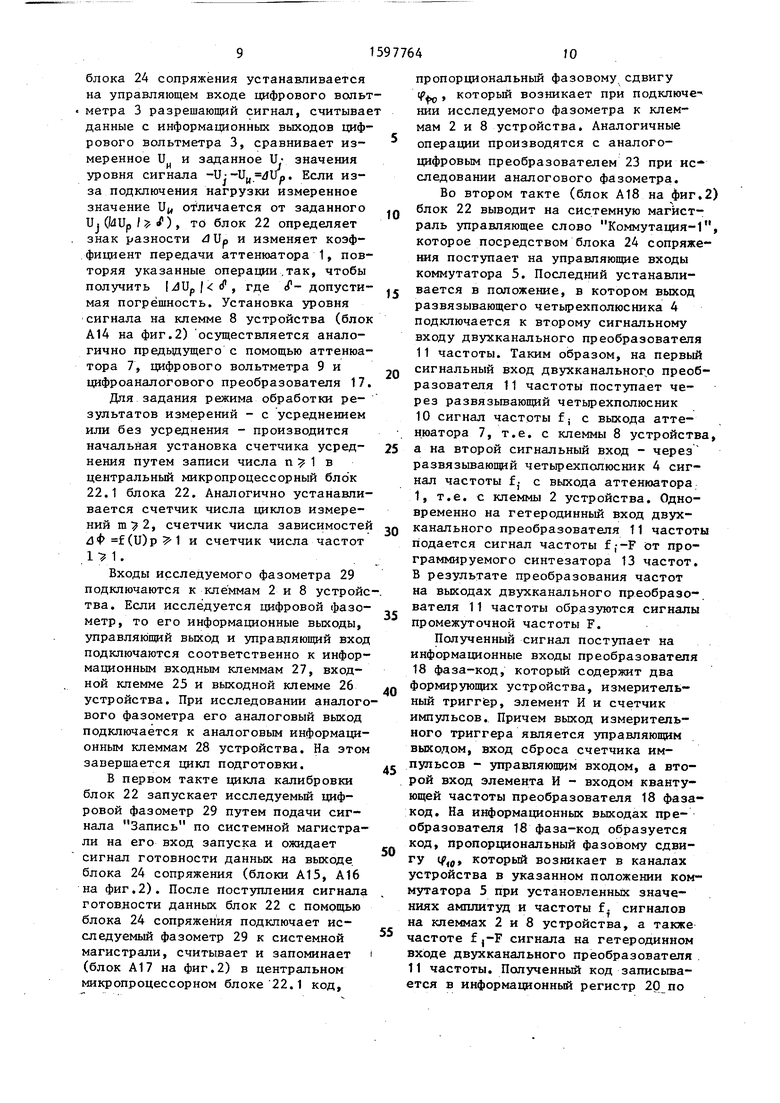

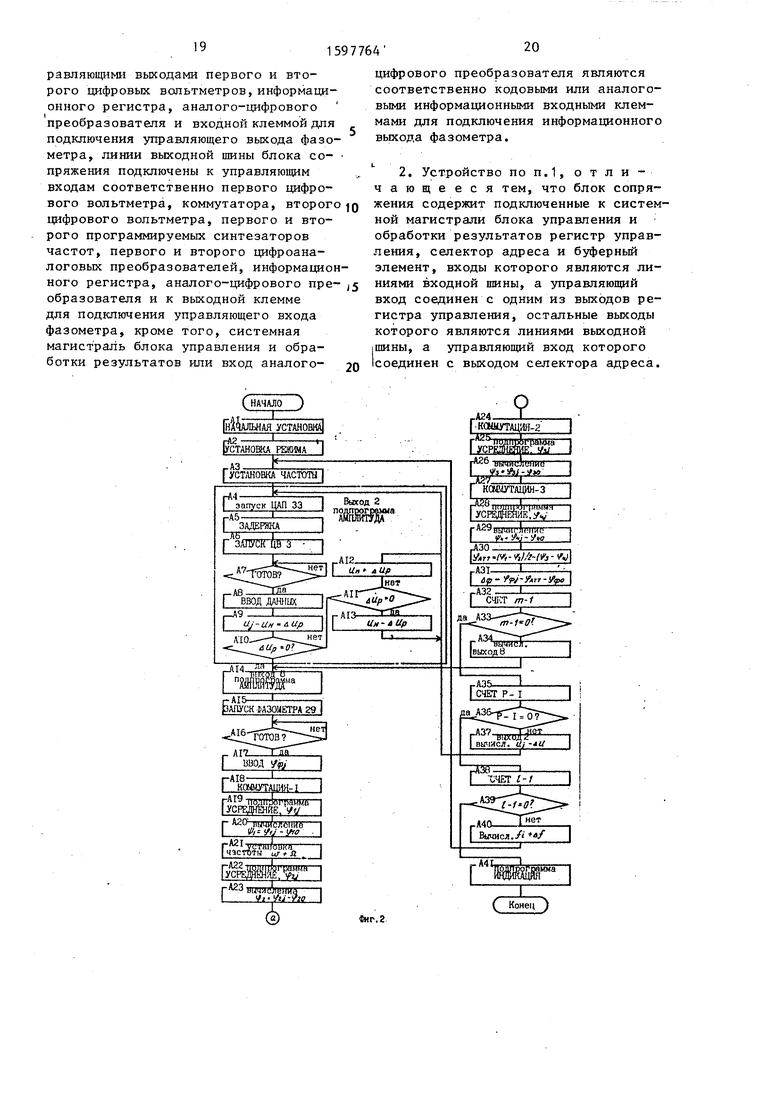

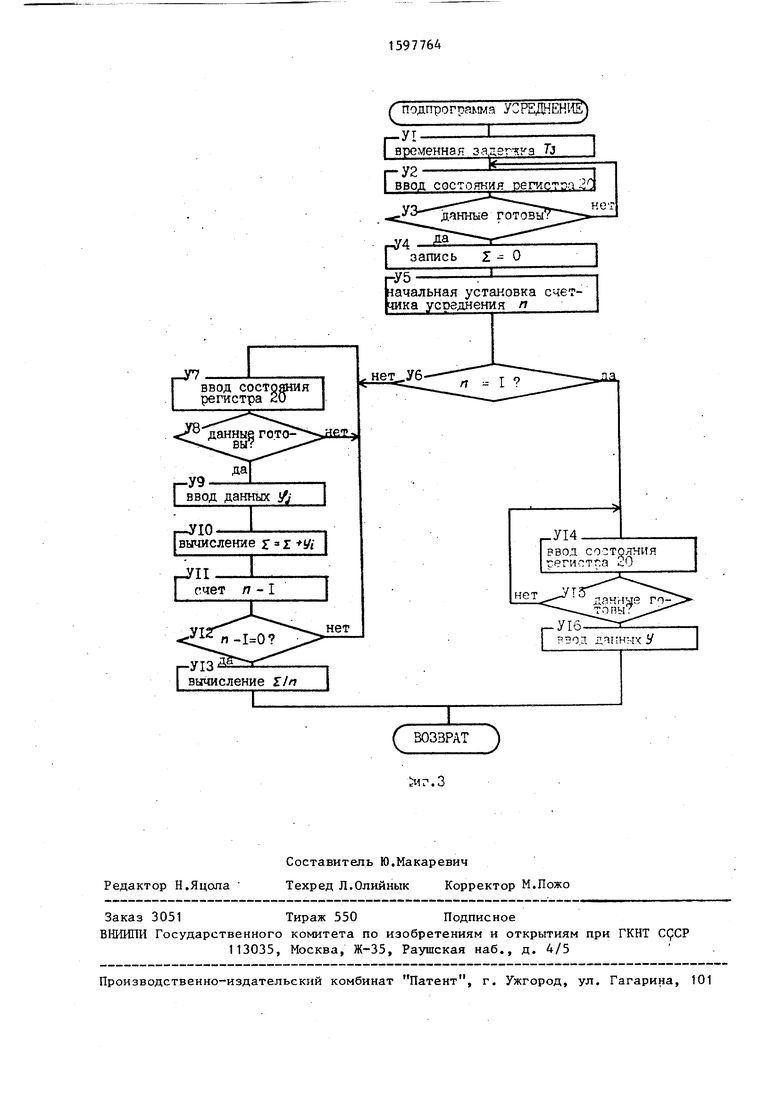

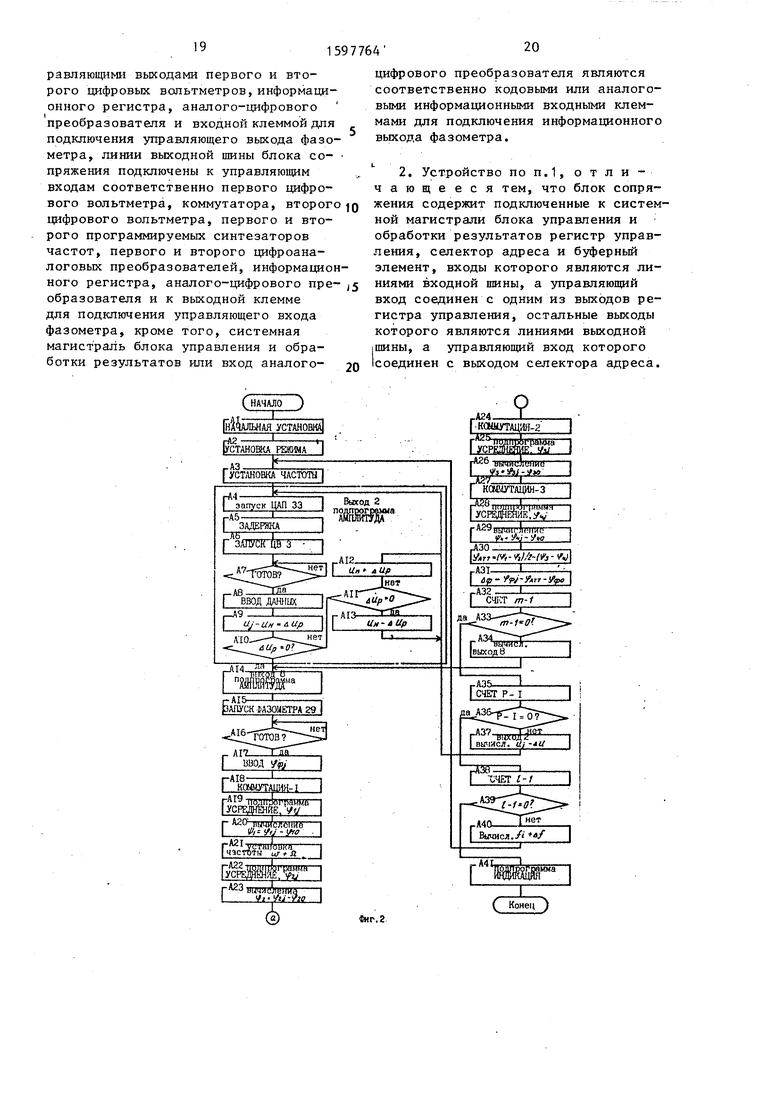

На фиг.1 приведена структурная схема устройства; на фиг.2 и 3 - Структурная схема алгоритма работы микро-ЭВМ.

Устройство для определения фазоамплитудной погрешности фазометров содержит первый аттенюатор 1,первую сигнальную выходную клемму 2, первый цифровой вольтметр 3, первый раз- вязывающий четьфехполюсник 4, коммутатор 5, второй развязывающий четырехполюсник 6, второй аттенюатор 7, вторую сигнальную выходную клемму 8, второй цифровой вольтметр 9,«третий развязьшаюший четырехполюсник 10, двухканальный преобразователь 11 частоты, четвертый развязывающий четырехполюсник 12, первый программируе- мьм синтезатор 13.частот, умножитель 14 частоты, второй программируемый синтезатор 15-.частот, первый 16 и второй 17 цифро-аналоговые преобразователи, преобразователь 18 фаза- код, первый формирователь 19 иьтуль- сов, информационный регистр 20, второй формирователь 21 импульсов, блок 22 управления и обработки результатов, аналого-цифровой преобразователь 23, блок 24 сопряжения, содержащий регистр 24.1 управления, селектор 24.2 адреса и буферный элемент 24.3, кроме того, устройство содержит входную клемму 25 для подключени управляющего выхода фазометра., выход ,ную клемму 26 для подключения управляющего входа фазометра, информационные кодовые 27 или аналоговые 28 входные клеммы для подключения инфор5

0

5

0

5

0

5

0

5

мационного выхода поверяемого фазометра 29.

Выход первого аттенюатора 1, сое- диненньй с первой сигнальной выходной клеммой 2, соединен также с входами первого цифрового вольтметра 3 и первого развязывающего четьфех- полюсника 4, выход которого подключен к первому входу коммутатора 5, второй вход которого соединен с выходом второго развязьшающего четырехполюсника 6, вход которого подключен к выходу второго аттенюатора 7, который соединен с второй сигнальной выходной клеммой 8 и с входами второго цифрового вольтметра 9 и третьего развязывающего четырехполюсника 10, выход которого соединен с первым сигнальным входом двухканального преобразователя 11 частоты и с входом четвертого развязывающего четьфех- псшюсника 12, выход которого подключен к третьему входу коммутатора 5, выход которого соединен с вторым сигнальным входом двухканального преобразователя 11 частоты, гетеродинный вход которого подключен к выходу первого программируемого синтезатора. 13 частот, вход синхронизации которого соединен с входом умножителя 14 частоты и с выходом.опорной частоты второго программируемого синтезатора 15 частот, выход которого подключен к входам первого аттенюатора 1 и второго аттенюатора 7, управляющие входы которых соединены соответственно с выходами первого 16 и второго 17 циф- роаналоговых преобразователей.

Вькод у1 ножителя 14 частоты подключен к входу квантующей частоты преобразователя 18 фаза-код, информационные входы которого соединены с выходами двухканального преобразователя 11 частоты. Управляющий выход преобразователя 18 фаза-код подключен через первый формирователь 19 импульсов к входу записи информационного

регистра 20, управляющий выход которого соединен через второй формирователь 21 импульсов с входом сброса преобразователя 18 фаза-код, информационные выходы которого подключену к информационным входам информационного регистра 20, информационные выходы которого соединены с системной магистралью блока 22 управления и обработки, который также соединен с выходами первого цифрового вольтметра 3, второго цифрового вольтметра 9, входами первого программируемого синтезатора 13 частот,второго программируемого синтезатора 15 частот, первого 16 и второго 17 цифроанало- говых преобразователей, выходами аналого-цифрового преобразователя 23 и системной магистралью блока 24 сопряжения, линии входной шины которого соединены соответственно с управляющими выходами первого 3 и второго 4 цифровых вольтметров, информационного регистра 20, аналого-цифрового преобразователя 23 и с входной клеммой 25 управляющего выхода фазометра 29. Линии выходной щины блока 24 сопряжения подключены к управляющим входам соответственно первого цифрового вольтметра 3, комт мутатора 5, второго цифрового вольтметра 9, первого 13 и второго 15 синтезаторов частот, первого 16 и второго 17 цифроаналоговых преобра- зователей, информационного регистра 20, аналого-цифрового преобразователя 23 и к выходной клемме 26 управляющего входа фазометра. Кроме того, системная магистраль блока 22 или выход анапого-цифрового преобразователя 23 являются соответственно кодовыми информационными входными клеммами 27 и аналоговыми информационными входными клеммами 28 для подключения информационного выхода поверяемого фазометра 29.

Блок 22 управления и обработки результатов измерений содержит центральный микропроцессорный бл ок 22.1, пульт 22.2 управления, блок 22.3 отображения информации и периферийный блок 22.4 (например, накопитель на гибких магнитных дисках). В качестве блока 22 может быть применена, например , одноплатная микро-ЭВМ ряда электроника МС 2101. Системная магистраль центрального микропроцессорного блока 22.1 является системной магистралью

0

5

0

блока 22 и содержит 16 линий Адреса/ данных и управляющие линии: Ввод (Чтение), Вывод (Запись), Выбор внешнего устройства, ГТрерьша- ние и Сброс. Пульт 22.2 управления подключен к 16 линиям Адреса/данных и к управляющим линиям Ввод (Чтение, Вывод (Запись, Выбор внешнего устройства и Прерывание системной магистрали. Блок 22.3 отображения информации соединен с 16 линиями Адреса/данных и с управляющими линиями Вывод(3апись)и Выбор внешнего устройства. Периферийный блок 22.4 подключен к интерфейсу центрального микропроцессорного блока 22.1.

Блок 24 сопряжения обеспечивает передачу управляющих сигналов между блоком 22 и другими блоками устройства и содержит регистр 24.1 управления, селектор 24.2 адреса и буферный элемент 24.3. Входы регист- 5 ра 24.1 управления, селектора 24.2 адреса и выходы буферного элемента 24.3 подключены к 16 линиям Адреса/ данных системной магистрали блока 22. Кроме того, управляющие линии Q Вьгоод (Запись), Выбор внешнего устройства и Сброс системной магистрали блока 22, а также выход селектора 24.2 адреса соединены с управляющими входами регистра 24.1 управления.выходы которого являются выходной щиной блока 24 сопряжения, а входы буферного элемента 24.3 являются входной шиной блока 24 сопряжения .

Устройство работает следующим образом.

По команде Пуск производится начальная установка блока 22. Последний формирует управляющий сигнал f Сброс, который по системной магистрали блока 22 поступает на вход сброса регистра 24.1 управления блока 24 сопряжения и устанавливает его в начальное состояние. При этом на линиях выходной шины блока 24 сопряжения (на выходах регистра 24.1 управления) появляются запрещающие -сигналы, которые отключают информационные вькоды цифровых вольтметров 3 и 9, информационного регистра 20, аналого-цифрового преобразователя 23, буферного элемента 24.3 блока 24 сопряжения, исследуемого фазометра 29 от системной магистрали блока 22 и

5

0

0

5

од1ювре 1е.нпо блокируют прием информации программируемыми синтезаторами 13 и 15 частот и цифроаналоговыми преобразоватепями 16 и 17.

Работа устройства осуществляется в три цикла: цикл подготовки, цикл калибровки и цикл измерений, причем цикл калибровки и цикл измерений состоит из пяти тактов,

в цикле подготовки с помощью пульта 22.2 управления блока 22 осуществляется установка режима работы устройства, а именно задаются диапазон частот, шаг перестройки частоты (число точек), исходные уровни сигналов на клеммах 2 и 8 устройства, диапазон и шаг изменения уровня сигналов (число точек), тип фазометра, число усреднений результатов одного измерения и другие операхщи алгоритма приведенного на фиг.2 и 3. При вводе информации с пульта 22,2 управления на управляющем входе блока 22 появляется сигнал, который поступает на вход прерывания центрального микропроцессорного блока 22,1. В результате этого блок 22 переходит к выполнению подпрограммы установки режима. По этой подпрограмме блок 22 считывает, дешифрует и запоминает состояние органов пульта 22.2 управления, а затем нормализует и корректирует введенные данные.

Для установки частоты f на выходе программируемого синтезатора 15 частот (блок A3 на фиг,2) блок 22 в младиих разрядах Адреса/данных системной магистрали выдает адрес блоку 24 сопряжения, а затем в старших разрядах Адреса/данных системной магистрали - управляющее слово. Адрес в блоке 24 сопряжения поступает на входы селектора 24.2 адреса, выхной сигнал которого разрешает запись информации в регистр 24.1 управления при поступлении по системной магистрали блока 22, сигнала Выбор устройства. По сигналу Запись, поступающему по управляющей

линии Вывод (Запись) системной магистрали блока 22, управляющее слово загружается в блок 24 сопряжения (регистр 24,1 управления), В результате этого на управляющем входе программируемого синтезатора 15 частот появляется разрешающий сигнал, кото- рьш подготавливает его к приему информации. После этого блок 22 вьщает

на системную магистраль код частоты ft , По сигналу Запись этот код загружается в программируемый синтезатор 15 частот, с выхода которого синусоидальный сигнал частоты f. поступает на входы аттенюаторов 1 и 7. . Сигнал частоты f с выхода опорной частоты программируемого синтезатора 15 частот подается на вход синхронизации программируемого синтезатора 13 частот и на вход умножителя 14 частоты, на выходе которого образуется сигнал с частотой f g. Этот сигнал поступает на вход квантующей частоты преобразователя 18 фаза-код. Установка частоты fj-F (F - промежуточная частота на выходах двухка- нального преобразователя 11 частоты) на выходе программируемого синтезатора 13 частот с помощью блока 22 производится аналогично рассмотренному процессу установки частоты на выходе программируемого-синтезатора 15 частот.

Для установки уровня испытательного сигнала на клемме 2 блок 22 переходит к выполнению подпрограммы Амплитуда (блоки А4,...,А13 на фиг,2), По этой подпрограмме с помощью блока 24 сопряжения устанавливается на управляющем входе цифро- аналогового преобразователя 16 раз- решающи й сигнал. По сигналу Запись блок 22 загружает в илфроаналоговьш 5 преобразователь 16 код амплитуды U- сигнала, задаваемого на клемме 2 устройства. На выходе цифроаналого- вого преобразователя 16 формируется соответствующее постоянное напряжение, управляющее коэффициентом передачи аттенюатора 1, После временной задержки, необходимой для установления уровня сигнала на выходе аттенюатора 1, блок 22 вьщает сигнал За0

5

0

0

5

0

5

пись , который поступает по системной магистрали блока 22 на вход запуска цифрового вольтметра 3.

Блок 22 посредством регистра 24,1 управления устанавливает на управляющем входе буферного элемента 24,3 разрешающий сигнал и тем самым подключает его к системной магистрали. После этого блок 22 ожидает сигнал готовности данных, который поступает через буферный элемент 24,3 с управляющего выхода цифрового вольтметра 3, После поступления CHfHana готовности данных с помощью

блока 24 сопряжения устанавливается на управляющем входе цифрового вольт- метра 3 разрешающий сигнал, считывает данные с информационных выходов цифрового вольтметра 3, сравнивает из- меренное U и заданное U- значения уровня сигнала -U;-U.. 41/0. Если из 1 -H. f)

за подключения нагрузки измеренное значение Uj, отличается от заданного

10

15

20

Uj (/4Up / I/), ТО блок 22 определяет знак разности гЗПр и изменяет коэффициент передачи аттенюатора 1, повторяя указанные операции.так, чтобы получить iJUp (, где f- допустимая погрешность. Установка уровня сигнала на клемме 8 устройства (блок А14 на фиг.2) осуществляется аналогично предьщущего с помощью аттенюатора 7, цифрового вольтметра 9 и цифроаналогового преобразователя 17.

Для задания режима обработки результатов измерений - с усреднением или без усреднения - производится начальная установка счетчика усред- 25 нения путем записи числа п 91 в центральный микропроцессорный бло к 22.1 блока 22. Аналогично устанавливается счетчик числа циклов измерений , счетчик числа зависимостей .,Q 4Ф(и) и счетчик числа частот .

Входы исследуемого фазометра 29 подключаются к клеммам 2 и 8 устройс-. тва. Если исследуется цифровой фазометр, то его информационные выходы, управляющий выход и управляющий вход подключаются соответственно к информационным входным клеммам 27, входной клемме 25 и выходной клемме 26 устройства. При исследовании аналогового фазометра его аналоговый выход подключается к аналоговым информационным клеммам 28 устройства. На этом завершается цикл подготовки.

В первом такте цикла калибровки блок 22 запускает исследуемый цифровой фазометр 29 путем подачи сигнала Запись по системной магистрали на его вход запуска и ожидает сигнал готовности данных на выходе, блока 24 сопряжения (блоки А15, А16 на фиг.2). После Поступления сигнала готовдости данных блок 22 с помощью блока 24 сопряжения подключает исследуемый фазометр 29 к системной магистрали, считывает и запоминает i (блок А17 на фиг.2) в центральном микропроцессорном блоке 22.1 код,

35

40

45

50

10

15

20

25 .,Q

5

0

5

0

пропорциональный фазовому сдвигу (f , который возникает при подключе НИИ исследуемого фазометра к клеммам 2 и 8 устройства. Аналогичные операции производятся с аналого- цифровым преобразователем 23 при исследовании аналогового фазометра.

Во втором такте (блок А18 на фиг.2) блок 22 выводит на системную магистраль управляющее слово Коммутация-1, которое посредством блока 24 сопряжения поступает на управляющие входы коммутатора 5. Последний устанавливается в положение, в котором выход развязывающего четырехполюсника 4 подключается к второму сигнальному входу двухканального преобразователя 11 частоты. Таким образом, на первый сигнальный вход двухканальног о преобразователя 11 частоты поступает через развязьгоающий четырехполюсник 10 сигнал частоты fj с выхода аттенюатора 7, т.е. с клеммы 8 устройства, а на второй сигнальный вход - через развязывающий четьфехполюсник 4 сигнал частоты fJ с выхода аттенюатора 1, т.е. с клеммы 2 устройства. Одновременно на гетеродинный вход двухканального преобразователя 11 частоты подается сигнал частоты f ,--F от программируемого синтезатора 13 частот. В результате преобразования частот на выходах двухканального преобразователя 11 частоты образуются сигналы промежуточной частоты F.

Пол5гченный сигнал поступает на информационные входы преобразователя 18 фаза-код, который содержит два формирующих устройства, измерительный триггер, элемент И и счетчик импульсов. Причем выход измерительного триггера является управляющим выходом, вход сброса счетчика импульсов - управляющим входом, а второй вход элемента И - входом квантующей частоты преобразователя 18 фаза- код. На информационных выходах преобразователя 18 фаза-код образуется код, пропорциональный фазовому сдви- гу If to который возникает в каналах устройства в указанном положении коммутатора 5 при установленных значениях амплитуд и частоты f сигналов на клеммах 2 и 8 устройства, а также частоте fj-F сигнала на гетеродинном входе двухканального преобразователя 11 частоты. Полученный код записьша- ется в информационный регистр 20 по

фронту импульса, поступающего на вход записи с выхода форг-шрователя 19 импульсов, Одповременно этот импульс, форГ Шруемый по спаду импульса на уп- равляшщем выходе преобразователя 18 фаза-код, устанавливает на управляющем выходе информационного регистра 20 сигнал готовности данных. По фронту готовности данных на вы- ходе формирователя 21 импульсов образуется и fflyльc, которьй поступает на управляющий вход преобразователя 18 фаза-код и устанавливает на его ин- формационных выходах нулевой код.

На этом завершается процесс подготовки данных для обработки, и блок 22 переходит к вьшолнению подпрограммы Усреднение (блок А19 на фиг.2).

По этой подпрограмме (фиг.З) блок 22 после переключения коммутатора 5 вводит временную задержку, учитывающую переходные процессы при коммутации, и ожидает появления на управляющем выходе информационного регистра 20 сигнала готовности данных (блоки У1-У13 на фиг.З), который поступает через блок 24 сопряжения. При появлении сигнала готовности данных блок 2 устанавливает посредством блока 24 сопряжения ра управляющем входе информационного регистра 20 разрещаю- щий сигнал, который сбрасывает сигнал готовности данных на управляющем выходе информационного регистра 20, а его информационные выходы подключает к системной магистрали. Затем независимо от кода, находящегося в регистре 20, в центральный микропроцессорный блок 22.1 микро-ЭВМ записывается нулевой код (блок У5 на фиг.З), т.е. производится пропуск первого результата измерения, который может быть искажен при вы- полне1ши временной задержки.

Таким образом, с помощью рассмотренных операций достигается устранение погрешности, обусловленной переходными процессами в коммутируемых цепях устройства, и одновременно

обеспечивается синхронизация работы устройства. При синхронной работе блок 22 обрабатывает всегда целое число результатов измерений и, тем самым, устраняется низкочастотная

погрешность дискретного преобразования. Блок 22 осуществляет анализ данного числа усреднений (блоки У5, У6 на Фиг.З). В результате этого

анализа, например, при п 1 блок 22 переходит к циклической процедуре ввода данных, суммирования получен- ньк результатов, измерения и проверки содержимого счетчика усреднения (блоки У7,...,У12 на фиг.З). Указанные операции выполняются п раз и завершается циклическая процедура формированием в центральном микро- роцессорном блоке 22.1 кода, пропор- Iп

ционального сумме 2 noTi Делением полученной суммы на число п заканчивается подпрограмма Усредне- п

ние 1/. 2 t/ffoii /п (блок У19 на I

фиг.З).

При осуществляется аналогичная процедура ввода данных только один раз и на том завершается выполнение подпрограммы Усреднение (блоки У14,...,У16 на фиг;3). Блок 22 заканчивает второй такт вычисления разности ф, if,g-0 (блoк А10 на фиг.2). Код, пропорциональный фазовому сдвигу ( , записывается в центральный микропроцессорный блок 22.1.

Третий такт (блоки А21,.,.,А23 на фиг. 2) блок 22 .начинает с установки на выходе программируемого синтезатора 13 частот сигнала с-частотой f.+F, смещенной вверх на промежуточ- частоту F относительно частоты f сигнала на клеммах 2 и 8 устройства. Коммутатор 5 остается в прежнем положении. В результате преобразования частот, преобразования фаза-код и выполнение подпрограммы Усреднение, которые осуществляются так же, как и во втором такте, в централь- ном микропроцессорном блоке 22.1 образуется код, соотвётствуюший фазо7 вому сдвигу - fffu, завершается третий такт вычислений разности и . Код, пропорциональный фазовому сдвигу - (, записывается в центральный микропроцессорный блок 22.1.

Б четвертом такте (блоки А24,..., А26 на фиг.2) блок 22 выводит управ- ляющее слово Коммутация-2 и, тем самым коммутатор 5 устанавливается в положение, в котором выход развязывающего четьфехполюсника 6 подключается к второму сигнальному входу двухканального преобразователя 11 частоты, т.е. второй сигнальный вход

двухканального преобразователя 11 частоты подключается через развязывающий четырехполюсник 6 к клемме 8 устройства. На выходе программируе- мого синтезатора 13 частот устанавливается сигнал частоты f,--F.

Далее устройство работает аналогично второму такту, в результате в центральный микропроцессорный блок 22.1 записывается код, пропорциональный фазовому сдвигу ( fj(- 1Лд

Пятый такт цикла калибровки (блоки А27,...,АЗО) блок 22 начинает с вывода управляющего слова Коммута- ция-2. В результате этого коммутатор 5 устанавливается в положение, в котором выход развязывающего четырехполюсника 12 подключается к второму сигнальному входу двухканального преобразователя 11 частоты, т.е. второй сигнальный вход двухканального преобразователя 11 частоты подключается через первый развязывающий четырехполюсник 12 к первому сигналь- ному входу двухканального преобразовтеля 11 частоты. После этого уст- ройство работает так же, как и во втором такте, и в центральный микро- процессорный блок 22.1 записывается код, соответствующий фазовому сдвигу

V4 40-0

Завершается цикл калибровки изменением и проверкой содержимого счет- чика числа циклов измерений (блоки А32, АЗЗ на фиг.2). После этого блок 22 вычисляет значение уровня сигнала на клемме 8 устройства, при котором будет производиться определение фазоамплитудной погрешности ис- следуемого фазометра 29 (блок А34 на фиг.2) и переходит к выполнению подпрограммы Амплитуда; (блок А14 на фиг.2).

Первый такт цикла измерений начи- нается после завершения подпрограммы Амплитуда и полностью аналогичен первому такту цикла калибровки (блоки А15-А16 на фиг.2). По окончании первого такта в центральном микро- процессорном блоке 22.1 формируется код, пропорциональный фазовому сдвиг

ФГ

ifi - начальное значение фазового сдвига в каналах исследуемого фазометра 29 при исходных значениях уровней

g

Q

5 0

5

сигналов на клеммах 2 и 8 устройства, измеренное в цикле калибровки;

а. - фазоамплитудная погрешность, возникающая в каналах исследуемого фазометра 29 , при изменении уровня сигнала на клемме 8 устройства; - фазовый сдвиг, возникаЬщий в результате изменения коэффициента передачи аттенюатора 7.

После завершения второго такта цикла измерений, который полностью аналогичен второму такту цикла калибровки, в центральном микропроцессорном блоке 22.1 образуется код, соот- ветствуюшрй фазовому сдвигу

(f; If,.- (f,g (, + Л;+л)-q-to

,

где M fo фазовый сдвиг, возникающий в каналах устройства при исходных значениях уровней на клеммах 2 и 8; , фазовые сдвиги (фазоампли- тудные погрешности), возникающие соответственно на первом сигнальном входе и выходе двухканального преобразователя 11 частоты при изменении амплитуды сигнала на клемме 8 устройства, причем сдвиг Д учитывает также фазоампли- тудную погрешность, вносимую преобразователем 18 - фаза-код.

Третий такт цикла измерений полностью аналогичен третьему такту цикла калибровки. В результате выполнения третьего такта в центральном микропроцессорном блоке 22.1 формируется код, пропорциональный фазовому сдвигу

V,

ц-()

-(-ф«) .

мв

Знаки фазовых сдвигов изменяются, на противоположные по сравне- 1ШЮ с вторым тактом, так как частота f.+F сигнала на гетеродинном входе двухканального преобразователя 11 частоты выше частоты f,. сигналов на его сигнальных, входах. Величины фазовых сдвигов ,3 { , л , и .остаются такими же, как и во втором такте цикла измерений, поскольку амплитуды сигналов на клеммах 2 и 8 устройства и соответственно на сигнальных входах двухканального преобразователя 11 частоты не изменяются.

В четвертом такте цикла измерений который аналогичен четвертому такту jцикла калибровки, в центральном мик- ропроцессорном блоке 22.1 образуется код, соответствующий фазовому сдвигу

V3 4 3r%.

-( + d|)j- ч з, .,

где 4 -1- фазовые сдвиги (фазоамплитудные погрешности), возникающие соответственно на втором сигнальном входе и выходе двухканального преобразователя 11

частоты.

После окончания пятого такта цикла измерений, который полностью j аналогичен пятому такту цикла калиб- ровки, в центральном микропроцессор- ном блоке 22.1 формируется код, про- Iпорциональный фазовому сдвигу

Ч 4-40 410+ (гЗ X, И ,Ч Л , ) -((.

Завершается цикл измерения вычислением фазового сдвига (погрешности), I вносимого аттенюатором 7 при изме- лп НИИ его коэффициента передачи (блок АЗО на фиг.2),

А - Ч .)/2 -()

вычислением фазоамгшитудной пог- рещности исследуемого фазометра 29 (блок А31 на фиг.2)

ФГ

и вьтолнением анализа заданного числа циклов измерений (блоки А32,.,., АЗЗ на фиг.2).

В результате этого анализа, напри мер, при т-1 70, блок 22 переходит к следующему циклу измерения. При блок 22 завершает определение фазоамплитудной погрешности исследуемого фазометра 29 в зависимости от изменения уровня сигнала на одно из его входов (клемма 8 устройства) и фиксированном уровне сигнала на другом (клемма 2 устройства) ЛФ f(U). Затем блок 22 изменяет и анализирует состояние счетчика числа зависимостей f(U) (блок А35, А36 на фиг.2). Например, при р-1 О в блоке 22 снова устанавливается счетчик числа циклов измерений, котррьш вычисляет значение уровня сигнала на клемме 2 устройства, выполняет подпрограмму Амплитуда для установки уровней сигналов на клеммах 2 и 8 устройства и переходи к осуществлению цикла калибровки и циклов измерений как описано. При блок 22 изменяет и анализирует состояние счетчика числа частот. Например, при 1-1 О блок 22 устанавливает счетчик циклов измерений, счётчик числа зависимостей, вычисляет значение частоты и далее, как описано, устанавливает значение частоты и уровней сигналов на клеммах 2 и 8 устройства, проводит цикл калибровки и циклы измерений. При блок 22 переходит к выполнению подпрограммы Индикация. По этой подпрограмме блок 22 выводит результаты определения фазоамплитудной погрешности в блок 22.3 отображения информации и документирует полученные данные с помощью периферийного устройства 22.4.

В устройстве благодаря введению развязывающих четырехполюсников 4,6, 10 и 12 коммутатора 5, программируемого синтезатора 13 частот, преобразователя 18 фаза-код и обработке в блоке 22 результатов измерения пяти тактов цикла калибровки и циклов измерений, во время которых переключаются сигналы и их частоты на входах двухканального преобразователя 11 частот, автоматически устраняется фазоамплитудная погрешность устройства и погрешность, возникающая при изменении коэффициента передачи аттенюаторов 1 и 7.

I

Введение и;ифровых вольтметров 3 и 9, программируемых синтезаторов 13 и 15 частот позволяет уменьшить, погрешности, обусловленные изменением нагрузки на клеммах 2 и-8 . устройства и неточностью установки частоты, т.е.

дополнительно повысить точность определения фазоамипитудной погрешности.

Введение формирователей 19 и 21 информационного регистра 20, блока 24 сопряжения и блока 22 управления и обработки результатов обеспечивает синхронную работу узлов устройства. Это позволяет устранить низкочастотную погрешность дискретного преобразования при регулировании в широких пределах числа усреднений п и погрешность, обусловленную переходными процессами в коммутируемых цепях устройства, т.е. дополнительно повы- сить точность измерений.

Благодаря применению блока 22 для управления аттенюаторами 1 и 7 с помощью цифроаналоговых преобразователей 16 и 17 цифровыми вольтметрами 3 и 9, коммутатором 5, программируемыми синтезаторами 13 и 15 частот, аналого-цифровым преобразователем 23, запоминания и обработки полученных данных достигается автоматизация процесса определения фазоамплитудной погрешности фазометров, обеспечивается автоматическая коррекция погрешностей и определение характера изменения фазоамплитудной погрешности фазометров в заданных диапазонах изменения уровней и частот сигналов, исследования различных типов (аналоговых и цифровых) фазометров с документированием полученных данных.

Формула изобретения

1. Устройство для определения фазоамплитудной погрешности фазометров, содержащее два аттенюатора, выходы которых являются сигнальными выходными клеммами для подключения входов фазометра, и двухканальный преобразователь частоты, о т л и - чающееся тем, что, с целью повышения точности и ускорения процесса поверки; фазометров путем автоматизации определения фазоамплитудной погрешности, в него введены два цифровых вольтметра, четыре развязывающих четырехполюсника, коммутатор, два программируемьгх синтезатора частот, два цифроаналоговых преобразователя, преобразователь фаза-код, два формирователя импульсов, информацион- ный регистр, блок управления и обработки результатов, аналого-цифровой преобразователь и блок сопряжения.

0

,

5 п

0

5

0

.

0

причем выход первого аттенюатора соединен с входами первого цифрового вольтметра и первого развязывающего четырехполюсника, выход которого подключен к первому входу коммутатора, второй вход которого соединен с выходом второго развязывающего четырехполюсника, вход которого подключен к выходу второго аттенюатора и к входам второго цифрового вольтметра и третьего развязывающего четырехполюсника, выход которого соединен с пер- вым сигнальным входом двухканального преобразователя частоты и с входом четвертого развязывающего четырехполюсника, выход которого подключен к третьему входу коммутатора, выход которого соединен с вторым сигнальным входом двухканального преобразователя частоты, гетеродинный вход которого подключен к выходу первого программируемого синтезатора частот, вход синхронизации которого соединен с входом умножителя частоты и с выходом опорной частоты второго программируемого синтезатора частоты, выход которого подключен к входам первого и второго аттенюаторов, управляющие входы которых соединены соответственно с выходами первого и второго цифроаналоговых преобразователей, выход умножителя частоты подключен к входу квантующей частоты преобразователя фаза-код, информационные входы которого соединены соответственно с первыми и вторыми выходами двухканаль- ного преобразователя частоты, а управляюш 1й выход подключен через первый формирователь импульсов к входу записи информационного регистра, управляюш51й выход которого соединен через второй формирователь иьтуль- сов с входом сброса преобразователя фаза-код, информационные выходы которого подключены к информационным входам информационного регистра, системная магистраль блока управления и обработки результатов подключена к выходам первого и второго цифровых вольтметров, входам первого и второго программируемых синтезаторов частоты, входам первого и второго цифроаналоговых преобразователей, выходам информационного регистра, выходам аналого-цифрового преобразователя и к системной магистрали блока сопряжения, линии входной шины которого соединены соответственно с управляющими выходами первого и второго цифровых вольтметров, информационного регистра, аналого-цифрового преобразователя и входной клеммой для подключения управляющего выхода фазометра, линии выходной шины блока со- пряжения подключены к управляющим входам соответственно первого цифрового вольтметра, коммутатора, второго цифрового вольтметра, первого и второго программируемых синтезаторов частот, первого и второго цифроана- логовых преобразователей, информационного регистра, аналого-цифрового пре- образователя и к выходной клемме для подключения управляющего входа фазометра, кроме того, системная магистраль блока управления и обработки результатов или вход аналого-

цифрового преобразователя являются соответственно кодовыми или аналоговыми информационными входными клеммами для подключения информационного выхода фазометра.

2. Устройство по П.1, о т л и - чающеесятем, что блок сопряжения содержит подключенные к системной магистрали блока управления и обработки результатов регистр управления, селектор адреса и буферный элемент, входы которого являются линиями входной шины, а управляющий вход соединен с одним из выходов регистра управления, остальные выходы которого являются линиями выходной |Шины, а управляющий вход которого 1соединен с выходом селектора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометр | 1985 |

|

SU1273837A1 |

| Измеритель фазочастотных характеристик и группового времени запаздывания | 1989 |

|

SU1626202A1 |

| Измеритель группового времени запаздывания | 1988 |

|

SU1555697A1 |

| Измеритель группового времени запаздывания | 1990 |

|

SU1725180A2 |

| Калибратор фазы | 1982 |

|

SU1027640A1 |

| Устройство для измерения фазоамплитудных характеристик | 1986 |

|

SU1401397A1 |

| Измеритель группового времени запаздывания | 1984 |

|

SU1226400A1 |

| Радиочастотный преобразователь разности фаз | 1984 |

|

SU1164625A1 |

| Цифровой фазометр | 1985 |

|

SU1262412A1 |

| Устройство для измерения фазовых сдвигов,вносимых взаимными четырехполюсниками | 1982 |

|

SU1045156A1 |

Изобретение позволяет повысить точность и автоматизировать определение фазоамплитудной погрешности (ФАП) фазометров путем автоматической коррекции ФАП устройства, погрешности, возникающей при изменении коэффициента передачи аттенюаторов, и автоматического управления режимами работы узлов устройства. Уровни испытательных сигналов на выходах 2, 8 устройства, фиксируемые цифровыми вольтметрами 3, 9, устанавливаются ослаблением выходного сигнала программируемого синтезатора частот (ПСЧ) 15 с помощью аттенюаторов 1, 7, коэффициент передачи которых изменяют цифроаналоговые преобразователи 16, 17. Двухканальный преобразователь частоты (ДПЧ) 11, на сигнальных входах которого включены развязывающие четырехполюсники 4, 6, 10, 12, совместно с ПСЧ 13 обеспечивает перенос фазового сдвига, вносимого аттенюаторами 1, 7, из диапазона частот на промежуточную частоту. Формирование цифрового кода, соответствующего этому фазовому сдвигу, и запись его в информационный регистр 20 осуществляются с помощью преобразователя 18 фаза - код и формирователей 19, 21 импульсов. Алгоритм определения ФАП, реализуемый микроЭВМ 22, включает два цикла: калибровки и измерения, состоящих из пяти тактов. В каждом такте обоих циклов коммутатор 5 переключает сигналы на втором сигнальном входе ДПЧ 11, а ПСЧ 13 изменяет частоту сигнала на его гетеродинном входе, микроЭВМ 22 обрабатывает накопленный объем измерительной информации, корректирует полученный результат и управляет режимами работы устройства посредством блока 24 сопряжения. 1 з.п. ф-лы, 3 ил.

(НАЧШ УСТАНОШй

«иг.г

г

ввод состддния регистра

да У91

I ввод данных ifj

-31Q1

вычисление j г «//

рУП

I СЧ6

счет Г7 -1

нет

П

У13 вычисление Г/

Т

( подпрограм ла УСРЕДНЕН1

.У1

GJ :- |рсменнак задержка Tj

п

У2

Е

ввод состояния perMCTCiai C

запись - О

начальная установка счет- ника усреднения п

-нет .Уб

У14

ввод сое регистра

нет

У16

1 90Д ЛПННМХ У

I

г ВОЗВРАТ

| Устройство для измерения фазоамплитудных характеристик четырехполюсников | 1985 |

|

SU1269049A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения фазоамплитудных погрешностей фазометров | 1977 |

|

SU645096A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-10-07—Публикация

1988-05-10—Подача