СП

ная большой емкостью конденсатора А.1, а нормально замкнутые контактные группы 6, 10, 13 и 16 реле 7 обеспечивают подключение к выходу источника 14 измерительного напряжения низкоомного делителя напряжения, образованного низкоомными резисторами 8 и 1.1, причем нижнее плечо делителя, образованное резистором 8, шунтирует на корпус исследуемую

цепь 3.1. Пройдя через элемент НЕ 30, сигнал обнуляет также триггер 26, который готовит элемент И 18 для пропускания сигналов с выхода блока 9 сравнения. Устройство содержит также задатчик 25 времени вьщержки, источник 17 опорного напряжения, дешифратор 34, блок. 35 сигнализации, сиг- нальные индукторы 31 и 32. 8 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь для устройства контроля сопротивления изоляции | 1985 |

|

SU1357870A1 |

| Преобразователь частоты | 1983 |

|

SU1173501A1 |

| Устройство контроля сопротивления изоляции | 1989 |

|

SU1751692A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для автоматической настройки дугогасящего реактора | 1984 |

|

SU1228182A1 |

| Способ контроля сопротивления изоляции | 1978 |

|

SU1045166A1 |

| Способ гашения дуги однофазного замыкания на землю в сети переменного тока | 1986 |

|

SU1376169A1 |

| Реле времени | 1980 |

|

SU868872A1 |

| Двухканальная следящая система | 1984 |

|

SU1241188A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПОГРУЖНОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1999 |

|

RU2146071C1 |

Изобретение относится к электроизмерительной технике и предназначено для автоматического контроля состояния изоляции объектов, содержащих большое количество электрически разобщенных цепей, зашунтированных конденсаторами. Цель изобретения - повышение помехозащищенности. По сигналу с шины 28 обнуления сбрасывается в исходное состояние счетчик переключающего блока 5. Исследуемые цепи 3.1-3.K объекта 2 контроля отключены от блока 9 сравнения. Обнулена ключевая схема 22, обесточено реле 7 с нормально замкнутыми контактируемыми группами 6, 10, 13 и 16. По сигналу с шины 29 запуска, соединенной с первым входом элемента ИЛИ 19, на его выходе появляется импульсный сигнал, поступающий на вход блока 20 задержки, а также на (K+1)-й управляющий вход переключающего блока 5. К первому входу блока 9 сравнения с помощью одной из клемм 1.1-1.K подключается исследуемая цепь 3.1, зашунтированная большой емкостью конденсатора 4.1, а нормально замкнутые контактные группы 6, 10, 13 и 16 реле 7 обеспечивают подключение к выходу источника 14 измерительного напряжения низкоомного делителя напряжения, образованного низкоомными резисторами 8 и 11, причем нижнее плечо делителя, образованное резистором 8, шунтирует на корпус исследуемую цепь 3.1. Пройдя через элемент НЕ 30, сигнал обнуляет также триггер 26, который готовит элемент И 18 для пропускания сигналов с выхода блока 9 сравнения. Устройство содержит также задатчик 25 времени выдержки, источник 17 опорного напряжения, дешифратор 34, блок 35 сигнализации, сигнальные индукторы 31 и 32. 8 ил.

Изобретение относится к электроизмерительной технике и предназначено для автоматического контроля состояния изоляции объектов, содержащих большое количество электрически ра- зобщенных цепей, зашунтированных конденсаторами.

Цель изобретения - повьш1ение поме- хозашлщенности.

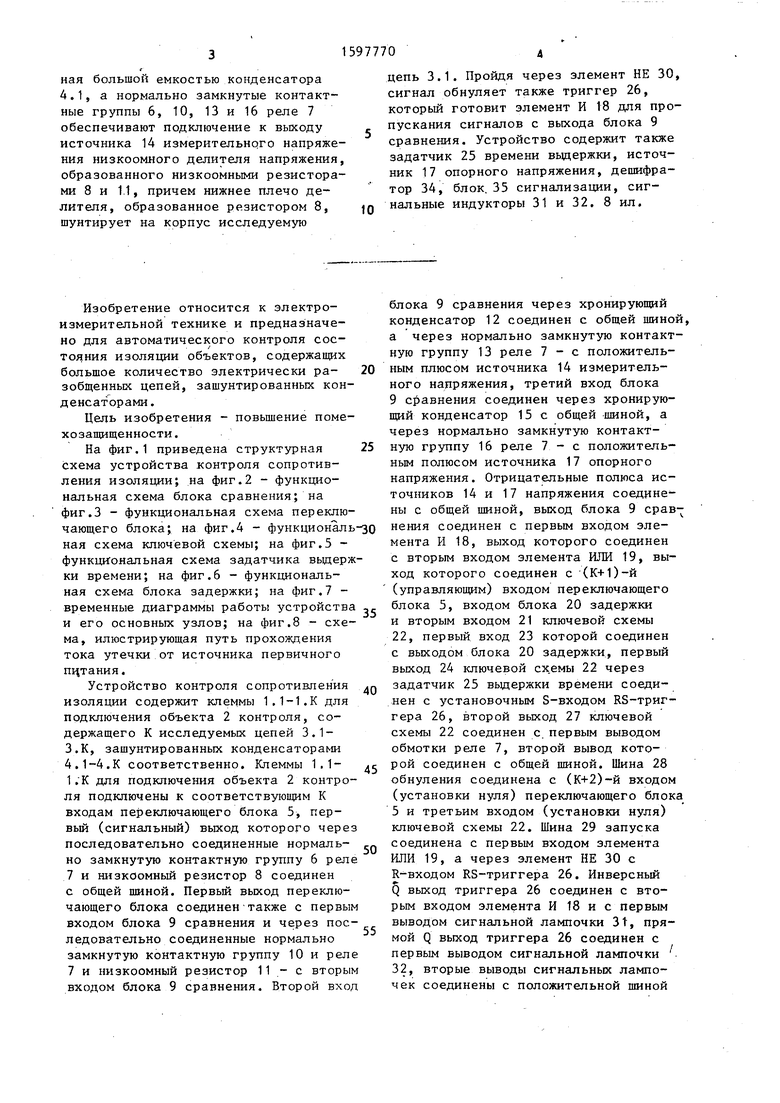

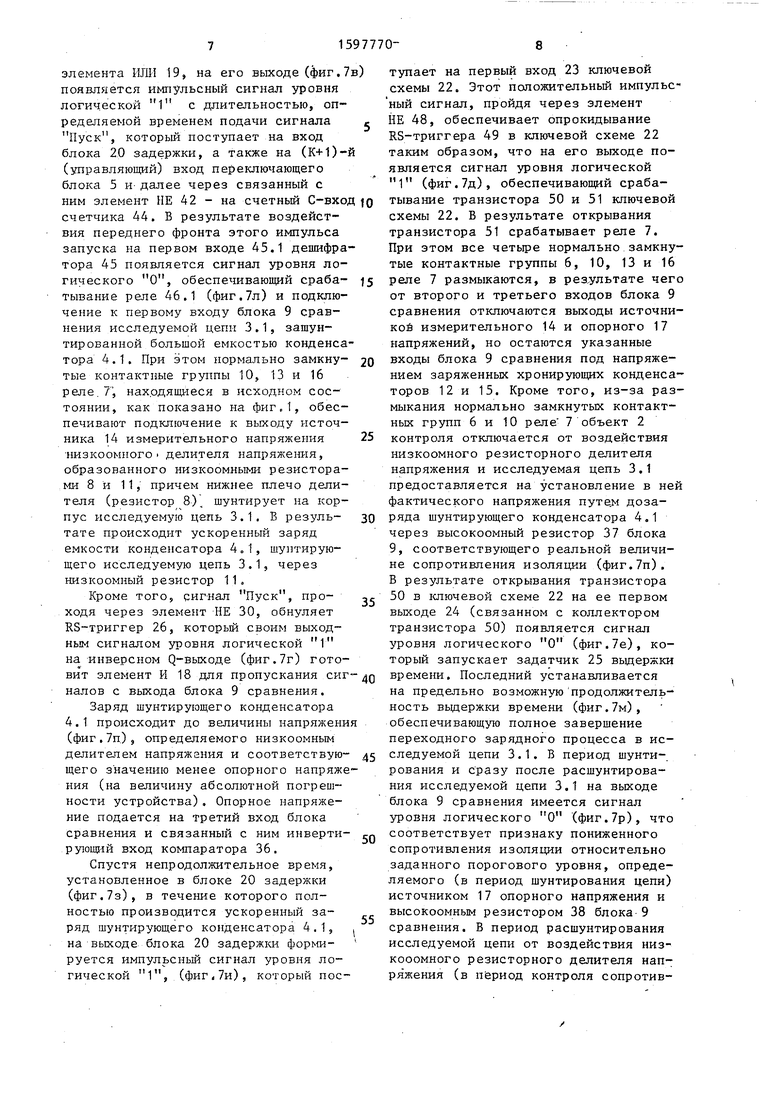

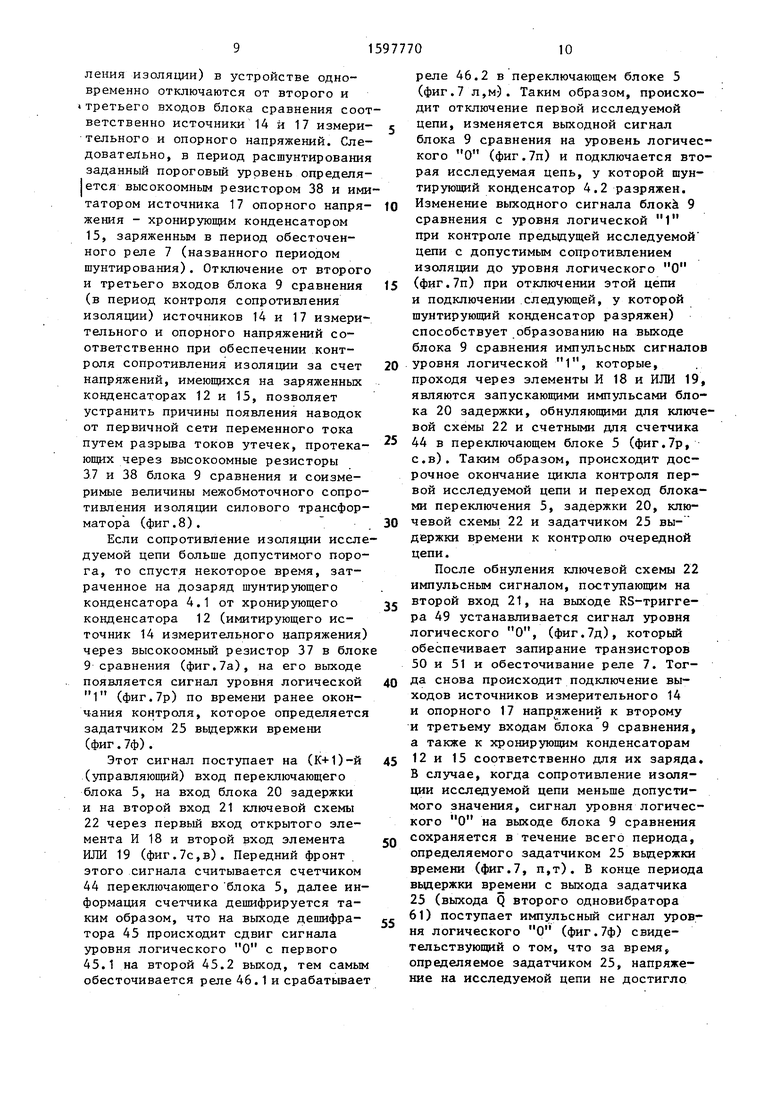

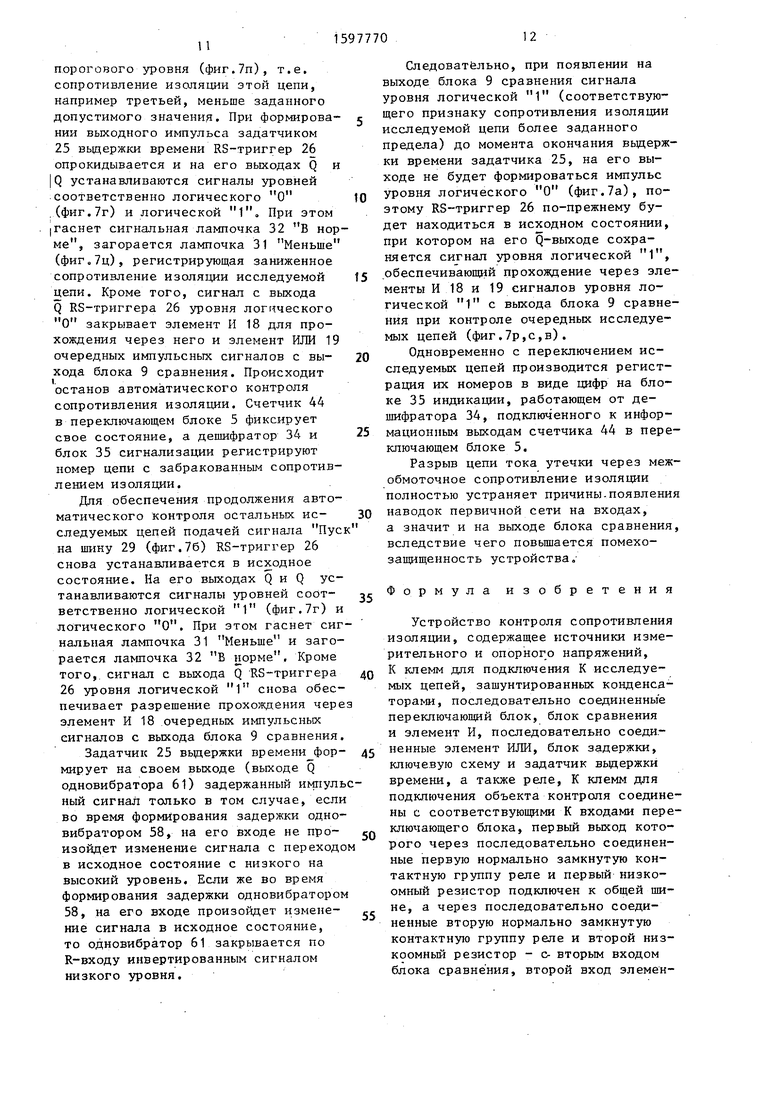

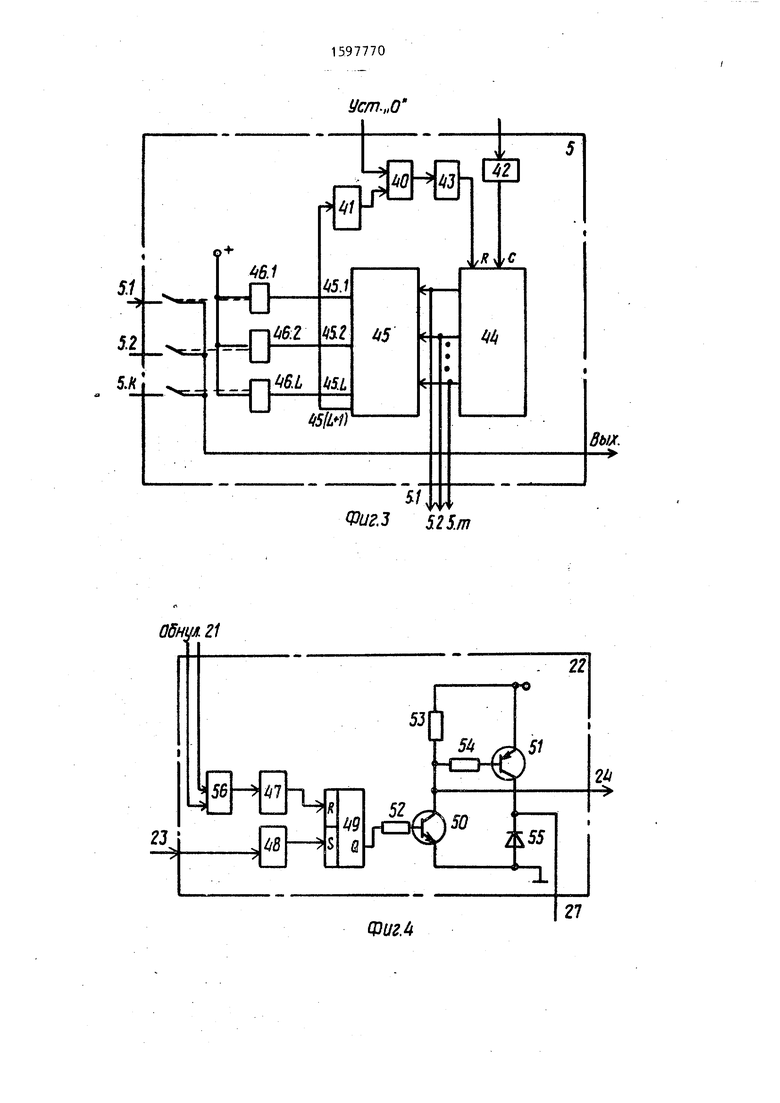

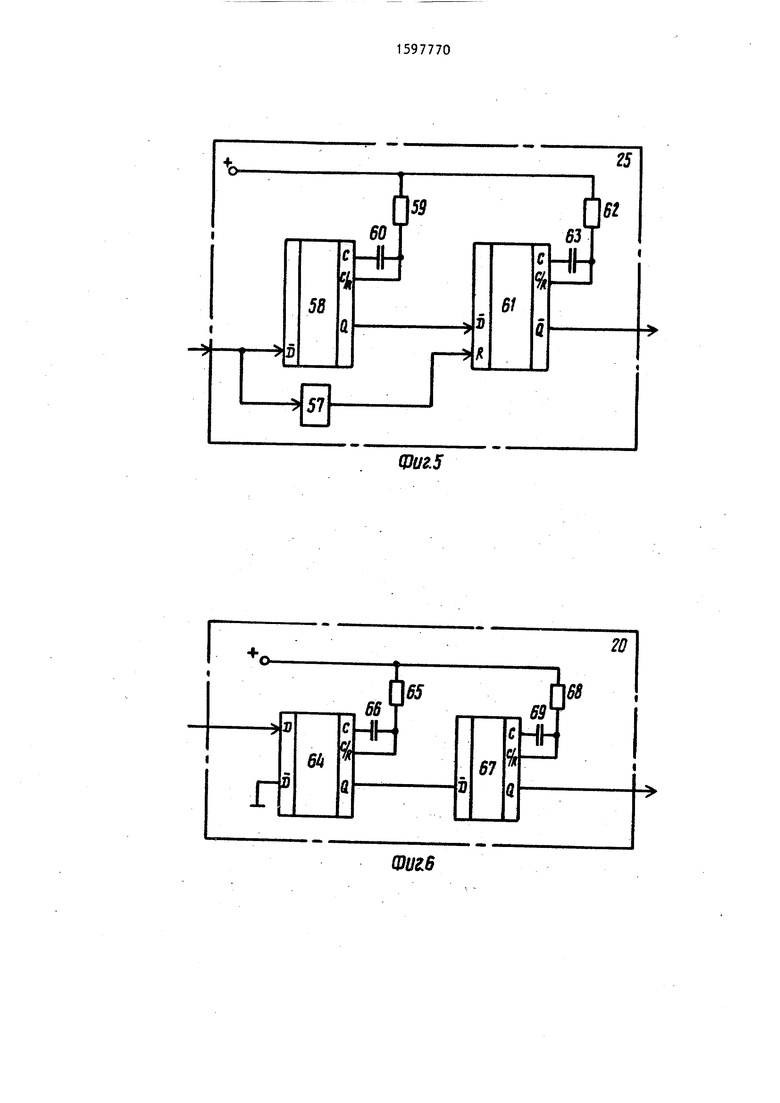

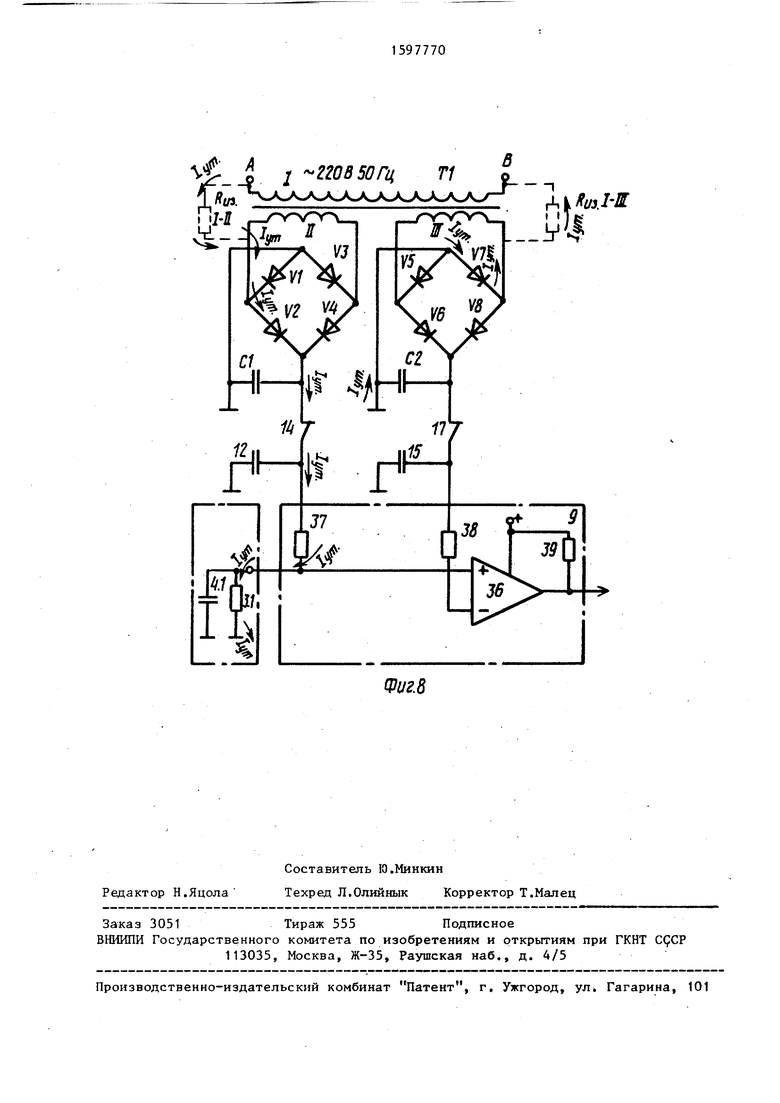

На фиг.1 приведена структурная схема устройства контроля сопротивления изоляции; на фиг.2 - функциональная схема блока сравнения; на фиг.З - функциональная схема переключающего блока; на фиг.4 - функциональ ная схема ключевой схемы; на фиг.5 - функциональная схема задатчика вьщержки времени; на фиг.6 - функциональная схема блока задержки; на фиг.7 - временные диаграммы работы устройства и его основных узлов; на фиг.8 - схема, илюстрирующая путь прохождения тока утечки от источника первичного пцтания.

Устройство контроля сопротивления изоляции содержит клеммы 1.1-1.К для подключения объекта 2 контроля, содержащего К исследуемых цепей 3.1- З.К, зашунтированных конденсаторами 4.1-4.К соответственно. Клеммы 1,1- 1.К для подключения объекта 2 контроля подключены к соответствующим К входам переключающего блока 5, первый (сигнальный) выход которого через последовательно соединенные нормаль- но замкнутую контактную группу 6 реле 7 и низкоомный резистор 8 соединен с общей шиной. Первьш выход переключающего блока соединен также с первым входом блока 9 сравнения и через последовательно соединенные нормально замкнутую контактную группу 10 и реле 7 и низкоомный резистор 11 - с вторым входом блока 9 сравнения. Второй вход

0

5 о ,

Q с Q

5

блока 9 сравнения через хронирующий конденсатор 12 соединен с общей шиной, а через нормально замкнутую контактную группу 13 реле 7 - с положительным плюсом источника 14 измерительного напряжения, третий вход блока 9 сравнения соединен через хронирующий конденсатор 15 с общей шиной, а через нормально замкнутую контактную группу 16 реле 7 - с положительным полюсом источника 17 опорного напряжения. Отрицательные полюса источников 14 и 17 напряжения соединены с общей шиной, выход блока 9 сравнения соединен с первым входом элемента И 18, выход которого соединен с вторым входом элемента ИЛИ 19, выход которого соединен с (К+1)-й (управляющим) входом переключающего блока 5, входом блока 20 задержки и вторым входом 21 ключевой схемы 22, первый вход 23 которой соединен с выходом блока 20 задержки, первый выход 24 ключевой сх.емы 22 через задатчик 25 вьздержки времени соединен с установочным S-входом RS-триг- гера 26, второй выход 27 ключевой схемы 22 соединен с. первым выводом обмотки реле 7, второй вывод которой соединен с общей шиной. Шина 28 обнуления соединена с (К+2)-й входом (установки нуля) переключающего блока 5 и третьим входом (установки нуля) ключевой схемы 22. Шина 29 запуска соединена с первым входом элемента ИЛИ 19, а через элемент НЕ 30 с R-входом RS-триггера 26. Инверсный Q выход триггера 26 соединен с вторым входом элемента И 18 и с первым выводом сигнальной лампочки 3t, прямой Q выход триггера 26 соединен с первьш выводом сигнальной лампочки 32, вторые выводы сигнальных лампочек соединены с положительной шиной

33 питания. М информационных входов дешифратора 34 соединены с соответствующими М информационными выходами переключающего блока 5, а N выходов дешифратора 34 соединены с соответствующими N входами блока 35 сигнализации .

Блок 9 сравнения (фиг.2) содержит компаратор 36 с высокоомными резисторами 37 и 38 на входах. В качестве нагрузки используется резистор 39,

Переключающий блок 5 (фиг.З) содержит элемент ИЛИ 40, элементы НЕ 41 и 42, одновибратор 43, двоично-десятичный счетчик 44 с подключенным на выходе дешифратором 45 двоично-десятичного кода в десятичный код, имеющий (L+1) выходов 43.1 - 45 (L+1).

К L выходам дешифратора 45 подключены первые выводы обмоток реле 46, вторые выводы которых соединены с положительной шиной питания. Последний (Ь+1)-й выход дешифратора 45 подключен через элемент НЕ 41 к первому входу элемента ИЛИ 40, второй вход которого соединен с (К+2)-м входом (установки нуля) переключающего блока 5, а выход через одновибратор 43 соединен с обнуляющим входом счетчика 44, счетный С-вход которого соединен с (K+D-M (управляющим) входом переключающего блока 5 через второй элемент НЕ 42. Переключающиеся контакты каждого реле 46, соединенные вместе, образуют сигнальный выход переключающего блока 5, а замыкающиеся контакты - входы от 1 до К. Выходы двоично-десятичного счетчика кроме того образуют информационные выходы от 1 до М переключающего блока 5. Одновибратор 43 предназначен для формирования импульса обнуления уровня логической 1 заданной длительности из сигналов, поступающих либо с (К+2)-го входа (установки нуля) переключающего блока 5, либо с (L+1)-ro выхода дешифратора 45 через первьй элемент НЕ 41. Дешифратор 45 преобразует двоично-десятичный код счетчика 44 в десятичньй код типа бегущего нуля.

Ключевая схема 22 (фиг.4) содержит элементы НЕ 47 и 48, RS-триггер 49, транзисторы 50 и 51, резисторы 52-54, обеспечивающие заданные режимы работы транзисторов, демпфирующий диод 55, элемент ИЛИ 56, первый вход которого является входом 21 ключевой схемы 22,

5

0

5

0

5

5

0

5

0

второй - третим входом (установки нуля) ключевой схемы 22, а выход че- ,рез элемент НЕ 47 соединен с R-входом iRS-триггера 49, установочный S-вход которого через элемент НЕ 48 соединен с первым входом 23 ключевой схемы 22. База транзистора 50 через резистор 52 соединена с прямым Q-выходом RS- триггера 49, коллектор транзистора 50 является первым выходом 24 ключевой схемы 22, а коллектор транзистора 51 является вторым выходом 27 ключевой схемы 22. Задатчик 25 вьщержки времени (фиг.5) содержит элемент НЕ 57, одновибратор 58 с внешними времязадающими р езисторами 59 и конденсатором 60, одновибратор 61 с внешними времязадающими резистором 62 и конденсатором 63.

Блок 20 задержки (фиг.6) содержит одновибратор 64 с внешними времяза- дающими резистором 65 и конденсатором 66, одновибратор 67 с внешними времязадающими резистором 68 и конденсатором 69.

Устройство контроля сопротивления изоляции работает следующим образом.

После подачи сигнала на шину 28 обнуления счетчик 44 переключающего блока 5 обнуляется, на выходах 45,1- 45. (L+1) дешифратора 45 присутст- взлот сигналы уровня логической 1, все реле 46 обесточены и их нормально разомкнутые контакты 46.2-46 L не подключают ни одну из исследуемых цепей 3.1-3.К объекта 2 контрсхля к первому входу блока 9 сравнения. Кроме того, обнулена ключевая схема 22 по третьему входу (установки нуля), Обеспечивая срабатывание RS-триггера

49в такое состояние, когда на его прямом Q-выходе сигнал уровня логического О. При этом транзисторы

50и 51 ключевой схемы 22 будут закрыты, реле 7 обесточено, а на первом выходе 24 ключевой схемы 22 будет сигнал уровня логической 1. При обесточенном реле 7 к выходам источников 14 и 17 измерительного и опорного напряжений соответственно будут подключены хронируюш 1е конденсаторы 12 и 15, которые в период нахождения нормально замкнутых контактных групп реле заряжаются до величи ны напряжений указанных источников 14 и 17.

После поДачи сигнала Пуск на :шину 29 запуска, на первый вход

элемента ИШ1 19, на его вькоде (фиг, 7 появляется импульсный сигнал уровня логической 1 с длительностью, определяемой временем подачи сигнала Пуск, который поступает на вход блока 20 задержки, а также на (К+1)(управляющий) вход переключающего блока 5 и- далее через связанный с ним элемент НЕ 42 - на счетный С-вхо счетчика 44. В результате воздействия переднего фронта этого импульса запуска на первом входе 45.1 дешифратора 45 появляется сигнал уровня логического О, обеспечивающий сраба- тывание реле 46.1 (фиг.7л) и подключение к первому входу блока 9 сравнения исследуемой цепы 3.1, зашун- тированной большой емкостью конденсатора 4.1. При этом нормально замкну- тые контактные группы 10, 13 и 16 реле. 7, нахрдящ теся в исходном состоянии, как показано на фиг.1, обеспечивают подключение к выходу источника 14 измерительного напряжения низкоомного I делителя напряжедаш, образованного низкоомными резисторами 8 и 11, причем нижнее плечо делителя (резистор 8). шунтирует на корпус исследуемую цепь 3.1. В резуль- тате происходит ускоренный заряд емкости конденсатора 4.1, шунтирующего исследуемую цепь 3.1, через низкоомный резистор 11,

Кроме того, сиг-нал Пуск, про- ходя через элемент НЕ 30, обнуляет RS-триггер 26, которьш своим выходным сигналом уровня логической 1 на инверсном Q-выходе (фиг.7г) готовит элемент И 18 для пропускания сиг налов с выхода блока 9 сравнения.

Заряд шунтирующего конденсатора 4.1 происходит до величины напряжени (фиг.7п), определяемого низкоомным делителем напряжения и соответствую- щего значению менее опорного напряжения (на величину абсолютной погрешности устройства). Опорное напряжение подается на третий вход блока сравнения и связанный с ним инверти- РУ1ош -1й вход компаратора 36.

Спустя непродолжительное время, установленное в блоке 20 задержки (фиг.7з), в течение которого полностью производится ускоренный заряд шунтирующего конденсатора 4.1, на выходе блока 20 задержки формируется импульсньй сигнал уровня логической 1, (фиг47и), который пос

з 0 5 О

, д

5

0

5

тупает на первый вход 23 ключевой схемы 22. Этот положительньш импульс- ный сигнал, пройдя через элемент НЕ 48, обеспечивает опрокидывание RS-триггера 49 в ключевой схеме 22 таким образом, что на его выходе появляется сигнал уровня логической 1 (фиг.7д), обеспечивающий срабатывание транзистора 50 и 51 ключевой схемы 22. В результате открывания транзистора 51 срабатывает реле 7. При этом все четыре нормально замкнутые контактные группы 6, 10, 13 и 16 реле 7 размыкаются, в рез ультате чего от второго и третьего входов блока 9 сравнения отключаются выходы источни- кой измерительного 14 и опорного 17 напряжений, но остаются указанные входы блока 9 сравнения под напряжением заряженных хронирующих конденсаторов 12 и 15. Кроме того, из-за размыкания нормально замкнутых контактных групп 6 и 10 реле 7 объект 2 контроля отключается от воздействия низкоомного резисторного делителя напряжения и исследуемая цепь 3.1 предоставляется на установление в ней фактического напряжения путе.м доза- ряда шунтирующего конденсатора 4.1 через высокоомный резистор 37 блока 9, соответствующего реальной величине сопротивления изоляции (фиг.7п). В результате открывания транзистора 50 в 1шючевой схеме 22 на ее первом выходе 24 (связанном с коллектором транзистора 50) появляется сигнал уровня логического О (фиг.7е), который запускает задатчик 25 вьщержки времени. Последний устанавливается на предельно возможную продолжительность вьщержки времени (фиг.7м), обеспечивающую полное заверщение переходного зарядного процесса в исследуемой цепи 3.1. В период шунтирования и сразу после расшунтирова- ния исследуемой цепи 3.1 на выходе блока 9 сравнения имеется сигнал уровня логического О (фиг.7р), что соответствует признаку пониженного сопротивления изоляции относительно заданного порогового уровня, определяемого (в период шунтирования цепи) источником 17 опорного напряжения и высокоомным резистором 38 блока 9 сравнения. В период расшунтирования исследуемой цепи от воздействия низ- кооомного резисторного делителя напряжения (в период контроля сопротивлеиия изоляции) в устройстве одновременно отключаются от второго и третьего входов блока сравнения соответственно источники 14 и 17 измерительного и опорного напряжений. Следовательно, в период расшунтирования заданный пороговый уровень определя- |ется высокоомным резистором 38 и имитатором источника 17 опорного напряжения - хронирующим конденсатором 15, заряженным в период обесточенного реле 7 (названного периодом шунтирования). Отключение от второго и третьего входов блока 9 сравнения (в период контроля сопротивления изоляции) источников 14 и 17 измерительного и опорного напряжений соответственно при обеспечении контроля сопротивления изоляции за счет напряжений, имеющихся на заряженных конденсаторах 12 и 15, позволяет устранить причины появления наводок от первичной сети переменного тока путем разрьша токов утечек, протекающих через высокоомные резисторы 37 и 38 блока 9 сравнения и соизмеримые величины межобмоточного сопротивления изоляции силового трансформатора (фиг.8).

Если сопротивление изоляции исследуемой цепи больше допустимого порога, то спустя некоторое время, затраченное на дозаряд шунтирующего конденсатора 4.1 от хронирующего конденсатора 12 (имитирующего источник 14 измерительного напряжения) через высокоомньм резистор 37 в блок 9 сравнения (фиг.7а), на его выходе появляется сигнал уровня логической 1 (фиг.7р) по времени ранее окончания контроля, которое определяется задатчиком 25 вьщержки времени (фиг. 7ф) .

Этот сигнал поступает на (К+1)-й (управляющий) вход переключающего блока 5, на вход блока 20 задержки и на второй вход 21 ключевой схемы 22 через первый вход открытого элемента И 18 и второй вход элемента ИЛИ 19 (фиг.7с,в). Передний фронт этого сигнала считывается счетчиком 44 переключающего блока 5, далее информация счетчика дешифрируется таким образом, что на выходе дешифратора 45 происходит сдвиг сигнала уровня логического О с первого 45.1 на второй 45.2 выход, тем самым обесточивается реле 46.1 и срабатьшает

0

5

0

5

0

5

0

5

0

5

реле 46.2 в переключающем блоке 5 (фиг . 7 л,м-) . Таким образом, происходит отключение первой исследуемой цепи, изменяется выходной сигнал блока 9 сравнения на уровень логического О (фиг.7п) и подключается вторая исследуемая цепь, у которой шунтирующий конденсатор 4.2 разряжен. Изменение выходного сигнала блок 9 сравнения с уровня логической 1 при контроле предьщущей исследуемой цепи с допустимым сопротивлением изоляции до уровня логического О (фиг.7п) при отключении этой цепи и подключении следующей, у которой шунтирующий конденсатор разряжен) способствует образованию на выходе блока 9 сравнения импульсных сигналов .уровня логической 1, которые, проходя через элементы И 18 и ИЛИ 19, являются запускающими импульсами блока 20 задержки, обнуляющими для ключевой схемы 22 и счетными дпя счетчика 44 в переключающем блоке 5 (фиг.7р, с.в). Таким образом, происходит досрочное окончание цикла контроля первой исследуемой цепи и переход блоками переключения 5, задержки 20, ключевой схемы 22 и задатчиком 25 вы- держки времени к контролю очередной цепи.

После обнуления ключевой схемы 22 импульсным сигналом, поступаюпщм на второй вход 21, на выходе RS-трнгге- ра 49 устанавливается сигнал уровня логического О, (фиг.7д), который обеспечивает запирание транзисторов 50 и 51 и обесточивание реле 7. Тогда снова происходит подключение выходов источников измерительного 14 и опорного 17 напряжений к второму и третьему входам блока 9 сравнения, а также к хронирующим конденсаторам 12 и 15 соответственно для их заряда, В случае, когда сопротивление изоляции исследуемой цепи меньше допустимого значения, сигнал уровня логического О на выходе блока 9 сравнения сохраняется в течение всего периода, определяемого задатчиком 25 вьдержки времени (фиг.7, п,т). В конце периода вьдержки времени с выхода задатчика 25 (выхода Q второго одновибратора 61) поступает импульсный сигнал уровня логического О (фиг.7ф) свидетельствующий о том, что за время, определяемое задатчиком 25, напряжение на исследуемой цепи не достигло

порогового уровня (фиг.7п), т.е. сопротивление изоляции этой цепи, например третьей, меньше заданного допустимого значения. При формирова- НИИ выходного импульса задатчиком 25 вьщержки времени RS-триггер 26 опрокидывается и на его выходах Q и IQ устанавливаются сигналы уровней соответственно логического

,(фиг.7г) и логической 1 При этом |Гаснет сигнальная лампочка 32 В норме, загорается лампочка 31 Меньше (фиг.7ц), регистрирующая заниженное сопротивление изоляции исследуемой цепи. Кроме того, сигнал с выхода Q RS-триггера 26 уровня логического О закрывает элемент И 18 для прохождения через него и элемент РЮИ 19 очередных импульсных сигналов с вы- хода блока 9 сравнения. Происходит останов автоматического контроля сопротивления изоляции. Счетчик 44 в переключающем блоке 5 фиксирует свое состояние, а дешифратор 34 и блок 35 сигнализации регистрируют номер цепи с забракованным сопротивлением изоляции.

Для обеспечения продолжения автоматического контроля остальных ис- следуемых цепей подачей сигнала Пус на шину 29 (фиг.76) RS-триггер 26 снова устанавливается в исходное состояние. На его выходах Q и Q устанавливаются сигналы уровней соот- ветственно логической 1 (фиг.7г) и логического О. При этом гаснет сигнальная лa ffloчкa 31 Меньше и загорается лa шoчкa 32 В норме. Кроме того, сигнал с выхода Q RS-триггера 26 уровня логической 1 снова обеспечивает разрешение прохождения чере элемент И 18 очередных импульсньк сигналов с выхода блока 9 сравнения.

Задатчик 25 вьщержки времени фор- мирует на своем выходе (выходе Q одновибратора 61) задержанный импульный сигнал только в том случае, если во время формирования задержки одно- вибратором 58, на его входе не про- изойдет изменение сигнала с переходо в исходное состояние с низкого на высокий уровень. Если же во время формирования задержки одновибратором 58, на его входе произойдет измене- ние сигнала в исходное состояние, то одновибратор 61 закрывается по R-входу инвертированным сигналом низкого уровня.

5

5 0

30 35 40

45 JQj

Следовательно, при появлении на выходе блока 9 сравнения сигнала уровня логической 1 (соответствующего признаку сопротивления изоляции исследуемой цепи более заданного предела) до момента окончания вьщержки времени задатчика 25, на его выходе не будет формироваться импульс уровня логического О (фиг.7а), поэтому RS-триггер 26 по-прежнему будет находиться в исходном состоянии, при котором на его Q-выходе сохраняется сигнал уровня логической 1, обеспечивающий прохождение через элементы И 18 и 19 сигналов уровня логической 1 с выхода блока 9 сравнения при контроле очередных исследуемых цепей (фиг.7р,с,в).

Одновременно с переключением исследуемых цепей производится регистрация их номеров в виде цифр на блоке 35 индикации, работающем от дешифратора 34, подключенного к информационным выходам счетчика 44 в переключающем блоке 5.

Разрыв цепи тока утечки через межобмоточное сопротивление изоляции полностью устраняет причины.появления наводок первичной сети на входах, а значит и на выходе блока сравнения, вследствие чего повьщ1ается помехо- защищенность устройства.Формула изобретения

Устройство контроля сопротивления изоляции, содержащее источники измерительного и опорного напряжений, К клемм для подключения К исследуемых цепей, зашунтированных конденсаторами, последовательно соединенные переключающий блок, блок сравнения и элемент И, последовательно соединенные элемент ИЛИ, блок задержки, ключевую схему и задатчик вьщержки времени, а также репе, К клемм для подключения объекта контроля соединены с соответствующими К входами переключающего блока, первый выход которого через последовательно соединенные первую нормально замкнутую контактную группу реле и первый низко- омный резистор подключен к общей шине, а через последовательно соединенные вторую нормально замкнутую контактную группу реле и второй низ- коомный резистор - с- вторым входом блока сравнения, второй вход элементй ИЛИ соединен с шиной запуска, выход элемента ИЛИ соединен с вторым входом ключевой схемы и с (К+1)-м (управляющим) входом переключающего блока, второй выход ключевой схемы соединен с первым выводом обмотки реле, второй вьшод которой соединен с общей шиной, щина обнуления соединена с третьим входом ключевой схемы и (К+2)-м входом переключающего блока, отличающееся тем, что с целью повышения помехозащищенности в него введены дешифратор, блок индикации, два хронирующих конденсатора, два сигнальных индикатора, элемент НЕ, RS-триггер и третья и четвертая нормально замкнутые контактные группы реле, положительный полюс источника измерительного напряжения через третью нормальло замкнутую контактную группу реле соединен с вторым входом блока сравнения, и первой обкладкой первого хронирующего конденсатора, положительный полюс источ- ника опорного напряжения через чет

р 0 5

5

вертую нормально замкнутую контактную группу реле соединен с третьим входом блока сравнения и первой обкладкой второго хронирующего конденсатора, вторые обкладки первого и второго хронирующих конденсаторов и отрицательные полюсы источников измерительного и опорного напряжений соединены с общей шиной, шина запуска через элемент НЕ соединена с R-входом RS-триггера, S-вход которого соединен с выходом задатчика вьщержки времени, инверсный Q-выход- с вторым входом элемента И и с первым вьшодом первого сигнального индикатора, а прямой Q-выход - с первым выводом второго сигнального индикатора, вторые выводы сигнальных индикаторов соединены с положительной шиной питания, М информационных входов дешифратора соединены с соответствующими М выходами переключающего блока, N выходов дешифратора соединены с N входами блока сигнализации.

Фиг.г

. 5.1 S.m

Обнш 21

iE

Ч

3

(Л

s а J

53

i

sit

2

50

ФигЛ

27

6t

Г1

Фиг.У

67

%

69

нн

Ш(/г5

v€ J ; ггов5огц п

№

в

lKu3l S

Фиг.8

| Устройство для допускового контроля сопротивлений | 1984 |

|

SU1310747A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь для устройства контроля сопротивления изоляции | 1985 |

|

SU1357870A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-10-07—Публикация

1988-06-08—Подача