(Л

с

Изобретение относится к информационно-измерительной технике и может быть использовано для автоматизации процессов разбраковки конденсаторов по допусковым группам. Цель изобретения - повышение точности измерений путем измерения относительного отклонения емкости конденсатора от номинального значения с учетом диэлектрических потерь измеряемой емкости и вне зависимости от значений частот сигналов источников переменного напряжения. Устройство содержит два источника 1 и 2 переменного напряжения, два управляемых ключа 3 и 4, эталонный конденсатор 5, измеряемый конденсатор 6, резистор 9, блок 10 управления, два преобразователя 11 и 12 напряжение - код, вычислительный блок 13. 3 ил.

fu.f

ел

х со

эо

Изобретение относится к информационно-измерительной технике и может быть использовано для автоматиз ации процессов разбраковки конденсаторов по допусковым группам.

Целью изобретения является повышение точности измерений путем измерения относительного отклонения емкости конденсатора от номинального значения с учетом диэлектрических потерь измеряемой емкости и вне зависимости от значений частот сигналов источников переменного напряжения.

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - схема блока управления; на фиг. 3 - схемы преобразователей напряжение - код.

Устройство (фиг.1) содержит два источника 1 и 2 переменного напряжения, два управляемых ключа 3 и 4, эталонньш конденсатор 5 (емкость С, сопротивление R), измеряемый конденсатор б (емкость С;с, сопротивление R), клеммы 7 и 8 для подсоединения измеряемого конденсатора 6,резистор 9 (сопротивление R,), блок 10 управления, два преобразователя 1I и 12 напряжение - код и вычислительный блок 13.

Источники 1 и 2 переменного напряжения, попеременно через первый ключ 3 и второй ключ А соединены с эталонным конденсатором 5 или измеряе-- мым конденсатором б, подключаемым к клеммам 7 и 8, которые через резистор 9 соединены с обшей шиной и вторым преобразователем 12 напряжение - код, разрядные выходы кода которого соединены с второй шиной данных вычислительного блока 13, а второй выход готовности данных - с вторым входом разрешения записи вычислительного блока 13. Средняя точка между ключами 3 и 4 соединена с первым преобразователем И напряжение - код, разрядйые выходы кода которого соединены с первой шиной данных вычислительного блока 13, а второй выход готовности данных - с первым входом разрешения записи вычислительного блока 13. Выход Конец записи вычислительного блока 13 соединен с входом блока 10 управления, первый выход которого- соединен с управляющим входом первого управляемого ключа 3,второй выход - с управляющим входом второго управляемого ключа 4, третий выход - с входом начала преобразования перво

5

0

5

0

5

0

5

0

5

го преобразователя 11, напряжение - код, а четвертый выход - с входом начала преобразования второго преобразователя 12 напряжение - код.

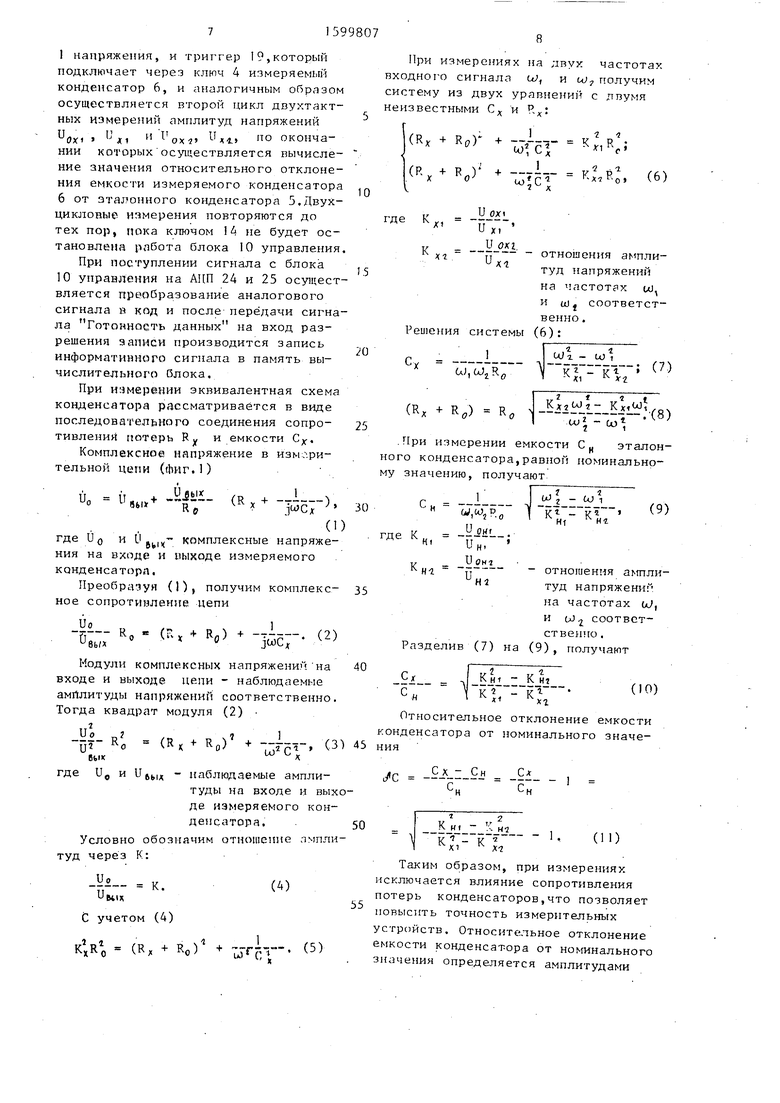

Блок 10 управления ((Ьиг.2) содержит два ключа 14 и 15, два двоичных счетчика 16 и 17, два триггера 18 и 19 и два элемента 20 и 21 задержки. Вычислительный блок.13 через ключ 14 соединен с первым двоичным счетчиком 16 и первым входом первого триггера 18, выход которого соединен с управляющим входом ключа 3 и через элементы 20 и 21 аадержки с преобразователями 11 и 12 напряжение - код. Средняя точка между первым двоичным счетчиком 16 и первым триггером 18 соединена с входом второго двоичного счетчика 17,выход которого соединен с вторым входом первого триггера 18 и первым входом второго триггера 19, выход которого соединен с управляющим входом ключа 4. Второй вход второго триггера 19 соединен с обшей шиной. Через ключ 15 на второй вход первого триггера

18и на первый вход второго триггера

19подается положительное напряжение.

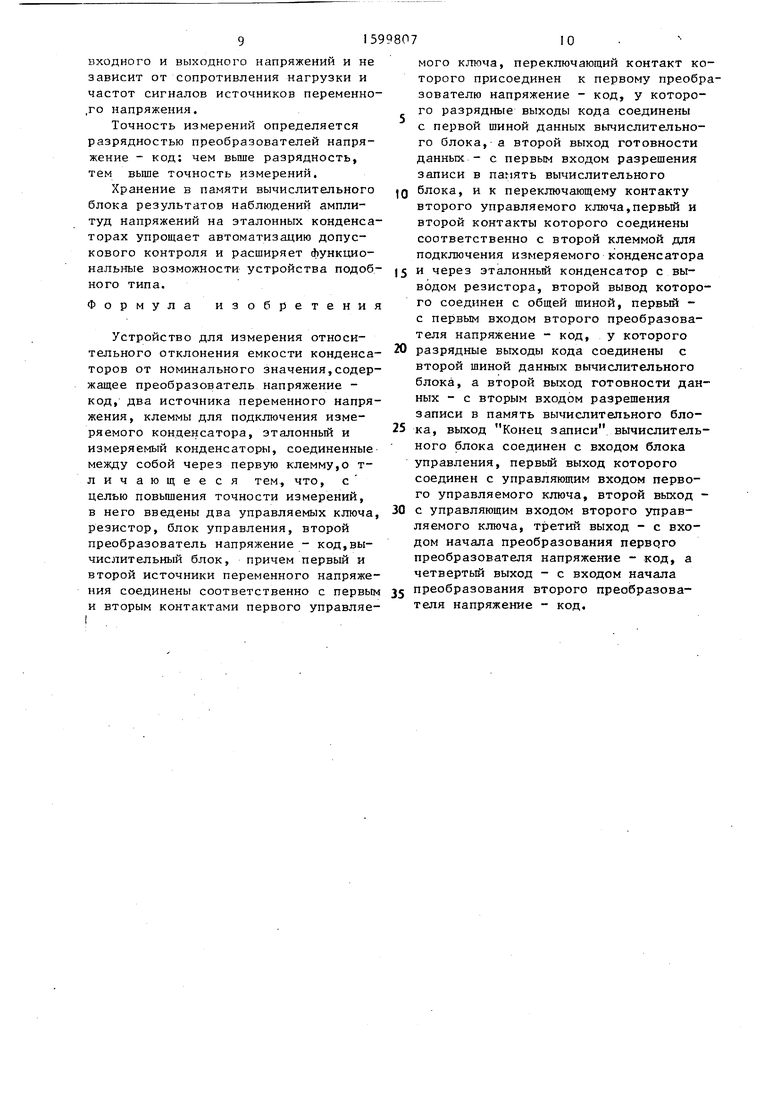

Преобразователи 11 и 12 напряжение - код (фиг.3,а,б) аналогичны и содержат амплитудные детекторы 22 и 23 и Функционально-законченные ана- лого-циЛровые преобразователи 24 и 25, в .ix имеются клеммы выхода 10-разрядного цифрового кода,Готовность данных, Начало преобразования, а также питания и аналогового входа.

Устройство работает следующим образом.

По сигналу Пуск блока 10 управления ключ 3 подключает к измерительной цепи источник 1 переменного напряжения с частотой сигнала uj. , а ключ 4 - эталонный конденсатор 5.По сигналу блока 10 управления первьй преобразователь 1I преобразует в код амплитуду напряжения UQ, на входе эталонного конденсатора 5,значение которой заносится в память вычислительного блока 13. Сигнал об окончании записи с вычислительного блока 13 поступает в блок 10 управления. С задержкой по времени по сравнению с сигналом блока 10 управления, поступающим на первый преобразователь 11, с блока 1 О управления

подается сигнал на цторой преобразователь 12, который преобразует в ко амплитуду напряжения U, на выходе эталонного конденсатора 5,значение которо-й заносится в память вычислительного блока 13. По окончании запси сигнала в память i-a блок 10 упраления с вычислительного блока 13 поступает второй сигнал, от которог в блоке 10 вырабатывается сигнал, подключающий через ключ 3 к измерительной цепи источник 2 переменного напряжения с частотой сигнала .По аналогичной схеме последовательно во времени с блока 10 управления поступают сигналы на преобразовател 11 и 12, которые преобразуют амплитуды напряжений и„ и и„, на входе и выходе эталошгаго конденсатора 5, значения которых заносятся в память вычислительного блока 13. После последовательной передачи двух сигналов окончания записи в память с вычислительного блока 13 в блок 10 управления (по счету двух сигналов от записи результатов измерения на частоте О), и двух сигналов на частоте

О),, а всего четырех сигналов), где вырабатываются сигналы, которые под- , ключают через ключ 3 к цепи источник 1 переменного напряжения с частотой сигнала со, , а также через ключ 4 - измеряемый конденсатор 6, аналогично преобразуются в коды и заносятся в память вычислительного блока 13 послдовательно значения U,, и U., агтли- туд напряжений на входе и выходе измеряемого конденсатора 6 соответственно.

После поступления двух последовательных сигналов окончания записи в память с вычислительного блока 13 в блок 10 управления в нем вырабатывается управляющий сигнал на ключ 3, который подключает к цепи источник 2 переменного напряжения с частотой сигнала Аналогично преобразуют- .ся и заносятся в память вычислительного блока 13 последовательно во врег мени значения U Q -Ч г амплитуд напряжений на входе и выходе измеряемого конденсатора 6 соответственно. По заверщении второго цикла двухтактных измерений на вход блока 10 управления последовательно поступают два сигнала об окончании записи, которые по аналогичной схеме повторяют измерения (U, и U,; U р и

99807

и

П

и и

6

и

Н7 i ort И л,; ояг и U,,j) до

осуществления в блоке 10 управления команды Останов. В вычислительном блоке получают относительное отклонение емкости измеряемого конденсатора 6 от номинального значения по алгоритму

10

:fC

где К

Ht

t5

20

х

и ОК2

ношения амплитуд напряжений при измерении емкости эталонного конденсатора на двух частотах W, и to.;

К

X 1

25

л

и Ох -2

иГГ

30

4С

отношения амплитуд напряжений при измерении емкости измеряемого конденсатора на тех же частотах соответственно, При включении ключа 15 подается положительное напряжение на входы триггеров 18 и 19, которые через ключ 3 подключают источник 1 переменного напряжения к цепи, через ключ 4 - эталонньш конденсатор 5, а че- 3 рез элементы 20 и 21 задержки последовательно во времени запускают преобразования сигналов в преобразова-. талях Пи 12 соответственно.

На вход блока 10 управления поступает первый сигнал об окончании запи-. си в память вычислительного блока 13 значения амплитуды напряжения и 4„, на входе эталонного конденсатора 6, а затем второй сигнал об окончании записи и „, на выходе эталонного конденсатора 6, от которого срабатывает первый триггер 18 и подключает ключом 3 источник 2 переменного напряжения к цепи, а также запуска- 0 ет преобразования сигналов в преобразователях 11 и 12. На вход блока 10 управления поступает третий сигнал об окончании записи , а за- тем четвертый сигнал об окончании 5 записи Uj, в результате срабатывает первый двоичный счетчик 16, а затем вторрй двоичный счетчик 1/,вследствие чего срабатывают триггер 18, который подключает к цепи источник

1599807

I напряжения, и триггер 19,который подключает через ключ 4 измеряемый конденсатор 6, и аналогичным образом осуществляется второй цикл двухтактных измерений амплитуд напряжений 0X1 ох2 j4. О окончании которых осуществляется вычисле- ние значения относительного отклонения емкости измеряемого конденсатора 6 от эталонного конденсатора З.Двух- цикловые измерения повторяются до тех пор, пока ключом lA це будет остановлена работа блока 10 управления

При поступлении сигнала с блока 10 управления на АЦП 24 и 25 осущест вляется преобразование аналогового сигнала в код и после передачи сигнала Готонноеть данных на вход разрешения записи производится запись информативного сигнала в память вычислительного блока.

При измерении эквивалентная схема конденсатора рассматривается в виде последовательного соединения сопро- тивления ttOTepb Ry и емкости С,

Комплексное напряжение в изм:лри- тельной цепи (фиг.)

о u.. (.

(О

где и о и и комплексные напряжения на входе и выходе измеряемого конденсатора.

Преобразуя (1), получим комплекс- ное сопроти}аление цепи

Uo вь/х

1

( о 2)

Модули комплексных напряжений на 40 входе и выходе цепи - наблюдаемые амплитуды напряжении соответственно. Тогда квадрат модуля (2)

7

-цТ- RO (RX + RO) + -ТТр, (3) 45 вык л

где и, и - наблюдаемые амплитуды на входе и выходе измеряемого конденсатора. . 50 Условно обозначим отношение пмплитуд через К:

К.

(4)

(4)

(RX + RO) -

8

При измерениях на двух частотах входного сигнала w, и и; получим систему из двух уравнений с двумя неизвестными Cv и R,:

Лл

(6)

де К

X

кг

и 0X1

иУГ

У 0X1.

и

х-г

- отношения туд напряжений на частотах uJ, и О) J соответственно . Решения системы (6):

W,(J,,R

+ R,,) R,

Wl - LO

К - 1C Ч- - 1 л-г

(7)

, г t It KxfW

tu

2

СО

: (8)

.При измерении емкости С„ эталонного конденсатора,равной номинальному значению, получают

(9)

туд напряжени: на частотах (xj, и ы соответ- стве}пго. (7) на (9), получают

.Сх J - KS,

к

00)

ч

Относительное отклонение емкости конденсатора от номинального значения

н С..

Сл

с„

V 1

Х1 М Таким образом, при измерениях исключается влияние сопротивления потерь конденсаторов,что позволяет повысить точность измерительных устройств. Относительное отклонение емкости конденсатора от нo fинaльнoгo значения определяется амплитудами

входного и выходного напряжении и не зависит от сопротивления нагрузки и частот сигналов источников переменно- ,го напряжения.

Точность измерений определяется разрядностью преобразователей напряжение - код: чем выше разрядность, тем выше точность измерений.

Хранение в памяти вычислительного блока результатов наблюдений амплитуд напряжений на эталонных конденсаторах упрощает автоматизацию допус- кового контроля и расширяет функциональные возможности устройства подобного типа.

Формула изобретения

Устройство для измерения относительного отклонения емкости конденсаторов от номинального значения,содержащее преобразователь напряжение - код, два источника переменного напряжения, клеммы для подключения измеряемого конденсатора, эталонный и измеряемый конденсаторы, соединенные между собой через первую клемму,о т- личающееся тем, что, с целью повьппения точности измерений, в него введены два управляемых ключа, резистор, блок управления, второй преобразователь напряжение - код,вычислительный блок, причем первый и второй источники переменного напряжения соединены соответственно с первым и вторым контактами первого управляемого ключа, переключающий контакт которого присоединен к первому преобразователю напряжение - код, у которого разрядные выходы кода соединены с первой шиной данных вычислительного блока, а второй выход готовности данных - с первым входом разрешения записи в память вычислительного

g блока, и к переключающему контакту второго управляемого ключа,первый и второй контакты которого соединены соответственно с второй клеммой для подключения измеряемого конденсатора и через эталонный конденсатор с выводом резистора, второй вывод которого соединен с общей шиной, первый - с первым входом второго преобразователя напряжение - код, у которого разрядные выходы кода соединены с второй щиной данных вычислительного блока, а второй выход готовности данных - с вторым входом разрешения записи в память вычислительного бло5 ка, выход Конец записи вычислительного блока соединен с входом блока управления, первый выход которого соединен с управляющим входом первого управляемого ключа, второй выход 0 с управляющим входом второго управляемого ключа, третий выход - с входом начала преобразования перврго преобразователя напряжение - код, а четвертый выход - с входом начала

C преобразования второго преобразователя напряжение - код.

5

0

Фиг. 2,

Фиг.З

| Эпштейн С.Л., Давидович В.Г., Литвинов Г.И | |||

| Цифровые приборы и системы для измереишЧ параметров конденсаторов | |||

| М.: Сов | |||

| радио,1978, с.15, рис.1.4в. |

Авторы

Даты

1990-10-15—Публикация

1988-03-21—Подача