ключ 3, делитель 4 входного сигнала, блоки 5-7 компараторов, мультиплексоры 8 и 9, триггеры 10,11,16- 27, ключи 28-30, линии 31-33 задерж- - ки, преобразователи 34-36 время- амплитуда, счетчики 37 и 38 и преобразователь 39 амплитуда-код. Делитель 4 входного сигнала представляет собой резистивно-емкостную цепочку и служит для нормализадии измеряемого сигнала к амплитуде,

.обеспечивающей нормальный режим работы блоков 5-7 компараторов. Он

Изобретение относится к электроизмерительной технике и может быть использовано для измерения характеристик элек трических сиг- налов в автоматике, вы шслительной технике, приборостроении.

Цель изобретения - повьшение достоверности контроля характеристик электрических сигналов за счет исключения неоднозначности счета импульсов счетчиками грубого измерения сигнала.

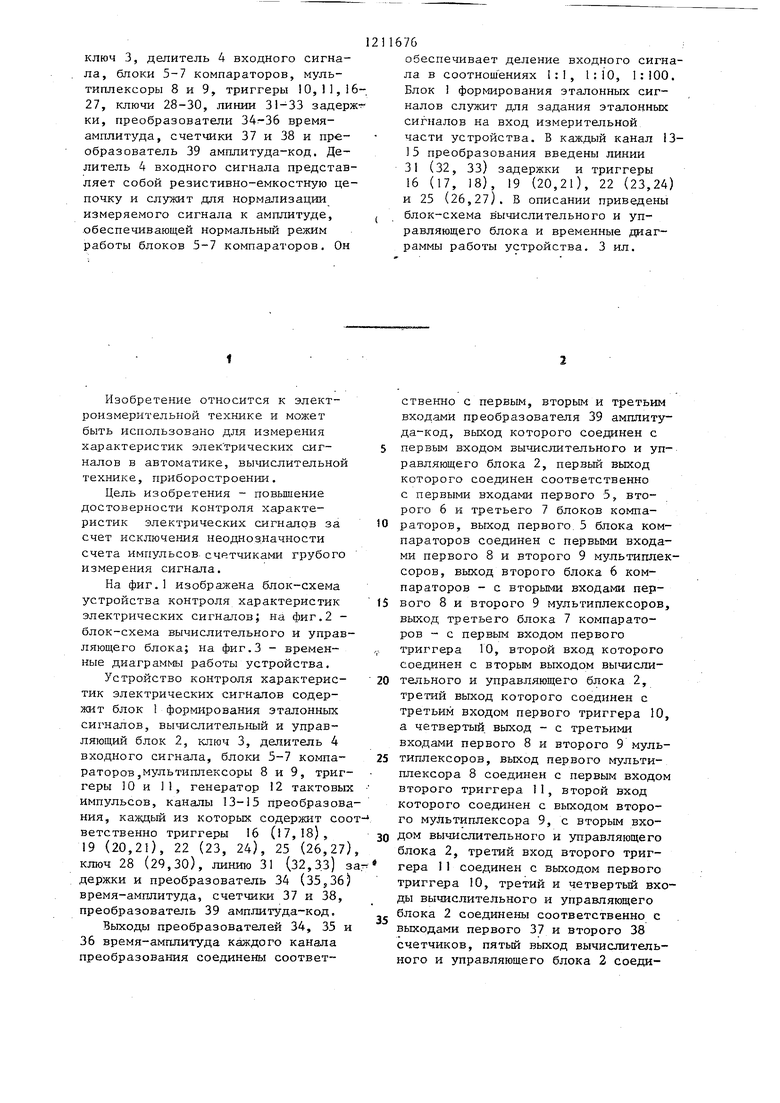

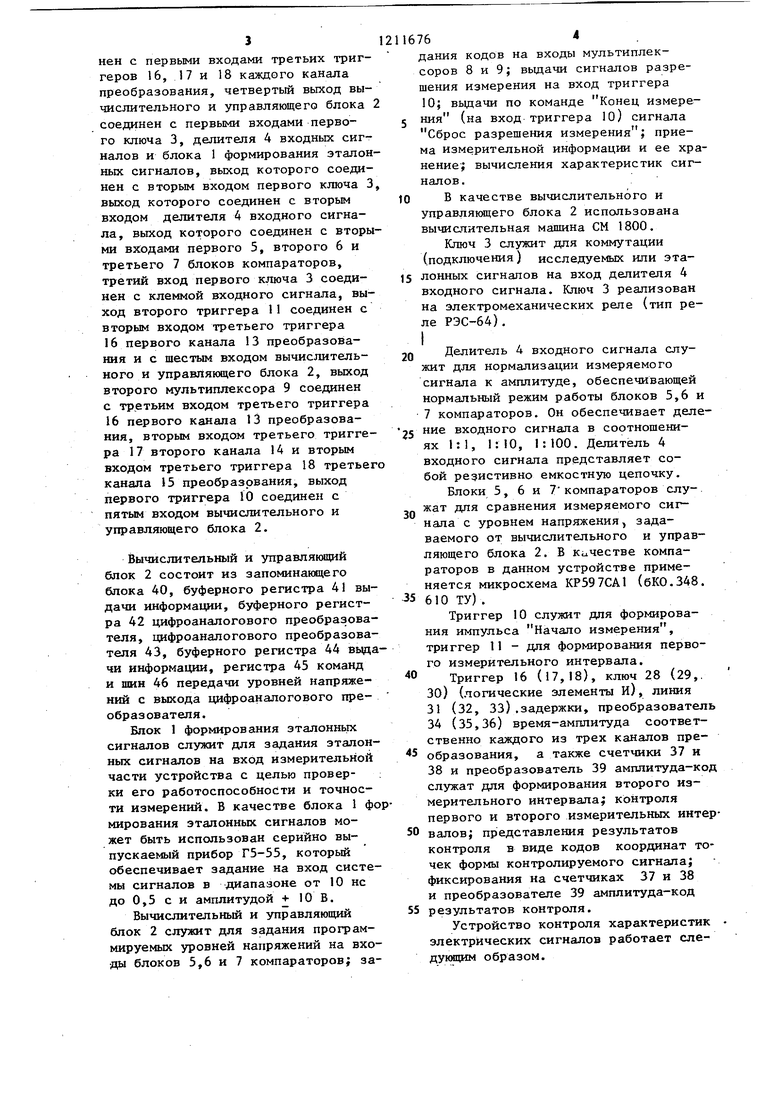

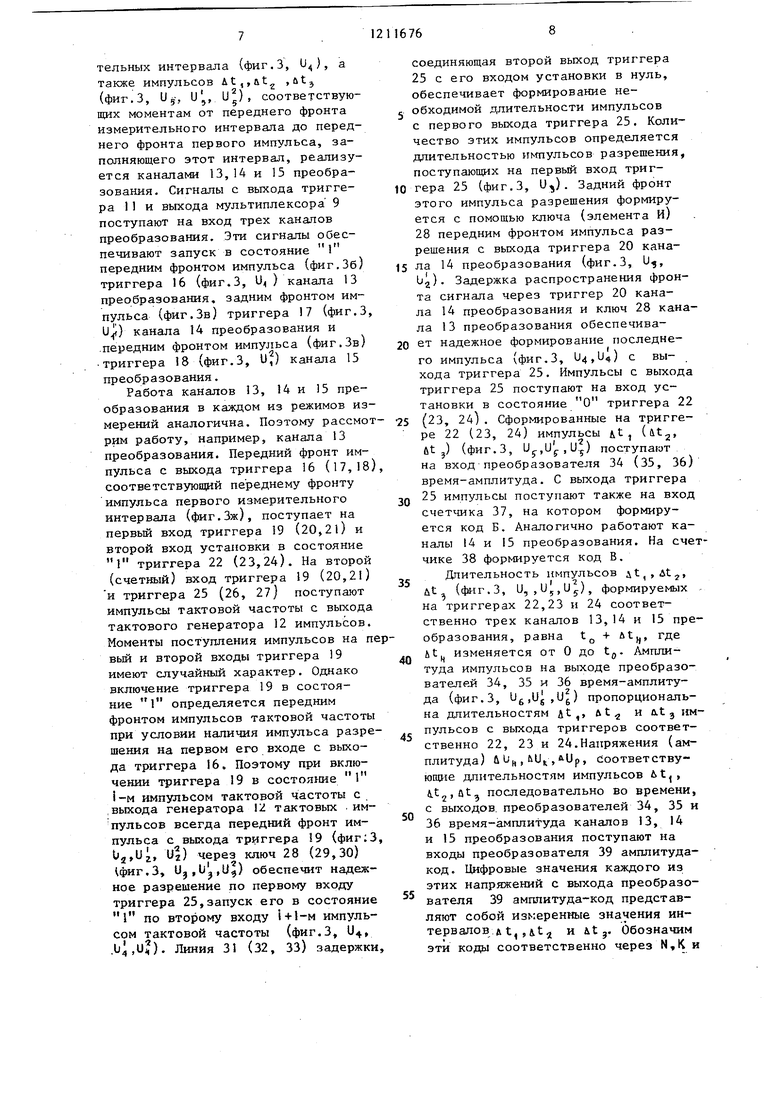

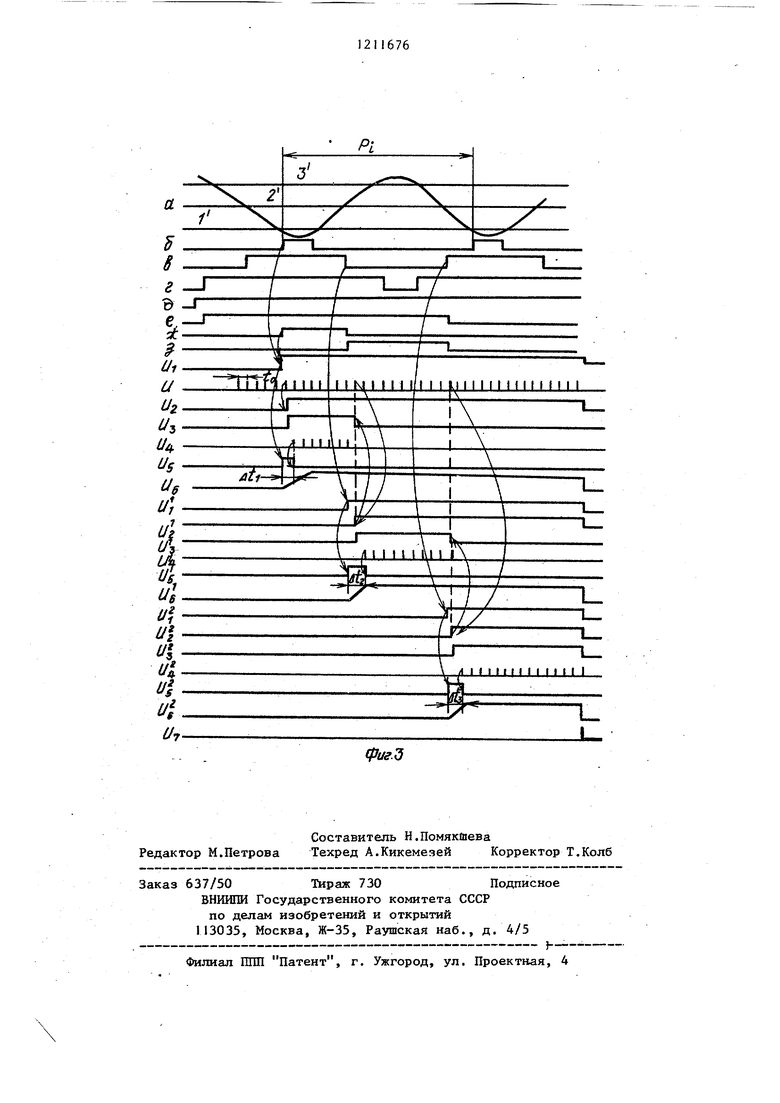

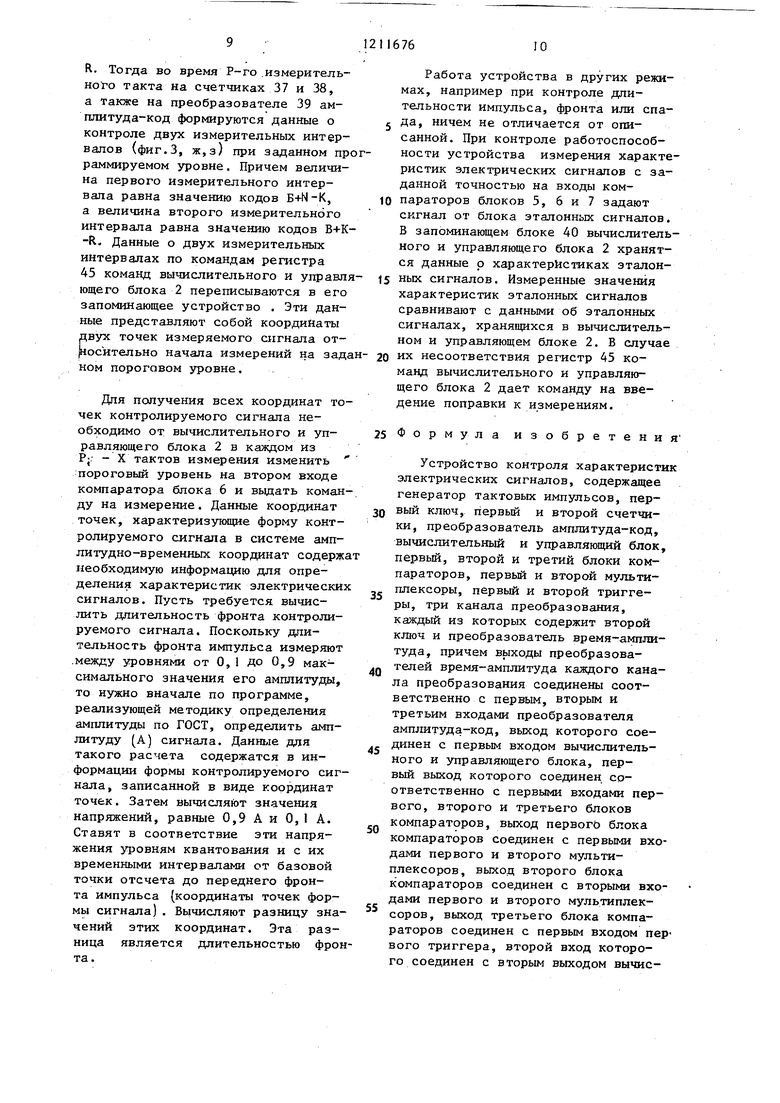

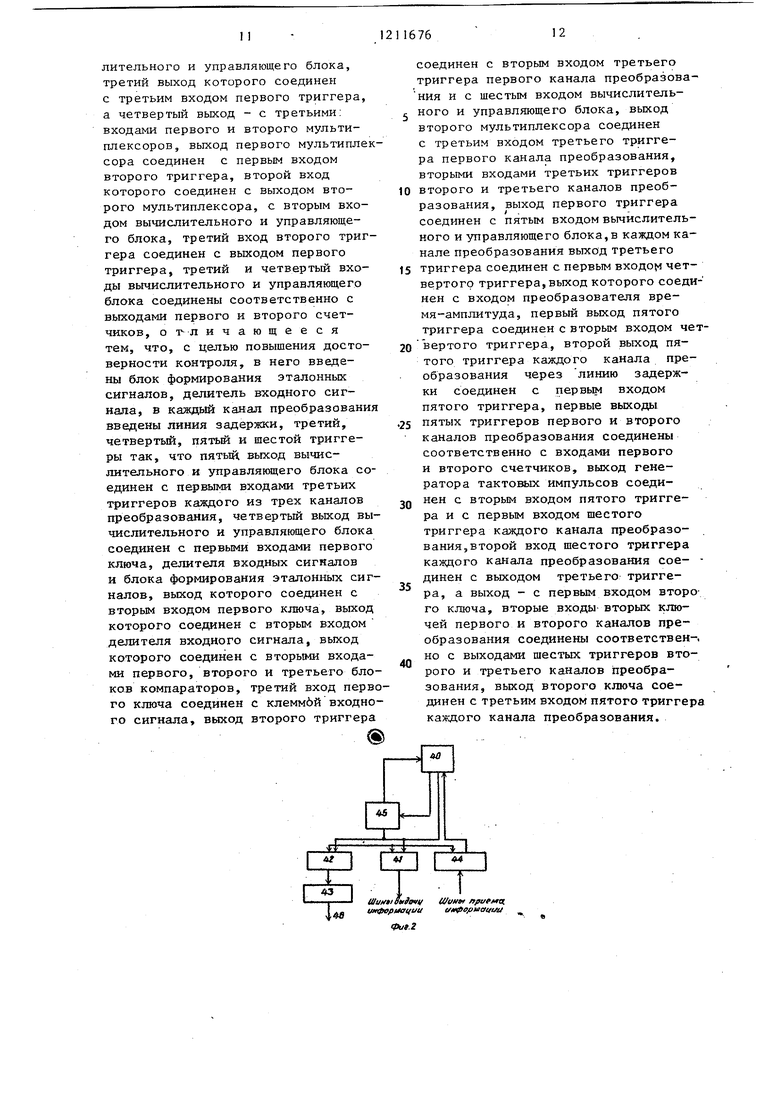

На фиг.1 изображена блок-схема устройства контроля характеристик электрических сигналов; на фиг,2 - блок-схема вычислительного и управляющего блока; на фиг,3 - временные диаграммы работы устройства.

Устройство контроля характерис- тик электрических сигналов содержит блок t формирования эталонных сигналов, вычислительный и управляющий блок 2, ключ 3, делитель 4 входного сигнала, блоки 5-7 компа- раторов,мультиплексоры 8 и 9, триггеры 10 и 11, генератор 12 тактовых импульсов, каналы 13-15 преобразования, каждый из которых содержит соо ветственно триггеры 16 (17,18), 19 (20,21), 22 (23, 24), 25 (26,27) ключ 28 (29,30), линию 31 (32,33) з держки и преобразователь 34 (35,36) время-амплитуда, счетчики 37 и 38, преобразователь 39 амплитуда-код.

Выходы преобразователей 34, 35 и 36 время-амплитуда каждого канала преобразования соединены соответ

1676

обеспечивает деление входного сигнала в соотношениях 1:1, 1:10, 1: 100. Блок 1 формирования эталонных сигналов служит ДД1Я задания эталонных сигналов на вход измерительной части устройства, В каждый канал 1315преобразования введены линии 31 (32, ЗЗ) задержки и триггеры

16(17, 18), 19 (20,21), 22 (23,24) и 25 (26,27). В описании приведены блок-схема вычислительного и управляющего блока и временные диаграммы работы устройства. 3 ил.

ственно с первым, вторым и третьим входами преобразователя 39 амплитуда-код, выход которого соединен с первым входом вычислительного и управляющего блока 2, первый выход которого соединен соответственно с первыми входами первого 5, второго 6 и третьего 7 блоков компараторов, выход первого. 5 блока компараторов соединен с первыми входами первого 8 и второго 9 мультиплексоров, выход второго блока 6 компараторов - с вторыми входами первого 8 и второго 9 мультиплексоров, выход третьего блока 7 компараторов - с первым входом первого триггера 10, второй вход которого соединен с вторым выходом вычислительного и управляющего блока 2, третий выход которого соединен с третьим входом первого триггера 10, а четвертый, выход - с третьими входами первого 8 и второго 9 мультиплексоров, выход первого мультиплексора 8 соединен с первьм входом второго триггера 11, второй вход которого соединен с выходом второго мультиплексора 9, с вторым входом вычислительного и управляющего блока 2, третий вход второго триггера I1 соединен с выходом первого триггера 10, третий и четвертый входы вычислительного и управляющего блока 2 соединены соответственно с выходами первого 37 и второго 38 счетчиков, пятьй выход вычислительного и управляющего блока 2 соеди3

нен с первыми входами третьих триггеров 16, 17 и 18 каждого канала преобразования, четвертый выход вычислительного и управляющего блока соединен с первыми входами первого ключа 3, делителя 4 входных сигналов и блока 1 формирования эталонных сигналов, выход которого соединен с вторым входом первого ключа 3 выход которого соединен с вторым входом делителя 4 входного сигнала, выход которого соединен с вторыми входами первого 5, второго 6 и третьего 7 блоков компараторов, третий вход первого ключа 3 соединен с клеммой входного сигнала, выход второго триггера 11 соединен с вторым входом третьего триггера 16 первого канала 13 преобразования и с шестым входом вычислительного и управлякядего блока 2, выход второго мультиплексора 9 соединен с третьим входом третьего триггера 16 первого канала 13 преобразования, вторым входом третьего триггера 17 второго канала 14 и вторым входом третьего триггера 18 третьег канала 15 преобразования, выход первого триггера 10 соединен с пятым входом вычислительного и управляющего блока 2.

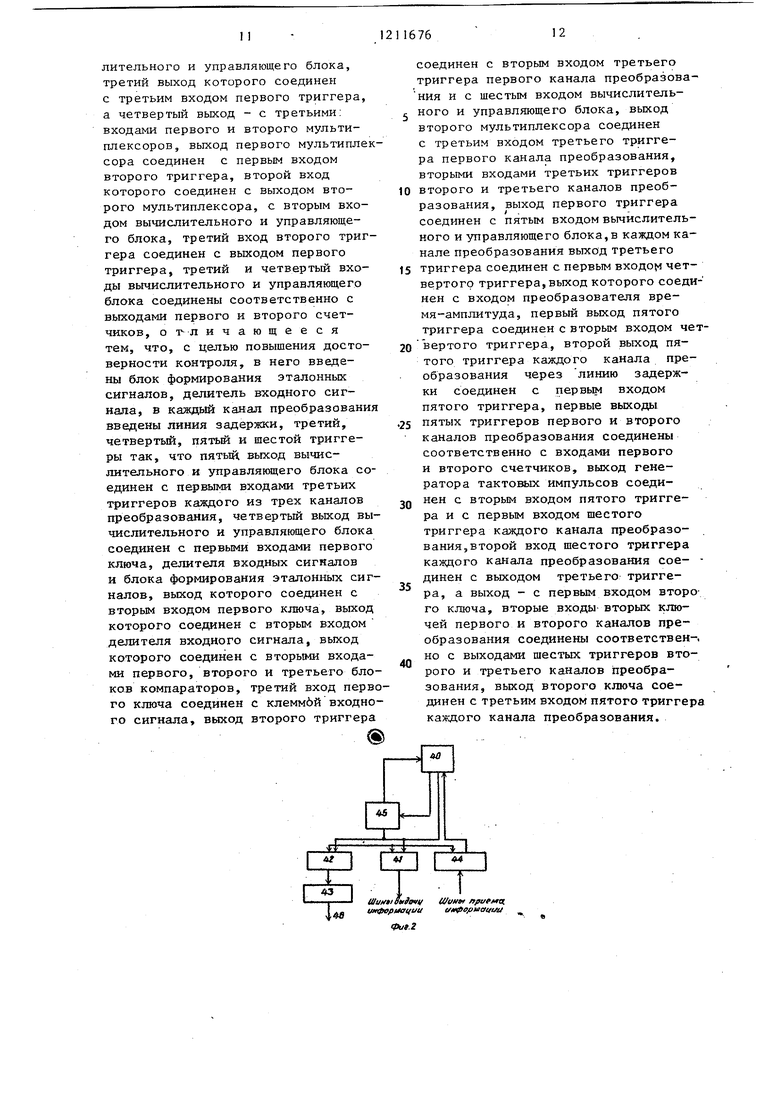

Вычислительный и управляющий блок 2 состоит из запоминаидего блока 40, буферного регистра 41 выдачи информации, буферного регистра 42 цифроанашогового преобразователя, цифроаналогового преобразователя 43, буферного регистра 44 вьща чи информации, регистра 45 команд и шин 46 передачи уровней напряжений с выхода цифроаналогового пре- образователя.

Блок 1 формирования зталонньпс сигналов служит для задания эталон- ных сигналов на вход измерительной части устройства с целью провер- ки его работоспособности и точности измерений. В качестве блока 1 фомирования эталонных сигналов может быть использован серийно выпускаемый прибор Г5-55, который обеспечивает задание на вход системы сигналов в диапазоне от 10 не до 0,5 си амплитудой + 10 В.

Вычислительный и управляющий блок 2 служит для задания программируемых уровней напряжений на входы блоков 5,6 и 7 компараторов; за1676

Дания кодов на входы мультиплексоров 8 и 9; вьщачи сигналов разрешения измерения на вход триггера 10; выдачи по команде Конец измере5 ния (на вход триггера 10) сигнала Сброс разрешения измерения ; приема измерительной информации и ее хранение; вычисления характеристик сигналов .

0 В качестве вычислительного и управдякяцего блока 2 использована вычислительная машина СМ 1800.

Ключ 3 служит для коммутации (подключения) исследуемых или эта5 лонных сигналов на вход делителя 4 входного сигнала. Ключ 3 реализован на электромеханических реле (тип реле РЭС-64).

Q Делитель 4 входного сигнала служит для нормализации измеряемого сигнала к амплитуде, обеспечивающей нормальный режим работы блоков 5,6 и 7 компараторов. Он обеспечивает деле- 5 ние входного сигнала в соотношениях 1:1, 1:10, 1: 100. Делитель 4 входного сигнала представляет собой резистивно емкостную цепочку.

Блоки 5, 6 и 7 компараторов слу-. жат для сравнения измеряемого сигнала с уровнем напряжения, задаваемого от вычислительного и управляющего блока 2. В Качестве компараторов в данном устройстве применяется микросхема КР597СА1 (бКО.348.

5 610 ТУ).

Триггер 10 служит дпя формирования импульса Начало измерения, триггер 11 - для формирования первого измерительного интервала,

0 Триггер 16 (17,18), ключ 28 (29,. ЗО) (логические элементы И), линия 31 (32, 33).задержки, преобразователь 34 (35,36) время-амплитуда соответственно каждого из трех каналов пре5 образования, а также счетчики 37 и 38 и преобразователь 39 амплитуда-код служат для формирования второго измерительного интервала; контроля первого и второго измерительных интер0 валов; пр1едставления результатов

контроля в виде кодов координат точек формы контролируемого сигнала; фиксирования на счетчиках 37 и 38 и преобразователе 39 амплитуда-код

5 результатов контроля.

Устройство контроля характеристик электрических сигналов работает следующим образом.

Пусть в качестве входного сигнала служит исследуемый сигнал, поступающий на входную клемму устройства, или эталонный сигнал с выхода блока 1 формирования эталонных иг- налов. Тогда по команде вычислительного и управляющего блока 2 в его буферный регистр 41 выдачи информации, а также в буферный регистр 42 цифроаналогового преобразователя записываются следующие управляющие коды: код управления ключом 3; код управления делителем 4 входного сигнала; код формирования уровней напряжений; код задания режимов измерения на входы мультиплексоров

и 9. 1

Измеряемый сигнал через ключ 3 и делитель 4 входного сигнала поступает на первые входы компараторов блоков 5,. 6 и 7, на вторые входы которых поступают опорные уровни напряжений по пшне 46 от цифроана- логового преобразователя 43 вычислительного и управляющего блока 2, При этом, если амплитуда сигнала на первых входах компараторов превышает опорные уровни 1апряже- ний на вторых входах компараторов блоков 5, 6 и 7, то с их вьзходов через мультиплексоры 8 и 9 и триггер 1 импульсы поступают на входы первого и второго разрядов буферного регистра 44 приема информации вычислительного и управляющего блока 2. Единичные состояния первого и второго триггеров буферного регистра приема информащш являются признаком на изменение коэффициента деления делителя 4 входного сигнала. Вычислительный и управляющий блок 2 по команде регистра 45 команд с выхода запог.шнающего блока 40 изменяет код управления делителя 4 входного сигнала и передает его через буферные регистры 41 вьщачи информации. Таким образом измерительный сигнал формируют по амплитуде, обеспечивающей необходимый режим рабоим блоков 5,6 и 7 компараторов. После этого с выхода цифроаналогового преобразо- вателя 43 вычислительного и управляющего блока 2 задают уровень напряжения (фиг.За,l) на второй вход компаратора блока 5 на время измерительных тактов, уровень напряжения (фиг.За, 2) на второй вход компараторов блока 6 на время Pj-го измерительного такта, а уро- 5 вень напряжения (фиг.За, З) на второй вход компаратора блока 7 на время Р измерительных тактов.

Тогда сигналы (фиг.Зб, в) с выходов компараторов блоков 5 и 6 по10 ступают на входы мультиплексоров 8 и и 9, а сигналы с выхода компаратора блока 7 (фиг.Зг) поступают на вход триггера 0. На второй вход триггера 10 поступает сигнал

5 (фиг.3д разрешения измерения от первого разряда буферного регистра 41 вьщачи информации вычислительного и управляющего блока 2. Триггер 0 устанавливается в состояние 1

0 (фиг.Зе). Это соответствует переднему фронту импульса Начало измерения . С выхода триггера 10 импульс Начало измерения поступает на вход триггера 11 и в третий

5 разряд буферного регистра 4 приема информации вычислительного и

управляющего блока 2. I

Пусть на входы мультиплексоров Q 8 и 9 задан режим, заключающийся в определении координат точек формы контролируемого сигнала. Это обеспечивает прохождение сигнала с выхода блока 5 компараторов через мультиплексор 8 на вход установки в состояние 1 триггера 1I (фиг.Зж) и прохождение сигнала с выхода блока 6 компараторов через мультиплексор 8 на вход установки в состояние О триггера 11 (фмг.Зж). Сформированный на триггере 11 импульс (фиг.Зж) является первым измерительным интервалом. Он соответствует времени от начала измерений (координат) до момента времени пересечения фронта контролируемого сигнала с уровнем напряжения, заданного от вычислительного и управляющего блока 2 На вторые входы блока 6 компараторов. Второй измерительный интервал соответствует промежутку времени, когда уровень контролируемого сигнала выше уровня, задаваемого на второй вход блока 6 компарато- ров напряжения (фиг.За). Выделение числа импульсов тактовой частоты генератора 12 тактовых импульсов (фиг,2, U), заполняющих оба измери5

5

0

тельных интервала (фиг.З, U), а также импульсов At,,ut,utj (фиг.З, Uj, U j, Up, соответствующих моментам от переднего фронта измерительного интервала до переднего фронта первого импульса, заполняющего этот интервал, реализуется каналами 13,14 и 15 преобразования. Сигналы с выхода триггера 11 и выхода мультиплексора 9 поступают на вход трех каналов преобразования. Эти сигналы обеспечивают запуск в состояние Г передним фронтом импульса (фиг.Зб) триггера 16 (фиг.З, U ) канала 13 преобразования, задним фронтом импульса (фиг.Зв) триггера 17 (фиг.З, и) канала 14 преобразования и .передним фронтом импульса (фиг.Зв) триггера 18 (фиг.З, U) канала 15 преобразования.

Работа каналов 13, 14 и 15 преобразования в каждом из режимов измерений аналогична. Поэтому рассмотрим работу, например, канала 13 преобразования. Передний фронт импульса с выхода триггера 16 (17,18) соответствующий переднему фронту импульса первого измерительного интервала (фиг.Зж), поступает на первый вход триггера 19 (20,21) и второй вход установки в состояние 1 триггера 22 (23,24). На второй (счетный) вход триггера 19 (20,21) и триггера 25 (26, 27) поступают импульсы тактовой частоты с выхода тактового генератора 12 импульсов. Моменты поступления импульсов на певый и второй входы триггера 19 имеют случайный характер. Однако включение триггера 19 в состояние 1 определяется передним фронтом импульсов тактовой частоты при условии наличия импульса разрешения на первом его входе с выхода триггера 16, Поэтому при включении триггера 19 в состояние 1

i-M импульсом тактовой частоты с ,выхода генератора 2 тактовых . импульсов всегда передний фронт импульса с выхода триггера 9 (фиг;3 t j.Uj, Uz) через ключ 28 (29,30) фиг.З, Uj,Uj,U) обеспечит надежное разрешение по первому входу триггера 25,запуск его в состояние 1 по второму входу i+1-м импульсом тактовой частоты (фиг.З, U4 .U.uJ). Линия 31 (32, 33) задержки

соединяющая второй выход триггера 25 с его входом установки в нуль, обеспечивает формирование не- с обходимой длительности импульсов с первого выхода триггера 25. Количество этих импульсов определяется длительностью импульсов разрешения, поступающих на первый вход триг0 гера 25 (фиг.З, U). Задний фронт этого импульса разрешения формируется с помощью ключа (элемента И) 28 передним фронтом импульса разрешения с выхода триггера 20 кана5 ла 14 преобразования (фиг.З, U, Uj). Задержка распространения фронта сигнала через триггер 20 канала 14 преобразования и ключ 28 канала 13 преобразования обеспечива0 ет надежное формирование последнего импульса (фиг.З, U4,U4) с выхода триггера 25. Импульсы с выхода триггера 25 поступают на вход установки в состояние О триггера 22

5 (23, 24). Сформированные на триггере 22 (23, 24) импульсы t , (utj fit j) (фиг.З, Uj.,U j. , U.j) поступают на вход преобразователя 34 (35, Зб) время-амплитуда. С выхода триггера

Q 25 импульсы поступают также на вход счетчика 37, на котором формируется код Б. Аналогично работают каналы 14 и 15 преобразования. На счетчике 38 формируется код В.

Длительность импульсов At,,utj, it . (фиг.З, и, ,U,j,Uy), формируемых на триггерах 22,23 и 24 соответственно трех каналов 13,14 и 15 преобразования, равна 1д + At, где 4tj изменяется от О до t. Амплитуда импульсов на выходе преобразователей 34, 35 и 36 время-амплитуда (фиг.З, J6iUg,Uj) пропорциональна длительностям At,, ut и ut 3 им пульсов с выхода триггеров соответственно 22, 23 и 24.Напряжения (амплитуда) UЬц,bUn, Up, Соответствующие длительностям импульсов it,, . последовательно во времени, с выходов, преобразователей 34, 35 и 36 время-амплитуда каналов 13, 14 и 15 преобразования поступают на входы преобразователя 39 амплитуда- код. Цифровые значения каждого из этих напряжений с выхода преобразователя 39 амплитуда-код представляют собой измеренные значения интервалов д t, , it и it,. Обозначим эти коды соответственно через N,К и

R. Тогда во время Р-го.измеритель- но го такта на счетчиках 37 и 38, а также на преобразователе 39 амплитуда-код формируются данные о контроле двух измерительных интервалов (фиг.З, ж,з) при заданном прораммируемом уровне. Причем величина первого измерительного интервала равна значению кодов Б+N-К, а величина второго измерительного интервала равна значению кодов В+К- R. Данные о двух измерительных интервалах по командам регистра 45 команд вычислительного и управляющего блока 2 переписываются в его запоминающее устройство . Эти данные представляют собой координаты двух точек измеряемого сигнала от- рюсительно Начала измерений на заданом пороговом уровне.

Для получения всех координат точек контролируемого сигнала необходимо от вычислительного и управляющего блока 2 в каждом из PJ - X тактов измерения изменить пороговый уровень на втором входе компаратора блока 6 и вьщать команду на измерение. Данные координат точек, характеризующие форму контролируемого сигнала в системе амплитудно-временных координат содержа необходимую информахщю для определения характеристик электрических сигналов. Пусть требуется вычислить длительность фронта контролируемого сигнала. Поскольку длительность фронта импульса измеряют .между уровнями от О,1 до 0,9 максимального значения его амплитуды, то нужно вначале по программе, реализующей методику определения амплитуды по ГОСТ, определить амплитуду (А) сигнала. Данные дця такого расчета содержатся в информации формы контролируемого сигнала, записанной в виде координат точек. Затем вычисляют значения напряжений, равные 0,9 А и О,1 А. Ставят в соответствие эти напряжения уровням квантования и с их временными интервалами от базовой точки отсчета до переднего фронта импульса (координаты точек формы сигнала) . Вычисляют разницу значений этих координат. Эта разница является длительностью фронта.

Работа устройства в других режимах, например при контроле длительности импульса, фронта или спа- J да, ничем не отличается от описанной. При контроле работоспособности устройства измерения характеристик электрических сигналов с заданной точностью на входы ком0 параторов блоков 5, 6 и 7 задают сигнал от блока эталонных сигналов. В запоминающем блоке 40 вычислительного и управляющего блока 2 хранятся данные о характеристиках эталон5 ных сигналов. Измеренные значения характеристик эталонных сигналов сравнивают с данными об эталонных сигналах, хранящихся в вычислительном и управляющем блоке 2. В случае

0 их несоответствия регистр 45 команд вычислительного и управляющего блока 2 дает команду на введение поправки к измерениям.

5 Формула изобретения

Устройство контроля характеристик электрических сигналов, содержащее генератор тактовых импульсов, пер0 вь1й ключ, первый и второй счетчики, преобразователь амплитуда-код, вычислительный и управлякяций блок, первьй, второй и третий блоки компараторов, первьй и второй мультиплексоры, первый и второй триггеры, три канала преобразования, каждый из которых содержит второй ключ и преобразователь время-амплитуда, причем выходы преобразоваQ телей время-амплитуда каждого канала преобразования соединены соответственно с первым, вторым и третьим входами преобразователя амплитуда-код, выход которого соединен с первым входом вычислительного и управляющего блока, первый выход которого соединен, соответственно с первыми входами первого, второго и третьего блоков компараторов, выход первого блока компараторов соединен с первыми входами первого и второго мультиплексоров, выход второго блока компараторов соединен с вторыми входами первого и второго мультиплексоров, выход третьего блока компараторов соединен с первым входом первого триггера, второй вход которого соединен с вторым выходом вычис

5

лительного и управляющего блока, третий выход которого соединен с третьим входом первого триггера, а четвертый выход - с третьими: входами первого и второго мультиплексоров, выход первого мультиплексора соединен с первьс входом второго триггера, второй вход которого соединен с выходом второго мультиплексора, с вторым входом вычислительного и управляющего блока, третий вход второго триггера соединен с вькодом первого триггера, третий и четвертый входы вычислительного и управляющего блока соединены соответственно с выходами первого и второго счетчиков, от-личающееся тем, что, с целью повышения достоверности контроля, в него введены блок формирования эталонных сигналов, делитель входного сигнала, в каждый канал преобразования введены линия задержки, третий, четвертый, пятый и шестой триггеры так, что пятый выход вычислительного и управляющего блока соединен с первыми входами третьих триггеров каждого из трех каналов преобразования, четвертый выход вычислительного и управляющего блока соединен с первыми входами первого ключа, делителя входных сигналов н блока формирования эталонных сигналов, выход которого соединен с вторым входом первого ключа, выход которого соединен с вторым входом делителя входного сигнала, выход которого соединен с вторыми входами первого, второго и третьего блоков компараторов, третий вход первого ключа соединен с клеммбй входного сигнала, выход второго триггера

0

0

соединен с вторым входом третьего триггера первого канала преобразова- ния и с щестым входом вычислительJ ного и управляющего блока, выход второго мультиплексора соединен с третьим входом третьего триггера первого канала преобразования, вторыми входами третьих триггеров второго и третьего каналов преобразования, выход первого триггера соединен с пятым входом вычислительного и управляющего блока,в каждом канале преобразования выход третьего

5 триггера соединен с первым входо - четвертого триггера, выход которого соединен с входом преобразователя время-амплитуда, первый выход пятого триггера соединен с вторым входом чет- вертого триггера, второй выход пятого триггера каждого канала преобразования через линию задержки соединен с первьм входом пятого триггера, первые выходы пятых триггеров первого и второго каналов преобразования соединены соответственно с входами первого и второго счетчиков, выход генератора тактовых импульсов соединен с вторым входом пятого триггера и с первым входом шестого триггера каждого канала преобразования, второй вход шестого триггера каждого канаша преобразования сое- - динен с выходом третьего триггера, а выход - с первым входом второго ключа, вторые входы вторых ключей первого и второго каналов преобразования соединены соответствен-, но с выходами шестых триггеров второго и третьего каналов преобразования, выход второго ключа соединен с третьим входом пятого триггера каждого канала преобразования.

5

0

5

I И II И

4//L

у / /

L/Z

L.

jr

/t J LJ 111 I I I I I I I I

L- I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля характе-РиСТиК элЕКТРичЕСКиХ СигНАлОВ | 1979 |

|

SU849114A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2646356C1 |

| Устройство для измерения среднеквадратического значения напряжения | 1989 |

|

SU1786443A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1990 |

|

SU1817031A2 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство приема информации с временным разделением каналов | 1987 |

|

SU1425750A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

Изобретение может быть использовано для измерения характеристик электрических сигналов в автоматике, вычислительной технике, приборостроении. Цель изобретения - повышение достоверности контроля характеристик. Устройство содержит блок I формирования эталонных сигналов вычислительный и управляющий блок 2, (Л

Авторы

Даты

1986-02-15—Публикация

1984-04-18—Подача