Изобретение относится к релейной защите и может быть использовано для защиты генераторов, синхронных компенсаторов, ошиновок, высоковольтных электродвигателей и сборных щин станций и подстанций.

Целью изобретения является повышение надежности функционирования уст ройства путем улучшения отстройки от переходных режимов.

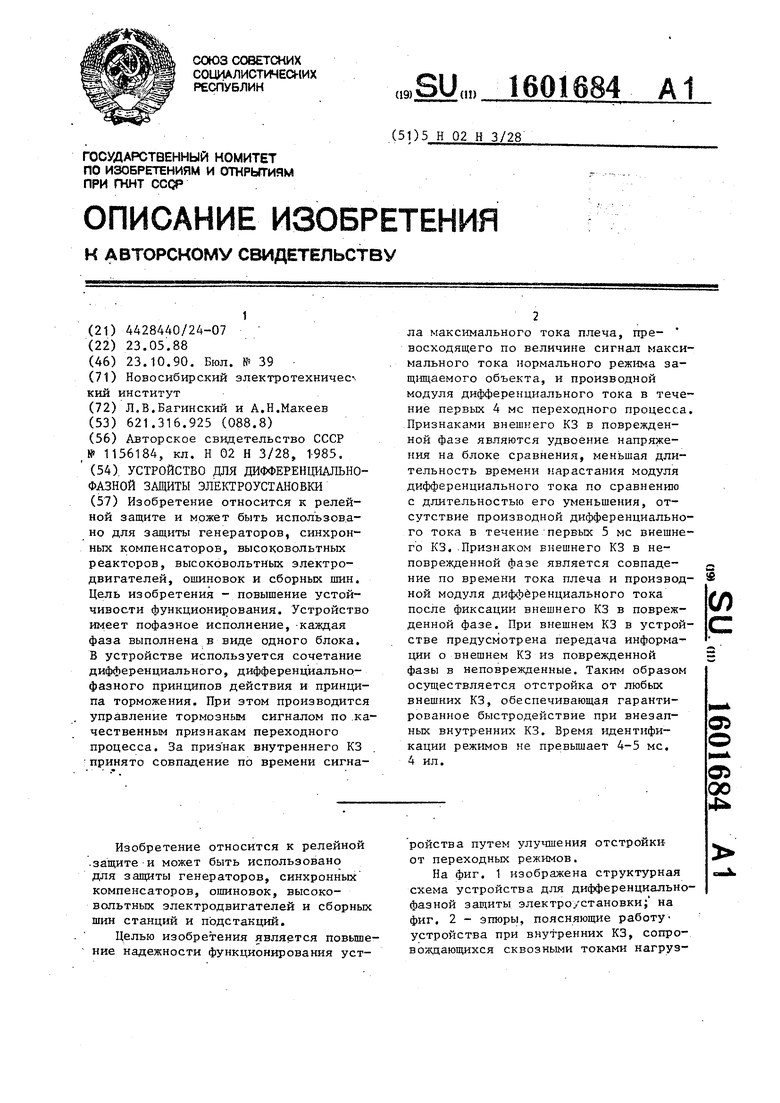

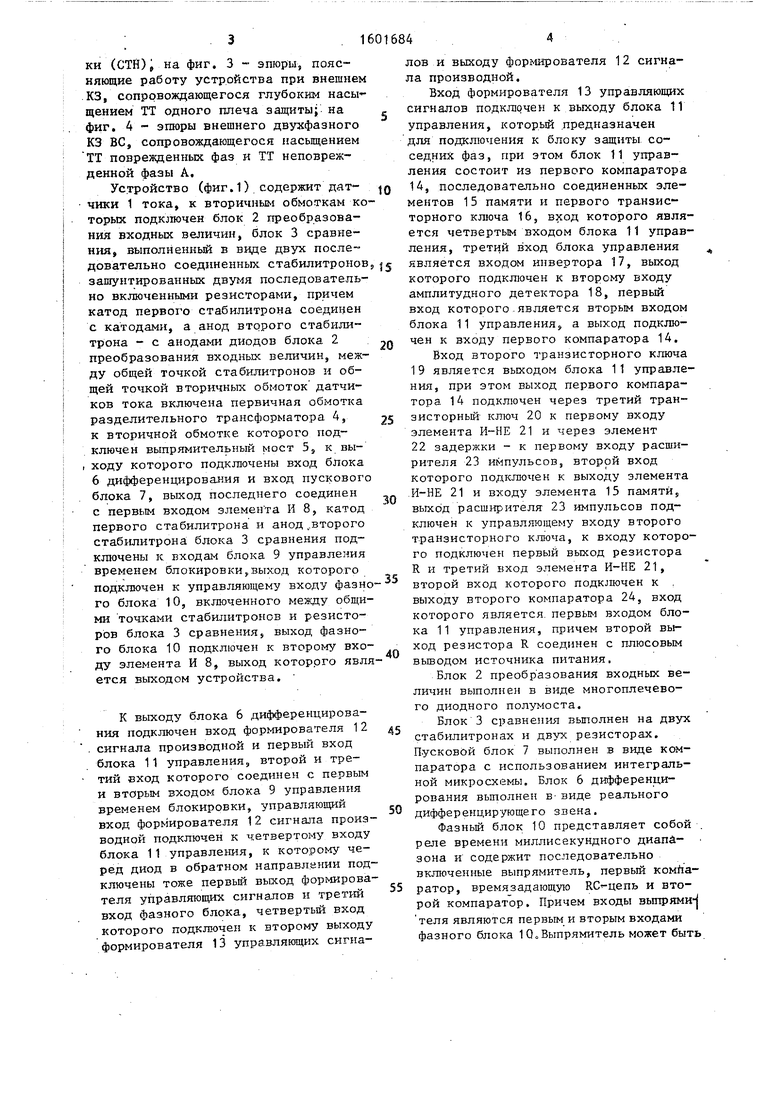

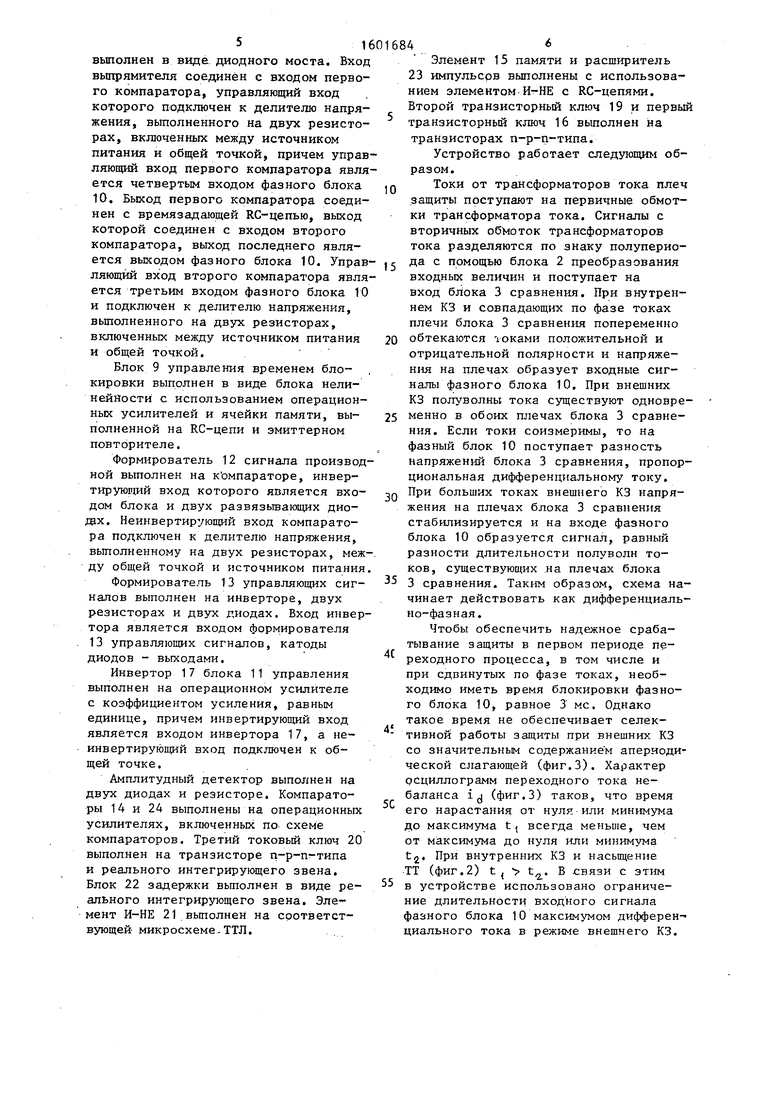

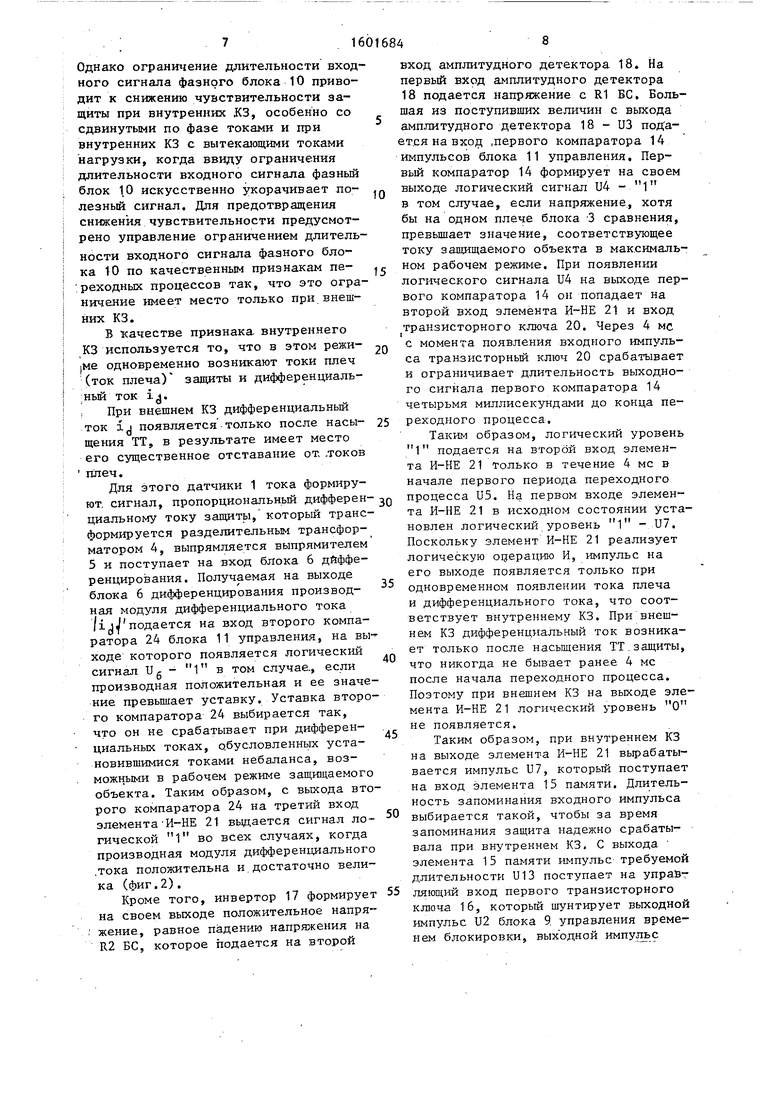

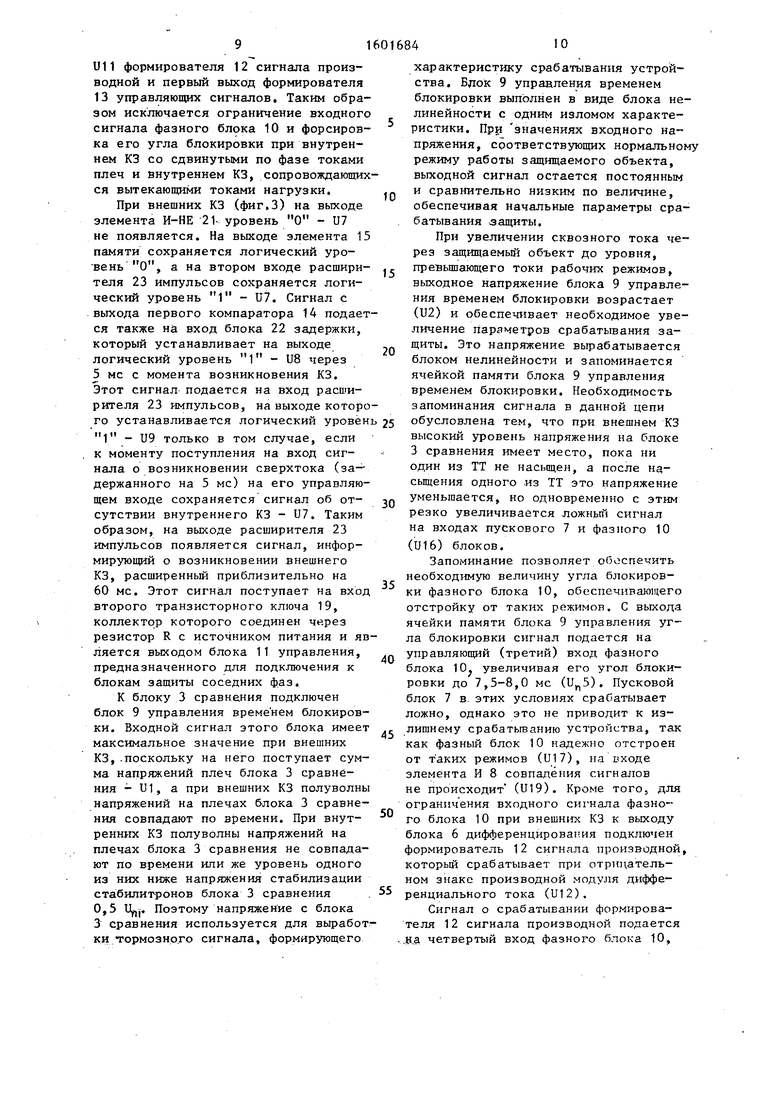

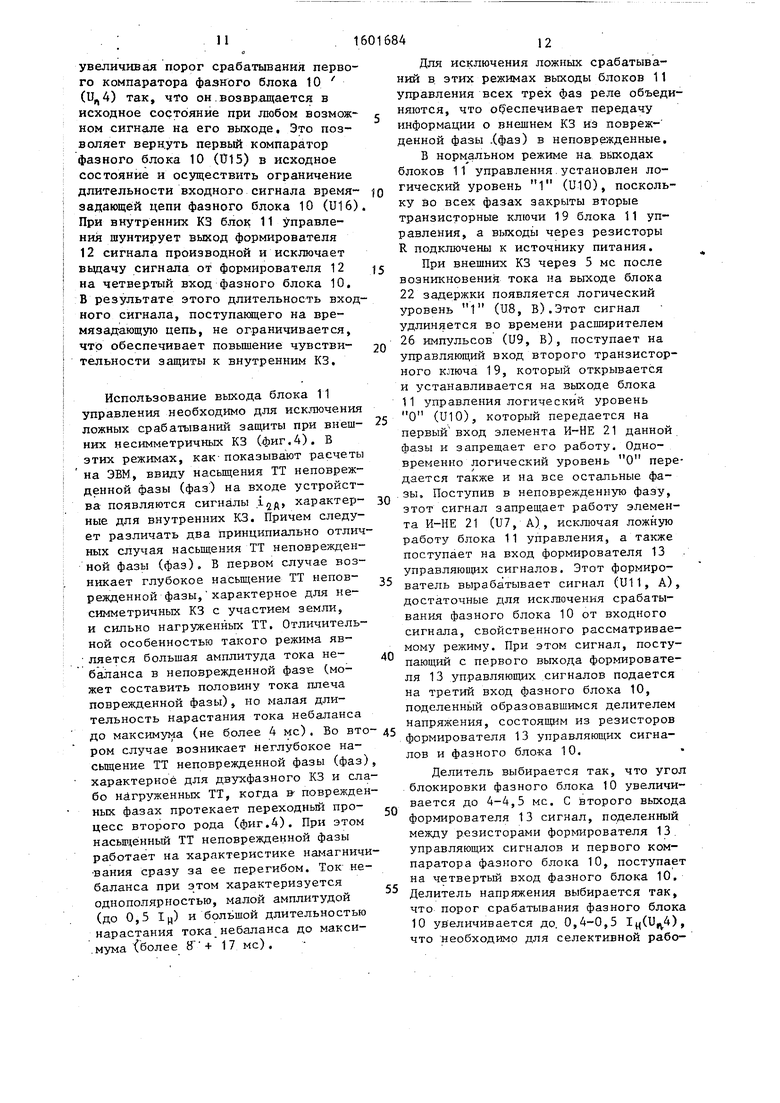

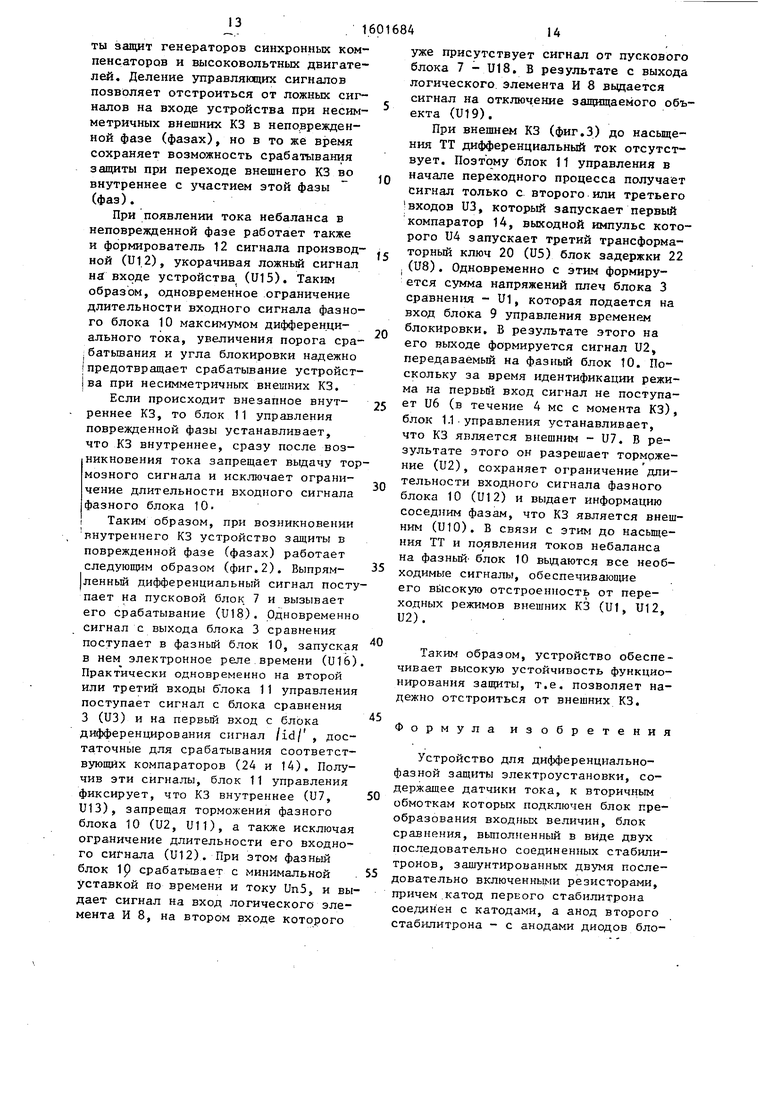

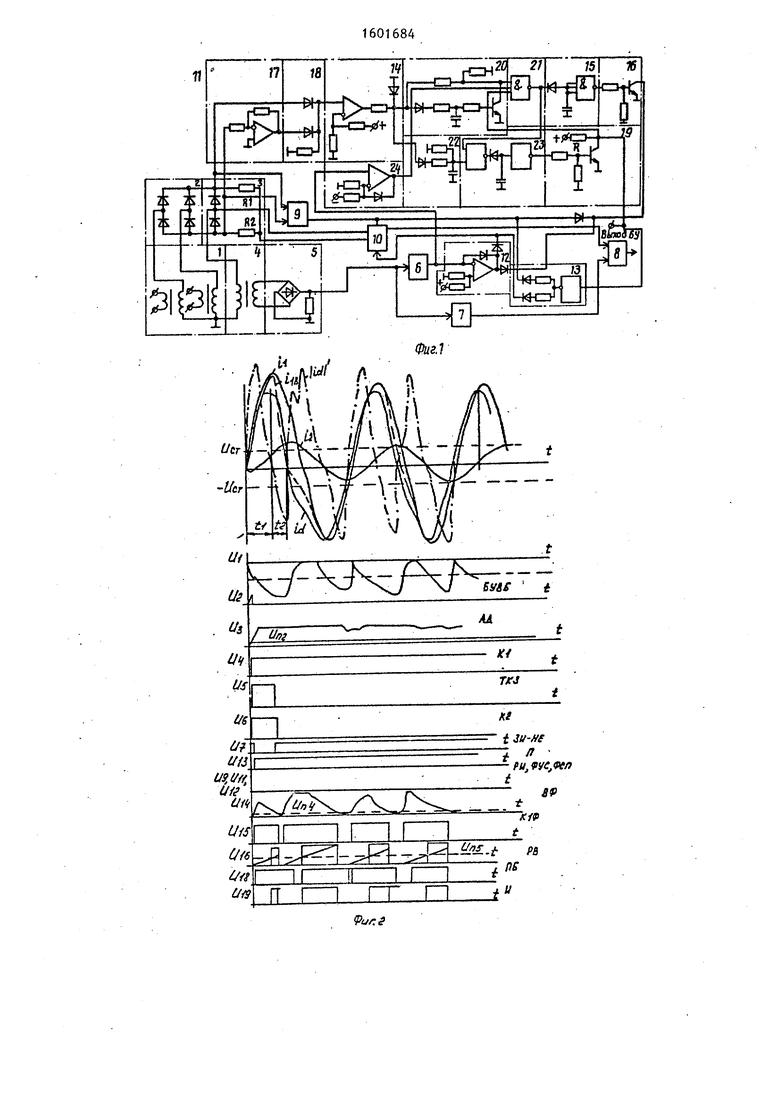

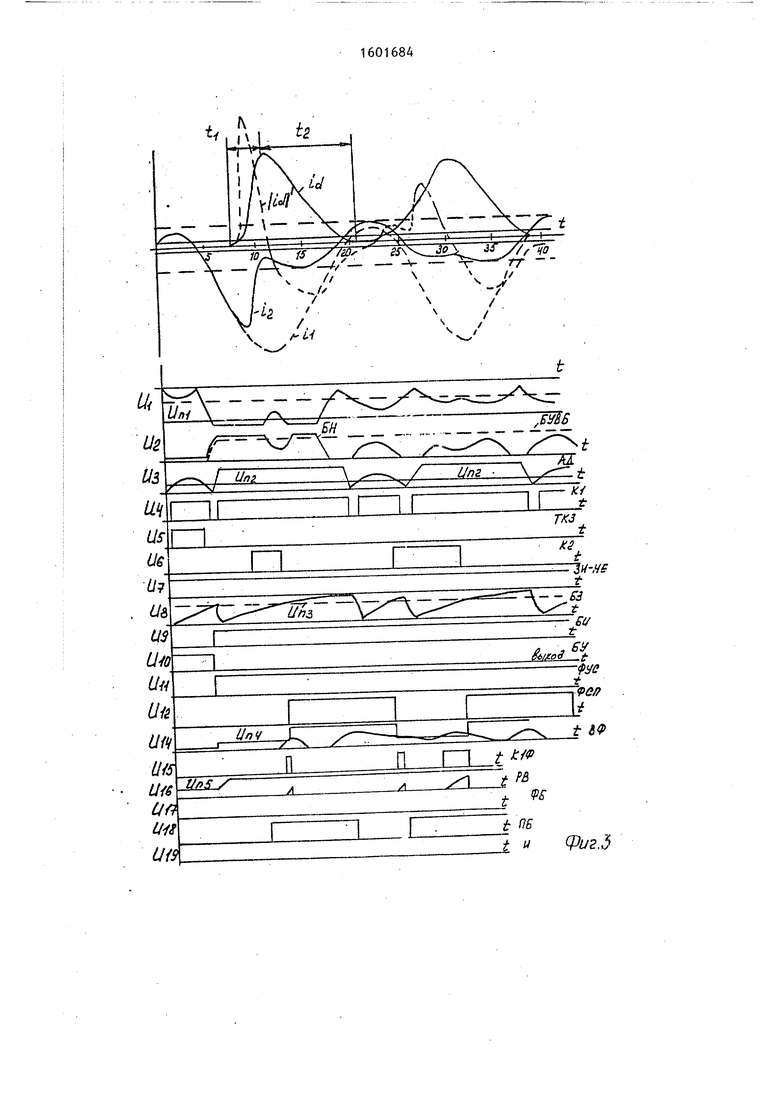

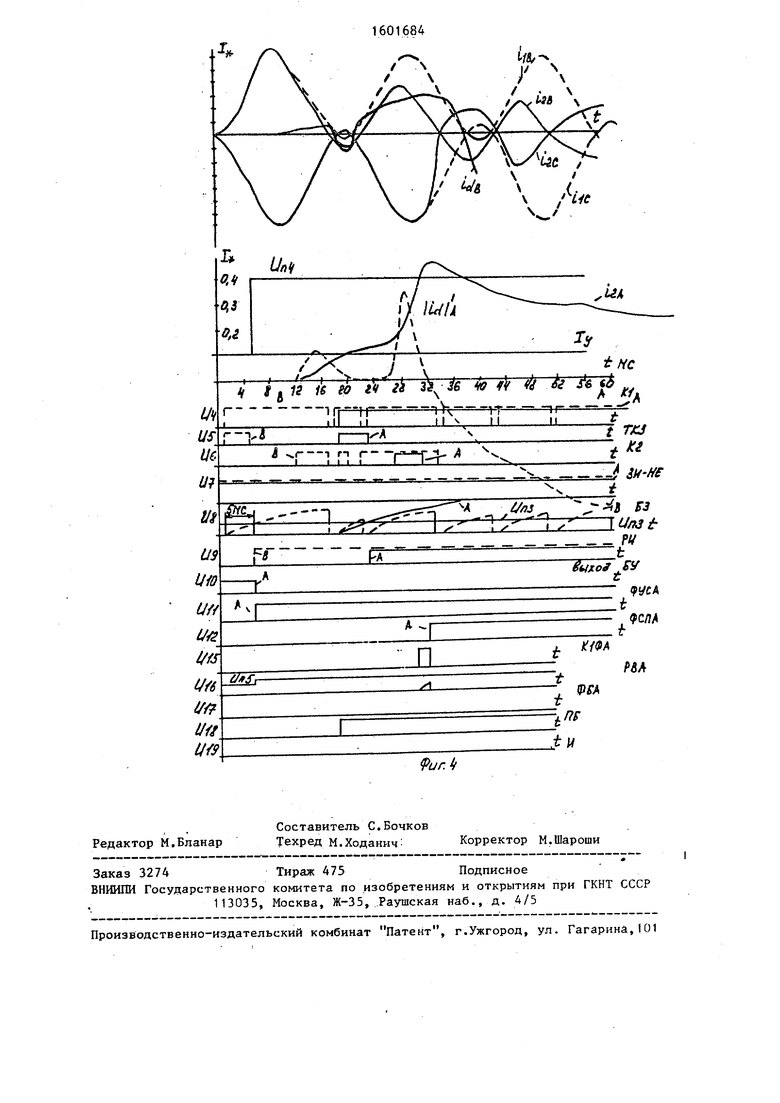

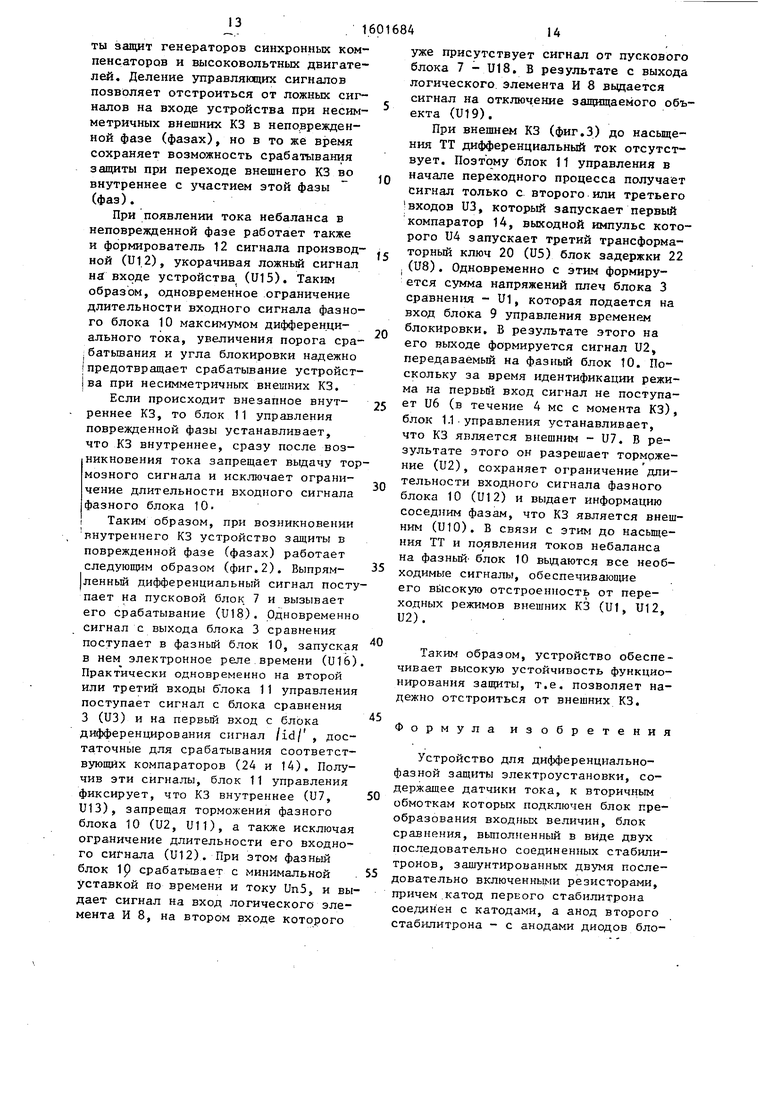

На фиг. 1 изображена структурная схема устройства для дифференциально- фазной защиты электроустановки; на фиг. 2 - эпюры, поясняющие работу- устройства при внутренних КЗ, сопровождающихся сквозными токами нагрузки (СТН); на фиг. 3 - эпюры, поясняющие работу устройства при внешнем КЗ, сопровождающегося глубоким насыщением ТТ одного плеча защиты; на фиг, 4 - эгаоры внешнего двухфазного КЗ ВС, сопровождающегося насыщением ТТ поврежденных фаз и ТТ неповрежденной фазы А.

Устройство (фиг.1).содержит дат- Q чики 1 тока, к вторичным обмоткам которых подключен блок 2 преобразования входных величин, блок 3 сравнения, выполненный в виде двух последовательно соединенных стабилитроновj jj зап1унтированных двумя последовательно включенными резисторами, причем катод первого стабилитрона соединен с катодами, а анод второго стабилитрона - с анодами диодов блока 2 JQ преобразования входных величин, между общей точкой стабилитронов и общей точкой вторичных обмоток датчиков тока включена первичная обмотка разделительного трансформатора 4, 25 к вторичной обмотке которого подключен выпрямительный мост 5, к вы- ходу которого подключены вход блока 6 дифференцирования и вход пускового блока 7, выход последнего соединен . с первым входом элемента И 8, катод первого стабилитрона и анод „второго стабилитрона блока 3 сравнения подключены к входам блока 9 управления временем блокировки,выход которого

подключен к управляющему входу фазно го блока 10, включенного между общими точками стабилитронов и резисторов блока 3 сравнения, выход фазного блока 10 подключен к второму входу элемента И 8, выход которого является выходом устройства.

,-35

40

К выходу блока 6 дифференцирования подключен вход формирователя 12 сигнала производной и первый вход блока 11 управления, второй и третий вход которого соединен с первым и вторым входом блока 9 управления временем блокировки, управляющий вход формирователя 12 сигнала производной подключен к четвертому входу блока 11 управления, к которому черед диод в обратном направлении подключены тоже первьй выход формирователя управляющих сигналов и третий вход фазного блока, четвертьш вход которого подключен к второму выходу формирователя 13 управляющих сигна

Q jj JQ 25 .

35

40

дз Q

55

лов и выходу формирователя 12 сигнала производной.

Вход формирователя 13 управляющих сигналов подкл10чен к выходу блока 11 управления, который лредназначен для подключения к блоку защиты соседних фаз, при этом блок 11 управления состоит из первого компаратора 14, последовательно соединенных элементов 15 памяти и первого транзисторного ключа 16, вход которого является четвертым входом блока 11 управления, третий вход блока управления является входом инвертора 17, выход которого подключен к второму входу амплитудного детектора 18, первый вход которого.является вторым входом блока 11 управления, а выход подключен к входу первого компаратора 14.

Вход второго транзисторного ключа 19 является выходом блока 11 управления, при этом выход первого компаратора 14 подключен через третий транзисторный ключ 20 к первому входу элемента И-НЕ 21 и через элемент 22 задержки - к первому входу расширителя 23 импульсов, второй вход которого подключен к выходу элемента .И-НЕ 21 и входу элемента 15 памяти, выход расширителя 23 импульсов подключен к управляющему входу второго транзисторного ключа, к входу которого подключен первый выход резистора R и третий вход элемента И-НЕ 21, второй вход которого подключен к , выходу второго компаратора 24, вход которого является, первым входом блока 11 управления, причем второй выход резистора R соединен с плюсовым вьшодом источника питания.

Блок 2 преобразования входных величин выполнен в виде многоплечевого диодного полумоста.

Блок 3 сравнения выполнен на двух стабилитронах и двух резисторах. Пусковой блок 7 выполнен в виде компаратора с использованием интегральной микросхемы. Блок 6 дифференцирования выполнен в- виде реального дифференцирующего з.вена.

Фазньй блок 10 представляет собой . реле времени миллисекундного диапй- зона и содержит последовательно включенные выпрямитель, первый комйа- ратор, времязадающую RC-цепь и второй компаратор. Причем входы выпрями-j теля являются первым и вторым входами фазного блока 1 О Выпрямитель может быть.

51601684

выполнен в виде, диодного моста. Вход вьтрямителя соединён с входом первого компаратора, управляющий вход которого подключен к делителю напряжения, вьтолненного на двух резисторах, включенных между источником питания и общей точкой, причем управляющий вход первого компаратора является четвертым входом фазного блока 10. Выход первого компаратора соединен с времязадающей RC-цепью, выход которой соединен с входом второго компаратора, выход последнего явля

Элемент 15 памяти и расширитель 23 импульсов выполнены с использованием элементом И-НЕ с RC-цепями, Второй транзисторньй ключ 19 и первый транзисторный ключ 16 вьшолнен на транзисторах п-р-п-типа.

Устройство работает следующим образом.

Токи от трансформаторов тока плеч защиты поступают на первичные обмотки трансформатора тока. Сигналы с вторичных обмоток трансформаторов тока разделяются по знаку полуперио

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференциально-фазной защиты электроустановки | 1987 |

|

SU1677762A1 |

| Устройство для дифференциально-фазной защиты электроустановки | 1984 |

|

SU1156184A1 |

| Устройство для дифференциальной защиты электроустановки | 1983 |

|

SU1141498A1 |

| Устройство для защиты сборных шин электростанции и подстанции | 1981 |

|

SU945937A1 |

| Блок управления для устройства дифференциально-фазной защиты электроустановки | 1989 |

|

SU1677763A2 |

| Блок управления для устройства дифференциально-фазной защиты электроустановки | 1986 |

|

SU1427465A1 |

| Устройство для дифференциальной защиты трансформатора | 1984 |

|

SU1272390A1 |

| Устройство дифференциальной защиты трансформаторов | 2024 |

|

RU2829990C1 |

| Устройство для дифференциальной защиты электроустановки | 1985 |

|

SU1259388A2 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

Изобретение относится к релейной защите и может быть использовано для защиты генераторов, синхронных компенсаторов, высоковольтных реакторов, высоковольтных электродвигателей, ошиновок и сборных шин. Цель изобретения - повышение устойчивости функционирования. Устройство имеет пофазное исполнение, каждая фаза выполнена в виде одного блока. В устройстве используется сочетание дифференциального, дифференциально-фазного принципов действия и принципа торможения. При этом производится управление тормозным сигналом по качественным признакам переходного процесса. За признак внутреннего КЗ принято совпадение по времени сигнала максимального тока плеча, превосходящего по величине сигнал максимального тока нормального режима защищаемого объекта, и производной модуля дифференциального тока в течении первых 4 мс переходного процесса. Признаками внешнего КЗ в поврежденной фазе являются удвоение напряжения на блоке сравнения, меньшая длительность времени нарастания модуля дифференциального тока по сравнению с длительностью его уменьшения, отсутствие производной дифференциального тока в течение первых 5 мс внешнего КЗ. Признаком внешнего КЗ в неповрежденной фазе является совпадение по времени тока плеча и производной модуля дифференциального тока после фиксации внешнего КЗ в поврежденной фазе. При внешнем КЗ в устройстве предусмотрена передача информации о внешнем КЗ из поврежденной фазы в неповрежденные. Таким образом, осуществляется отстройка от любых внешних КЗ, обеспечивающая гарантированное быстродействие при внезапных внутренних КЗ. Время идентификации режимов не превышает 4-5 мс. 4 ил.

ется выходом фазного блока 10. Управ- jr да с помощью блока 2 преобразования

30

ляющии вход второго компаратора является третьим входом фазного блока 10 и подключен к делителю напряжения, вьшолненного на двух резисторах, включенных между источником питания 20 и общей точкой.

Блок 9 управления временем блокировки выполнен в виде блока нелинейности с использованием операционных усилителей и ячейки памяти, вы- 25 полненной на RC-цепи и эмиттерном повторителе.

Формирователь 12 сигнала производной выполнен на к омпараторе, инвер- тируюр1ий вход которого является входом блока и двух развязьшающих диодах. Неинвертирующий вход компаратора подключен к делителю напряжения, вьтолненному на двух резисторах, меж-, ду общей точкой и источником питания. Формирователь 13 управляющих сигналов выполнен на инверторе, двух резисторах и двух диодах. Вход инвертора является входом формирователя . 13 управляющих сигналов, катоды диодов - выходами.

Инвертор 17 блока 11 управления выполнен на операционном усилителе с коэффициентом усиления, равным единице, причем инвертируюгций вход является входом инвертора 17, а не- инвертирующий вход подключен к общей точке.

Амплитудный детектор выполнен на двух диодах и резисторе. Компараторы 14 и 24 выполнены на операционных усилителях, включенных по схеме компараторов. Третий токовый ключ 20 выполнен на транзисторе п-р-п-типа и реального интегрирующего звена. Блок 22 задержки выполнен в виде ре- 55 ального интегрирующего звена. Элемент И-НЕ 21 выполнен на соответствующей микросхеме,ТТЛ.

35

4С

4f

5С

входных величин и поступает на вход блока 3 сравнения. При внутреннем КЗ и совпадающих по фазе токах плечи блока 3 сравнения попеременно обтекаются 1оками положительной и отрицательной полярности и напряжения на плечах образует входные сигналы фазного блока 10. При внешних КЗ полуволны тока существуют одновре менно в обоих плечах блока 3 сравнения. Если токи соизмеримы, то на фазный блок 10 поступает разность напряжений блока 3 сравнения, пропор циональная дифференциальному току. При больших токах внешнего КЗ напряжения на плечах блока 3 сравнения стабилизируется и на входе фазного блока 10 образуется сигнал, равный разности длительности полуволн токов, существующих на плечах блока 3 сравнения. TaKJiM образом, схема на чинает действовать как дифференциаль но-фазная.

Чтобы обеспечить надежное срабатывание защиты в первом периоде переходного процесса, в том числе и при сдвинутых по фазе токах, необходимо иметь время блокировки фазного блока 10, равное 3 мс. Однако такое время не обеспечивает селективной работы защиты при внешних КЗ со значительным содержанием апериодической слагающей (фиг.З). Характер осциллограмм переходного тока небаланса ij (фиг.З) таков, что время его нарастания от нуля или минимума до максимума t всегда меньше, чем от максимума до нуля или минимума tj. При внутренних КЗ и насыщение

.ТТ (фиг.2) t

t. В связи с этим

в устройстве использовано ограничение длительности входного сигнала фазного блока 10 максимумом дифференциального тока в режиме внешнего КЗ.

0

0

5

5

5

С

f

С

входных величин и поступает на вход блока 3 сравнения. При внутреннем КЗ и совпадающих по фазе токах плечи блока 3 сравнения попеременно обтекаются 1оками положительной и отрицательной полярности и напряжения на плечах образует входные сигналы фазного блока 10. При внешних КЗ полуволны тока существуют одновременно в обоих плечах блока 3 сравнения. Если токи соизмеримы, то на фазный блок 10 поступает разность напряжений блока 3 сравнения, пропорциональная дифференциальному току. При больших токах внешнего КЗ напряжения на плечах блока 3 сравнения стабилизируется и на входе фазного блока 10 образуется сигнал, равный разности длительности полуволн токов, существующих на плечах блока 3 сравнения. TaKJiM образом, схема начинает действовать как дифференциально-фазная.

Чтобы обеспечить надежное срабатывание защиты в первом периоде переходного процесса, в том числе и при сдвинутых по фазе токах, необходимо иметь время блокировки фазного блока 10, равное 3 мс. Однако такое время не обеспечивает селективной работы защиты при внешних КЗ со значительным содержанием апериодической слагающей (фиг.З). Характер осциллограмм переходного тока небаланса ij (фиг.З) таков, что время его нарастания от нуля или минимума до максимума t всегда меньше, чем от максимума до нуля или минимума tj. При внутренних КЗ и насыщение

.ТТ (фиг.2) t

t. В связи с этим

в устройстве использовано ограничение длительности входного сигнала фазного блока 10 максимумом дифференциального тока в режиме внешнего КЗ.

;7. 160

Однако огран№1ение длительности входного сигнала фазного блока 10 приводит к снижению чувствительности защиты при внутренних ДЗ, особенно со сдвинутыми по фазе токами и при внутренних КЗ с вытекающими токами нагрузки, когда ввиду ограничения длительности входного сигнала фазный блок 10 искусственно укорачивает по- лезньй сигнал. Для предотвращения снижения чувствительности предусмотрено управление ограничением длительности входного сигнала фазного блока 10 по качественным признакам па- реходных процессов так, что это ограничение имеет место только при.внешних КЗ.

В качестве признака внутреннего

КЗ используется то, что в этом режи- |ме одновременно возникают токи плеч

(ток плеча) защиты и дифферендиальньй ток ij.

; При внешнем КЗ дифференциальньй ток ij появляется только после насы- щения ТТ, в результате имеет место его существенное отставание от .токов

плеч.

Для этого датчики 1 тока формируют сигнал, пропорциональный дифферен- циальному току защиты, который трансформируется разделительным трансформатором 4, выпрямляется выпрямителем 5 и поступает на вход блока 6 дифференцирования. Получаемая на выходе блока 6 дифференцирования производ ная модуля дифференциального тока |iiJ подается на вход второго компаратора 24 блока 11 управления, на выходе которого появляется логический сигнал Ug - 1 в том случае., если производная положительная и ее значение превьшает уставку. Уставка второго компаратора 24 выбирается так,

что он не срабатывает при дифферен-

циальных токах, обусловленных установившимися токами небаланса, возможными в рабочем режиме заш,ищаемого объекта. Таким образом, с выхода второго компаратора 24 на третий вход элемента И-НЕ 21 вьщается сигнал логической 1 во всех случаях, когда производная модуля дифференциального .тока полозкительна и. достаточно велика (фиг.2).

Кроме того, инвертор 17 формируе на своем выходе положительное напря ; жение, равное падению напряжения на R2 БС, которое подается на второй

Q

5

Q

,

ээ

5

8

вход амплитудного детектора 18. На первый вход амплитудного детектора 18 подается напряжение с R1 БС. Большая из поступивших величин с выхода амплитудного детектора 18 - U3 подается на вход .первого компаратора 14 импульсов блока 11 управления. Первый компаратор 14 формирует на своем выходе логический сигнал U4 - 1 в том случае, если напряжение, хотя бы на одном плече блока -3 сравнения, превьш1ает значение, соответствующее току защищаемого объекта в максимальном рабочем режиме. При появлении логического сигнала U4 на выходе первого компаратора 14 он попадает на второй вход элемента И-НЕ 21 и вход транзисторного ключа 20, Через 4 мс с момента появления входного импульса транзисторный ключ 20 срабатывает и ограничивает длительность выходного сигнала первого компаратора 14 четырьмя миллисекундами до конца переходного процесса.

Таким образом, логический уровень 1 подается на второй вход элемента И-НЕ 21 только в течение 4 мс в начале первого периода переходного процесса U5. На первом входе элемента И-НЕ 21 в исходном состоянии установлен логический уровень 1 - 1)7. Поскольку элемент И-НЕ 21 реализует логическую операцию И, импульс на его выходе появляется только при одновременном появлении тока плеча и дифференциального тока, что соответствует внутреннему КЗ. При внешнем КЗ дифференциальный ток возникает только после насыщения ТТ.защиты, что никогда не бывает ранее 4 мс после начала переходного процесса. Поэтому при внешнем КЗ на выходе элемента И-НЕ 21 логический уровень О не появляется.

Таким образом, при внутреннем КЗ на выходе элемента И-НЕ 21 вырабатывается импульс U7, который поступает на вход элемента 15 памяти. Длительность запоминания входного импульса выбирается такой, чтобы эа время запоминания защита надежно срабатывала при внутреннем КЗ. С выхода элемента 15 памяти импульс требуемой длительности U13 поступает на управляющий вход первого транзисторного ключа 16, которьй шунтирует выходной импульс U2 блока 9. управления временем блокировки, вых одной импульс

9

U11 формирователя 12 сигнала производной и первый выход формирователя 13 управляющих сигналов. Таким образом исключается ограничение входног сигнала фазного блока 10 и форсиров ка его угла блокировки при внутреннем КЗ со сдвинутьми по фазе токами плеч и внутреннем КЗ, сопровождающися вытекающими токами нагрузки.

При внешних КЗ (фиг.З) на выходе элемента И-НЕ 21- уровень О - U7 не появляется. На выходе элемента 1 памяти сохраняется логический уро- вень О, а на втором входе расширителя 23 импульсов сохраняется логический уровень 1 - U7. Сигнал с выхода первого компаратора 14 подаеся также на вход блока 22 задержки, который устанавливает на выходе логический уровень 1 - U8 через 5 мс с момента возникновения КЗ. Этот сигнал подается на вход расширителя 23 импульсов, на выходе которго устанавливается логический урове 1 - U9 только в том случае, если к моменту поступления на вход сигнала о возникновении сверхтока (задержанного на 5 мс) на его управляющем входе сохраняется сигнал об отсутствии внутреннего КЗ - U7. Таким образом, на выходе расширителя 23 импульсов появляется сигнал, информирующий о возникновении внешнего КЗ, расширенный приблизительно на 60 мс. Этот сигнал поступает на вхо второго транзисторного ключа 19, коллектор которого соединен через резистор R с источником питания и яляется выходом блока 11 управления, предназначенного для подключения к блокам защиты соседних фаз.

К блоку 3 сравнения подключен блок 9 управления временем блокировки. Входной сигнал этого блока имее максимальное значение при внешних КЗ,.поскольку на него поступает сумма напряжений плеч блока 3 сравнения - U1, а при внешних КЗ полуволн напряжений на плечах блока 3 сравнения совпадают по времени. При внутренних КЗ полуволны напряжений на плечах блока 3 сравнения не совпадают по времени или же уровень одного из них ниже напряжения стабилизации стабилитронов блока 3 сравнения 0,5 . Поэтому напряжение с блока 3 сравнения используется для вырабоки тормозного сигнала, формирующего

10

15

20

1684

5

0

5

0

5

0

5

10

характеристику срабатывания устройства. БЛОК 9 управления временем блокировки выполнен в виде блока нелинейности с одним изломом характеристики. При значениях входного напряжения, соответствующих нормальному режиму работы защищаемого объекта, выходной сигнал остается постоянным и сравнительно низким по величине, обеспечивая начальные параметры срабатывания защиты.

При увеличении сквозного тока через защищаемый объект до уровня, превьшающего токи рабочих режимов, выходное напряжение блока 9 управления временем блокировки возрастает (U2) и обеспечивает необходимое увеличение параметров срабатывания защиты. Это напряжение вырабатывается блоком нелинейности и запоминается ячейкой памяти блока 9 управления временем блокировки. Необходимость запоминания сигнала в данной цепи обусловлена тем, что при внешнем КЗ высокий уровень напряжения на блоке 3 сравнения имеет место, пока ни один из ТТ не насьпцен, а после насыщения одного из ТТ это напряжение уменьшается, но одновременно с этим резко увеличивается ложньм сигнал на входах пускового 7 и фазного 10 (U16) блоков.

Запоминание позволяет обоспечить необходимую величину угла блокировки фазного блока 10, обе;спечивающего отстройку от таких режимов. С выхода ячейки памяти блока 9 управления угла блокировки сигнал подается на управляющий (третий) вход фазного блока 10 увеличивая его угол блокировки до 7,5-8,0 мс (). Пусковой блок 7 в. этих условиях срабатывает ложно, однако это не приводит к излишнему срабатьгоанию устройства, так как фазный блок 10 надежно отстроен от таких режимов (U17), на входе элемента И 8 совпадения сигналов не происходит (U19). Кроме того, для ограничения входного сигнала фазного блока 10 при внешних КЗ к выходу блока 6 дифференцирования подключен формирователь 12 сигнала производной, который срабатывает при отр1П1атель- ном знаке производной модуля дифференциального тока (U12).

Сигнал о срабатывании формирователя 12 сигнала производной подается жа четвертый вход фазного блока 10,

увеличивая порог срабатывания первого компаратора фазного блока 10 () так, что он.возвращается в исходное состояние при любом возможном сигнале на его выходе, Это позволяет вернуть первый компаратор фазного блока 10 (tJ15) в исходное состояние и осуществить ограничение длительности входного сигнала время- задающёй цепи фазного блока 10 (U16) При внутренних КЗ блок 11 управления шунтирует выход формирователя 12 сигнала производной и исклочает вьщачу сигнала от формирователя 12 на четвертый вход фазного блока 10, В результате этого длительность входного сигнала, поступающего на вре- мязадающую цепь, не ограничивается, что обеспечивает повьшение чувствительности защиты к внутренним КЗ,

,- 25

Использование выхода блока 11 управления необходимо для исключения ложных срабатываний защиты при внеш них несимметричных КЗ (Лиг.4), В этих режимах, как-показывают расчеты на ЭВМ, ввиду насьщения ТТ неповрежденной фазы (фаз) на входе устройства появляются сигналы , характерные для внутренних КЗ, Причем следует различать два принципиально отличных случая насыщения ТТ неповрежденной фазы (фаз). В первом случае возникает глубокое насьщение ТТ неповрежденной фазы, характерное для несимметричных КЗ с участием земли, и сильно нагруженных ТТ. Отличительной особенностью такого режима яв- ляется большая амплитуда тока не- баланса в неповрежденной фазе Сможет составить половину тока плеча поврежденной фазы), но малая длительность нарастания тока небаланса

При внешних КЗ через 5 мс после возникновения тока на выходе блока 22 задержки появляется логический уровень 1 (U8, В).Этот сигнал удлиняется во времени расширителем 26 импульсов (U9, В), поступает на управляющий вход второго транзисторного ключа 19, который открывается и устанавливается на выходе блока 11 управления логический уровень О (U10), который передается на первый вход элемента И-НЕ 21 данной фазы и запрещает его работу. Одновременно логический уровень О пере дается также и на все остальные фа- .зы. Поступив в неповрежденную фазу, этот сигнал запрещает работу элемента И-НЕ 21 (U7, А), исключая ложную работу блока 11 управления, а также поступает на вход формирователя 13 управляющих сигналов. Этот формиро- 35 ватель вырабатывает сигнал (U11, А) достаточные для исключения срабатывания фазного блока 10 от входного сигнала, свойственного рассматриваемому режиму. При этом сигнал, посту пающий с первого выхода формировате ля 13 управляющих сигналов подается на третий вход фазного блока 10, поделенный образовавшимся делителем

30

40

, -, -напряжения, состояш;им из резисторов

до максимума (не более 4 мс). Во вто- 45

ром случае возникает неглубокое на- сьш1ение ТТ неповрежденной фазы (фаз), характерное для двухфазного КЗ и слабо нагруженных ТТ, когда в- поврежденных фазах протекает переходный процесс второго рода (фиг.4). При этом насьщенный ТТ неповрежденной фазы работает на характеристике намагничи- вания сразу за ее перегибом. Ток небаланса при характеризуется однополярностью, малой амплитудой (до 0,5 1ц) и большой длительностью нарастания тока.небаланса до макси- .мума (более S + 1 7 мс) .

50

55

формирователя 13 управляющих сигналов и фазного блока 10.

Делитель выбирается так, что уго блокировки фазного блока 10 увеличи вается до 4-4,5 мс. С jBToporo выход формирователя 13 сигнал, поделенный между резисторами формирователя 13. управляющих сигналов и первого компаратора фазного блока 10, поступае на четвертый вход фазного блока 10, Делитель напряжения выбирается так, что порог срабатывания фазного блок 10 увеличивается до. 0,4-0,5 I(U,y4) что необходимо для селективной рабо

. 10

15

20

25

Для исключения ложных срабатываний в. этих режимах выходы блоков 11 управления всех трех фаз реле объединяются, что обеспечивает передачу информации о внешнем КЗ из повреж- денной фазы .(фаз) в неповрежденные,

В нормальном режиме на выходах блоков 11 управления.установлен логический уровень 1 (U10), поскольку во всех фазах закрыты вторые транзисторные ключи 19 блока 11 управления, а выходы через резисторы R подключены к источнику питания.

При внешних КЗ через 5 мс после возникновения тока на выходе блока 22 задержки появляется логический уровень 1 (U8, В).Этот сигнал удлиняется во времени расширителем 26 импульсов (U9, В), поступает на управляющий вход второго транзисторного ключа 19, который открывается и устанавливается на выходе блока 11 управления логический уровень О (U10), который передается на первый вход элемента И-НЕ 21 данной фазы и запрещает его работу. Одновременно логический уровень О передается также и на все остальные фа- .зы. Поступив в неповрежденную фазу, этот сигнал запрещает работу элемента И-НЕ 21 (U7, А), исключая ложную работу блока 11 управления, а также поступает на вход формирователя 13 управляющих сигналов. Этот формиро- 35 ватель вырабатывает сигнал (U11, А), достаточные для исключения срабатывания фазного блока 10 от входного сигнала, свойственного рассматриваемому режиму. При этом сигнал, поступающий с первого выхода формирователя 13 управляющих сигналов подается на третий вход фазного блока 10, поделенный образовавшимся делителем

30

40

напряжения, состояш;им из резисторов

формирователя 13 управляющих сигналов и фазного блока 10.

Делитель выбирается так, что угол блокировки фазного блока 10 увеличивается до 4-4,5 мс. С jBToporo выхода формирователя 13 сигнал, поделенный между резисторами формирователя 13. управляющих сигналов и первого компаратора фазного блока 10, поступает на четвертый вход фазного блока 10, Делитель напряжения выбирается так, что порог срабатывания фазного блока 10 увеличивается до. 0,4-0,5 I(U,y4), что необходимо для селективной работы защит генераторов синхронных компенсаторов и высоковольтных двигателей. Деление управляющих сигналов позволяет отстроиться от ложных сигналов на входе устройства при несимметричных внешних КЗ в неповрежденной фазе (фазах), но в то же время сохраняет возможность срабатывания защиты при переходе внешнего КЗ во внутреннее с участием этой фазы (фаз).

При появлении тока небаланса в неповрежденной фазе работает также и формирователь 12 сигнала производной (U12), укорачивая ложный сигнал на входе устройства (U15). Таким образом, одновременное ограничение длительности входного сигнала фазного блока 10 максимумом дифференциального тока, увеличения порога сра- .батьшания и угла блокировки надежно I предотвращает срабатывание устройст- Iва при несимметричных внешних КЗ.

Если происходит внезапное внутреннее КЗ, то блок 11 управления поврежденной фазы устанавливает, что КЗ внутреннее, сразу после возникновения тока запрещает выдачу тормозного сигнала и исключает ограничение длительности входного сигнала фазного блока 10.

Таким образом, при возникновении внутреннего КЗ устройство защиты в поврежденной фазе (фазах) работает следующим образом (фиг.2). Выпрямленный дифференциальный сигнал поступает на пусковой блок. 7 и вызывает его срабатывание (U18). Одновременно сигнал с выхода блока 3 сравнения поступает в фазный блок 10, запуская в нем злектронное реле времени (U16). Практически одновременно на второй или третий входы блока 11 управления поступает сигнал с блока сравнения 3 (из) и на первый вход с блока дифференцирования сигнал /id/ , достаточные для срабатывания соответствующих компараторов (24 и 14). Получив эти сигналы, блок 11 управления фиксирует, что КЗ внутреннее (U7, U13), запрещая торможения фазного блока 10 (U2, U11), а также исключая ограничение длительности его входного сигнала (U12). При этом фазный блок 1р срабатьшает с минимальной уставкой по времени и току Un5, и выдает сигнал на вход логического элемента И 8, на втором входе которого

10

Т5

20

25

30

5

0

5

0

уже присутствует сигнал от пускового блока 7 - U18. В результате с выхода логического, элемента И 8 выдается сигнал на отключение защищаемого объекта (U19).

При внешнем КЗ (фиг.З) до насыщения ТТ дифференциальный ток отсутствует. Поэтому блок 11 управления в начале переходного процесса получает сигнал только с второго или третьего Iвходов из, который запускает первый компаратор 14, выходной импульс которого U4 запускает третий трансформаторный ключ 20 (U5) блок задержки 22 I(U8). Одновременно с этим формируется сумма напряжений плеч блока 3 сравнения - U1, которая подается на вход блока 9 управления временем блокировки. В результате этого на его выходе формируется сигнал U2, передаваемый на фазный блок 10. Поскольку за время идентификации режима на первый вход сигнал не поступает U6 (в течение 4 мс с момента КЗ), блок 1.1 .управления устанавливает, что КЗ является внешним - U7. В результате этого он разрешает торможение (U2), сохраняет ограничение длительности входного сигнала фазного блока 10 (и12) и выдает информацию сосед1гим фазам, что КЗ является внешним (U10). В связи с этим до насьпце- ния ТТ и появления токов небаланса на фазный- блок 10 выдаются все необходимые сигналы, обеспечиваюпще его высокую отстроенность от переходных режимов внешних КЗ (U1, U12

Таким образом, устройство обеспечивает высокую устойчивость функционирования защиты, т.е. позволяет надежно отстроиться от внешних КЗ.

Формула изобретения

Устройство для дифференциально- фазной защиты электроустановки, содержащее датчики тока, к вторичным обмоткам которых подключен блок преобразования входных величин, блок сравнения, вьшолленный в вИде двух последовательно соединенных стабилитронов, зашунтированньгх двумя последовательно включеннь1ми резисторами, причем катод первого стабилитрона соединен с катодами, а анод второго стабилитрона - с анодами диодов бло

,5160

ка преобразования входных величин, между общей точкой стабилитронов и общей точкой вторичных обмоток датчиков ока включена первичная обмотка разделительного трансформатора, к вторичной обмотке которого подклю- чен выпрямительный мост, к выходу которого подключены вход блока дифференцирования и .вход пускового бло- Ktf, выход п оследнего соединен, с первым входом элемента И, катод первого стабилитрона и анод второго стабилитрона блока сравнения подключены к первому и второму входам блока управления временем блокировки, выход кбторого подключен к управляющему входу фазного блок-а, общие точки стабилитронов и резисторов блока сравнения подключены к первому и второму входам фазного блока, выход которого подключен к второму входу элемента И, выход которого я вляется выходом устройства, источник питания, к выходу блока дифференцирования подключен первый вход блока управления, выполненньй в виде первого , компаратора и последовательно со единенных элемента ПАМТЬ и управляющего входа транзисторного ключа, при этом второй и третий входы блока управления соединены с- первым и вторым входами блока управления временем блокировки соответственно, о т л и чающееся тем, что, с целью повышения надежности функционирования устройства путем улучшения от стройки от переходных режимов, в устройство дополнительно введены разделительный диод, формирователь сигнала производной, формирователь управляющих сигналов, а в блок упраления дополнительно введены инверто амплитудный детектор, второй и тре тий транзисторные ключи, второй ком паратор, элемент задержки, расшири

0

15

684

,

20

25

30

35

40

тель импульсов, рез.истор, элемент И-НЕ, при этом к выходу блока дифференцирования подключен вход фор миро- вателя сигнала производной, первьш выход, которого подключен к четвертому входу блока управления, к которому через диод в обратном направлении подключен также первый выход формирователя управляющего сигнала и третий вход фазного блока, четвертый вход которого подключен к второму выходу формирователя сигнала производной и к второму выходу формирователя управляющих сигналов, вход последнего подключен к выходу блока управления, который предназначен для подключения к блоку защиты соседних фаз, при этом в блоке управления первый вход блока управления являете входом второго компаратора, второй вход - первым входом амплитудного детектора, третий вход - входом инвертора, четвертый вход - входом первого транзисторного ключа, а выходом - вход второго транзисторного утюча, при этом выход инвертора подключен к второму входу амплитудного детектора, выход которого соединен с входом первого компаратора, выход которого подключен через элемент задержки к первому входу расширителя импульсов и через третий транзисторный ключ - к первому входу элемента И-НЕ, второй вход которого подключен к выходу второго компаратора, третий вход - к входу второго транзисторного ключа, а выход - к входу элемента память и второму входу расширителя импульсов, выход которого подключен к управляющему входу второго транзисторного ключа, к входу которого подключен первый вывод резистора, второй вывод которого соединен с плюсовьм выводом источника питания.

h ,

/ |

а

w

(PU2.5

| Устройство для дифференциально-фазной защиты электроустановки | 1984 |

|

SU1156184A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-10-23—Публикация

1988-05-23—Подача