Фиг,1

Изобретение относится к измерительной технике и может быть использовано в интегральных схемах входных устройств цифровой обработки аналоговой информации.

Цель изобретения - повьшение частоты дискретизации аналогового сигнала о

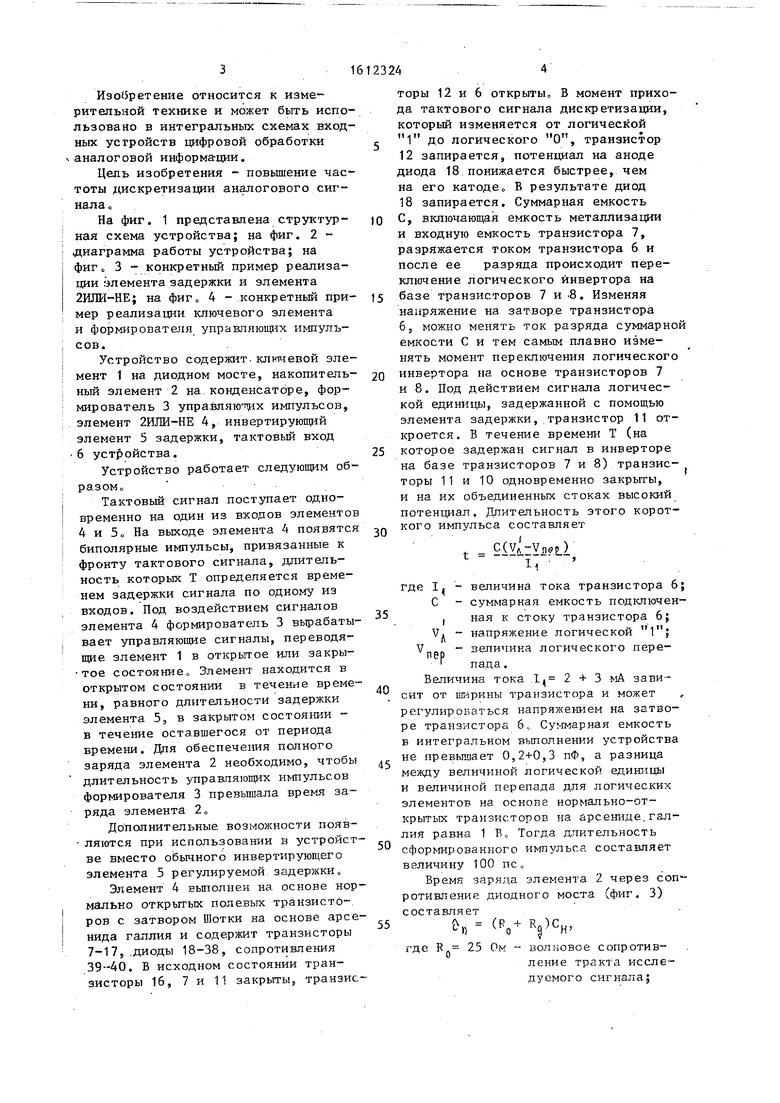

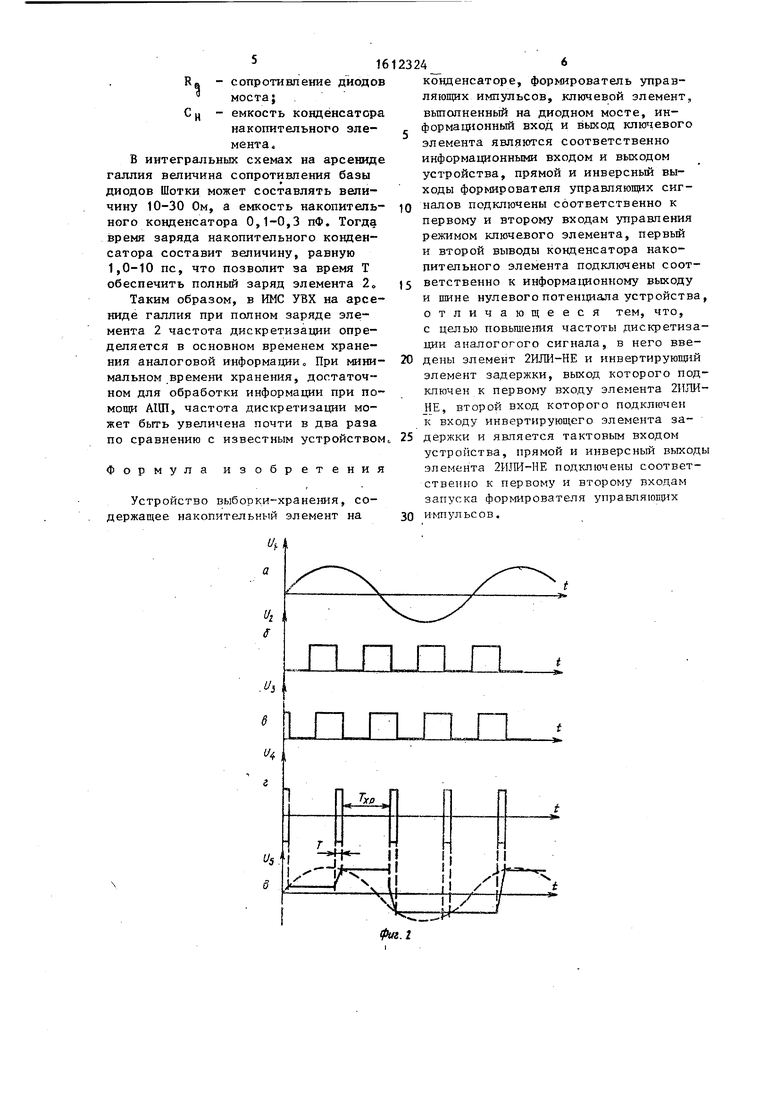

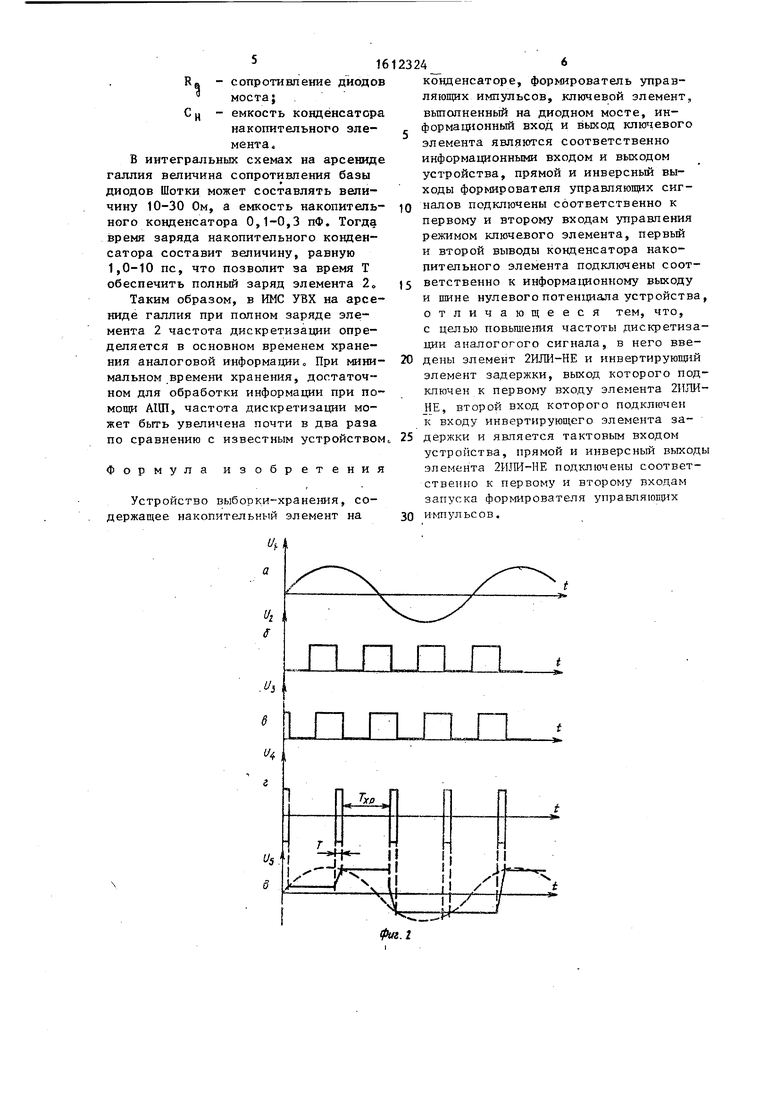

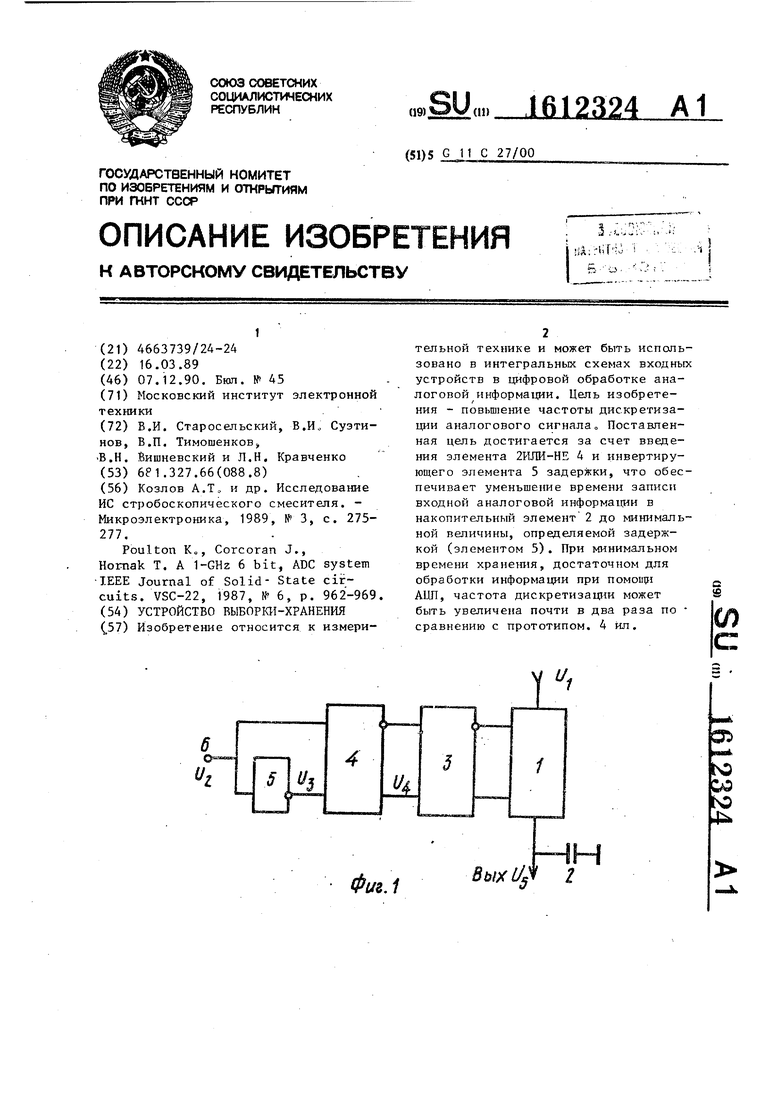

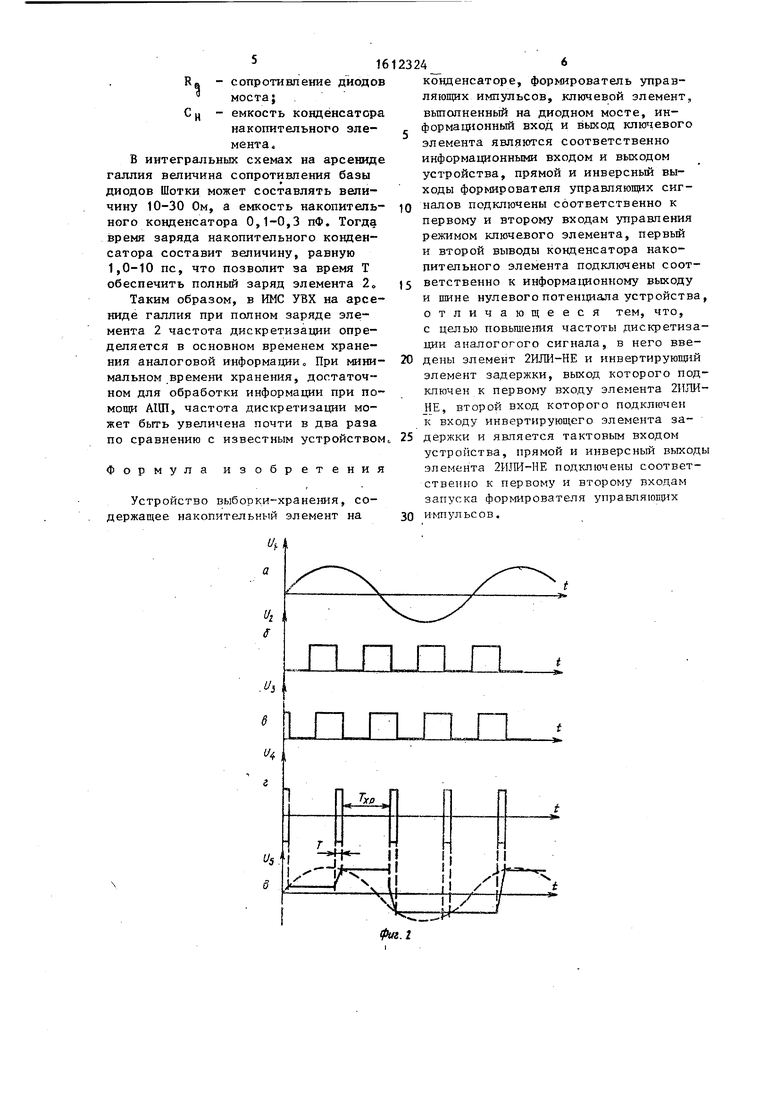

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - иаграмма работы устройства; на фиг 3 - конкретный пример реализации элемента задержки и элемента 2ИЛИ-НЕ; на фиг о 4 - конкретный пример реализации ключевого элемента и формирователя управляющих импульсов.

Устройство содержит.ключевой элемент 1 на диодном мосте, накопительный элемент 2 на конденсаторе, формирователь 3 управляю тих импульсов, элемент 2ИЛИ-НЕ 4, инвертирующий элемент 5 задержки, тактовый вход 6 устройства.

Устройство работает следующим образом,,

Тактовьш сигнал пост.упает одновременно на один из входов элементов 4 и 5с На вькоде элемента 4 появятся биполярные импульсы, привязанные к фронту тактового сигнала, длительность которых Т определяется временем задержки сигнала по одному из входов. Под воздействием сигналов элемента 4 формироватсшь 3 вырабатывает управляющие сигналы, переводящие элемент 1 в открытое или закры- тое состояние Элемент находится в открытом состоянии в течение времени, равного длительности задержки элемента 5, в закрытом состоянии - в течение оставшегося от периода времени. Для обеспечения полного заряда элемента 2 необходимо, чтобы длительность управляющих импульсов формирователя 3 превьпиала время заряда элемента 2

До полнительные возможности появ- ляются при использован-ии в устройстве вместо обычного инвертирующего элемента 5 регулируемой,задержки.

Элемент 4 ньшолнен на основе нормально открытых полевых транзисторов с затвором Шотки на основе арсе- нида галлия и содержит транзисторы 7-17,.диоды 18-38, сопротивления 39-40. Б исходном состоянии транзисторы 16, 7 и 11 закрыты,, транзисторы 12 и 6 открыты, В момент прихода тактового сигнала дискретизации, который изменяется от логической

1 до логического О, транзистор 12 запирается, потенциал на аноде диода 18 понижается быстрее, чем на его катоде. В результате диод 18 запирается. Суммарная емкость

С, включающая емкость металлизации и входную емкость транзистора 7, разряжается током транзистора 6 и после ее разряда происходит переключение логического инвертора на

базе транзисторов 7 и .8. Изменяя напряжение на затвор.е транзистора 6; можно менять ток разряда суммарной емкости С и тем самым плавно изменять момент переключения логического

инвертора на основе транзисторов 7 и В. Под действием сигнала логической единицы, задержанной с помощью элемента задержки, транзистор 11 откроется. В течение времени Т (на

которое задержан сигнал в инверторе на базе транзисторов 7 и 8) транзисторы 11 и 10 одновременно закрыты, и на их объединенных стоках высокий потенциал. Длительность этого короткого импульса составляет

CCVft-Vn E.) - ----: -,

где I, - величина тока транзистора 6; С - суммарная емкость подключен- I ная к стоку транзистора 6;

V, - напряжение логической V р.. - величина логического перег пада.

Величина тока .1,, 2 + 3 мА зависит от ширины транзистора и может , регулироваться напряжением на затворе транзистора 6 , Су марная емкость в интегральном выполнении устройства не превьппает 0,2+0,3 пФ, а разница между величиной логической и величиной перепада для логических элементов на основе нормально-открытых транзисторов на арсениде.галлия равна 1 Б„ Тогда длительность сформированного имлульса составляет величину 100 пс„

Бремя заряда элемента 2 через сопротивление диодного моста (фиг, 3) составляет „ (Р.+ RJC,

РС

где F. 25 Ом - волковое сопротивление тракта исслб дуемого сигнала.;

R« - сопротивление диодов

моста;

С ц - емкость конденсатора накопительного элемента.

В интегральных схемах на арсениде галлия величина сопротивления базы диодов Шотки может составлять величину 10-30 Ом, а емкость накопительного конденсатора 0,1-0,3 пФ. Тогда время заряда накопительного конденсатора составит величину, равную 1,0-10 ПС, что позволит за время Т обеспечить полный заряд элемента 2

Таким образом, в ИМС УВХ на арсениде галлия при полном заряде элемента 2 частота дискретизации определяется в основном временем хранения аналоговой информа1д }и« При минимальном времени хранения, достаточном для обработки информации при помощи А1Ш, частота дискретизации может быть увеличена почти в два раза по сравнению с известным устройством

Формула изобретения

Устройство выборки-хранения, содержащее накопительный элемент на

конденсаторе, формирователь управляющих импульсов, ключевой элемент,

вьшолненный на диодном мосте, информационный вход и выход ключевого

элемента являются соответственно информационными входом и выходом устройства, прямой и инверсный выходы формирователя управляющих сигналов подключены соответственно к первому и второму входам управления режимом ключевого элемента, первый и второй выводы конденсатора накопительного элемента подключены соответственно к информадаонному выходу и шине нулевого потенциала устройства, отличающееся тем, что, с целью повышения частоты дискретизации аналогогого сигнала, в него введены элемент 2ИЛИ-НЕ и инвертирующий элемент задержки, выход которого подключен к первому входу элемента 2ИЛИ- НЕ, второй вход которого подключен к входу инвертируюп его элемента задержки и является тактовым входом

устройства, прямой и инверсный выходы элемента 2ШМ-НЕ подключены соответственно к первому и второму входам запуска формирователя управляющих

игшульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОТОПРИЕМНАЯ ЛИНЕЙКА | 2009 |

|

RU2419242C1 |

| ШИРОКОПОЛОСНАЯ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА УСТРОЙСТВА ВЫБОРКИ И ХРАНЕНИЯ | 2003 |

|

RU2244374C2 |

| МНОГОЭЛЕМЕНТНЫЙ ФОТОДАТЧИК И УСТРОЙСТВО РЕГИСТРАЦИИ ИЗОБРАЖЕНИЯ | 2009 |

|

RU2417436C1 |

| Устройство для определения междуфазных замыканий и замыканий на землю в сетях с изолированной нейтралью напряжением 6-10 кВ | 2022 |

|

RU2788035C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| Универсальная тиристорная система зажигания | 1990 |

|

SU1781447A1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ | 2015 |

|

RU2595487C1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Стробоскопический преобразователь электрических сигналов | 1984 |

|

SU1239607A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

Изобретение относится к измерительной технике и может быть использовано в интегральных схемах входных устройств в цифровой обработке аналоговой информации. Цель изобретения - повышение частоты дискретизации аналогового сигнала. Поставленная цель достигается за счет введения элемента 2ИЛИ-НЕ 4 и инвертирующего элемента 5 задержки, что обеспечивает уменьшение времени записи входной аналоговой информации в накопительный элемент 2 до минимальной величины, определяемой задержкой (элементом 5). При минимальном времени хранения, достаточном для обработки информации при помощи АЦП, частота дискретизации может быть увеличена почти в два раза по сравнению с прототипом. 4 ил.

г S

|J7j

1 J

{38

| Козлов А.Т, и др | |||

| Исследование ИС стробоскопического смесителя | |||

| - Микроэлектроника, 1989, № 3, с | |||

| ТЕЛЕФОННЫЙ АППАРАТ, ОТЗЫВАЮЩИЙСЯ ТОЛЬКО НА ВХОДЯЩИЕ ТОКИ | 1921 |

|

SU275A1 |

| Poulton К„, Corcoran J., Homak Т | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Способ гидрогенизации жиров, масел, жирных кислот из них и других непредельных органических соединений | 1913 |

|

SU962A1 |

Авторы

Даты

1990-12-07—Публикация

1989-03-16—Подача