Фиг.1

тель20. Сущность изобретения заключается в возможности двухкратного сокращения длительности измерительного временного интервала с сохранением заданной точности измерения частоты гармонического сигнала. Это достигается путем формирования из исходного гармонического сигнала импульсной последовательности, каждый импульс которой отмечает момент изменения полярности исходного гармонического сигнала, и автоматическим выбором необходимого образцового измерительного интервала счета для заданной погрешности измерения. 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1981 |

|

SU970255A1 |

| Цифровой автоматический измеритель интервалов времени | 1980 |

|

SU875325A1 |

| Цифровой частотомер | 1985 |

|

SU1275314A2 |

| Цифровой частотомер | 1982 |

|

SU1190285A1 |

| Устройство для пересчета импульсов с автоматическим выбором интервалом счета | 1979 |

|

SU783985A1 |

| Цифровой частотомер с нониусной интерполяцией | 1980 |

|

SU868612A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Формирователь измерительного интервала цифрового частотомерапериодомера | 1978 |

|

SU748269A1 |

| Цифровой измеритель периода | 1981 |

|

SU980063A1 |

| Цифровой частотомер с автоматическим выбором пределов измерения | 1973 |

|

SU474760A1 |

Изобретение может быть испол-.зовано в автоматических измерителях частоты гармонического сигнала. Цель изобретения - повышение быстродействия измерения при задгиной точности. Поставленная цель достигается тем, то в цифровой частотомер для измерения частоты гармонического сиг1 г ни з нн и нала введены диодный мост 3, блок 14 выбора образцового интервала счета, который содержит первый и второй блоки, элементов И, блок элементов задержки, блок триггеров, блок формирователей импульса, информационные входы, первый и второй управляющие входы, первую и вторую группы выходов. Частотомер также содержит- входную шину 1 сигнала измеряемой частоты, входной формирователь 2, ключ 4, счетчик 5 импульсов, блок 6 цифровой регистрации, блок 7 вентилей, состоящий из элементов И 8 и первого элемента ИЛИ 9, первый и второй формирователи 10 и 11, блок 12 несовпадения, второй элемент ИЛИ 13, входную шину 15 импульса синхронизации, генератор 16 образцовой частоты, блок 17 регулировки, делитель 18 частоты, источник 19 разрешающего сигнала, переключаbf Ё

Изобретение относится к измерительной технике и может быть использовано в автоматических измерителях частоты.

Цель изобретения - повышение быстродействия измерения при заданной точно- сти.

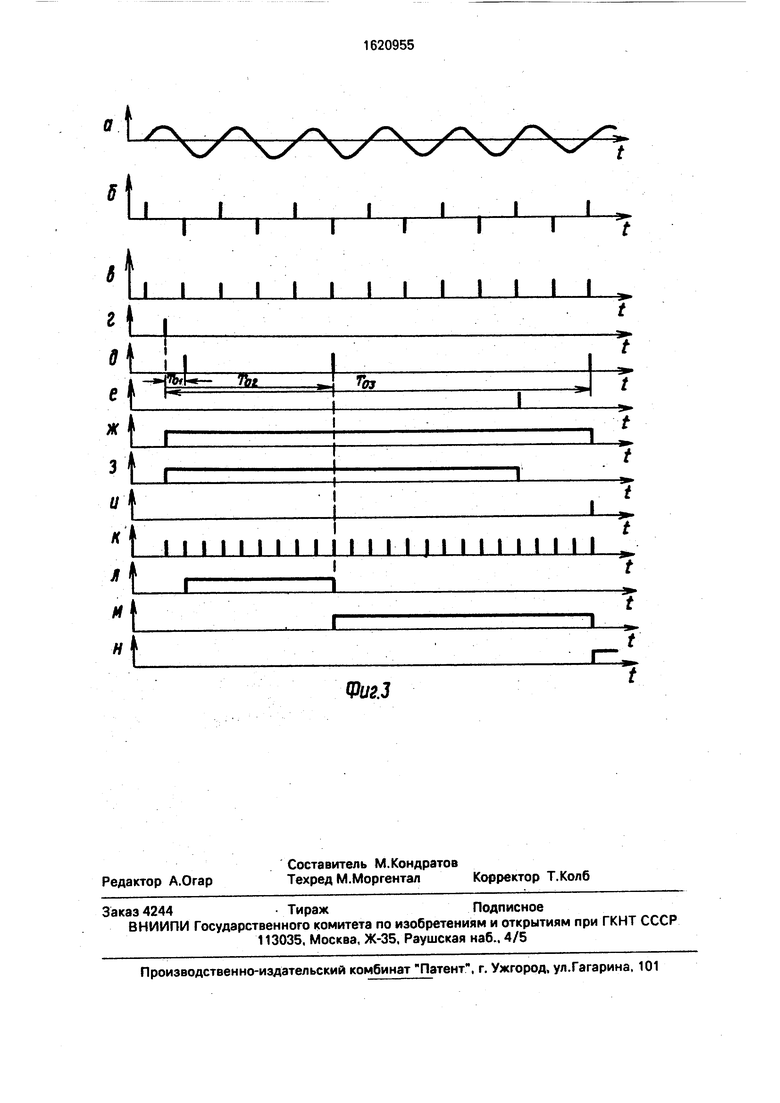

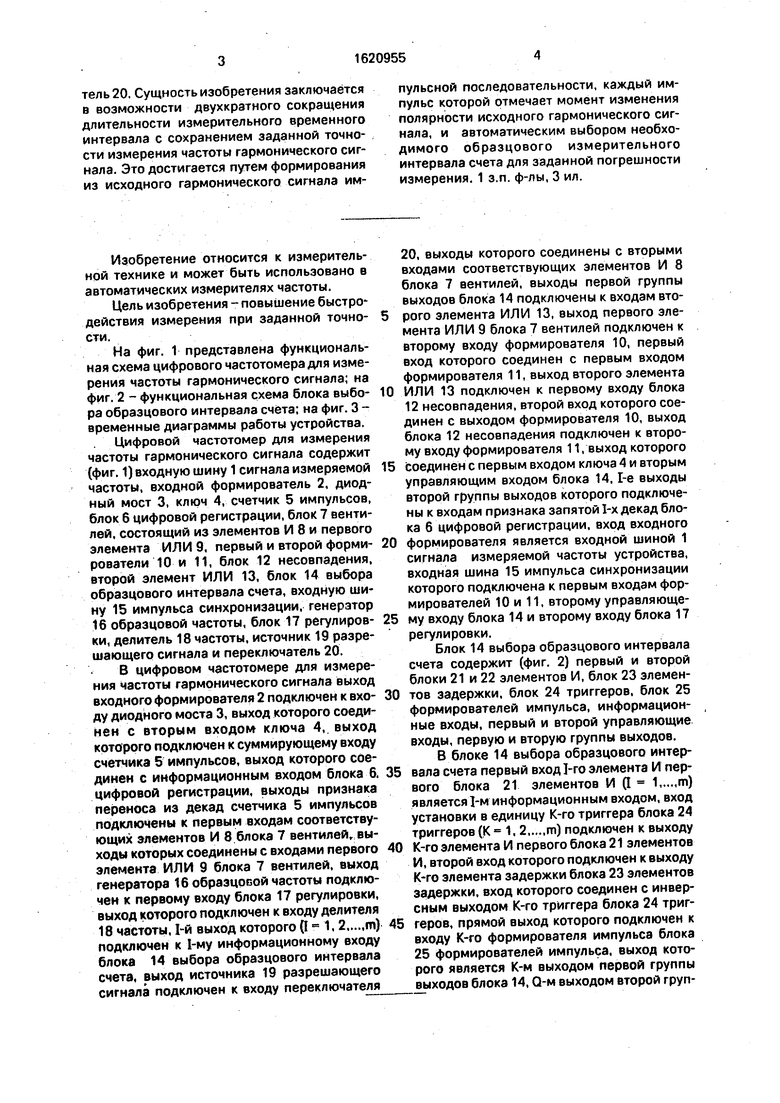

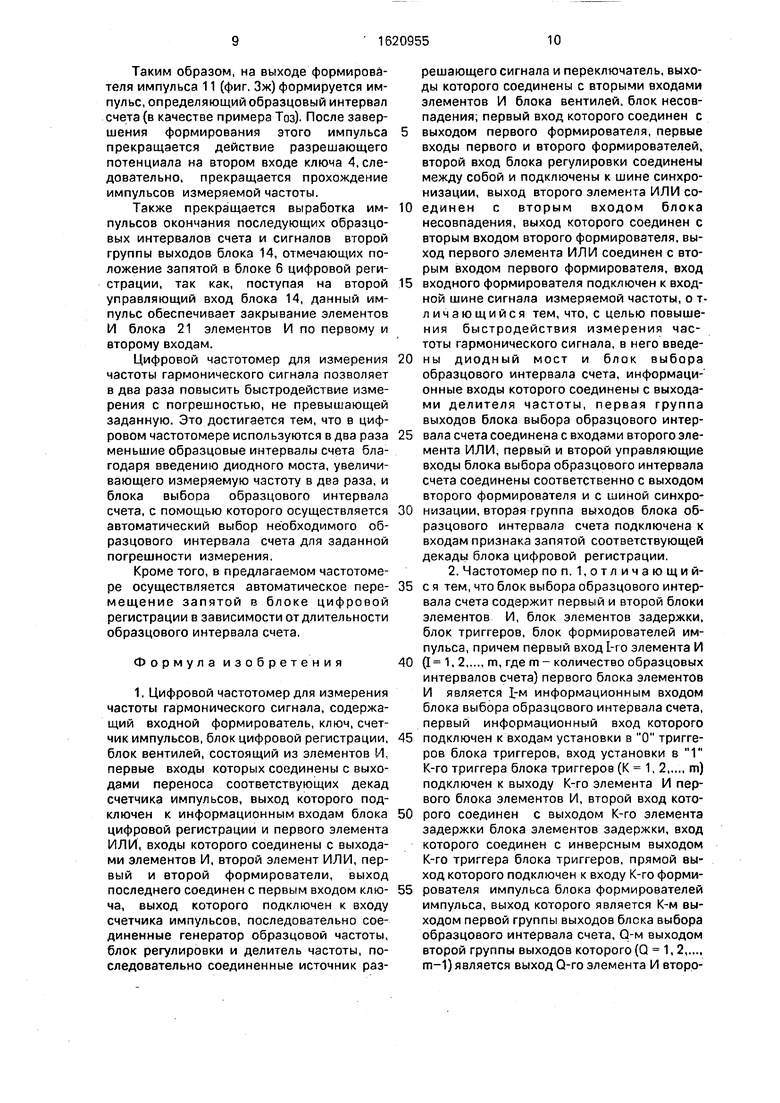

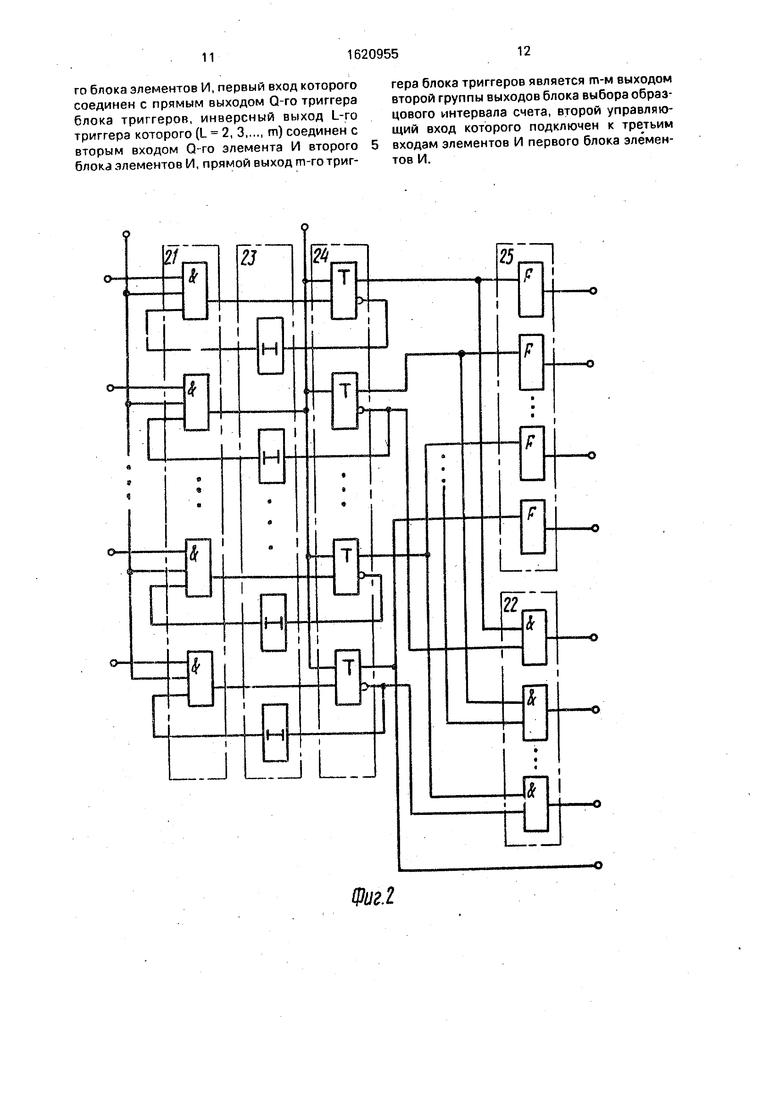

На фиг. 1 представлена функциональная схема цифрового частотомера для измерения частоты гармонического сигнала; на фиг. 2 - функциональная схема блока выбо- ра образцового интервала счета; на фиг. 3 - временные диаграммы работы устройства.

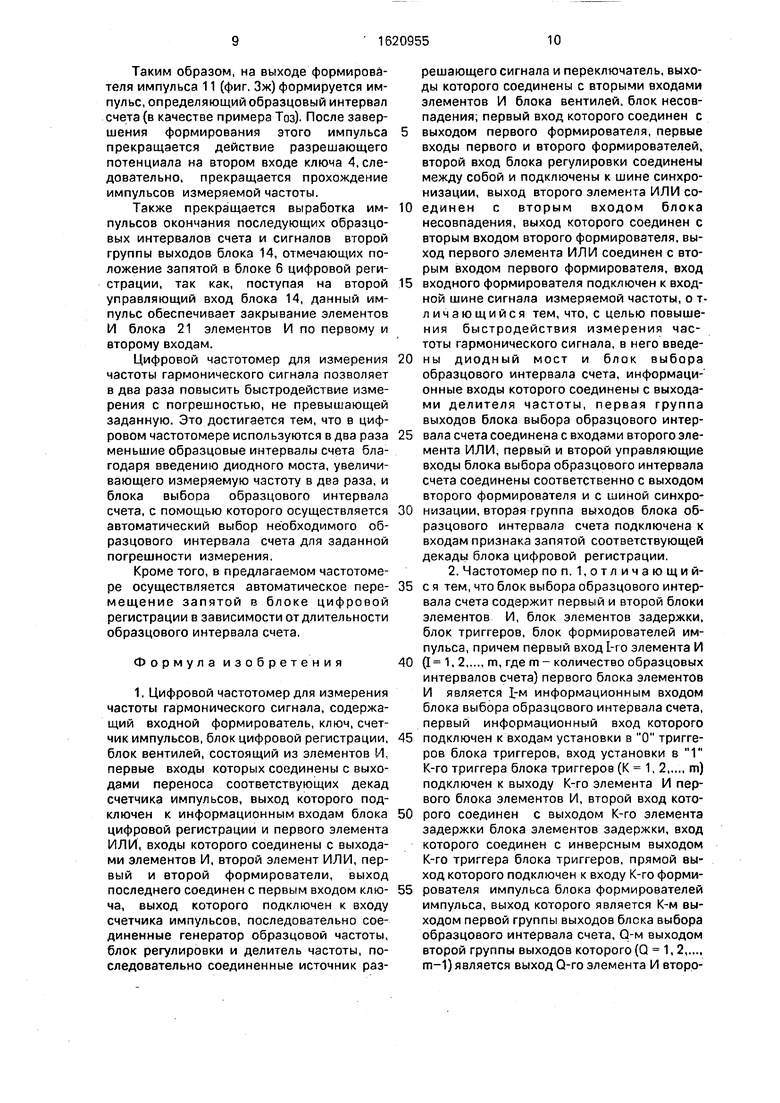

Цифровой частотомер для измерения частоты гармонического сигнала содержит (фиг. 1) входную шину 1 сигнала измеряемой частоты, входной формирователь 2, диодный мост 3, ключ 4, счетчик 5 импульсов, блок б цифровой регистрации, блок 7 вентилей, состоящий из элементов И 8 и первого элемента ИЛИ 9, первый и второй форми- рователи 10 и 11, блок 12 несовпадения, второй элемент ИЛИ 13, блок 14 выбора образцового интервала счета, входную шину 15 импульса синхронизации, генератор 16 образцовой частоты, блок 17 регулиров- ки, делитель 18 частоты, источник 19 разрешающего сигнала и переключатель 20.

В цифровом частотомере для измерения частоты гармонического сигнала выход входного формирователя 2 подключен к вхо- ду диодного моста 3, выход которого соединен с вторым входом ключа 4, выход которого подключен к суммирующему входу счетчика 5 импульсов, выход которого соединен с информационным входом блока 6. цифровой регистрации, выходы признака переноса из декад счетчика 5 импульсов подключены к первым входам соответствующих элементов И 8 блока 7 вентилей, выходы которых соединены с входами первого элемента ИЛИ 9 блока 7 вентилей, выход генератора 16 образцовой частоты подключен к первому входу блока 17 регулировки, выход которого подключен к входу делителя 18 частоты, 1-й выход которого 0 1,2,...,т) подключен к 1-му информационному входу блока 14 выбора образцового интервала счета, выход источника 19 разрешающего сигнала подключен к входу переключателя

20, выходы которого соединены с вторыми входами соответствующих элементов И 8 блока 7 вентилей, выходы первой группы выходов блока 14 подключены к входам второго элемента ИЛИ 13, выход первого элемента ИЛИ 9 блока 7 вентилей подключен к второму входу формирователя 10, первый вход которого соединен с первым входом формирователя 11, выход второго элемента ИЛИ 13 подключен к первому входу блока 12 несовпадения, второй вход которого соединен с выходом формирователя 10, выход блока 12 несовпадения подключен к второму входу формирователя 11, выход которого соединен с первым входом ключа 4 и вторым управляющим входом блока 14,1-е выходы второй группы выходов которого подключены к входам признака запятой 1-х декад блока 6 цифровой регистрации, вход входного формирователя является входной шиной 1 сигнала измеряемой частоты устройства, входная шина 15 импульса синхронизации которого подключена к первым входам формирователей 10 и 11, второму управляющему входу блока 14 и второму входу блока 17 регулировки.

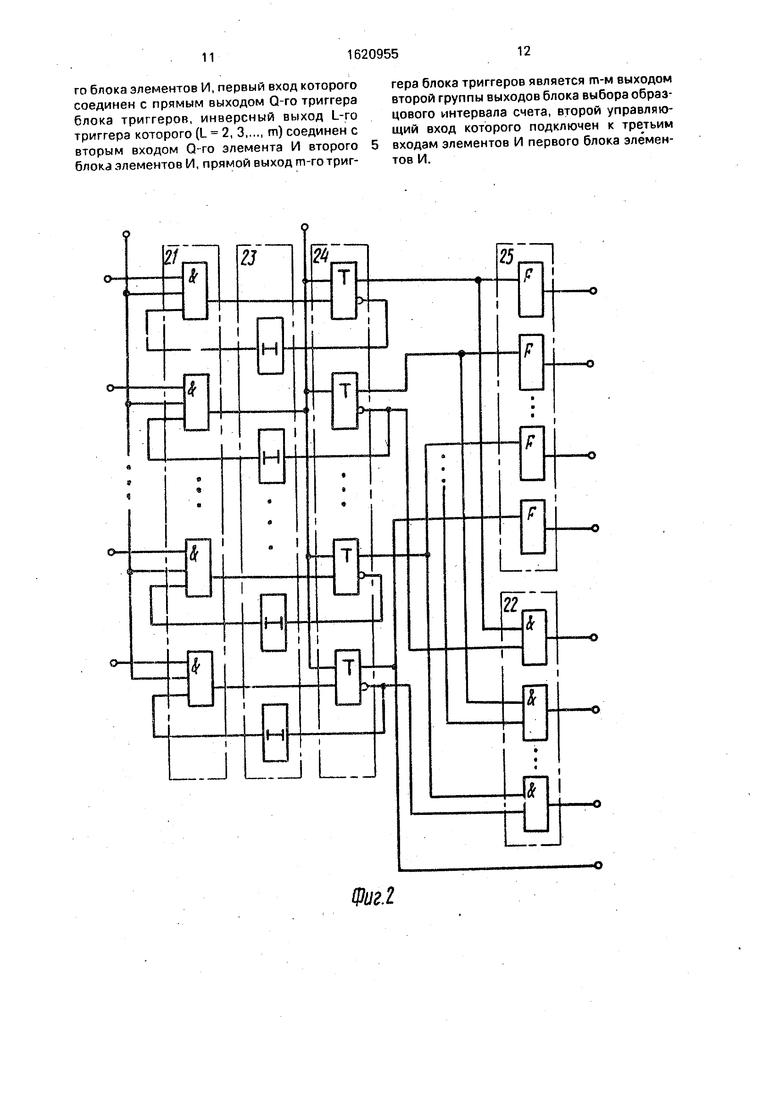

Блок 14 выбора образцового интервала счета содержит (фиг. 2) первый и второй блоки 21 и 22 элементов И, блок 23 элементов задержки, блок 24 триггеров, блок 25 формирователей импульса, информационные входы, первый и второй управляющие входы, первую и вторую группы выходов.

В блоке 14 выбора образцового интервала счета первый вход 1-го элемента И первого блока 21 элементов И (I 1„..,т) является 1-м информационным входом, вход установки в единицу К-го триггера блока 24

триггеров (К 1, 2т) подключен к выходу

К-го элемента И первого блока 21 элементов И, второй вход которого подключен к выходу К-го элемента задержки блока 23 элементов задержки, вход которого соединен с инверсным выходом К-го триггера блока 24 триггеров, прямой выход которого подключен к входу К-го формирователя импульса блока 25 формирователей импульса, выход которого является К-м выходом первой группы выходов блока 14, Q-м выходом второй труппы выходов которого (0 1, 2,..., т-1) является выход Q-ro элемента И второго блока 22 элементов И, первый вход которого соединен с прямым выходом Q-ro триггера блока 24 триггеров, инверсный выход 1-го триггера которой (L 2, 3,...,т) соединен с вторым входом Q-ro элемента И второго блока 22 элементов И, прямой выход m-ro триггера блока 24 триггеров является т-м выходом второй группы выходов блока 14, первый управляющий вход которого подключен к входам установки в О триггеров блока 24 триггеров, второй управляющий вход подключен к третьим входам элементов И первого блока 21 элементов И.

На фиг. 3 представлены временные диаграммы, поясняющие принцип работы устройства: а - гармонический сигнал, поступающий на шину 1 устройства; б - сигнал с выхода входного формирователя 2; в - сигнал, полученный на выходе диодного моста 3; г - сигнал синхронизации на входной шине 15 импульса синхронизации; д - сигнал с выхода элемента ИЛИ 13; е - сигнал на выходе элемента ИЛИ 9; ж - сигнал с выхода формирователя 11; з - сигнал с выхода формирователя 10; и - сигнал на выходе блока 12 несовпадения; к - импульсы измеряемой частоты с выхода ключа 4; л, м, н - сигналы на первом, втором и третьем выходах второй группы выходов блока 14 соответственно.

Частотомер работает следующим образом.

Перед началом измерения с помощью переключателя 20 осуществляется задание необходимой погрешности измерения. Это достигается подачей разрешающего потенциала от источника 19 разрешающего сигнала на второй вход одного из элементов И 8 блока 7 вентилей (например, первого элемента И 8).

На вход входного формирователя 2 подается гармонический сигнал, частоту которого необходимо измерить (фиг. За), на выходе формирователя появляется последовательность разнополярных импульсов (фиг. 36), следующих с периодом, в два раза меньшим периода измеряемой частоты гармонического сигнала, вследствие того, что входной формиро ватель 2 формирует импульс каждый раз при переходе колебаний входного сигнала через ноль. Последовательность разнополярных импульсов поступает на вход диодного моста 3, на выходе которого появляется последовательность однополярных импульсов (фиг. Зв). На выходе ключа 4 данная последовательность импульсов проходит лишь втом случае.если на

втором входе ключа 4 присутствует разрешающий потенциал, вырабатываемый формирователем 11.

При появлении импульса синхронизации на входной шине 15 (фиг. Зг) формирователи 10 и 11 импульсов устанавливаются в единичное состояние. При этом на выходе формирователя 11 импульса устанавливается сигнал единичного уровня, являющийся

0 разрешающим для ключа 4, который, поступая на второй управляющий вход блока 14, подготавливает элементы И блока 21 элементов И блока 14 к открытию (фиг. 2).

Импульс синхронизации с входной ши5 ны 15 синхронизации устройства поступает также на управляющий вход блока 14, устанавливая триггеры блока 24 триггеров в нулевое состояние, и на второй вход блока 17 регулировки, разрешая прохождение сигна0 ла с выхода генератора 16 образцовой частоты.

Импульсы с выхода ключа 4 поступают на счетчик 5 импульсов. На выходе формирователя 10 сигнал единичного уровняяв5 ляется запрещающим для блока 12 несовпадения, и при его наличии сигнал, подаваемый на второй вход блока 12, не может пройти на его выход. Поэтому до тех пор, пока формирователь 10 импульса не

0 изменит своего состояния под воздействием импульса с выхода элемента ИЛИ 9 блока 7, импульс с выхода элемента ИЛИ 13 не проходит через блок 12 несовпадения на второй вход формирователя 11 и не изменя5 ет его состояния.

Сигнал образцовой частоты с выхода генератора 16 через блок 17 регулировки поступает на вход делителя 18 частоты, на 1-й 0 выход которого подается последовательность сигналов 1-го образцового интер(0-D 1

вала счета с периодом T0i 1 Q(

Fo6p.

.где

1 1,...,m; Fo6p - образцовая частота, F06p - 5 2 МГц. Данная последовательность поступает на первый информационный вход блока 14 выбора образцового интервала счета. Работа блока 14 состоит в следующем. При поступлении импульса синхрони- 0 зации на первый управляющий вход блока 14 блок 24 триггеров устанавливается в нулевое состояние. При поступлении первого сигнала из последовательности сигналов первого образцового интервала счета на 5 первый информационный вход он проходит через первый элемент И первого блока 21 элементов И, поскольку на втором входе данного элемента присутствует сигнал высокого уровня с инверсного выхода первого

триггера блока 24 триггеров, прошедший через первый элемент задержки блока 23 элементов задержки, а на третьем - сигнал высокого уровня с второго управляющего входа блока 14, подключенного к выходу формирователя 11.

Импульс с выхода элемента И первого блока 21 элементов И устанавливает в единичное состояние первый триггер блока 24 триггеров. Элементы задержки предназначены для компенсации времени распространения сигнала в элементах И блока 21 элементов И. Появление сигнала высокого уровня на прямом выходе первого триггера блока 24 вызывает выработку импульса окончания первого образцового интервала счета на выходе первого формирователя блока 25 формирователей импульса, поступающего на первый выход первой группы выходов блока 14 и далее на первый вход элемента ИЛИ 13 устройства, а также вызывает появление сигнала высокого уровня на выходе первого элемента И блока 2 элементов И, так как на втором входе этого элемента присутствует сигнал высокого уровня с инверсного выхода второго триггера блока триггеров. Сигнал высокого уровня с выхода первого элемента И блока 22 элементов И поступает на первый выход второй группы выходов блока 14 (фиг. Зл) и далее на вход признака запятой первой декады блока 6 цифровой регистрации, вызывая индикацию запятой в первой декаде блока 6.

Последующие импульсы последовательности первого образцового интервала счета, поступая на первый информационный вход блока 14 ничего не изменяют, так как могут пройти через первый элемент И .блока 21 элементов И из-за наличия на его втором входе сигнала низкого уровня с инверсного выхода первого триггера блока 24 триггеров.

При поступлении первого сигнала из последовательности сигналов второго образцового интервала счета происходит установка второго триггера блока триггеров в единичное состояние аналогично первому триггеру. Аналогично первому формирователю импульса из блока 25 второй формирователь вырабатывает импульс окончания второго образцового интервала счета, поступающий на второй выход первой группы выходов блока 14 и далее на второй вход элемента ИЛИ 13 устройства.

Изменение состояния второго триггера блока 24 приводит к исчезновению высокого уровня на первом выходе второй группы выходов блока 14, так как на втором входе первого элемента И блока 22 присутствует низкий уровень с инверсного выхода второ

го триггера блока 24 и к появлению высокого уровня на втором выходе второй группы выходов блока 14, поскольку на первом и втором входах второго элемента И блока 22

присутствует высокий уровень с прямого выхода второго триггера и инверсного выхода третьего триггера блока 24 триггеров. Сигнал уровня логической единицы с второго выхода второй группы выходов (фиг. Зм)

0 блока 14 поступает на вход признака запятой второй декады блока 6 цифровой регистрации, вызывая индикацию запятой теперь уже во второй декаде.

Процесс выработки импульсов оконча5 ния образцовых интервалов счета и перемещения запятой в блоке 6 цифровой регистрации продолжается аналогичным образом до появления низкого уровня на втором управляющем входе блока 14 в ре0 зультате установки формирователя 11 импульса в нулевое состояние. Импульсы с первой группы выходов блока 14 поступают на входы элемента ИЛИ 13, на выходе которого образуется последовательность им5 пульсов окончания образцовых интервалов

счета Toi, ТоаТот (фиг. Зд).

С начала формирования импульса в формирователе 11 счетчик 5 импульсов осуществляет подсчет импульсов, поступаю0 щих на его суммирующий вход.

Когда количество импульсов, подсчитываемых счетчиком 5, станет таким, что на выходе признака переноса из первой декады счетчика 5 импульсов появляется им5 пульс, то этот импульс проходит на выход первого элемента И 8 блока 7, так как именно на его втором входе имеется разрешающий потенциал (высокий уровень) с переключателя 20. Через элемент ИЛИ 9

0 этот импульс (фиг. Зе) проходит на второй вход формирователя 10 импульса и устанавливает его в нулевое состояние (фиг. Зз). Таким образом, заканчивается тот необходимый интервал времени, в течение кото5 рого производите , измерение частоты входного сигнала с погрешностью, не превышающей допустимую, задаваемую переключателем 20. Но этот интервал времени не является образцовым интервалом сче0 та, поскольку конец образцового интервала счета определяется одним из импульсов элемента ИЛИ 13 (фиг. Зд).

После изменения состояния формиро- вателя 10 блок 12 несовпадения оказы5 вается подготовленным для пропускания импульса с выхода элемента ИЛИ 13. Импульс проходит через блок 12 несовпадения, поступая на второй вход формирователя 11 импульса, и устанавливает его в нулевое состояние.

Таким образом, на выходе формирователя импульса 11 (фиг. Зж) формируется импульс, определяющий образцовый интервал счета (в качестве примера Тоз). После завершения формирования этого импульса прекращается действие разрешающего потенциала на втором входе ключа 4, следовательно, прекращается прохождение импульсов измеряемой частоты.

Также прекращается выработка импульсов окончания последующих образцовых интервалов счета и сигналов второй группы выходов блока 14, отмечающих положение запятой в блоке 6 цифровой регистрации, так как, поступая на второй управляющий вход блока 14, данный импульс обеспечивает закрывание элементов И блока 21 элементов И по первому и второму входам.

Цифровой частотомер для измерения частоты гармонического сигнала позволяет в два раза повысить быстродействие измерения с погрешностью, не превышающей заданную. Это достигается тем, что в цифровом частотомере используются в два раза меньшие образцовые интервалы счета благодаря введению диодного моста, увеличивающего измеряемую частоту в два раза, и блока выбора образцового интервала счета, с помощью которого осуществляется автоматический выбор необходимого образцового интервала счета для заданной погрешности измерения,

Кроме того, в предлагаемом частотомере осуществляется автоматическое перемещение запятой в блоке цифровой регистрации в зависимости от длительности образцового интервала счета,

Формула изобретения

выходом первого формирователя, первые входы первого и второго формирователей, второй вход блока регулировки соединены между собой и подключены к шине синхронизации, выход второго элемента ИЛИ со0 единен с вторым входом блока несовпадения, выход которого соединен с вторым входом второго формирователя, выход первого элемента ИЛИ соединен с вторым входом первого формирователя, вход

5 входного формирователя подключен к входной шине сигнала измеряемой частоты, о т- личающийся тем, что, с целью повышения быстродействия измерения частоты гармонического сигнала, в него введе0 ны диодный мост и блок выбора образцового интервала счета, информационные входы которого соединены с выходами делителя частоты, первая группа выходов блока выбора образцового интер5 вала счета соединена с входами второго элемента ИЛИ, первый и второй управляющие входы блока выбора образцового интервала счета соединены соответственно с выходом второго формирователя и с шиной синхро0 низации,вторая группа выходов блока образцового интервала счета подключена к входам признака запятой соответствующей декады блока цифровой регистрации.

0 (1 1, 2,..., т, где т- количество образцовых интервалов счета) первого блока элементов И является 1-м информационным входом блока выбора образцового интервала счета, первый информационный вход которого

5 подключен к входам установки в О триггеров блока триггеров, вход установки в 1

К-го триггера блока триггеров (К 1, 2т)

подключен к выходу К-ro элемента И первого блока элементов И, второй вход кото0 рого соединен с выходом К-го элемента задержки блока элементов задержки, вход которого соединен с инверсным выходом К-го триггера блока триггеров, прямой выход которого подключен к входу К-го форми5 рователя импульса блока формирователей импульса, выход которого является К-м выходом первой группы выходов блока выбора образцового интервала счета, Q-м выходом

второй группы выходов KOToporo(Q 1,2

m-1) является выход Q-ro элемента И второго бпока элементов И, первый вход которогогера блока триггеров является m-м выходом соединен с прямым выходом Q-ro триггеравторой группы выходов блока выбора образ- блока триггеров, инверсный выход L-roцового интервала счета, второй управляю- триггера которого (1 2, 3,..., т) соединен сщий вход которого подключен к тредьим вторым входом Q-ro элемента И второго5 входам элементов И первого блока элёмен- блона элементов И, прямой выход m-готриг-тов И.

Фиг

t

| Цифровой частотомер | 1981 |

|

SU970255A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1991-01-15—Публикация

1989-01-04—Подача