1

Изобретение относится к электроизмерительной технике и может быть использовано при создании прецизионных цифровых частотомеров.

Известен цифровой измеритель частоты, отношения двух частот и процентного отклонения измеряемой частоты от номинальной, содержащий входной формирователь, синхронизируемое запоминакяцее устройство, ключ, основной счетчик импульсов, селектор периода измеряемой частоты, нониусную схему отсчета дополнительных разрядов, образованную формирователем последовательности импульсов нониусной частоты, схемой совпадения, нониусным ключом и расширителем импульсов, а также счетчики дополнительных разрядов, при этом измеритель частоты снабжен линейным преобразователем длительности остаточных интервалов, схемой ИЛИ и коммутатором, причем входы линейного преобразователя подключены к выходам расши,рителя импульсов, входного формирователя и схемы совпадения, а выход через схему ИЛИ, второй вход которой подключен к выходу синхронизируемого запоминающего устройства формирования временного измерительного интервала, подключен ко входу запуска формирователя последовательности импульсов нониусной частоты и через коммутатор, подключенный вторым входом к выходу нониусного ключа - ко входам счетчиком дополнительных разрядов riD

Недостаток известного устройства - низкая точность измерения.

10

Наиболее близким к предлагаемому по техническому ранению является цифровой частотомер с нониусной интерполяцией , содержащий генератор образцовой частоты, подключенный

15 через ключ синхронизации измерительного временного интервгша с импульсами измеряемой частоты на выходе входного формирователя к блоку пересчета , выходы которого .соединены.

20 с входами схемы сравнения, другие входы которой соединены с выходами запоминакицего счетчика, а вход последнего через ключ селектора подключен к выходу ключа синхронизации,

25 причем другой вход ключа селектора через селектор присоединен к выходу входного формирователя, нониусный ключ, вход которого соединен с выходом блока сравнения, а выход - с кодовым входом пересчетного блока и

Входом блока сравнения последовательностей, основной счетчик, соединенный через основной ключ с выходом входного формирователя и выходом пересчетного .блока, и нониусные счетчики по числу этапов интерполирования, при этом частотомер снабжен коммутатором и блоком управления пересчетом, включенным в цепь обратной связи пересчетного блока, причем первый управляющий вход его соединен с выходом пересчетной схемы а его второй управляющий вход и управляющий вход коммутатора подключены к выходу блока сравнения опорно и нониусной последовательностей, при этом выход блока сравнения кодов через нониусный ключ и когФ1утатор подключен к входу нониусных счетчиков Гз

Недостатком известного устройства является сложность конструкции и низкая точность измерения частоты.

Цель изобретения - повышение точности устройства.

Указанная цель достигается тем, что в цифровой частотомер с нониусной интерполяцией, содержащий последовательно соединенные генератор образцовой частоты, ключ синхронизации, блок пересчета и блок сравнения, выход которого подключен к первому входу нониусного временного селектора, выход последнего соединен со вторым входом блока пересчета, с первым входом блока сравнения последовательностей и с первым входом коммутатора, второй вход которого подключен к выходу блока сравнения последовательностей, входной формирователь, выход которого соединен с вторым входом ключа синхронизации, с первым входом основного временного селектора и с вторым входом блока сравнения последовательностей, запсадинаюадий счетчик, выходы которого подключены ко вторым входам блока сравнения, основнЬй счетчик, вход которого соединен с выходом основного временного селектора, второй вход которого подключен к второму входу нониусного временного селектора и к второму выходу блока пересчета, а также п нониусных счетчиков, подключейных к первым выходам комт татора, введен формирователь кодов периода, первый вход которого соединен с выходом входного формирователя , /второй его вход подключен к выходт| синхронизации, третьи входы - ко вторым выходам коммутатора, четвертый вход - к выходу блока сравнения последовательностей, пятый вход - к входу основного счетчика, а выход формирователя кодов периода подключен к входу запоминающего счетчика.

Формирователь кодов периода выполнен в виде последовательно соединенных первого дополнительного временного селектора первого триггера, второго дополнительного временного селектора, первого дополнительного блока пересчета и второго дополнительного блока пересчета, последовательно соединенных второго триггера, третьего дополнительного временного селектора, элемента ИЛИ и третьего триггера, а также формирователя короткого импульса, вход которого соединен с вторым выходом первого триггера, причем выход формирователя короткого импульса подключен к второму входу третьего триггера, выход которого соединен с входом первого дополнительного временного селектора а вход элемента ИЛИ подключен к входу второго триггера.

Второй дополнительный блок пересчета формирователя кодов периода выполнен в виде последовательно соединенных счетной декады и дешифратора, последовательно соединенных первого блока задержки, блока запрета и второго блока задержки, причем вход счетной декады подключен к входу первого блока задержки, а выход дешифратора соединен с вторым входом блока запрета.

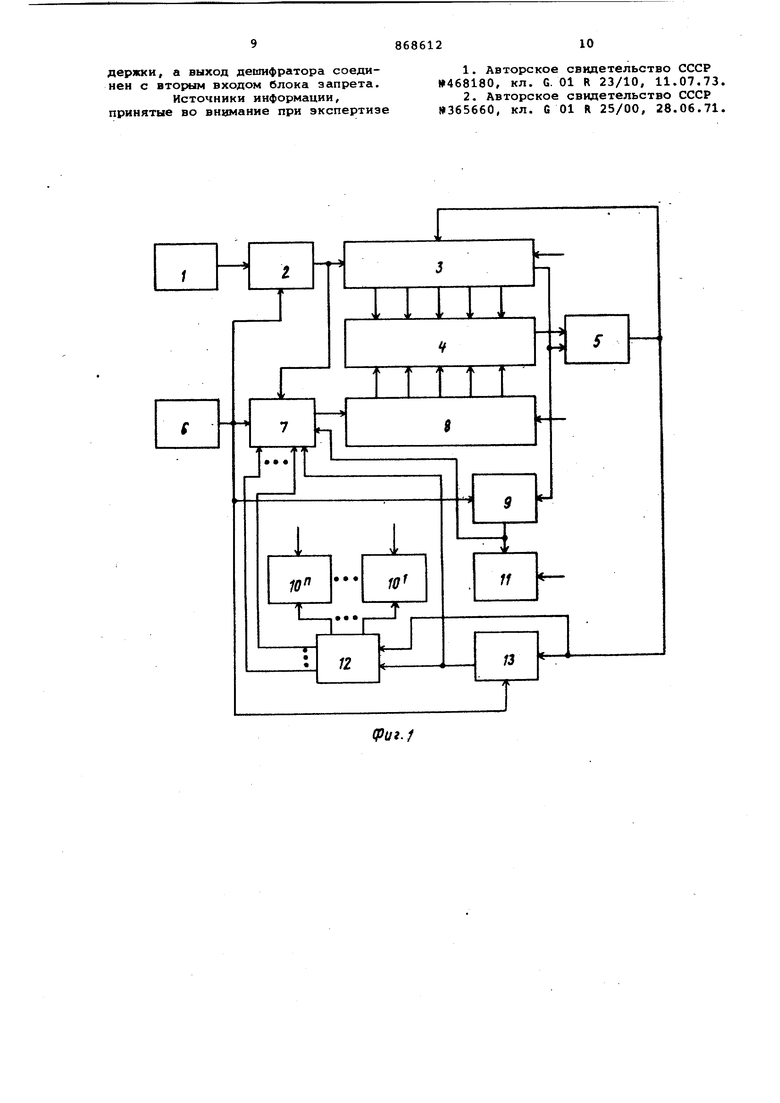

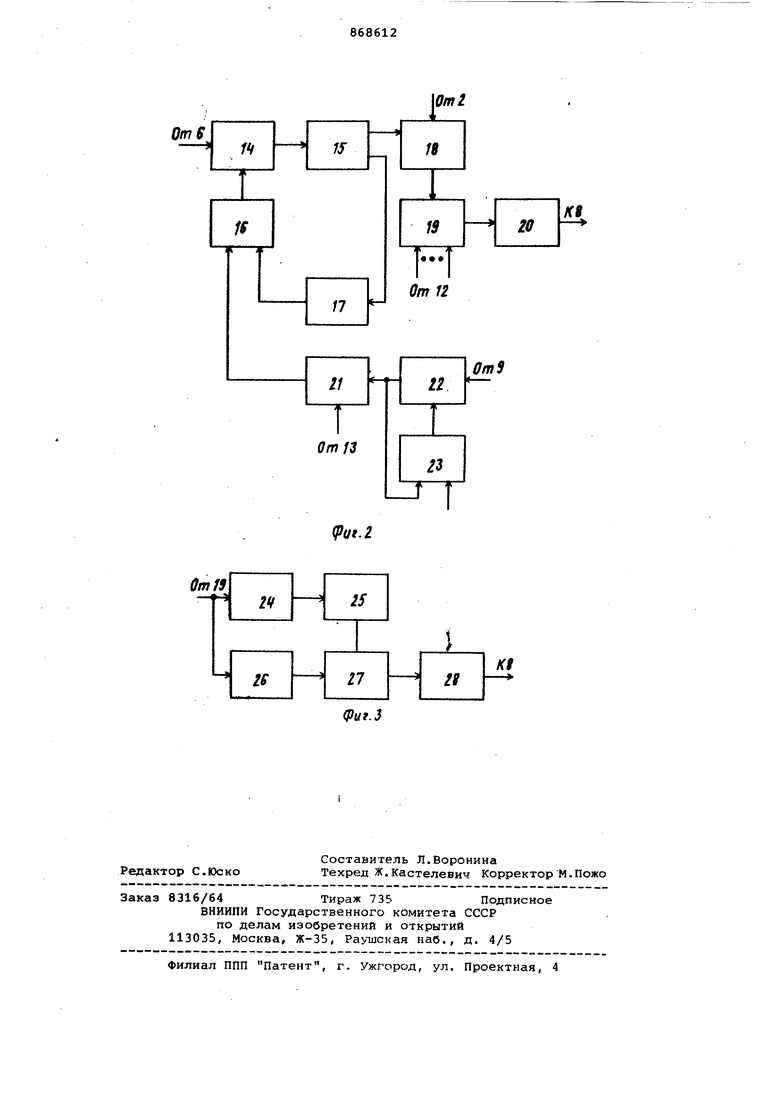

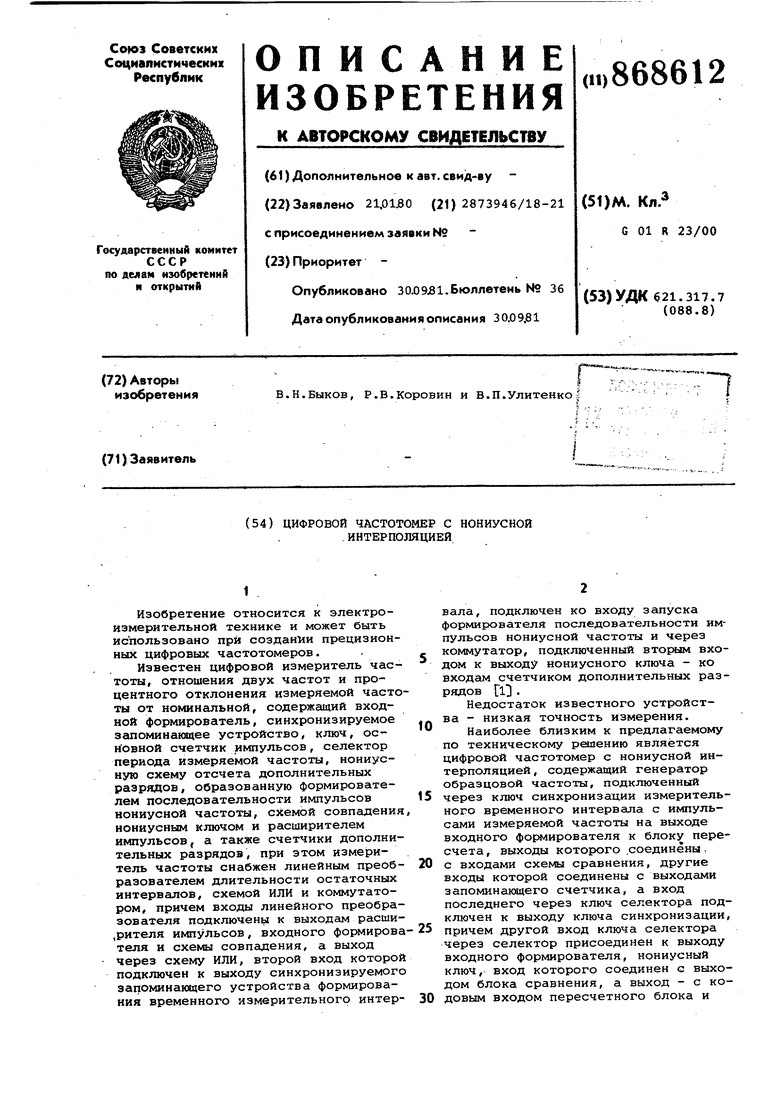

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 блок-схема формирователя кодов периода; на фиг. 3 - блок-схема,второй пересчетной схемы формирователя кодов периода.

Частотомер с нониусной интерполяцией содержит генератор 1 образцовой частоты, ключ 2 синхронизации, блок 3 пересчета, блок 4 сравнения, нониусный временной селектор 5, входной формирователь 6, формирователь 7 кодов периода, запоминающий счетчик 8, основной временной селектор 9, нониусные счетчики 10-10, основной счетчик 11, коммутатор 12, блок 13 сравнения. В свою очередь формирователь 7 кодов периода состоит из временного селектора 14, триггеров 15 и 16, формирователя 17 короткого импульса, временного селектора 18, пересчетных блоков 19 и 20 элемента 21 ИЛИ, временного селектора 22 и триггера 23, при этом пересчетный блок 20 содержит декаду 24, дешифратор 25, элемент 26 задержки, блок 27 запрета и элемент 28 задержки.

Устройство работает следующим образом.

В исходном состоянии, в которое схема переводится сигналгиии Сброс ключ 2, временной селектор 9 закрыты блок 3 и счетчики 8, 10 и 11 находятся в исходном нулевом состоянии.

Процесс измерения начинается с формирования входным формирователем 6 nepBoio импульса входной измеряемой частоты fу. Под действием этого

импульса открывается ключ 2, через который импульсы с генератора 1 образцовой частоты начинают поступать на блок 3. Первый же импульс, поступающий на блок 3, образует на выходе его положительный потенциал, который открывает временной селектор 9. Через открытый временной селектор 9 импульсы со входного формирователя 6 поступают на вход основного счетчика 11. Счетчик 11 насчитывает число целых периодов входного сигнала за некоторый образцовый временной интервал Т, формируемый блоком 3.

Пока счетчик 11 подсчитывает количество указанных периодов,блок 20 формирователя 7 кодов периода записывает в счетчик 8 код, соответствующий длительности 0,9 периода входной исследуемой частоты путем пропускания на счетчик 8 импульсов с выхода ключа 2 в течение интервсша времени между двумя соседними импульсами на выходе входного фо ж ирователя 6, а также путем деления этого количества импульсов на соответствующем пересчетном блоке. По окончании формирования блоком 3 временного интервала Т напряжение на выходе блока 3 прекргицается, в результате чего запирается временной селектор 9, прекращая поступление импульсов на счетчик 11, и открывается временной селектор 5. Пересчетный блок 3 при этом возвращается в исходное нулевое состояние.

Поскольку на пересчетный блок 3 продолжают поступать импульсы с ключа 2, пересчетный блок вновь начинает заполнухться до тех пор, пока не наступит равенство кодов, записанных в пересчетный блок 3 и счетчик 8. В этот момент сигнал с выхода блока 4 сравнения кодов, пройдя через временной селектор 5, возвращает в нулевое состояние блок 3 и поступает на входы блока 13 сравнения и коммутатора 12. Процесс заполнения и сброса пересчетной схемы повторяется, при этом на выходе временного селектора 5 формируется нониусная последовательность , период повторения которой за счет соответствующего кода в счетчике В равен 0,9 Т. Импульсы нониусной последовательности через коммутатор 12 поступают на вход первого нониусного счетчика 101 При совпа дении фаз опорной (Ту) и нониусной (0,9 Тх) последовательностей срабатывает блок 13 сравнения и,воздействуя на коммутатор 12, подключает импульсы нониусной последовательности ко входу второго нониусного счетчика 10 . Одновременно ,сигнал с вьгхода блока 13 сравнения поступает на формирователь 7 кодов периода, который добавляет в счетчик 8 количество импульсов, соответствующее коду 0,09 TX, в результате

чего код, записанный в счетчике 8, начинает соответствовать коду 0,99 ff

В дальнейшем работа частотомера происходит аналогично. Путем сравнения кодов блока 3 и счетчика 8 на выходе временного селектора 5 формируется нониусная последовательность с периодом 0,99 Ту, импульсы которой поступают на нониусный счетчик Ю до момента совпадения фаз опорной и нониусной последовательностей.

o После этого в счетчик 8 добавляется код, соответствующий 0,009 Т и новая нониусная последовательность коммутируется на вход нониусного счетчика 10.

5

Сравнение опорной и нониусной последовательностей по изменению фазы следования импульсов одной последовательности относительно другой исключает необходимость в фор0мировании строго определенной длительности импульсов одной из последовательностей. Кроме того, использование одного формирователя нониусных последовательностей для всех этапов интерполяции в сочетании с неиз5менным пересчетньм блоком 3 и изменяемым. кодом в счетчике 8, существенно упрощает устройство, значительно уменьшает объем оборудования и приводит к повышению точности из0мерения.

Работа формирователя 7.кодов периода (фиг.2) происходит следующим образом.

В исходном состоянии после подачи

5 сигнала Сброс триггер 23 держит открытым временной селектор 22, триггер 16 держит закрытым временной селектор 14, счетный триггер 15, держит закрытые временной селектор 18,

0 а пересчетный блок 19 (по соответствующему сигналу с коммутатора 12) имеет коэффициент пересчета равный 1. Второй блок 20 имеет коэффициент пересчета 0,9.

5

Первый же импульс измеряемой последовательности, поступившей с временного селектора 9, проходит через временной селектор 22. При этом он перебрасывает триггер 23, запирающий

0 временной селектор 22, и через элемент 21 перебрасывает триггер 16, в результате чего открывается вре;менной селектор 14. Импульс с выхода входного формирователя 6 поступает

5 на счетный триггер, перебрасывает его и начинает формировать на его выходе прямоугольный импульс, равный периоду TX. Этот импульс открывает временной селектор 18, в результате чего на выходе пересчетного блока 20

0 имеются импульсы, поступающие с ключа 2 с общим коэффициентом пересчета 0,9. После поступления через временной селектор 14 следующего импульса с формирователя 6, триггер 15 пере5

брасывается, запирается временной селектор 18, прекращая формирование кодов в счетчике 8, через формирователь 17 короткого импульса перебрасывает триггер 16 и запирает временной селектор 14.

После первого срабатьшания блока 13 сравнения коммутатор 12 меняет свое состояние, обеспечивая изменение коэффициента пересчета блока 19 с 1 до 10, а сам импульс блока 13 сравнения через элемент 21 воздействует на триггер 16 и вновь открывает временной селектор 14. Два очередных импульса формирователя 6 заставляют триггер 15 на длительность периода Т, & гкрыть временной селектор 18, через который импульсы образцово частоты поступают на пересчетные блоки 19 и 20. Поскольку общий коэффициент пересчета теперь равен 0,09, то число импульсов на выходе блока 20 соответствует коду О, 0,09 Т. В дальнейшем схема работает аналогично. Кс1ждое новое срабатывание блока 13 сравнения увеличивает коэффициент пересчета блока 19 в десять раз, благодаря чему блок 19 может быть сформирован из соответствующего количества счетных декад.Работа пересчетного блока 20 (фиг.З) с коэффициентом пересчета 0,9 происходит следующим образом.

В данной схеме элемент 26 задержки осуществляет згщержку импульсов на время, равное примерно половине периода следования импульсов генератора 1 образцовой частоты. Элемент 28 задержки осуществляет задержку импульсов на время, превышающее длительность периода.тех же сигналов. Дешифратор 25 вырабатывает на своем выходе напряжение при насчете декадой 24 девяти импульсов после нулевого состояния. Таким образом, каждые девять импульсов из десяти со входа пересчетно о блока поступают с некоторой задержкой на ее выход, а десятый, импульс не пропускается блоком 27, который запирается сигналом с дешифратора 25.

Таким образом/ введение в цифровой частотомер с нониусной интерполяцией формирователя кодов периода позволяет упростить устройство и приводит к повышению точности измерения.

формула изобретения

1. Цифровой частотомер с нониусной интерполяцией, содержащий последовательно соединенные генератор образцовой частоты, ключ синхронизации, блок пересчета и блок сраэнения, выход которого подключен к первому входу нониусного временного селектора, выход последнего соединей со вторым вхЪдом блока пересчета, с первым входом блока сравнения последовательностей и с первым входом коммутатора, второй вход которого подключен к выходу блока сравнения последовательностей, входной формирователь, выход которого соединен с вторым входом ключа синхронизации, с первым входом основного временного селектора, и с вторым входом блока сравнения последовательностей, запоминающий счетчик, выходы, которого подключены ко вторым входам блока сравнения, основной счетчик, вход которого соединен с выходом основного временного селектора, второй вход которого подключен ко второму входу нониусного временного селектора и к второму выходу блока пересчета, а также п нониусных счетчиков, подключенных к первым выходам коммутатора, отличающийся тем, что, с целью повышения точности в него введен формирователь кодов периода, первый вход которого соединен с выходом входного формирователя, второй его вход подключен к выходу ключа синхронизации, третьи входы - к вторым выходам коммутатора, четвертый вход - к выходу блока сравнения последовательностей, пятый вход - к входу основного счетчика, а выход формирователя кодов периода подключен к входу запоминающего счетчика.

2.Частотомер по п.1, отличающийся тем, что формирователь кодов периода выполнен в виде последовательно соединенных первого дополнительного временного селектора первого триггера, второго дополнительного временного селектора, первого дополнительного блока пересчета и второго дополнительного блока пересчета, последовательно соединенных второго триггера, третьего дополнительного временного селектора, элемента ИЛИ и третьего триггера,

а также формирователя короткого импульса, вход которого соединен с вторым выходом первого триггера, причем выход формирователя короткого импульса подключен к второму входу третьего триггера, выход которого соединен с входом первого дополнительного временного селектора, а элемента ИЛИ подключен к входу второго триггера.

3.Частотомер по п.2, отличающийся тем, что второй дополнительный блок пересчета формирователя кодов периода выполнен в виде последовательно соединенных счетной декады и де1;ифратора, последовательно соединенных первого блока задержки,, блока запрета и второго блока задержки, причем вход счетной декады подключен к входу первого блока задержки, а выход дешифратора соединен с вторым входом блока запрета.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР W468180, кл. G. 01 R 23/10, 11.07.73.

2.Авторское свидетельство СССР 1 365660, кл. G 01 R 25/00, 28.06.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТОМЕР С НОНИУСНОЙ ИНТЕРПОЛЯЦИЕЙ | 1973 |

|

SU365660A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ И ОТНОШЕНИЯ ДВУХ ЧАСТОТ | 1971 |

|

SU294112A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ, ОТНОШЕНИЯ ДВУХ | 1971 |

|

SU300856A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2032182C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2028628C1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2015 |

|

RU2584730C1 |

| ФОРМИРОВАТЕЛЬ МЕТОК ВРЕМЕНИ | 2018 |

|

RU2665283C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ СЕРИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2125736C1 |

| Цифровой частотомер | 1981 |

|

SU970255A1 |

Авторы

Даты

1981-09-30—Публикация

1980-01-21—Подача