А о В о

С оИзобретение относится к электротехнике и может быть использовано в преобразователях частоты с непосредственной связью (НПЧ), предназначенных, например, для частотного управления электроприводами, работающими в широком диапазоне частот вращения. Пель изобретения - улучшение качества выходного напряжения и расширение функциональных возможностей путем расширения диапазона рабочих частот и напряжений, а также независимости режима работы преобразователя от порядка подключения входных зажимов силовой части к фазам питающей сети.

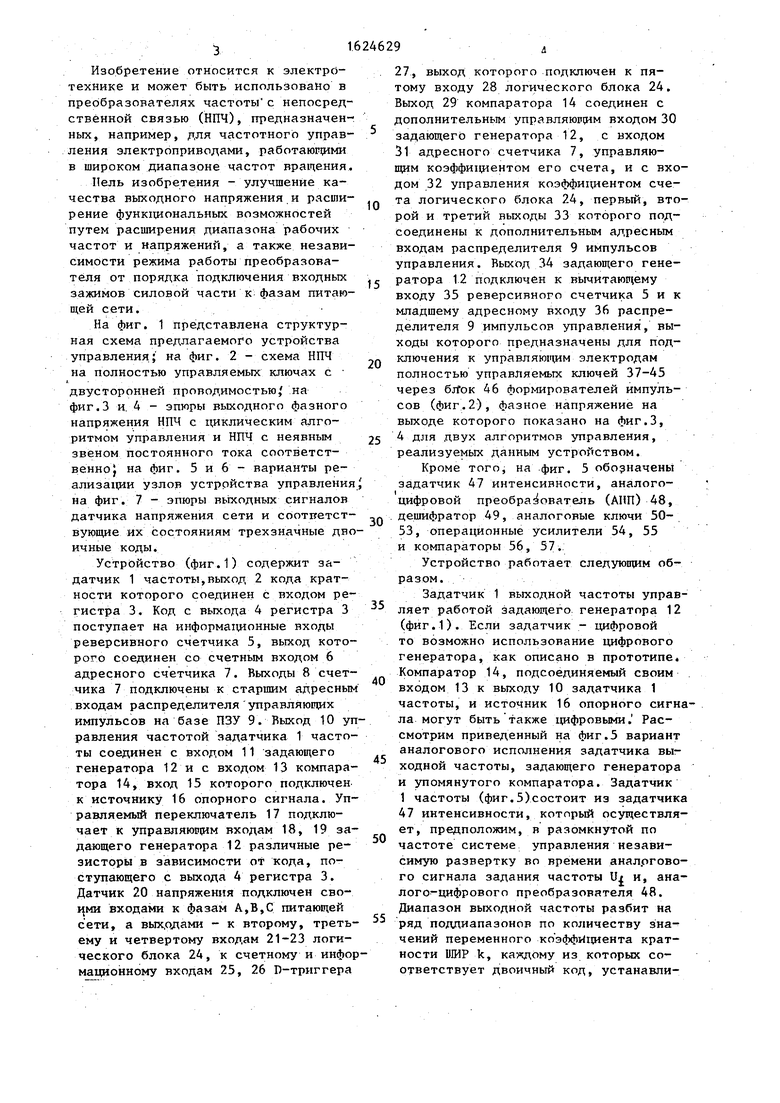

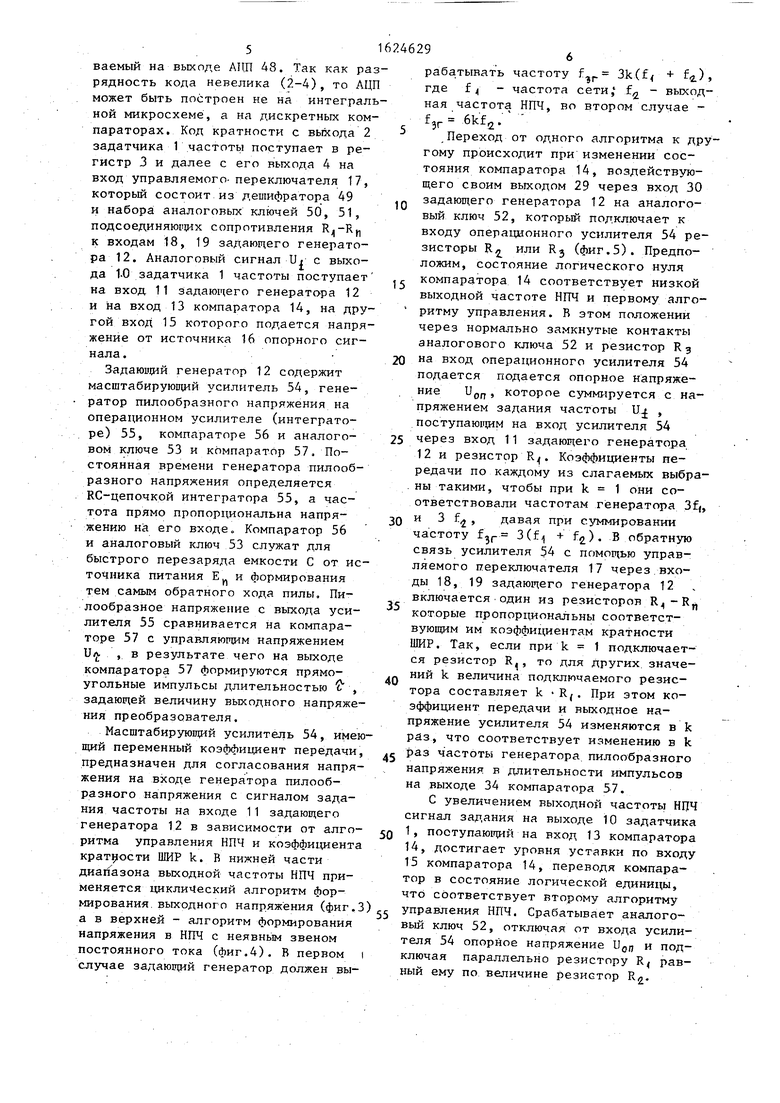

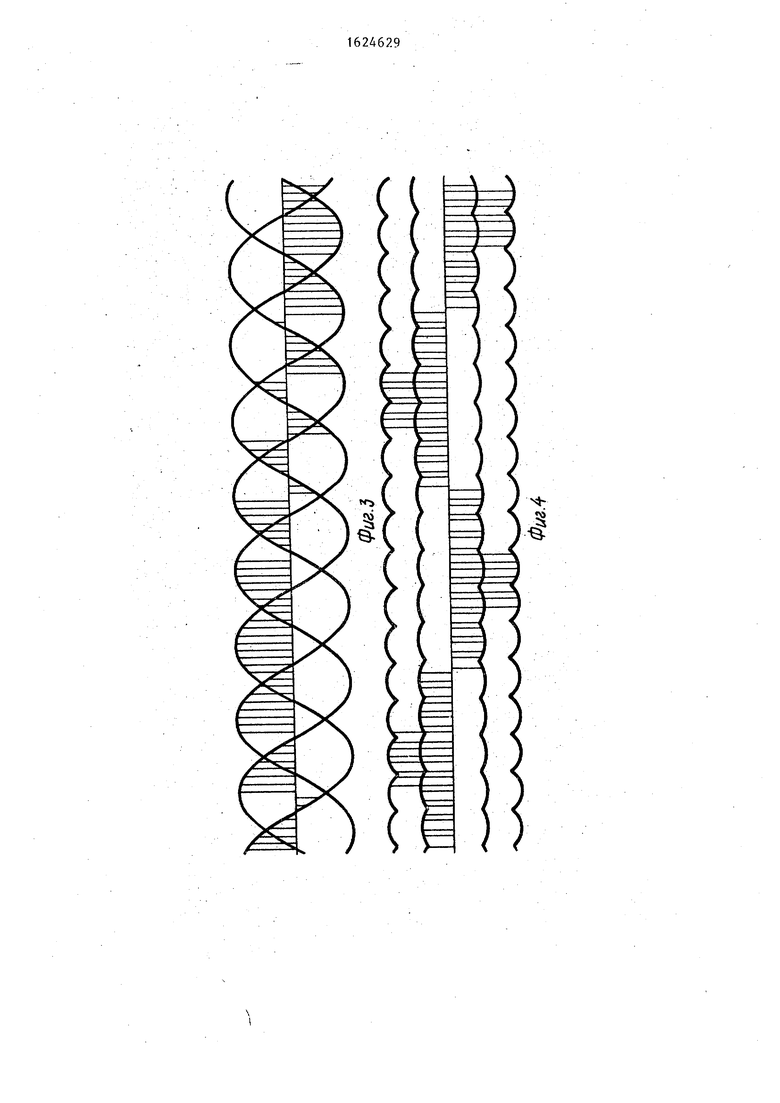

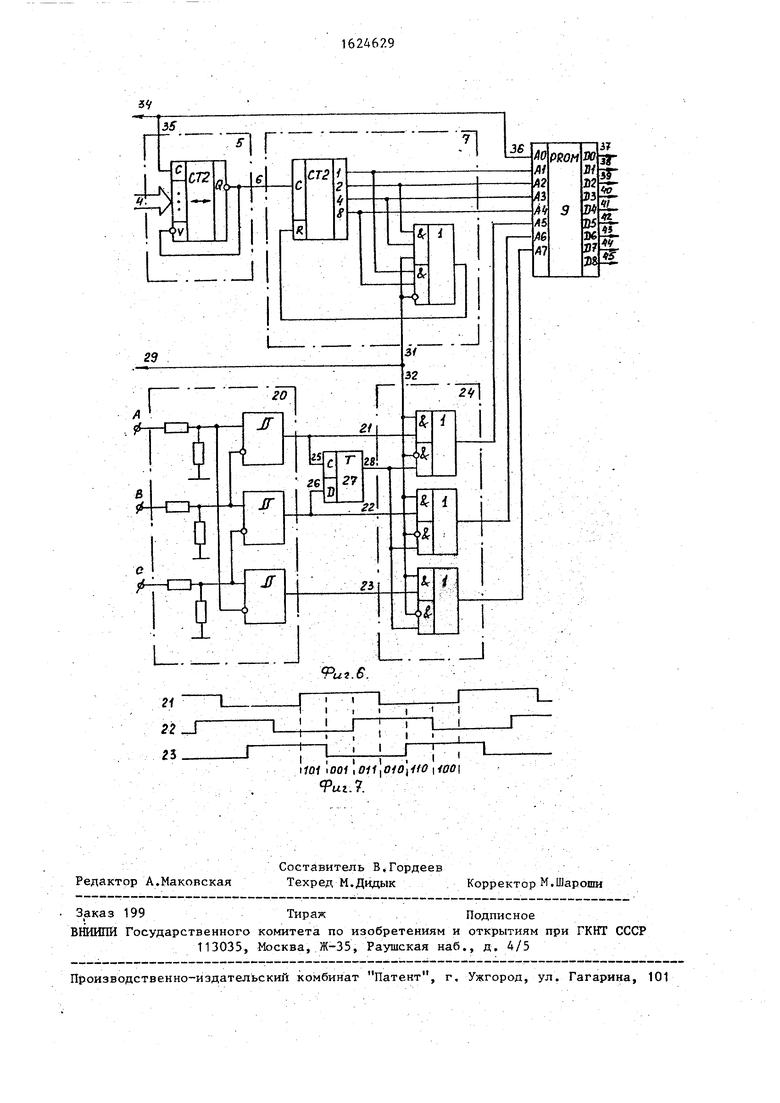

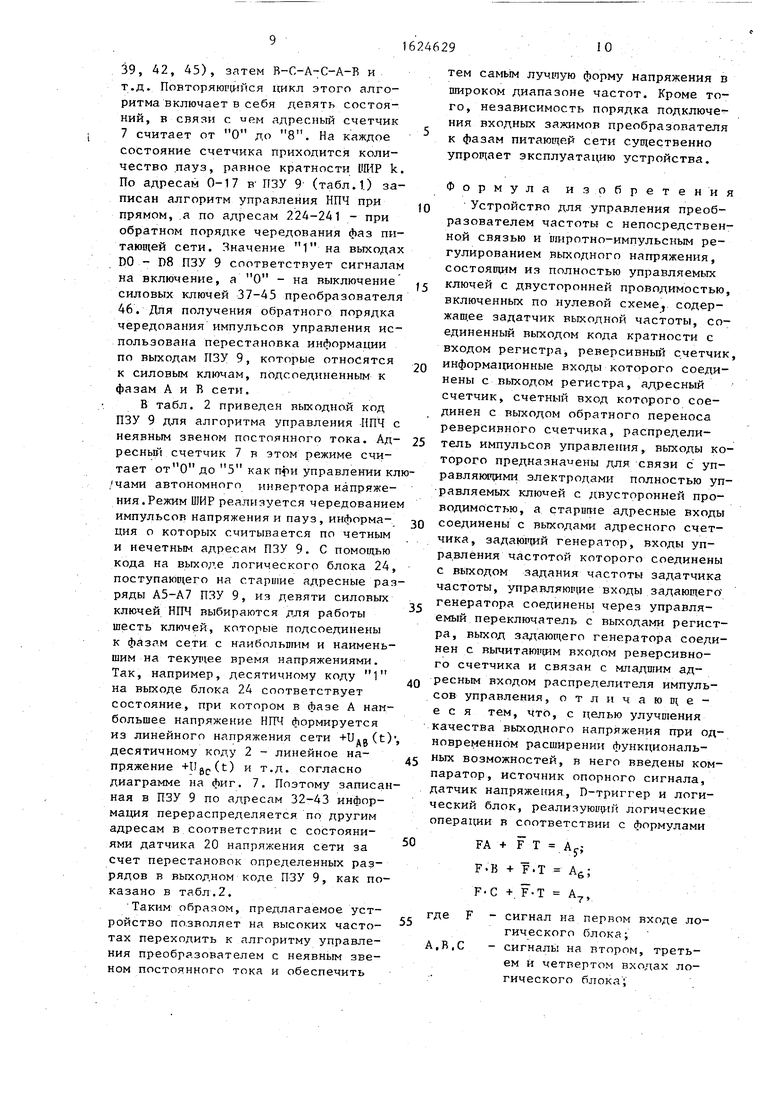

На фиг. 1 представлена структурная схема предлагаемого устройства управления; на фиг. 2 - схема НПЧ на полностью управляемых ключах с двусторонней проводимостью/ на фиг.З и 4 - эпюры выходного фазного напряжения НПЧ с циклическим алгоритмом управления и НПЧ с неявным звеном постоянного тока соответственно} на фиг. 5 и 6 - варианты реализации узлов устройства управления на фиг. 7 - эпюры выходных сигналов датчика напряжения сети и соответствующие их состояниям трехзначные двоичные коды.

Устройство (фиг.1) содержит за- датчик 1 частоты,выход 2 кода кратности которого соединен с входом регистра 3. Код с выхода 4 регистра 3 поступает на информационные входы реверсивного счетчика 5, выход кото- соединен со счетным входом 6 адресного счетчика 7. Выходы 8 счетчика 7 подключены к старшим адресным входам распределителя управляющих импульсов на базе ПЗУ 9. Выход 10 управления частотой задатчика 1 частоты соединен с входом 11 задающего генератора 12 и с входом 13 компаратора 14, вход 15 которого подключен к источнику 16 опорного сигнала. Управляемый переключатель 17 подключает к управляющим входам 18, 19 задающего генератора 12 различные резисторы в зависимости от кода, поступающего с выхода 4 регистра 3. Датчик 20 напряжения подключен своими входами к фазам А,В,С питающей сети, а выходами - к второму, третьему и четвертому входам 21-23 логического блока 24, к счетному и информационному входам 25, 26 D-триггера

5

0

5

0

5

0

5

0

5

27, выход которого подключен к пятому входу 28 логического блока 24. Выход 29 компаратора 14 соединен с дополнительным управляющим входом 30 задающего генератора 12, с входом 31 адресного счетчика 7, управляющим коэффициентом его счета, и с входом 32 управления коэффициентом счета логического блока 24, первый, второй и третий выходы 33 которого подсоединены к дополнительным адресным входам распределителя 9 импульсов управления. Выход 34 задающего генератора 12 подключен к вычитающему входу 35 реверсивного счетчика 5 и к младшему адресному входу 36 распределителя 9 импульсов управления, выходы которого предназначены для подключения к управляющим электродам полностью управляемых ключей 37-45 через блок 46 формирователей импульсов (фиг.2), фазное напряжение на выходе которого показано на фиг.З, 4 для двух алгоритмов управления, реализуемых данным устройством.

Кроме того, на фиг. 5 обозначены задатчик 47 интенсивности, аналого- цифровой преобразователь (АНП) 48, дешифратор 49, аналоговые ключи 50- 53, операционные усилители 54, 55 и компараторы 56, 57.

Устройство работает следующим образом.

Задатчик 1 выходной частоты управляет работой задающего генератора 12 (фиг.1). Если задатчик - цифровой то возможно использование цифрового генератора, как описано в прототипе Компаратор 14, подсоединяемый своим входом 13 к выходу 10 задатчика 1 частоты, и источник 16 опорного сигнала могут быть также цифровыми. Рассмотрим приведенный на фиг.5 вариант аналогового исполнения задатчика выходной частоты, задающего генератора и упомянутого компаратора. Задатчик 1 частоты (фиг.5)состоит из задатчика 47 интенсивности, который осуществляет, предположим, в разомкнутой по частоте системе управления независимую развертку во времени аналргово- го сигнала задания частоты lit и, аналого-цифрового преобразователя 48. Диапазон выходной частоты разбит на ряд поддиапазонов по количеству значений переменного коэффициента кратности ШИР k, каждому из которых соответствует двоичный код, устанавливаемый на выходе АЦП 48. Так как разрядность кода невелика (2-4), то АЦП может быть построен не на интегральной микросхеме, а на дискретных компараторах. Код кратности с выхода 2 задатчика 1 частоты поступает в регистр 3 и далее с его выхода 4 на вход управляемого переключателя 17, который состоит из дешифратора 49 и набора аналоговых ключей 50, 51, подсоединяющих сопротивления к входам 18, 19 задающего генератора 12. Аналоговый сигнал 1Ь с выхода 1-0 задатчика 1 частоты поступает на вход 11 задающего генератора 12 и на вход 13 компаратора 14, на другой вход 15 которого подается напряжение от источника 16 опорного CHI- нала.

Задающий генератор 12 содержит масштабирующий усилитель 54, генератор пилообразного напряжения на операционном усилителе (интеграторе) 55, компараторе 56 и аналоговом ключе 53 и компаратор 57. Постоянная времени генератора пилообразного напряжения определяется RC-цепочкой интегратора 55, а частота прямо пропорциональна напряжению на его входе. Компаратор 56 и аналоговый ключ 53 служат для быстрого перезаряда емкости С от источника питания ЕП и формирования тем самым обратного хода пилы. Пилообразное напряжение с выхода усилителя 55 сравнивается на компараторе 57 с управляющим напряжением U , в результате чего на выходе компаратора 57 формируются прямоугольные импульсы длительностью t , задающей величину выходного напряжения преобразователя.

Масштабирующий усилитель 54, имеющий переменный коэффициент передачи, предназначен для согласования напряжения на входе генератора пилообразного напряжения с сигналом задания частоты на входе 11 задающего генератора 12 в зависимости от алгоритма управления НПЧ и коэффициента кратности ШИР k. В нижней части диапазона выходной частоты НПЧ применяется циклический алгоритм формирования выходного напряжения (фиг.З а в верхней - алгоритм формирования напряжения в НПЧ с неявным звеном постоянного тока (фиг.4). В первом случае задающий генератор должен вырабатывать частоту f ,Р 3k(f + f4) ,

10

15

20

25

0

0

5

0

где f 4 - частота сети,1 f2 - выходная частота НПЧ, во втором случае - fr 6kf2.

Переход от одного алгоритма к другому происходит при изменении состояния компаратора 14, воздействующего своим выходом 29 через вход 30 задающего генератора 12 на аналоговый ключ 52, который подключает к входу операционного усилителя 54 резисторы R или RJ (фиг.5). Предположим, состояние логического нуля компаратора 14 соответствует низкой выходной частоте НПЧ и первому алгоритму управления. В этом положении через нормально замкнутые контакты аналогового ключа 52 и резистор Rg на вход операционного усилителя 54 подается подается опорное напряжение Uon, которое суммируется с напряжением задания частоты U.Ј , поступающим на вход усилителя 54 через вход 11 задающего генератора 12 и резистор R. Коэффициенты передачи по каждому из слагаемых выбраны такими, чтобы при k 1 они соответствовали частотам генератора 3f, и 3 f, давая при суммировании

частоту 3(f + fg). В обратную связь усилителя 54 с помощью управляемого переключателя 17 через входы 18, 19 задающего генератора 12 включается один из резисторов которые пропорциональны соответствующим им коэффициентам кратности ШИР. Так, если при k 1 подключается резистор R., то для других значе5

М

ний k величина подключаемого резистора составляет k R(. При этом коэффициент передачи и выходное напряжение усилителя 54 изменяются в k раз, что соответствует изменению в k раз частоты генератора пилообразного напряжения в длительности импульсов на выходе 34 компаратора 57.

С увеличением выходной частоты НПЧ сигнал задания на выходе 10 задатчика 1, поступающий на вход 13 компаратора 14, достигает уровня уставки по входу 15 компаратора 14, переводя компаратор в состояние логической единицы, что соответствует второму алгоритму управления НПЧ. Срабатывает аналоговый ключ 52, отключая от входа усилителя 54 опорное напряжение Uon и подключая параллельно резистору R равный ему по величине резистор R.

10

15

Из выходного напряжения усилителя 54 устраняется постоянная составляющая, обусловленная действием Vm , a коэффициент передачи сигнала задания частоты увеличивается в два раза, в результате чего на выходе задающего генератора вместо частоты 3kx K(f( +f„)устанавливается частота ЕЗГ 6kfЈ при сохранении прежней скважности импульсов.

Импульсы с выхода 34 генератора 12 поступают на младший разряд АО адресного входа 36 распределителя 9 импульсов управления (в дальнейшем ВЗУ как пример конкретного выполнения) и на вычитающий счетный вход 35 реверсивного счетчика 5 (фиг.6), выполняющего функцию управляемого делителя частоты, коэффициент деления которого записыва-4 ется с выхода 4 регистра 3 кода кратности по сигналу переноса на вход предварительной записи счетчика 5. Сигнал с выхода счетчика 5 частотой поступает на счетный вход ад- 25 ресного счетчика 7 (фиг.6). Сброс адресного счетчика 7 осуществляется по седьмому или десятому счетному импуль- су в зависимости от состояния компаратора 14, выход 29 которого соединен с входом 31 счетчика 7, управляющим коэффициентом его счета. Код с адресного счетчика 7 поступает на разряды Л1-А4 адресных входов ПЗУ 9.

Датчик 20 напряжения сети (фиг.6) состоит из трех компараторов, на входы которых с резистивных делителей подаются линейные напряжения трехфазной системы напряжений. Выходные сигналы 21-23 Датчика 20 представляют собой прямоугольные импульсы типа меандр, сдвинутые один относительно другого на 120 эл.град. На фиг. 7 приведены эти сигналы при прямом порядке чередования фаз, а также трехразрядные двоичные коды, образуемые ими, на каждых 60 эл.град.сетевой частоты. Выходные сигналы датчика напряжения сети не могут все одновременно равняться нулю или единице, т.е. отсутствуют двоичные коды 000 и 111.

Один из выходов датчика 20 (фиг.6) соединен со счетным входом 25, а другой - с информационным входом 26 D- триггера 27. Предположим, триггер

30

45

50

с информационного входа. При прямом порядке чередования фаз сети (фиг.7 D-триггер будет находиться в состоянии логического нуля, а при измене нии порядка чередования на обратный перейдет в состояние логической еди ницы .

Выходные сигналы датчика 20 напряжения сети, триггера 27 и компар тора 14 поступают в логический блок 24, который формирует на своих выхо дах трехразрядный двоичный код, подаваемый на адресные разряды А5-А7 ПЗУ 9 (фиг.6). Если на вход 32 блока 24 с выхода 29 компаратора 14 по ступает логический нуль, задающий циклический алгоритм управления НПЧ с поочередным подключением нагрузки к фазам питающей сети, то десятично -значение кода на выходе логического блока 24 равно О при прямом и 7 при обратном порядке чередования фаз сети. При алгоритме управления НПЧ с неявным знаком постоянного то ка на входе 32 блока 24 устанавливается логическая единица, и тогда выходной код блока 24 принимает десятичные яначения от 1 до 6, п торяя выходной код датчика 20 напря жения сети (фиг.7).

Каждому из двоичных кодов на адрес ных ПЗУ 9 соответствует выходной код ПЗУ 9, определяющий комбинацию вклю ченных силовых ключей НПЧ. Величина выходного напряжения НПЧ, регулиру- емого широтно-импульсным способом, определяется скважностью импульсов задающего генератора, поступающих на младший адресный разряд ПЗУ 9. Например , при четных значениях кода на адресных входах ПЗУ 9 силовые ключи формируют импульсы напряжения, при нечетных - паузы, во время которых все фазы нагрузки подсоединяются к одному и тому же проводу питающей сети.

В табл.1 приведен выходной код ПЗ 9 для циклического алгоритма управле ния НПЧ. С целью усреднения динамиче ских потерь силовых ключей при много кратном ШИР использован циклический сдвиг в чередовании фаз сети, к которым для организации пауз в выходном напряжении одновременно подклюсрабатывает от положительного фронтачаются все фазы нагрузки. Алгоритм

(перепад из нуля в единицу) импуль-подключения может быть следующим:

сов на счетном входе, передавая в этифаза А (ключи 37, 40, 43) - фаза В

моменты на выход триггера информацию(ключи 38, 41, 44) - фаза С (ключи

5

4 5

,

0

5

0

с информационного входа. При прямом порядке чередования фаз сети (фиг.7) D-триггер будет находиться в состоянии логического нуля, а при изменении порядка чередования на обратный перейдет в состояние логической единицы .

Выходные сигналы датчика 20 напряжения сети, триггера 27 и компаратора 14 поступают в логический блок 24, который формирует на своих выходах трехразрядный двоичный код, подаваемый на адресные разряды А5-А7 ПЗУ 9 (фиг.6). Если на вход 32 блока 24 с выхода 29 компаратора 14 поступает логический нуль, задающий циклический алгоритм управления НПЧ с поочередным подключением нагрузки к фазам питающей сети, то десятичное -значение кода на выходе логического блока 24 равно О при прямом и 7 при обратном порядке чередования фаз сети. При алгоритме управления НПЧ с неявным знаком постоянного тока на входе 32 блока 24 устанавливается логическая единица, и тогда выходной код блока 24 принимает десятичные яначения от 1 до 6, повторяя выходной код датчика 20 напряжения сети (фиг.7).

Каждому из двоичных кодов на адресных ПЗУ 9 соответствует выходной код ПЗУ 9, определяющий комбинацию включенных силовых ключей НПЧ. Величина выходного напряжения НПЧ, регулиру- емого широтно-импульсным способом, определяется скважностью импульсов задающего генератора, поступающих на младший адресный разряд ПЗУ 9. Например , при четных значениях кода на адресных входах ПЗУ 9 силовые ключи формируют импульсы напряжения, при нечетных - паузы, во время которых все фазы нагрузки подсоединяются к одному и тому же проводу питающей сети.

В табл.1 приведен выходной код ПЗУ 9 для циклического алгоритма управления НПЧ. С целью усреднения динамических потерь силовых ключей при многократном ШИР использован циклический сдвиг в чередовании фаз сети, к которым для организации пауз в выходном напряжении одновременно подклю

39, 42, 45), затем R-C-A-C-A-B и т.д. Повторяющейся цикл этого алгоритма включает в себя девять состояний, в связи с ем адресный счетчик 7 считает от О до 8. На каждое состояние счетчика приходится количество пауз, равное кратности ШИР k. По адресам 0-17 в- ПЗУ 9 (табл.1) записан алгоритм управления НПЧ при прямом, а по адресам 224-241 - при обратном порядке чередования фаз питающей сети. Значение 1 на выходах DO - D8 ПЗУ 9 соответствует сигналам на включение, а О - на выключение силовых ключей 37-45 преобразователя 46. Для получения обратного порядка чередования импульсов управления использована перестановка информации по выходам ПЗУ 9, которые относятся к силовым ключам, подсоединенным к фазам А и В сети.

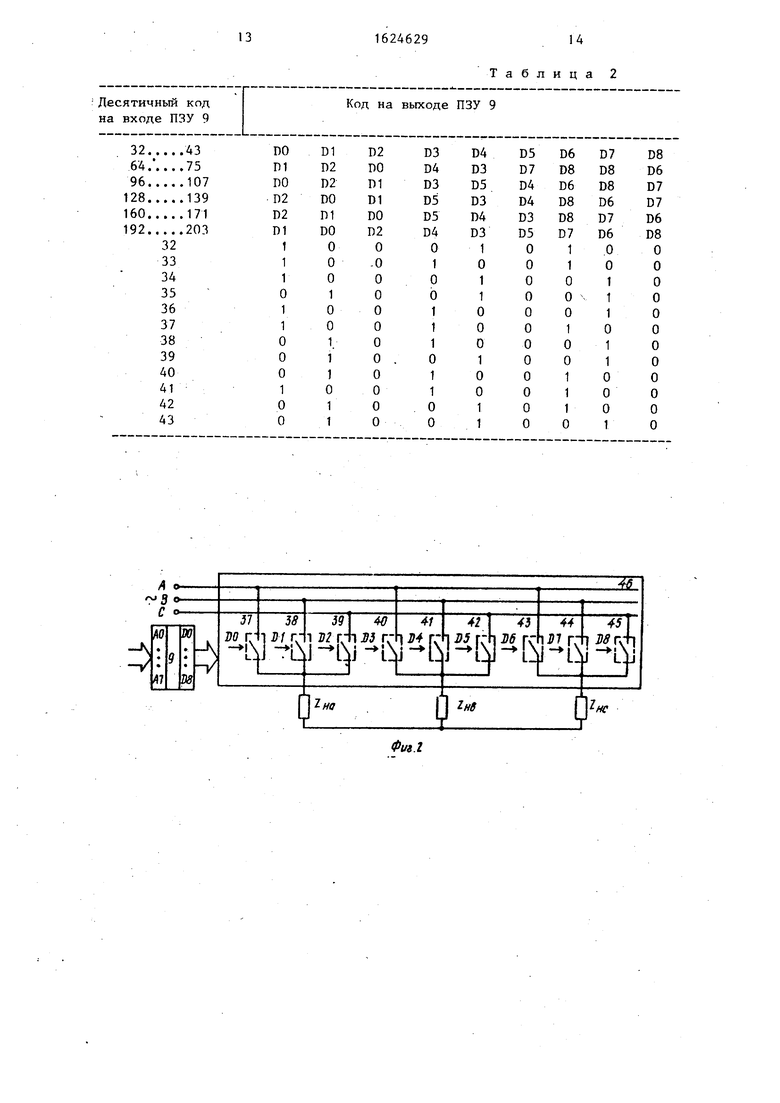

В табл. 2 приведен выходной код ПЗУ 9 для алгоритма управления НПЧ с неявным звеном постоянного тока. Ад- ресный счетчик 7 в этом режиме считает до 5 как управлении кл /чами автономного инвертора напряжения. Режим ШИР реализуется чередованием импульсов напряжения и пауз, информа- ция о которых считывается по четным и нечетным адресам ПЗУ 9. С помощью кода на выходе логического блока 24, поступающего на старите адресные разряды А5-А7 ПЗУ 9, из девяти силовых ключей НПЧ выбираются для работы шесть ключей, которые подсоединены к фазам сети с наибольшим и наименьшим на текущее время напряжениями. Так, например, десятичному коду 1 на выходе блока 24 соответствует состояние, при котором в фазе А наибольшее напряжение НПЧ формируется из линейного напряжения сети (t) десятичному коду 2 - линейное на- пряжение +I &c(t) и т.д. согласно диаграмме на фиг. 7. Поэтому записанная в ПЗУ 9 по адресам 32-43 информация перераспределяется по другим адресам в соответствии с состояниями датчика 20 напряжения сети за счет перестановок определенных разрядов в выходном коде ПЗУ 9, как показано в табл.2.

Таким образом, предлагаемое устройство позволяет на высоких часто тах переходить к алгоритму управления преобразователем с неявным звеном постоянного тока и обеспечить

,-

20

5 .J5

25 ю-о . , 35

50

55

тем самым лучшую форму напряжения в широком диапазоне частот. Кроме того, независимость порядка подключения входных зажимов преобразователя к фазам питающей сети существенно упрощает эксплуатацию устройства.

Формула изобретения

Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием выходного напряжения, состоящим из полностью управляемых ключей с двусторонней проводимостью, включенных по нулевой схеме, содержащее задатчик выходной частоты, соединенный выходом кода кратности с входом регистра, реверсивный счетчик, информационные входы которого соединены с выходом регистра, адресный счетчик, счетный вход которого соединен с выходом обратного переноса реверсивного счетчика, распределитель импульсов управления, выходы которого предназначены для связи с управляющими электродами полностью управляемых ключей с двусторонней проводимостью, а старшие адресные входы соединены с выходами адресного счетчика, задающий генератор, входы управления частотой которого соединены с выходом задания частоты задатчика частоты, управляющие входы задающего генератора соединены через управляемый переключатель с выходами регистра, выход задающего генератора соединен с вычитающим входом реверсивного счетчика и связан с младшим адресным входом распределителя импульсов управления, отличающееся тем, что, с целью улучшения качества выходного напряжения при одновременном расширении функциональных возможностей, в него введены компаратор, источник опорного сигнала, датчик напряжения, D-триггер и логический блок, реализующий логические операции в соответствии с формулами

FA + F Т Af; F-B + F.T А6; F-C + F-T А7,

где F - сигнал на первом входе логического блока;

А.В.С - сигналы на втором, третьем и четвертом входах логического блока;

Т - сигнал на пятом входе лоЧ

гического блока,

А5 А6

Ау - сигналы на первом, втором

и третьем выходах логического блока соответственно, при этом входы датчика по числу фаз питающей сети предназначены для подключения к питающей сети, а выходы соединены с вторым, третьим и четвертым входами логического блока соответственно, второй вход логического блока соединен со счетным входом D-триггера, а третий - с информационным входом П-триггера, выход которого соединен с пятым входом логического

блока, выход компаратора соединен с входом управления коэффициента счета адресного счетчика и первым входом логического блока, выход задания частоты задатчика частоты соединен с первым в-ходом компаратора, второй вход которого соединен с выходом источника опорного сигнала, причем распределитель импульсов управления снабжен дополнительными адресными входами, которые соединены соответственно с выходами логического блока, а задающий генератор снабжен дополнительным управляющим входом, соединенным с выходом компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем частоты с непосредственной связью | 1987 |

|

SU1525840A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1982 |

|

SU1075362A1 |

| Цифровое устройство для управления преобразователем частоты с непосредственной связью и однократной модуляцией | 1983 |

|

SU1164838A1 |

| Устройство для управления непосредственным преобразователем частоты со слежением | 1986 |

|

SU1356149A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1981 |

|

SU997227A1 |

| Трехфазно-трехфазный непосредственный преобразователь частоты | 1985 |

|

SU1292138A1 |

| Непосредственный преобразователь частоты с широтно-импульсным регулированием выходного напряжения | 1980 |

|

SU920992A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1983 |

|

SU1127070A1 |

| Способ регулирования выходного напряжения трехфазно-трехфазного преобразователя частоты с непосредственной связью | 1988 |

|

SU1617574A1 |

| Непосредственный преобразователь частоты с широтно-импульсным регулированием выходного напряжения | 1983 |

|

SU1107249A1 |

Изобретение относится к электротехнике и может быть использовано для управления преобразователями частоты с непосредственной связью. Целью изобретения является улучшение качества выходного напряжения и расширение функциональных возможностей. Введение в устройство датчика 20 напряжения, D-триггера 27, логического блока 24, компаратора 14 и источника 16 опорного сигнала с их связями позволяет управлять преобразователем в нижнем и верхнем диапазонах частот по двум различным алгоритмам с переменными коэффициентами кратности, обеспечивая при этом улучшенную форму напряжения в широком диапазоне регулирования. 2 табл. 7 ил. $ (Я о ьс 4 О to со 8

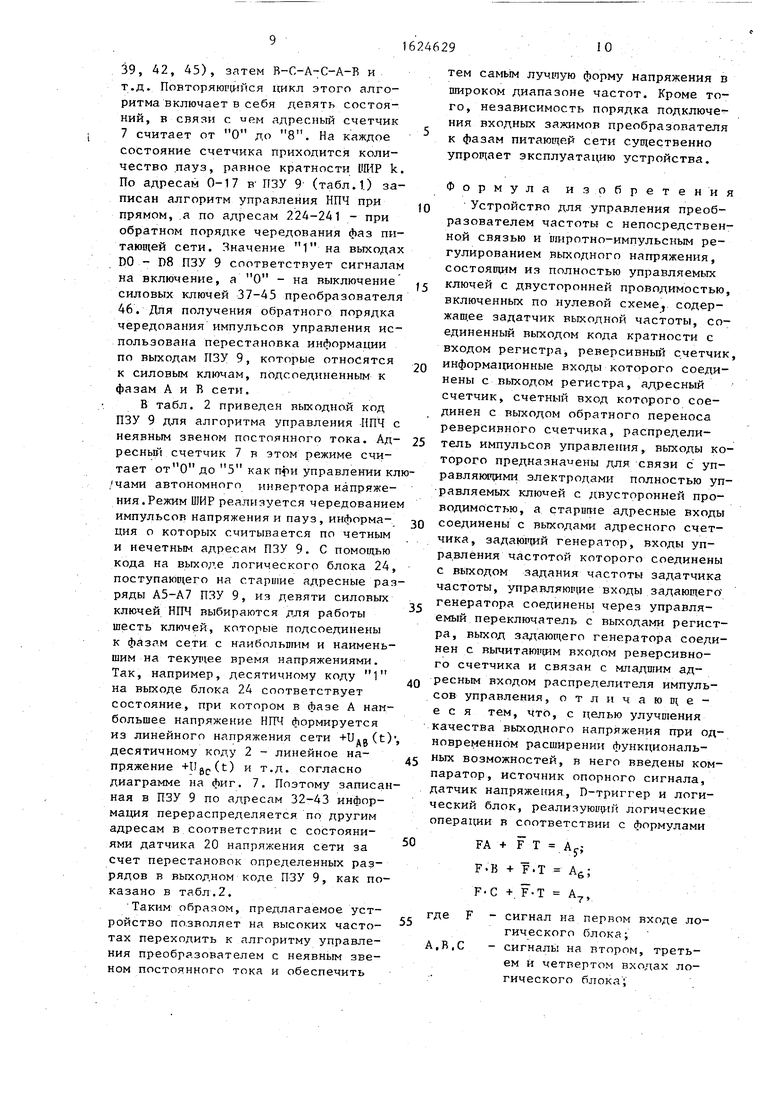

Десятичный код на входе ПЗУ 9

Код на выходе ПЗУ 9

Таблица 1

13

оо37DO Н

Ч

Г.1 Л/ГП 2tf ГП

5 ЛК1

Q

Т-на

Таблица 2

46

-« ГТ Л з Л

1и6

ттсР- лг из

ел

CM

чО

r cs чо

1

faJ

u...

Фиг.6.

| Устройство для управления непосредственным преобразователем частоты | 1983 |

|

SU1164839A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления непосредственным преобразователем частоты со слежением | 1986 |

|

SU1356149A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1983 |

|

SU1140212A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-01-30—Публикация

1989-02-01—Подача