П

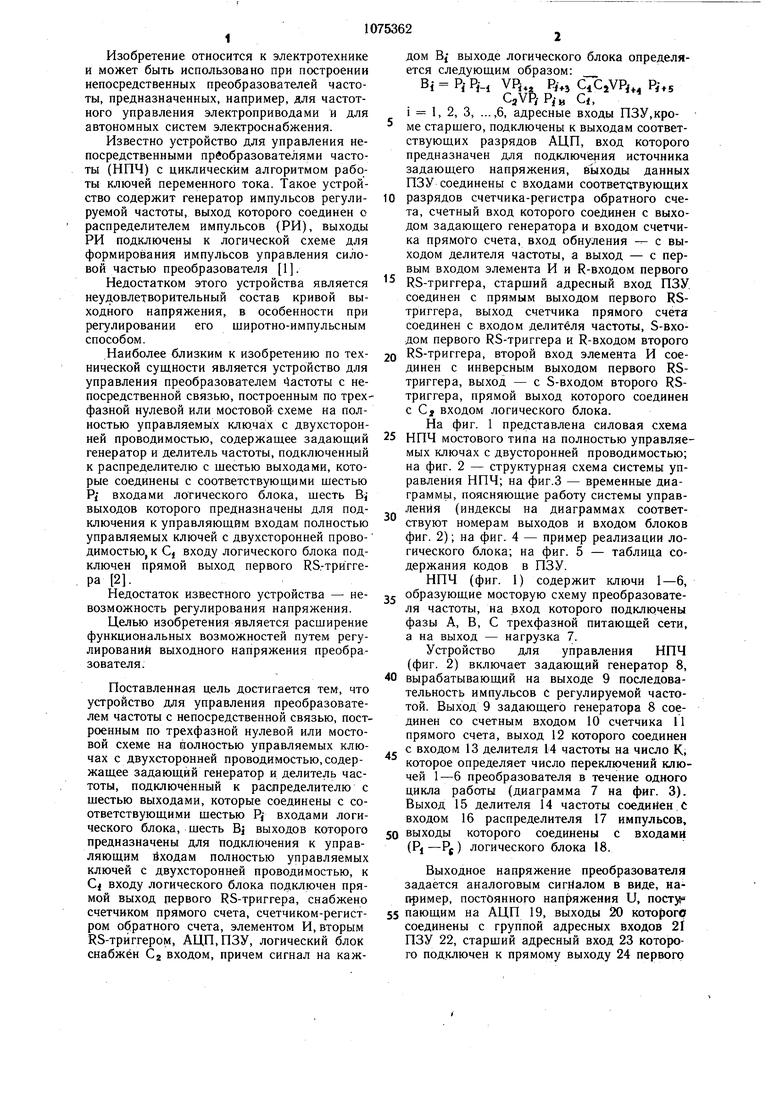

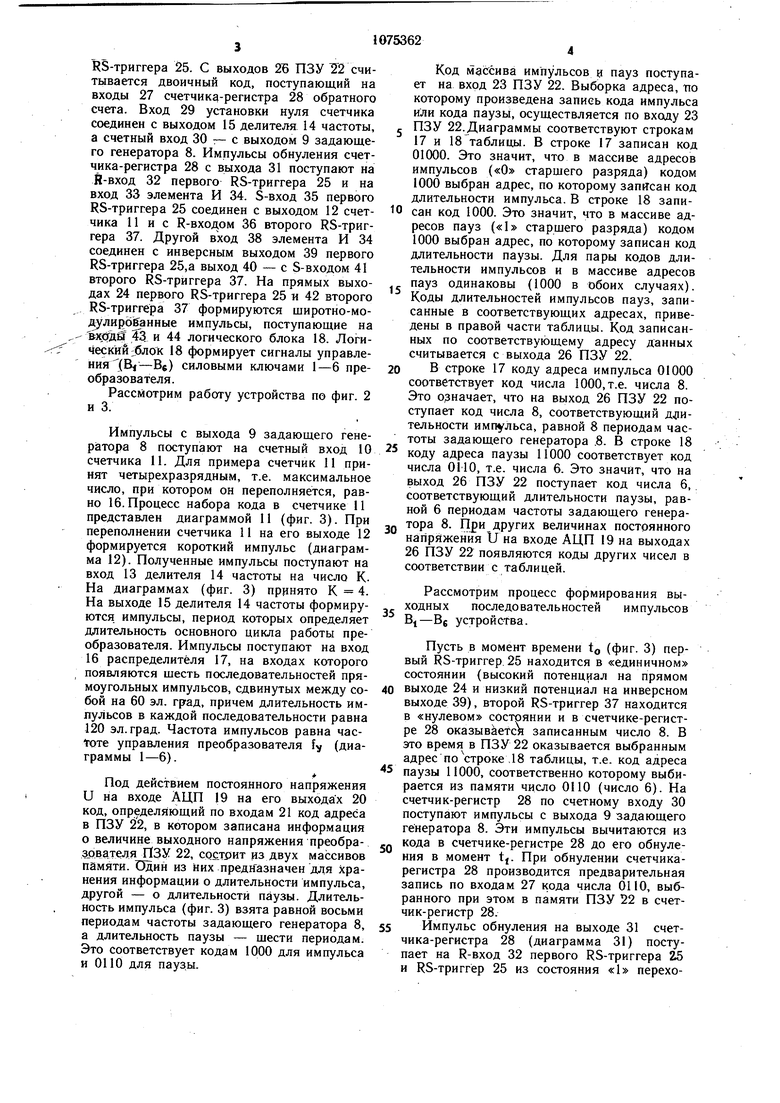

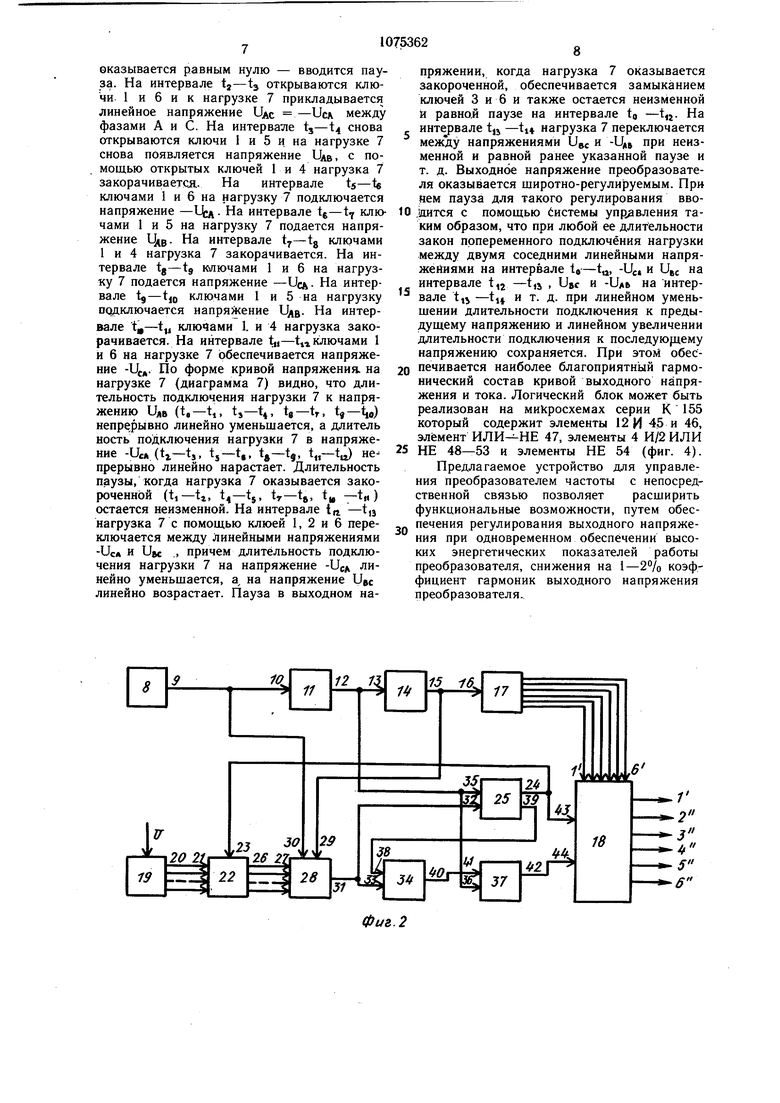

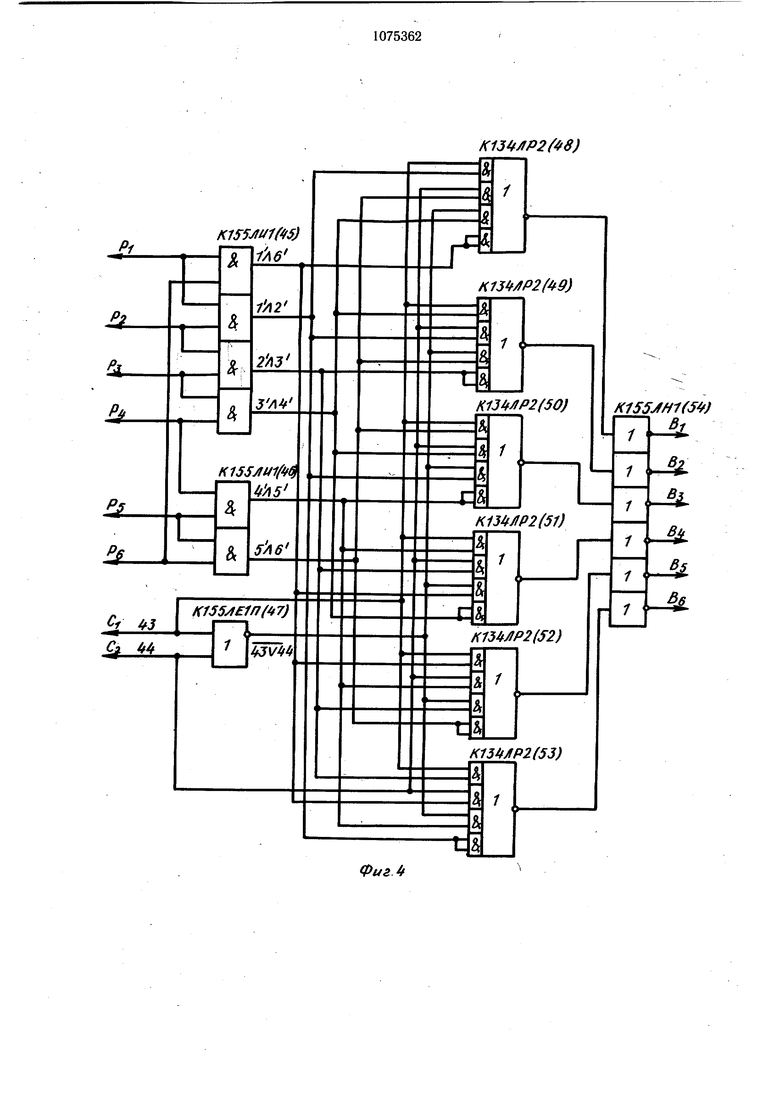

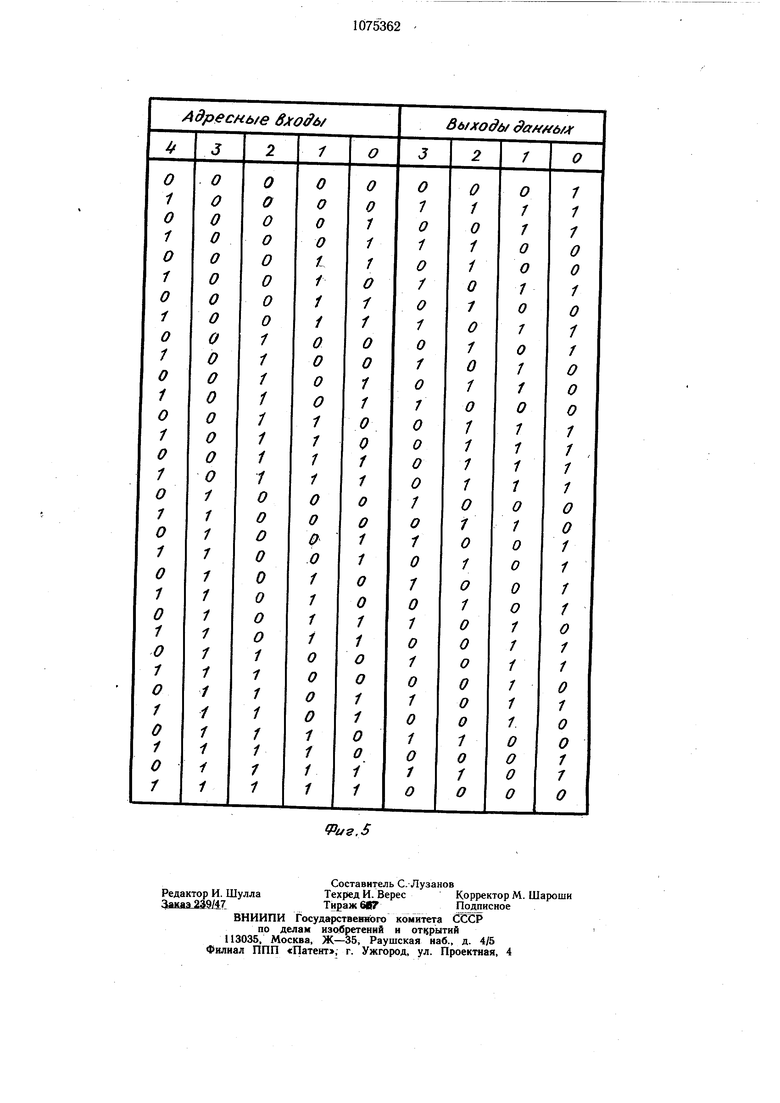

0t/3.f Изобретение относится к электротехнике и может быть использовано при построении непосредственных преобразователей частоты, предназначенных, например, для частотного управления электроприводами и для автономных систем электроснабжения. Известно устройство для управления непосредственными преобразователями частоты (НПЧ) с циклическим алгоритмом работы ключей переменного тока. Такое устройство содержит генератор импульсов регулируемой частоты, выход которого соединен о распределителем импульсов (РИ), выходы РИ подключены к логической схеме для формирования импульсов управления силовой частью преобразователя 1. Недостатком этого устройства является неудовлетворительный состав кривой выходного напряжения, в особенности при регулировании его широтно-импульсным способом. Наиболее близким к изобретению по технической сущности является устройство для управления преобразователем «1астоты с непосредственной связью, построенным по трехфазной нулевой или мостовой схеме на полностью управляемых ключах с двухсторонней проводимостью, содержащее задающий генератор и делитель частоты, подключенный к распределителю с щестью выходами, которые соединены с соответствующими щестью PI входами логического блока, шесть Bi выходов которого предназначены для подключения к управляющим входам полностью управляемых ключей с двухсторонней проводимостью, к Cj входу логического блока подключен прямой выход первого RS-триггера 2. Недостаток известного устройства - невозможность регулирования напряжения. Целью изобретения является расширение функциональных возможностей путем регулирований выходного напряжения преобразователя. Поставленная цель достигается тем, что устройство для управления преобразователем частоты с непосредственной связью, построенным по трехфазной нулевой или мостовой схеме на полностью управляемых ключах с двухсторонней проводимостью, содержащее задающий генератор и делитель частоты, подключённый к распределителю с шестью выходами, которые соединены с соответствующими щестью Pf входами логического блока, щесть Bj выходов которого предназначены для подключения к управляющим йходам полностью управляемых ключей с двухсторонней проводимостью, к GI входу логического блока подключен прямой выход рервого RS-триггера, снабжено счетчиком прямого счета, счетчиком-регистром обратного счета, элементом И, вторым RS-триггером, АЦП, ПЗУ, логический блок снабжён С2 входом, причем сигнал на каждом Bj выходе логического блока определяется следующим образом: Bi PfP,-, Vf,, Р/,5 QCjVPi,, Pi,5 QVFi-Pf С,, i 1, 2, 3, ...,6, адресные входы ПЗУ,кроме старшего, подключены к выходам соответствующих разрядов АЦП, вход которого предназначен для подключения источника задающего напряжения, выходы данных ПЗУ соединены с входами соответствующих разрядов счетчика-регистра обратного счета, счетный вход которого соединен с выходом задающего генератора и входом счетчика прямого счета, вход обнуления --- с выходом делителя частоты, а выход - с первым входом элемента И и R-входом первого RS-триггера, старщий адресный вход ПЗУ. соединен с прямым выходом первого RSтриггера, выход счетчика прямого счета соединен с входом делителя частоты, S-sxoдом первого RS-триггера и R-входом второго RS-триггера, второй вход элемента И соединен с инверсным выходом первого RSтриггера, выход - с S-входом второго RSтриггера, прямой выход которого соединен с Cj входом логического блока. На фиг. 1 представлена силовая схема НПЧ мостового типа на полностью управляемых ключах с двусторонней проводимостью; на фиг. 2 - структурная схема системы управления НПЧ; на фиг.З - временные диаграммь, поясняющие работу системы управления (индексы на диаграммах соответствуют номерам выходов и входом блоков фиг. 2); на фиг. 4 - пример реализации логического блока; на фиг. 5 - таблица содержания кодов в ПЗУ. НПЧ (фиг. I) содержит ключи 1-б, образующие мосторую схему преобразователя частоты, на вход которого подключены фазы А, В, С трехфазной питающей сети, а на выход - нагрузка 7. Устройство для управления НПЧ (фиг. 2) включает задающий генератор 8, вырабатывающий на выходе 9 последовательность импульсов с регулируемой частотой. Выход 9 задающего генератора 8 соединен со счетным входом 10 счетчика 11 прямого счета, выход 12 которого соединен с входом 13 делителя 14 частоты на число К, которое определяет число переключений ключей 1-6 преобразователя в течение одного цикла работы (диаграмма 7 на фиг. 3). Выход 15 делителя 14 частоты соединен.С входом 16 распределителя 17 импульсов, выходы которого соединены с входами (PI-Р() логического блока 18. Выходное напряжение преобразователя задается аналоговым сигналом в виде, например, постоянного напряжения U, nocTjr пающим на АЦП 19, выходы 20 которог У соединены с группой адресных входов 21 ПЗУ 22, старщий адресный вход 23 которого подключен к прямому выходу 24 первого

RS-триггера 25. С выходов 2Б ПЗУ Y2 считывается двоичный код, поступающий на входы 27 счетчика-регистра 28 обратного счета. Вход 29 установки нуля счетчика соединен с выходом 15 делителя 14 частоты, а счетный вход 30 г- с выходом 9 задающего генератора 8. Импульсы обнуления счетчика-регистра 28 с выхода 31 поступают на Н-вход 32 первого RS-триггера 25 и на вход 33 элемента И 34. S-вход 35 первого RS-триггера 25 соединен с выходом 12 счетчика 11 и с R-входом 36 второго RS-триггера 37. Другой вход 38 элемента И 34 соединен с инверсным выходом 39 первого RS-триггера 25,а выход 40 - с S-входом 41 второго RS-триггера 37. На прямых выходах 24 первого RS-триггера 25 и 42 второго RS-триггера 37 формируются щиротно-мо; лироВанные импульсы, поступающие на ЗЗ. и 44 логического блока 18. Логический :блок 18 формирует сигналы управления() силовыми ключами 1-6 преобразователя.

Рассмотрим работу устройства по фиг. 2 и 3.

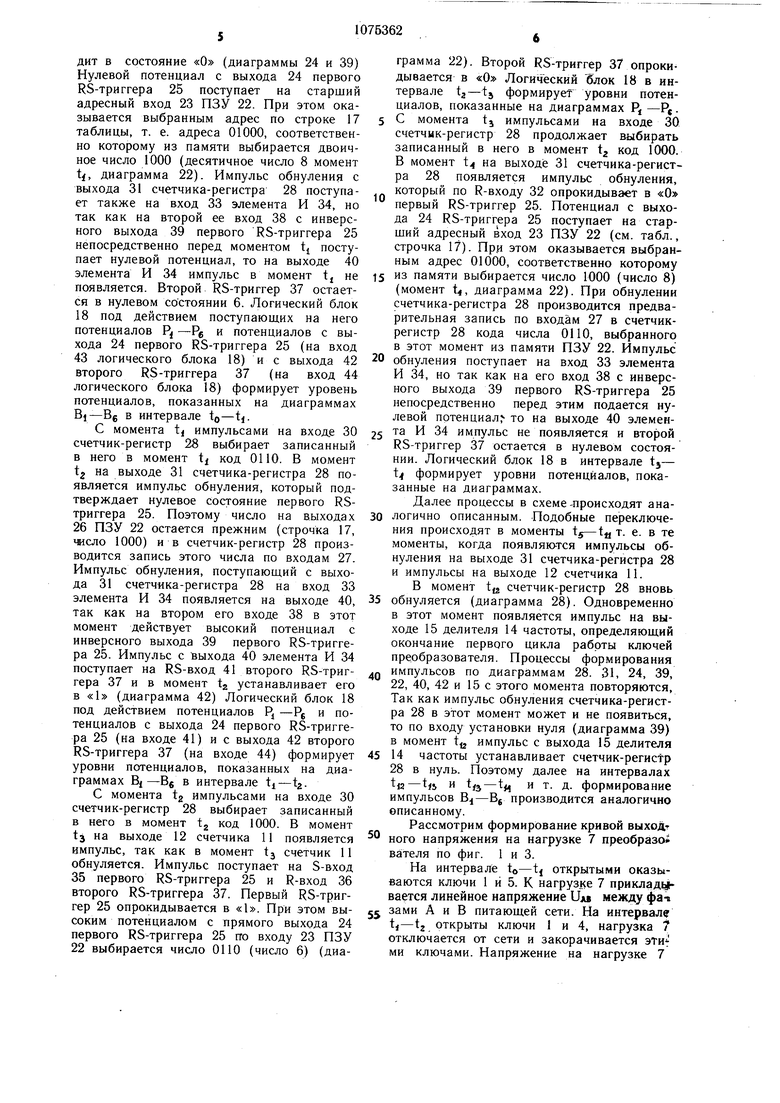

Импульсы с выхода 9 задающего генеpiaTopa 8 поступают на счетный вход 10 счетчика И. Для примера счетчик 11 принят четырехразрядным, т.е. максимальное число, при котором он переполняется, равно 16. Процесс набора кода в счетчике 11 представлен диаграммой 11 (фиг. 3). При переполнении счетчика 11 на его выходе 12 формируется короткий импульс (диаграмма 12). Полученные импульсы поступают на вход 13 делителя 14 частоты на число К. На диаграммах (фиг. 3) принято К 4. На выходе 15 делителя 14 частоты формируются импульсы, период которых определяет длительность основного цикла работы преобразователя. Импульсы поступают на вход 16 распределителя 17, на входах которого появляются шесть последовательностей прямоугольных импульсов, сдвинутых между собой на 60 эл. град, причем длительность импульсов в каждой последовательности равна 120 эл.град. Частота импульсов равна частоте управления преобразователя fv (диаграммы 1-6).

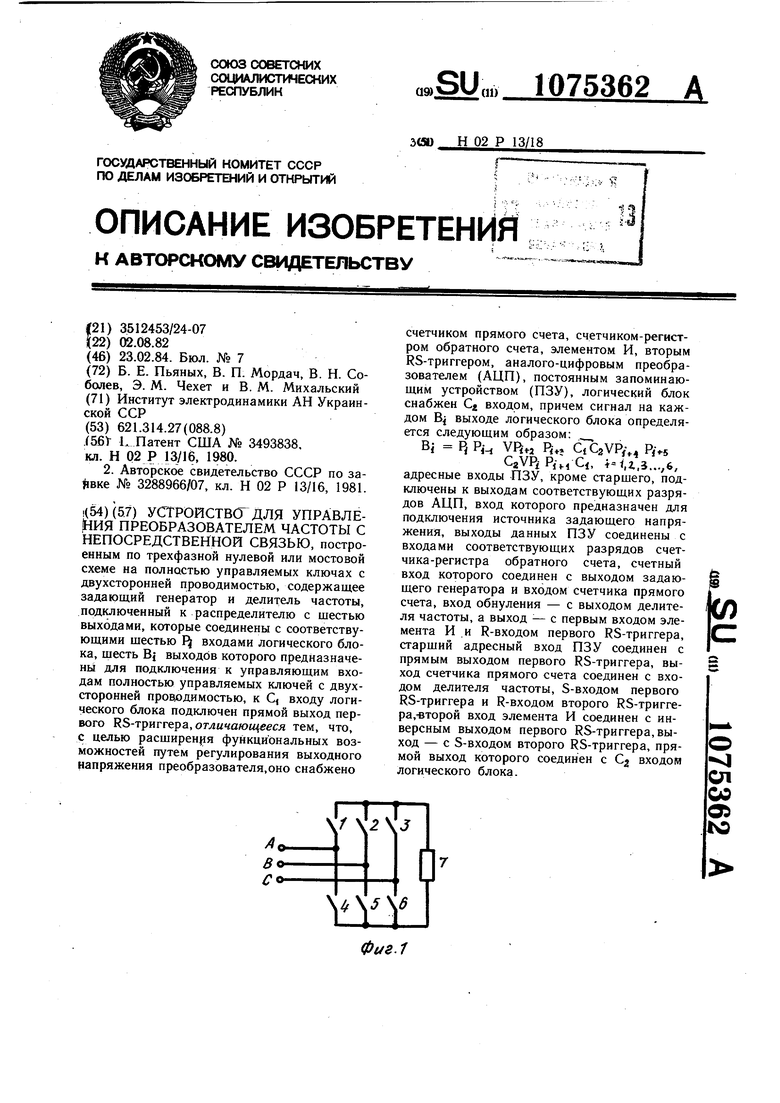

Под действием постоянного напряжения и на входе А ЦП 19 на его выходах 20 код, определяющий по входам 21 код адреса в ПЗУ 22, в котором записана информация о величине выходного напряжения преобра3 ователя ПЗУ 22, из двух массивов памяти. Один из Них предназначен хранения информации о длительности импульса, другой - о длительности паузы. Длительность импульса (фиг. 3) взята равной восьми периодам частоты задающего генератора 8, а длительность паузы - щести периодам. Это соответствует кодам 1000 для импульса и ОНО для паузы.

Код массива импульсов и пауз поступает на вход 23 ПЗУ 22. Выборка адреса, по которому произведена запись кода импульса или кода паузьь осуществляется по вхдау 23 J ПЗУ 22.Диаграммы соответствуют строкам 17 и 18 таблицы. В строке 17 записан код 01000. Это значит, что в массиве адресов импульсов («О старщего разряда) кодом 1000 выбран адрес, по которому записан код длительности импульса. В строке 18 запи0 сан код 1000. Это значит, что в массиве адресов пауз («I старщего разряда) кодом 1000 выбран адрес, по которому записан код длительности паузы. Для пары кодов длительности импульсов и в массиве адресов пауз одинаковы (1000 в обоих случаях). Коды длительностей импульсов пауз, записанные в соответствующих адресах, приведены в правой части таблицы. Код записанных по соответствующему адресу данных считывается с выхода 26 ПЗУ 22.

0 В строке 17 коду адреса импульса 01000 соответствует код числа 1000, т.е. числа 8. Это означает, что на выход 26 ПЗУ 22 поступает код числа 8, соответствующий длительности импульса, равной 8 периодам частоты задающего генератора .8. В строке 18

коду адреса паузы 11000 соответствует код числа 0110, т.е. числа 6. Это значит, что на выход 26 ПЗУ 22 поступает код числа 6, соответствующий длительности паузы, равной 6 периодам частоты задающего генераQ тора 8. При других величинах постоянного напряжения U на входе АЦП 19 на выходах 26 ПЗУ 22 появляются коды других чисел в соответствии с таблицей.

Рассмотрим процесс формирования выходных последовательностей импульсов BI-Bg устройства.

Пусть в момент времени t, (фиг. 3) первый RS-триггер. 25 находится в «единичном состоянии (высокий потенциал на прямом

0 выходе 24 и низкий потенциал на инверсном выходе 39), второй RS-триггер 37 находится в «нулевом состоянии и в счетчике-регистре 28 оказывается записанным число 8. В это время в ПЗУ 22 оказывается выбранным адрес подстроке ,18 таблицы, т.е. код адреса

5 паузы 11000, соответственно которому выбирается из памяти число ОНО (число 6). На счетчик-регистр 28 по счетному входу 30 поступают импульсы с выхода 9 задающего генератора 8. Эти импульсы вычитаются из

Q кода в счетчике-регистре 28 до его обнуления в момент t|. При обнулении счетчикарегистра 28 производится предварительная запись по входам 27 кода числа ОНО, выбранного при этом в памяти ПЗУ 22 в счетчик-регистр 28.

5 Импульс обнуления на выходе 31 счетчика-регистра 28 (диаграмма 31) поступает на R-вход 32 первого RS-триггера 2.5 и RS-триггер 25 из состояния «1 переходит в состояние «О (диаграммы 24 и 39) Нулевой потенциал с выхода 24 первого RS-триггера 25 поступает на старший адресный вход 23 ПЗУ 22. При этом оказывается выбранным адрес по строке 17 таблицы, т. е. адреса 01000, соответственно которому из памяти выбирается двоичное число 1000 (десятичное число 8 момент tf, диаграмма 22). Импульс обнуления с выхода 31 счетчика-регистра 28 поступает также на вход 33 элемента И 34, но так как на второй ее вход 38 с инверсного выхода 39 первого RS-триггера 25 непосредственно перед моментом tj поступает нулевой потенциал, то на выходе 40 элемента И 34 импульс в момент tj не появляется. Второй RS-триггер 37 остается в нулевом состоянии 6. Логический блок 18 под действием поступающих на него потенциалов Р -Pg и потенциалов с выхода 24 первого RS-триггера 25 (на вход 43 логического блока 18) и с выхода 42 второго RS-триггера 37 (на вход 44 логического блока 18) формирует уровень потенциалов, показанных на диаграммах в интервале to-t.

С момента tj импульсами на входе 30 счетчик-регистр 28 выбирает записанный в него в момент t код ОНО. В момент t на выходе 31 счетчика-регистра 28 появляется импульс обнуления, который подтверждает нулевое состояние первого RSтриггера 25. Поэтому число на выходах 26 ПЗУ 22 остается прежним (строчка 17, число 1000) ив счетчик-регистр 28 производится запись этого числа по входам 27. Импульс обнуления, поступающий с выхода 31 счетчика-регистра 28 на вход 33 элемента И 34 появляется на выходе 40, так как на втором его входе 38 в этот момент действует высокий потенциал с инверсного выхода 39 первого RS-триггера 25. Импульс с выхода 40 элемента И 34 поступает на RS-вход 41 второго RS-триггера 37 и в момент tg устанавливает его в «1 (диаграмма 42) Логический блок 18 под действием потенциалов P -Pj и потенциалов с выхода 24 первого RS-триггера 25 (на входе 41) и с выхода 42 второго RS-триггера 37 (на входе 44) формирует уровни потенциалов, показанных на диаграммах Bj-Bf в интервале ti-i.

С момента tg импульсами на входе 30 счетчик-регистр 28 выбирает записанный в него в момент t код 1000. В момент tj на выходе 12 счетчика 11 появляется импульс, так как в момент t счетчик 11 обнуляется. Импульс поступает на S-вход 35 первого RS-триггера 25 и R-вход 36 второго RS-триггера 37. Первый RS-триггер 25 опрокидывается в «1. При этом высоким потенциалом с прямого выхода 24 первого RS-триггера 25 гго входу 23 ПЗУ 22 выбирается число ОНО (число 6) (диаграмма 22). Второй RS-триггер 37 опрокидывается в «О Логический Ълок 18 в интервале tj-tj формирует уровни потенциалов, показанные на диаграммах Р -Р,.

С момента tj импульсами на входе 30 счетчик-регистр 28 продолжает выбирать записанный в него в момент t код 1000. В момент t на выходе 31 счетчика-регистра 28 появляется импульс обнуления, который по R-входу 32 опрокидывает в «О первый RS-триггер 25. Потенциал с выхода 24 RS-триггера 25 поступает на старщий адресный вход 23 ПЗУ 22 (см. табл., строчка 17). При этом оказывается выбранным адрес 01000, соответственно которому

5 из памяти выбирается число 1000 (число 8) (момент t, диаграмма 22). При обнулении счетчика-регистра 28 производится предварительная запись по входам 27 в счетчикрегистр 28 кода числа ОНО, выбранного в этот момент из памяти ПЗУ 22. Импульс

0 обнуления поступает на вход 33 элемента И 34, но так как на его вход 38 с инверсного выхода 39 первого RS-триггера 25 непосредственно перед этим подается нулевой пoтeнциaл то на выходе 40 элемен5 та И 34 импульс не появляется и второй RS-триггер 37 остается в нулевом состоянии. Логический блок 18 в интервале tj- i формирует уровни потенциалов, показанные на диаграммах.

Далее процессы в схеме-происходят ана0 логично описанным. Подобные переключения происходят в моменты т. е. в те моменты, когда появляются импульсы обнуления на выходе 31 счетчика-регистра 28 и импульсы на выходе 12 счетчика 11. В момент t(j счетчик-регистр 28 вновь

обнуляется (диаграмма 28). Одновременно в этот момент появляется импульс на выходе 15 делителя 14 частоты, определяющий окончание первого цикла работы ключей преобразователя. Процессы формирования

Q импульсов по диаграммам 28. 31, 24, 39, 22, 40, 42 и 15с этого момента повторяются, Так как импульс обнуления счетчика-регистра 28 в этот момент может и не появиться, то по входу установки нуля (диаграмма 39) в момент импульс с выхода 15 делителя

5 14 частоты устанавливает счетчик-регисТр 28 в нуль. Поэтому далее на интервалах tj2-tj5 и tjtj-t и т. д. формирование импульсов B.J-Bj производится аналогично описанному.

Рассмотрим формирование кривой выходг

кого напряжения на нагрузке 7 преобразо вателя по фиг. 1 и 3.

На интервале to-tj открытыми оказываются ключи 1 и 5. К нагрузке 7 прикладывается линейное напряжение UAB между фа-в

J зами А и В питающей сети. На интервал 1-tj открыты ключи 1 и 4, нагрузка 7 отключается от сети и закорачивается эти ми ключами. Напряжение на нагрузке 7

оказывается равным нулю - вводится пауза. На интервале открываются ключи 1 и 6 и к нагрузке 7 прикладывается линейное напряжение UAC -UCA между фазами А и С. На интервале t,-14 снова открываются ключи 1 и 5 и на нагрузке 7 снова появляется напряжение UAB, с помощью открытых ключей 1 и 4 нагрузка 7 закорачивается. На интервале ts-1« ключами 1 и 6 на нагрузку 7 подключается напряжение -Ц. На интервале tj-ty ключами 1 и 5 на нагрузку 7 подается напряжение 14в. На интервале ключами 1 и 4 нагрузка 7 закорачивается. На интервале tg-tj ключами 1 и 6 на нагрузку 7 подается напряжение -Uc. На интервале tg-tjo ключами 1 и 5 на нагрузку подключается напряжение Удв. На интервале t,-t,, ключами 1. и 4 нагрузка закорачивается. На интервале t,,-trt ключами 1 и б на нагрузке 7 обеспечивается напряжение -Ue. По форме кривой напряжения, на нагрузке 7 (диаграмма 7) видно, что длительность подключения нагрузки 7 к напряжению UAB (t,-ti, tj-tj, tg-tr, t,-t,e) непре,рывно линейно уменьшается, a длитель ность подключения нагрузки 7 в напряжение -U«(ti-tj, tj-t,, , t«-t) не прерывно линейно нарастает. Длительность паузы, когда нагрузка 7 оказывается закороченной (ti-tj, , tr-tj, ty -1« ) остается неизменной. На интервале in. -1,3 нагрузка 7с помощью клюей 1, 2 и 6 переключается между линейными напряжениями -UcA и UK ., причем длительность подключения нагрузки 7 на напряжение -Ue линейно уменьшается, а, на напряжение Ujc линейно возрастает. Пауза в выходном напряжении, когда нагрузка 7 оказывается закороченной, обеспечивается замыканием ключей 3 и 6 и также остается неизменной и равно.й паузе на интервале to -t,j. На интервале tjj -ti нагрузка 7 переключается между напряжениями Uee и -U, при неизменной и равной ранее указанной паузе и т. д. Выходное напряжение преобразователя оказывается щиротно-регулируемым. При нем пауза для такого регулирования вво.дится с помощью бистемы управления таким образом, что при любой ее длительности закон попеременного подключения нагрузки между двумя соседними линейными напряжениями на интервале t,-t, -U, и U на интервале t,, -tis , UBC и -UAU на интервале t,j -tjt и т. д. при линейном уменьшении длительности подключения к предыдущему напряжению и линейном увеличении длительности подключения к последую цему напряжению сохраняется. При этом обеспечивается наиболее благоприятный гармонический состав кривой выходного напряжения и тока. Логический блок может быть реализован на микросхемах серии К 155 который содержит элементы 12 И 45 и 46, элемент 47, элементы 4 И/2 ИЛИ

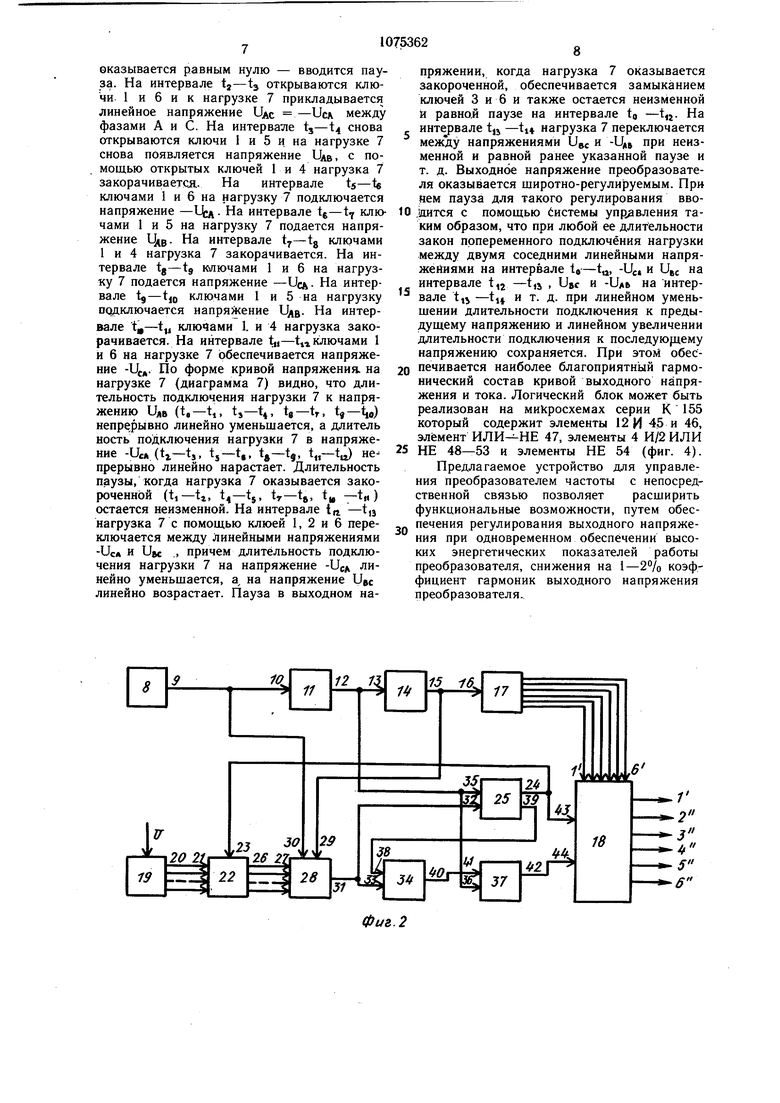

НЕ 48-53 и элементы НЕ 54 (фиг. 4). Предлагаемое устройство для управления преобразователем частоты с непосредственной связью позволяет расширить функциональные возможности, путем обеспечения регулирования выходного напряжения при одновременном обеспечении высоких энергетических показателей работы преобразователя, снижения на 1-2% коэффициент гармоник выходного напряжения преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Цифровое устройство для управления преобразователем частоты с непосредственной связью и однократной модуляцией | 1983 |

|

SU1164838A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1983 |

|

SU1127070A1 |

| СПОСОБ ВЫКЛЮЧЕНИЯ ЖИДКОСТНЫХ РАКЕТНЫХ ДВИГАТЕЛЕЙ СОСТАВНОЙ РАКЕТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2079690C1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Аналого цифровой преобразователь | 1987 |

|

SU1550622A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

.; -р

3 4 S

6

K13 /lP2f48)

Фиг

Авторы

Даты

1984-02-23—Публикация

1982-08-02—Подача