(21) (22) (46 (71) (72)

4606971/09

21.11.88

07.03.91. Б юл. Л1Ь 9

Грузинский политехнический институт

Н. Г. Харатишвили, Т. А. Векча, М. III. Котия, Б. Г. Гвинджи.чия и Ф. Д. Кобахидзе

(53)621.397(088.8)

(56)Авторское свидетельство СССР Л ь 1104690, кл. Н 04 7/18, 1982.

(54)УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННОГО СИГНАЛА С ПО- МОШЬЮ ДИФФЕРЕНЦИАЛЬНОЙ ИМцу;1ьсно-к()довой МОДУЛЯЦИИ

(57)Ишорек ние ошосится к средствам связи и может быть использовано при построении цифровых цветных телевизионных и видеотелефонных систем. Цель изобретения - повышение помехоустойчивости. Устр-во содержит передающую и приемную стороны. Вследствие того, что в устр-ве дифференциальной импульсно-кодовой модуляции (ДИКМ) по каналу связи передается разностный сигнал, ошибка в одном элементе изображения, возникающая из-за помех или искажений, распространяется при восстановлении видеосигнала на приемной стороне на соседние с ним элементы изображения, образуя на изображении так называемые треки ошибки. Устранение такого рода искажений осуществляется в устр-ве путем обнаружения, локализации и коррекции канальных ошибок на основе использования особенностей процесса ДИКМ, что обеспечивает повышение помехоустойчивости устр- ва. 3 ил.

5S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией | 1987 |

|

SU1434563A1 |

| Система передачи и приема телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1982 |

|

SU1104690A1 |

| Система передачи телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1983 |

|

SU1107342A2 |

| Система передачи телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1981 |

|

SU987854A2 |

| Система передачи телевизионногоСигНАлА | 1979 |

|

SU794774A1 |

| Устройство передачи телевизионного сигнала | 1988 |

|

SU1570028A1 |

| Система передачи телевизионного сигнала | 1982 |

|

SU1104691A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ВИДЕОСИГНАЛА, ПРЕДСТАВЛЯЮЩЕГО ИЗОБРАЖЕНИЯ, ПРИЕМНИК ТЕЛЕВИЗИОННОГО СИГНАЛА, ВКЛЮЧАЮЩЕГО ДАННЫЕ ЗАГОЛОВКОВ И ПОЛЕЗНЫЕ ДАННЫЕ В ВИДЕ СЖАТЫХ ВИДЕОДАННЫХ | 1992 |

|

RU2128405C1 |

| Система передачи телевизионного сигнала | 1984 |

|

SU1241528A1 |

| Система передачи телевизионного сигнала | 1985 |

|

SU1277429A2 |

Изобретение относится к средствам связи и может быть использовано при построении цифровых цветных телевизионных (ТВ) и видеотелефонных систем

Целью изобретения является повышение помехоустойчивое ги.

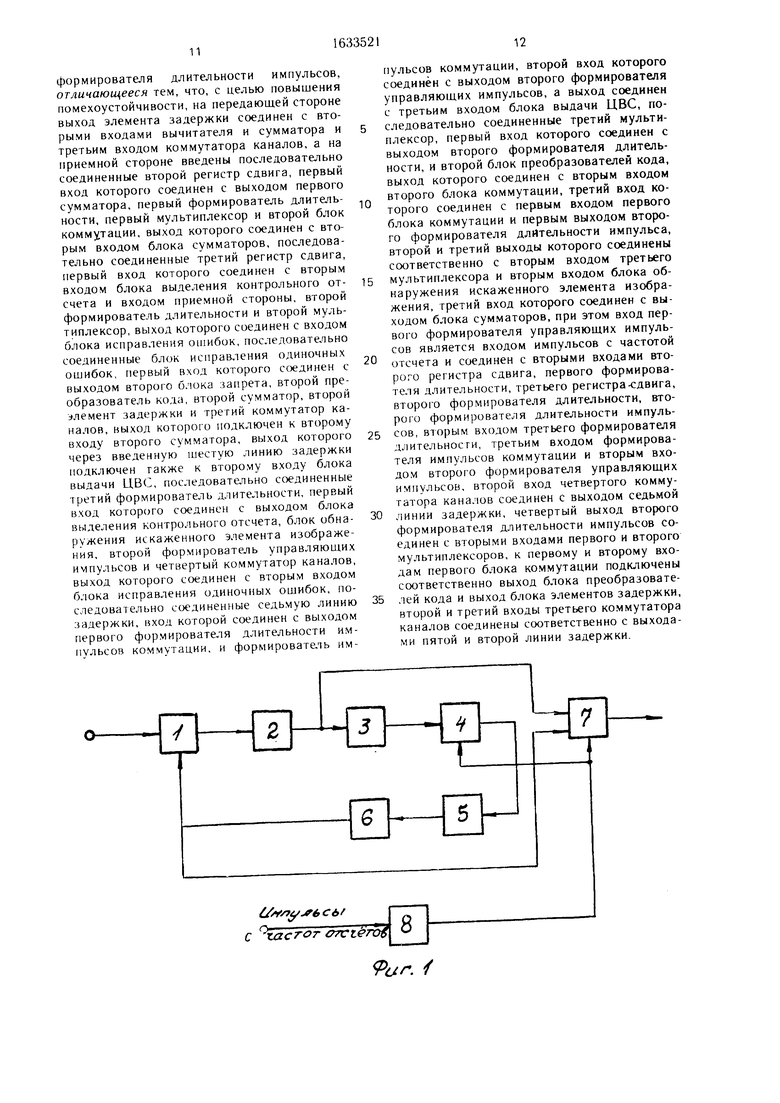

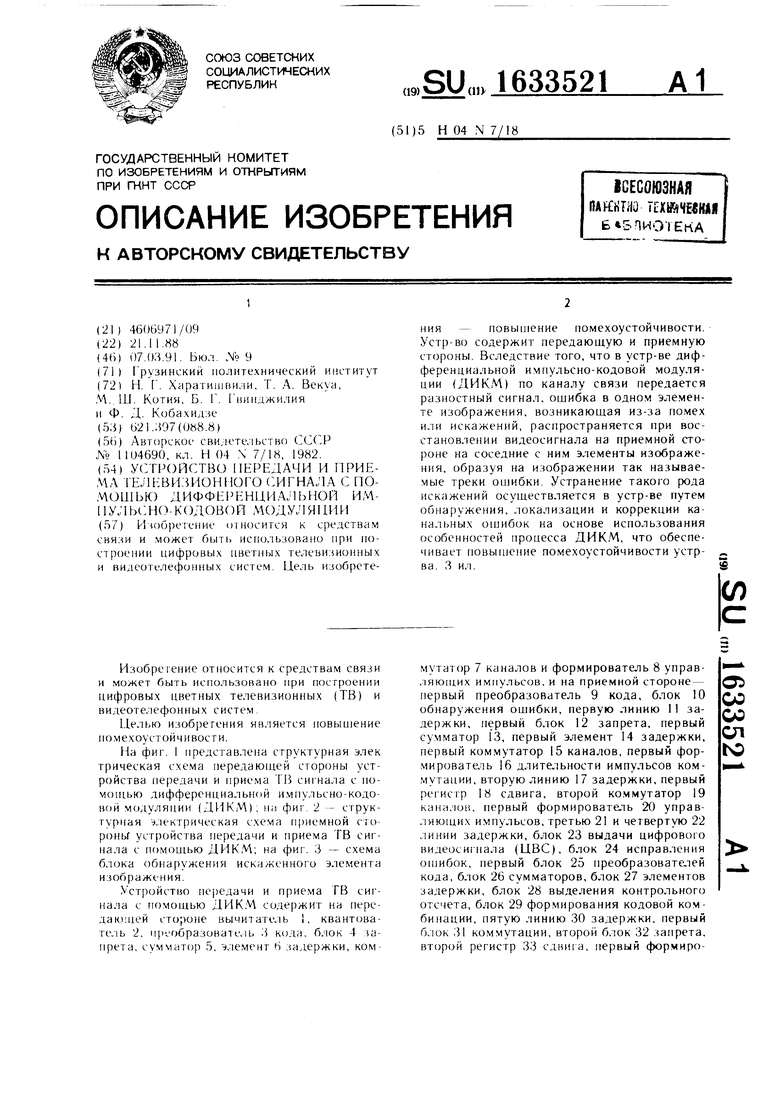

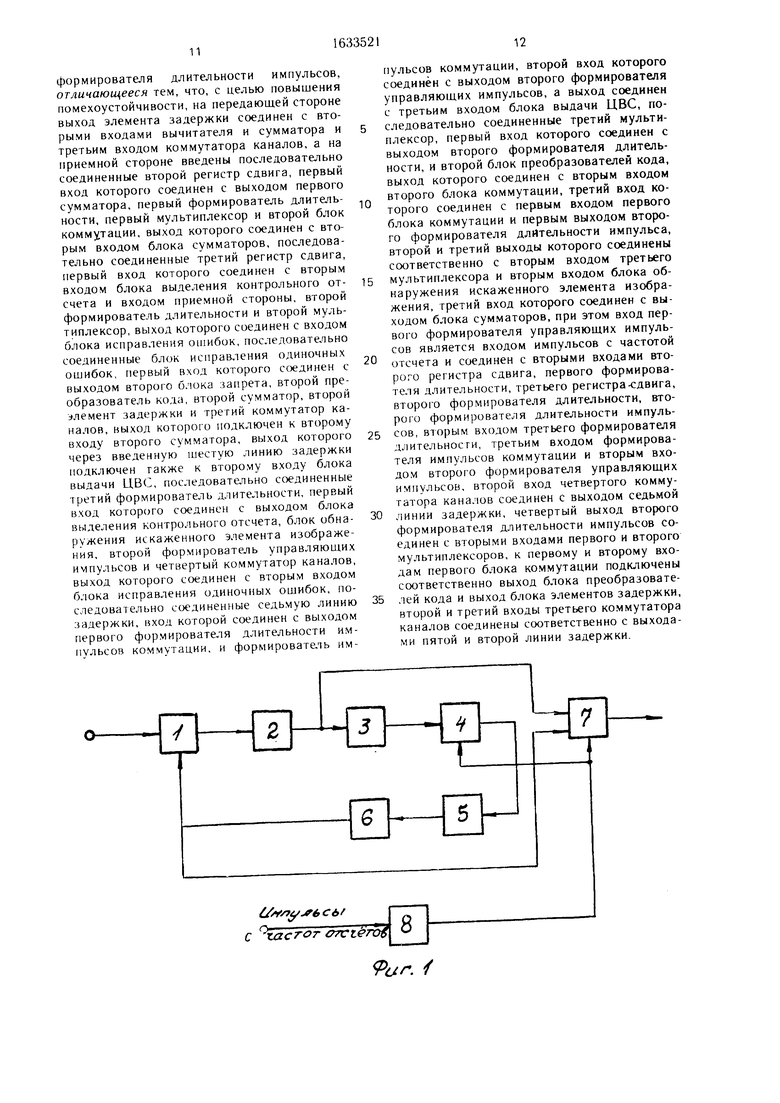

На фиг. I представлена структурная элек трическая схема передающей стороны устройства передачи и приема ТВ сигнала с помощью дифференциальной импульсно-кодовой модуляции (ДИКМ), на фиг 2 - структурная электрическая схема приемной по- роньГ устройства передачи и приема ТВ сигнала с помощью ДИКМ; на фиг. 3 - схема блока обнаружения искаженного элемента изображения.

Устройство передачи и приема ГВ сигнала с помощью ДИКМ содержит на передающей стороне вычитатель , квантователь 2, преобразователь 3 кода, блок 4 ia- прета, сумматор 5, элемент 6 задержки, коммутатор 7 каналов и формирователь 8 управляющих импульсов, и на приемной стороне - первый преобразователь 9 кода, блок 10 обнаружения ошибки, первую линию 11 задержки, первый блок 12 запрета, первый сумматор 13, первый элемент 14 задержки, первый коммутатор 15 каналов, первый формирователь 16 длительности импульсов коммутации, вторую линию 17 задержки, первый регистр 18 сдвига, второй коммутатор 19 каналов, первый формирователь 20 управляющих импульсов,третью 21 и четвертую 22 линии задержки, блок 23 выдачи цифрового видеосигнала (ЦВС), блок 24 исправления ошибок, первый блок 25 преобразователей кода, блок 26 сумматоров, блок 27 элементов задержки, блок 28 выделения контрольного отсчета, блок 29 формирования кодовой комбинации, пятую линию 30 задержки, первый блок 31 коммутации, второй блок 32 запрета, второй регистр 33 сдвша, первый формироО

оо ее

ел ю

ватель 34 длительности, первый мультиплексор 35, второй блок 36 коммутации, третий регистр 37 сдвига, второй формирователь 38 длительности, второй мультиплексор 39, блок 40 исправления одиночных ошибок, второй преобразователь 41 кода, второй сумматор 42, второй элемент 43 задержки, третий коммутатор 44 каналов, третий формирователь 45 длительности, блок 46 обнаружения искаженного элемента изображения, второй формирователь 47 управляющих импульсов, четвертый коммутатор 48 каналов, второй формирователь 49 длительности им- пчльсов, седьмую линию 50 задержки, формирователь 51 импульсов коммутации, третий мультиплексор 52, второй блок 53 преоб- разователей кода, шестую линию 54 задержки Блок 46 обнаружения искаженного элемента изображения содержит блоки 55-70 сравнения и блоки 71 -78 совпадения

Устройство работает следующим образом

На первый вход вычитателя 1 подается входной видеосшнал, представленный, например, параллельным восьмиразрядным двоичным кодом В вычитателе 1 разностное значение двух соседних отсчетов квантуется в квантователе 2 но нелинейной шкале, что позволяв, учитывая свойства зрения, значительно сократить число уровней квантования Например, при 256 уровнях квантования входного видеосигнала достаточно 16 уровней при нелинейном квантовании разност- ного сигнала Квантование на 16 уровней значение разностного сигнала в квантователе 2 преобразуется в четырехразрядный код Грея для передачи по каналу связи

Для выполнения арифметических операции в петле обратной связи в преобразова- теле 3 кода код Грея преобразуется в восьмиразрядный двоичный код В сумматоре 5 происходит сложение 1екушего разностного значения и значения предыдущего отсчета, полученного после задержки в элементе 6 задержки

На приемной стороне в первом сумматоре 13 происходит аналогичная операция Принятый разностный сигнал в коде Грея преобразуется в преобразователе 9 в восьмиразрядный двоичный код, который сумми- руется в первом сумматоре 13 со значением предыдущею отсчета видеосигнала, полученного с помощью первого элемента 14 задержки

Вследствие того, что в устройстве ДИКМ по каналу связи передается разностный сиг- нал, ошибка в одном элементе изображения, возникающая из-за помех или искажений, распространяется при восстановлении видеосигнала на приемной стороне на соседние с ним элементы изображения, образуя на изображении так называемые треки ошибки.

Устранение такого рода искажений может быть осуществлено путем обнаружения, локализации и коррекции канальных ошибок

0

5

на основе использования некоторых особенностей процесса ДИКМ.

Для этого каждая строка разбивается на группы (блоки), содержащие определенное количество элементов изображения. Последний элемент каждого блока является контрольным. Расположения контрольных отсчетов и, следовательно, и блоков меняется от строки к строке и от кадра к кадру. Количество отсчетов в блоке выбирается таким, чтобы это количество и число элементов в строке не имели общих множителей. Тогда выполняются условия перемещения контрольных точек, и фазы их совпадают через число кадров, равное числу элементов в блоке Число элементов в блоке, а также и закон их перемещения устанавливаются выбором коэффициента деления делителя частоты, входящего в состав формирователей 8 и 20, на вход которых подаются прямоугольные импульсы с частотой отсчетов (частотой дискретизации).

В контрольных точках разностное значение видеосигнала не передается, а вместо него с помощью коммутатора 7 каналов посылается значение видеосигнала предыдущего отсчета, представленное четырьмя старшими разрядами.

На приемной стороне разностный сигнал в виде четырезразрядного параллельного кода Грея поступает на вход преобразователя 9 кода, на вход блока 10 обнаружения ошибок, через первую линию 11 задержки на вход второго блока 32 запрета, на вход блока 28 выделения контрольного отсчета и на вход третьего регистра 37 сдвига.

В блоке 10 обнаружения ошибок происходит сравнение в моменты, соответствующие контрольным точкам принятого видеосигнала и видеосигнала, установленного и задержанного в петле обратной связи на период дискретизации, представленного четырьмя старшими разрядами. Сравнение этих значений в остальные моменты времени не происходит, что обеспечивается подачей на стробирующий вход блока 10 импульсов соответствующей длительности с первого формирователя 20 (сигнал U(t). Так как в контрольной точке передается значение предыдущего отсчета, то в случае отсутствия ошибок при передаче данного блока эти сравниваемые сигналы равны и на выходе блока 10 сигнал о наличии ошибки отсутствует

Сигнал отсутствует также на выходе блока 46 определения искаженного элемента изображения и, следовательно, на выходе второго формирователя 47 управляющих импульсов В результате, в первом 13 и во втором 42 сумматорах образуются правильные значения элементов изображения данного блока и блок 23 выдачи ЦВС по сигналу формирователя 51 импульсов коммутации выдает соответствующие элементы данного

блока, которые поступают с первого сумматора 13 через шестую линию 22 задержки.

Если же при передаче блока элементов изображения произошла ошибка, она воздействует на все последующие элементы блока, расположенные до контрольного отсчета. Поэтому в результате сравнения неправильно восстановленного значения видеосигнала (т. е. неправильно восстановленного предпоследнего элемента блока), полученного на выходе петли обратной связи со значением контрольного отсчета на выходе блока 10 появляется сигнал ошибки. В этом случае в блоке 46 обнаружения искаженного элемента изображения осуществляется определение искаженного элемента ошибочного блока.

Для обнаружения искаженных элементов изображения используется особенность ДИКМ. В частности, предпоследний элемент блока, т. е. элемент блока, который сравнивается с контрольным сигналом, восстанавливается в виде следующих сумм (согласно особенности процесса ДИКМ):

1-лл („ |)| А(,|;

. А,.-2 + +

А|„ I р

.V-1. А о-т-Л|Р-|-)-Л2-т-Л, +...+Л.

)| I

где Хп - i, , ..., Х - восстановление на

приемной стороне отсчета изображения; АО - заранее известное предсказанное значение для данного блока элементов; - разностные сигналы, полученные с канала связи;

ДЯ- I. Дл-2, ..

1)1, Ain- 2)2, Д2р -2, Д р-1

Д(

А

Л| л - I ll

с Д„,, А, || п 1 п- 6|Д я-1 t,. число блоке;

где , 2, р. Л, Лг

возможные искаженные вследствие действия одиночных помех в канале связи разностные сигналы

2 Д,. ,,

С 2, С(, Ј4),

элементов в

X

A,V,

-- восстановленные определенным обра юм предпоследние элементы блоков,

А(п- 1 )т, |6|А|1- I |;ч - I ; |, CfEjCl, C.J, С) С4.

Полученные таким образом восстановленные элементы блоков А ,, i сравниваются с соответствующими контрольными отсчетами ,|, Xt,n, .. Если для ошибочного

блока элементов с порядковым номером М выполняется условие

.f/0(C-t)rn.

(А(„-Пт -А(л- |)т)А,„, . t-2. Сд, С4|,

(2)

(HJ

то соответствующая разность , , является правильной, а кодовая комбинация - искаженной и. ее следует заменить комбинацией Д Ј1д/-т- Следует Q отметить, что восстановление предпоследнего элемента блоков в виде сумм (1) повторяет процесс некодирования на приемной стороне ДИКМ в обратной последовательности.

5Указанный алгоритм обнаружения искаженного элемента (точнее искаженной кодовой комбинации разности) реализуется путем введения в известное устройство дополнительных блоков.

В частности, с помощью регистров 33 и 37 сдвига восстановленные отсчеты и разностные сигналы задерживаются во времени на величину, равную 7 „,ф. При этом на их выходах восстановленные отсчеты и соответствующие разностные сигналы отдельных бло5 ков существуют одновременно (т. е. регистры их выдают параллельно). В результате на выходах регистров сдвига одновременно

образуются значения Дл-1, Дл-. AJ. Д:

и , А „- i, .... Х. AI, АО отдельных блоков. С помощью формирователей 34 и 38 длитель0 ности эти значения расширяются по длительности до величины, необходимой для анализа всех элементов блока, точнее до величины, необходимой для получения результатов суммирования по выражению (1). Длительность выходной информации

формирователей 34 и 38 длительности определяется по формуле

0

/ , (.-li|-i/,

(3)

где /ИИф - длительность выходной информации;

19 - период дискретизации;

Д; - число элементов в блоке.

Далее с помощью мультиплексора 35 на первый вход второго блока 35 коммутации последовательно подаются восстановленные отсчеты А „ 2, A ,,. t, .... A i, A o данного блока длительностью tllll ly . При этом отсчет А„ 2 сдвинут относительно конца контрольного отсчета данного блока на величину времени, равную 0-/, А л-.i -- на 1 1Я, А п-4 - на 3-/0, А ,,-.-, - на 6-/J , А л-я - на 10- /у , А,,-7 - на 15 Ig и т. д., что осуществляется подачей на второй вход первого мультиплексора 35 соответствующих коммутирующих импульсов с второго формирователя 49 длительности импульсов коммутации.

На другой вход второго блока 36 коммутации с помощью третьего 52 мультиплексора последовательно поступают разностные сигналы ( „, 2, | „-2. ,, i ,,i, Ал-j,

,

- на величину 6- /у , Л„ s

на

Л„-||4 . Ли, -.-, Л„.2, Л„-,,/-. При

этом разность A,,-iJ2 сдвинута относительно конца контрольного отсчета данного блока на величину времени 2/j , - на 4 Ту , 1 Л„...i з - на 7Tg , | A,,.- i|4 - на 11 7j и т. д., что осуществляется подачей на второй вход третьего мультиплексора 52 соответствующих коммутирующих импульсов с четвертого выхода второго формирователя 49 длительности импульсов коммутации.

Здесь U, .(...., -ц i соответствуют суммам в выражении (1), для реализации которых необходимы разностные сигналы такой последовательности. При атом п-,

Л„ ., У, А, до поступления в блок 36

коммутации во втором блоке 53 преобразователей кода преобразуются в восьмиразрядный двоичный код (как видно из описания, разностные сигналы Л,.,-:, ., Л,

Л| с канала связи поступают в коде Грен).

С помощью второго мультиплексора 39 на вход блока 24 исправления ошибок последовательно подаются разностные сигналы, поступающие с канала связи V,-i, Л„ , ..., Y. Л,, длительностью /,,, ц ЦрИ -.,Т()М V,. i сдвинут относите,тьно конца контроль- ного отсчета данного блока на величину времени, равной О- /g (т. с. появляется после лонтролы-ого отсчета), Л., на величину времени 1 /„ . Л., , на величину времени

величину К)-/о и г. д.. что осуществляется подачей на второй вход второго мультиплексора 39 соответствующих коммутирующих импульсов с первого выхода второго формирователя 49 длительности импульсов коммутации.

На выходе блока 24 исправления ошибок

:i3 входной последонаiельности .„ i. A,,

j, V, образуется последовательность., . f,, -i-i ., i. A,, ,. представленная в коде I рея, которые в первом блоке 25 преобразователей кодов преобразуются в восьми- разрядный двоичный код для выполнения арифметических операций.

Блоки 31 и 36 коммутации по сигналу, поступающему с третьего выход; второго формирователя 4) длительности импульсов коммутации, осуществляют коммутацию ин- формаций, поступающих с блоков 25 и 27, и 35 и 53 так, что на выходе блока 2В сумматоров образуются СУММЫ вида (I). которые поступаю: на вход блока 46 определения искаженных элементов изображения.

В блоке 4(i четырех старших разряда, полученных в блоке 26 сумм, сравниваются с контрольным отсчеюм данного блока элементов. Контрольные отсчеты поступают на другой вхоп блока 46 с блоков 46 и 28 через тре ий формирователь 45 длительности Необходимая длительность контрольных отсчетов определяется но формуле (3).

В случае удовлетворения УСЛОВИЯ 12) блок 46 обнаружения искаженного элемента

10

20 25

15

30 35

4Q

45

50

изображения выдает сигнал об искажении кодовой разности . Следует отметить, что в блоке 46 сравнение восстановленных отсчетов в виде результатов суммирования (правая часть выражения (1)) и контрольного отсчета данного блока осуществляется только в моменты, соответствующие образованию сумм, что осуществляется подачей на третий вход блока 46 управления импульсов с второго выхода второго формирователя 49 длительности импульсов, коммутации.

Для работы блока 46 (фиг. 3) в блоках 55 -70 сравниваются четыре старших разряда четырех сумм, поступающих от блока 26, и контрольная информация также представленная в четырехразрядном двоичном коде. Затем блоки 55-70 идентичны и представляют собой элемент типа ИСКЛЮ ЧАЮШЕЕ ИЛИ-НЕ. Результаты сравнения поступают на входы блоков 71 и 72 совпадения, которые идентичны и выполняют логическую функцию И. Далее полученные ре- .ультаты поступают на другие блоки 73 - 76 совпадения, которые также идентичны и выполняют логическую функцию И. На другие ьходы блоков 73- 76 совпадения поступает управляющий сигнал от второго выхода формирователя 49.

Следовательно, выходные сигналы блока 46 существуют в течение времени равной длительности блока элементов (т. е. выходные сигналы блока 46 существуют в моменты ко;орые соответствуют местонахождению разностных сигналов в данном блоке). Сигналы о местонахождении искаженной и правильной кодовых комбинаций с блока 46 поступают во второй формирователь 47 управляющих импульсов, где формируются по длительности и по форме и одновременно задерживаются.

Поскольку предлагаемый алгоритм согласно выражению (1) дает возможность обнаружить, локализовать и корректировать только одну единичную ошибку в течение одной группы элементов, то для предотвращения случаев ложного обнаружения ошибок после правильного обнаружения на выходе блока 46 сигналы об обнаружении ошибок существуют только один раз и соответствуют тому моменту, где первый раз была обнаружена ошибка. Остальные сигналы на блока 46 не пропускаются (вероятность возникновения указанного случая близка к нулю).

Выходные сигналы формирователя 47 через четвертый коммутатор 48 каналов по- тупают па вход блока 40 исправления одиночных ошибок. На второй вход коммутатора 48 через шестую линию 50 задержки поступает управляющий сигнал, т. е. при итсутствии сигнала о наличии ошибки в дан- блоке элементов выходные сигналы формирователя 17 не поступают в блок 40.

По сигналу второго формирователя 47 управляющих импульсов блок 40 исправления ошибок кодовую комбинацию заменяет комбинацией . В результате во втором сумматоре 42 образуются пра- вильные значения элементов данного блока, которые пропускаются блоком 23 выдачи цифрового видеосигнала на выход приемной стороны системы по сигналу формирователя 51 импульсов коммутации.

Следует отметить, что декодеры ДИКМ- основной (содержащий блоки 9, 12, 13. 14 и 15) и дополнительный (содержащий блоки 32. 41, 42, 43 и 44) работают идентично.

В случае необнаружения или неправильного обнаружения искаженного элемента блок 23 по сигналу формирователя 51 импульсов коммутации выдает CHI налы блока, соседними с данным блоком и расположенного на предыдущей строке, которые поступают с первого регистра 18 сдвига через второй коммутатор 19 каналов и четвертую линию 22 задержки.

На передающей и приемной сторонах в моменты времени, соответствующие контрольным отсчетам, с помощью блоков 12 и 32 запрета разностный сигнал приравни- вается к нулю. При безошибочной передаче блока это соответствует тому, что на восстановленном изображении на передающей и приемной сторонах системы значение яркости в точке контрольного отсчета приравнивается к яркости предыдущего отсчета Но так как контрольный отсчет не стабилизирован в данной точке (положение его меняете я от строки к строке и от кадра к кадру) а также,учитывая сильную корреляционную связь между соседними элементами изображения, такое повторение яркости незаметно для наблюдателя.

При наличии ошибки во время передачи блока на приемной стороне системы и петли обратной связи первого 13 и второго 42 сумматоров по выходному сигналу блока 10 обнаружения ошибок представляется четыре старших разряда предпоследнего элемента блока, переданных в контрольном отсчете, три младших разряда устанавливаются в нулевое, а следующий за ним разряд - в единичное состояние

Значение контрольного отсчета выделяется блоком 28, на выходе блока 29 обра зуется кодовая комбинация вида С С-СьС-,()()() (С„ 0/1) - значение символа в гг-м разряде, которая поступает на вход первого коммутатора 15 и через пятую линию 30 за- держки на вход третьего комм татора 44 каналов

Формула и.нюре гения

Устройство передачи и приема телевизионного сигнала помощью дифференциальной импульсно-кодовой модуляции, содержащее на передающей i гороне после0

5

5 0 5

0 5

0

5

довательно соединенный вычитагель, первый вход которого является входом передающей стороны устройства передачи и приема телевизионного (ТВ) сигнала с помощью дифференциальной импульсно-кодовой модуляции (ДИКМ), квантователь, преобразователь кода, блок запрета, сумматор и элемент задержки, а также формирователь, управляющих импульсов, выход которого соединен с вторым входом блока запрета, с первым входом коммутатора каналов, второй вход которого соединен с выходом квантователя, а выход является выходом передающей стороны устройства, а на приемной стороне последовательно соединенные первый преобразователь кода, вход которого обьединен с первым входом блока обнаружения ошибки и с входом первой линии задержки и является входом приемной стороны устройства, первый блок запрета, первый сумматор, первый элемент задержки и первый коммутатор каналов, второй вход которого соединен с первым входом первого формирователя длительности импульсов коммутации, входом второй линии задержки и выходом блока обнаружения ошибки, а выход соединен с вторым входом первого сумматора, выход которого соединен с входом первого регистра сдвига, первый и второй выходы которого подключены соответственно к первому и второму входам второго коммутатора каналов, третий вход которого соединен с выходом формирователя длительности импульсов коммутации, а также первый формирователь управляющих импульсов, выход которого соединен с вторым входом первого блока запрета, с вторым входом блока обнаружения ошибки, вторым входом первого формирователя длительности импульсов коммутации, с входом третьей линии задержки и первым входом блока выделения контрольного отсчета, выход которого через блок формирования кодовой комбинации соединен с третьим входом первого коммутатора каналов, четвертую линию задержки, включенную между выходом второго коммутатора каналов и входом блока выдачи цифрового видеосигнала (ЦВС), выход которого является выходом устройства передач ц ирне ма ТВ сигнала с помощью ДИКМ, последовательно соединенные блок исправления ошибок и первый блок преобразователей кода, последовательно соединенные блок сумматоров, первый вход которого соединен с выходом первого блока коммутации, и блок элементов задержки, пятую линию задержки, вход которой соединен с выходом блока формирования кодовой комбинации, второй блок запрета, первый и второй входы которою соединены соответственно с выходами первой линии задержки и третьей линии задержки, при этом третий вход блока обнаружения ошибки соединен с выходом первого элемен та затержки. третий вход втором) коммута гора каналов соединен с выходом первого

формирователя длительности импульсов, отличающееся тем, что, с целью повышения помехоустойчивости, на передающей стороне выход элемента задержки соединен с вторыми входами вычитателя и сумматора и третьим входом коммутатора каналов, а на приемной стороне введены последовательно соединенные второй регистр сдвига, первый вход которого соединен с выходом первого сумматора, первый формирователь длительности, первый мультиплексор и второй блок коммутации, выход которого соединен с вторым входом блока сумматоров, последовательно соединенные третий регистр сдвига, первый вход которого соединен с вторым входом блока выделения контрольного отсчета и входом приемной стороны, второй формирователь длительности и второй мультиплексор, выход которого соединен с входом блока исправления ошибок, последовательно соединенные блок исправления одиночных ошибок первый вход которого соединен с выходом второго блока запрета, второй преобразователь кода, второй сумматор, второй элемент задержки и третий коммутатор каналов, выход которого подключен к второму входу второго с мматора, выход которого через введенную шестую линию задержки подключен также к второму входу блока выдачи ЦВС, последовательно соединенные третий формирователь длительности, первый вход которого соединен с выходом блока выделения контрольного отсчета, блок обнаружения искаженного элемента изображения, второй формирователь управляющих импульсов и четвертый коммутатор каналов, выход которого соединен с вторым входом блока исправления одиночных ошибок, последовательно соединенные седьмую линию задержки, вход которой соединен с выходом первого формирователя длительности импульсов коммутации, и формирователь имt/#sfyjp, СЬ/

О

с tacror 07cteroc

0

5

0

5

пульсов коммутации, второй вход которого соединён с выходом второго формирователя управляющих импульсов, а выход соединен с третьим входом блока выдачи ЦВС, последовательно соединенные третий мультиплексор, первый вход которого соединен с выходом второго формирователя длительности, и второй блок преобразователей кода, выход которого соединен с вторым входом второго блока коммутации, третий вход которого соединен с первым входом первого блока коммутации и первым выходом второго формирователя длительности импульса, второй и третий выходы которого соединены соответственно с вторым входом третьего мультиплексора и вторым входом блока обнаружения искаженного элемента изображения, третий вход которого соединен с выходом блока сумматоров, при этом вход первого формирователя управляющих импульсов является входом импульсов с частотой отсчета и соединен с вторыми входами второго регистра сдвига, первого формирователя длительности, третьего регистра-сдвига, второю формирователя длительности, второю формирователя длительности импульсов, вторым входом третьего формирователя длительности, третьим входом формирователя импульсов коммутации и вторым входом второго формирователя управляющих импульсов, второй вход четвертого коммутатора каналов соединен с выходом седьмой линии задержки, четвертый выход второго формирователя длительности импульсов соединен с вторыми входами первого и второго мультиплексоров, к первому и второму входам первого блока коммутации подключены соответственно выход блока преобразователей кода и выход блока элементов задержки, второй и третий входы третьего коммутатора каналов соединены соответственно с выходами пятой и второй линии задержки

Pvr. j

aassg

Фиг 2

o9 i/ифв

9fv«SЈa

Or drrorcf 26

(&5&

(&),

(т)

(VWto

Авторы

Даты

1991-03-07—Публикация

1988-11-21—Подача