Изобретение относится к автоматике и вычислительной технике, а именно к устройствам, предназначенным для систем электронной коммутации цифровых сигналов, и может быть использовано в качестве межпроцессорного коммутатора с сохранением маршрута коммутации при отключении питания в мультипроцессорных вычислительных системах.

Целью изобретения является повышение помехоустойчивости за счет уменьшения перекрестных помех,

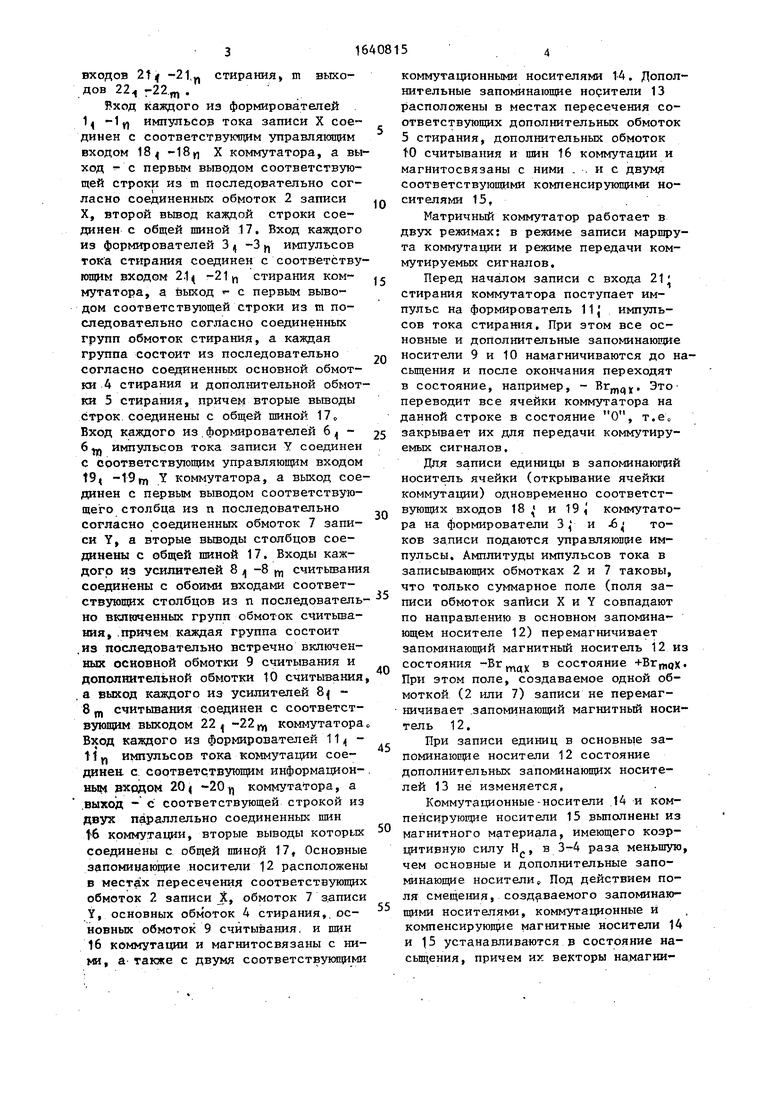

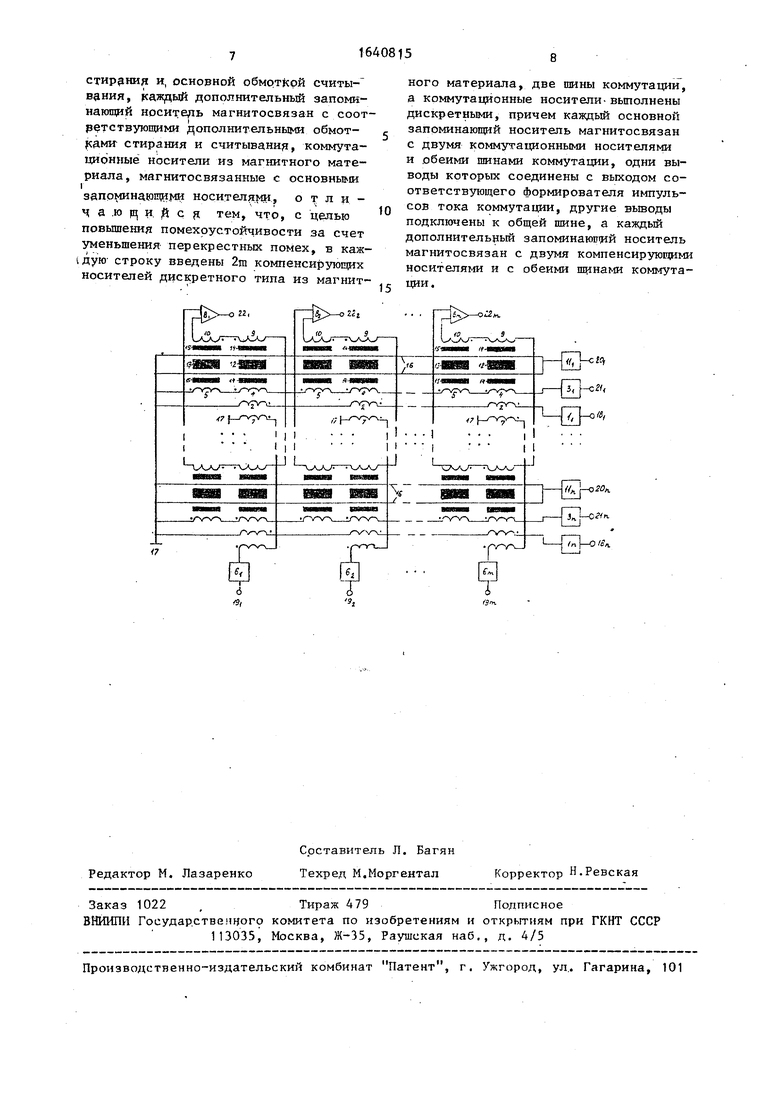

На чертеже представлена принципиальная электрическая схема предложенного устройства.

Матричный коммутатор содержит п формирователей 1«-1п импульсов тока записи X, п строк из m обмоток 2 записи X, п формирователей 3 -3п импульсов тока стирания, п строк основных 4 и дополнительных 5 обмоток стирания т формирователей 6 -6m импульсов тока записи У, m столбцов из п обмоток 7 записи Y, m усилителей 8, считывания,п строк из m основных обмоток

9считывания и m дополнительных обмоток

10считывания, п формирователей 11 11У. импульсов тока коммутации, п строк из m основных запоминающих носителей 12 и m дополнительных запоминающих носителей 13, п строк из 2и коммутационных дискретных носителей 14 и 2т компенсирующих дискретных носителей 15, п строк из двух коммутационных шин 16, общую шину 17,

п управляющих входов 18 -18п X, m управляющих входов 19 i -19 m Y. ti информационных входов 20 -20п , п

о

Ј

00 СЛ

входов 2f| 21,п стирания, m выходов 22, -22m .

Вход каждого из формирователей 1 -1 импульсов тока записи X соединен с соответствующим управляющим входом 18 { -18 и X коммутатора, а выход - с первым выводом соответствующей строки из m последовательно согласно соединенных обмоток 2 записи X, второй вывод каждой строки соединен с общей шиной 17. Вход каждого из формирователей 3 -3 и импульсов тока стирания соединен с соответствующим входом 2.1 21п стирания ком- мутатора, а выход - с первым выводом соответствующей строки из m последовательно согласно соединенных групп обмоток стирания, а каждая группа состоит из последовательно согласно соединенных основной обмотки 4 стирания и дополнительной обмотки 5 стирания, причем вторые выводы строк соединены с общей шиной 17„ Вход каждого из формирователей 6 -

W

импульсов тока записи У соединен

с соответствующим управляющим входом Т9 -19т Y коммутатора, а выход соединен с первым выводом соответствующего столбца из п последовательно согласно соединенных обмоток 7 записи Y, a вторые выводы столбцов соединены с общей шиной 17. Входы каждого из усилителей 8 ц -8 т считывания соединены с обоими входами соответ

ствующих столбцов из п последователь- но включенных групп обмоток считывания причем каждая группа состоит ,из последовательно встречно включенных основной обмотки 9 считывания и дополнительной обмотки 10 считывания, а выход каждого из усилителей 8( - 8 m считывания соединен с соответствующим выходом 22 -22, коммутатора Вход каждого из формирователей 11t - tln импульсов тока коммутации соединен с соответствующим информационным входом 20 -20 у, коммутатора, а выход - с соответствующей строкой из двух параллельно соединенных шин fb коммутации, вторые выводы которых соединены с общей шиной 17, Основные запоминающие носители 12 расположены в местах пересечения соответствующих обмоток 2 записи )t, обмоток 7 записи Y, основных обмоток 4 стирания, основных обмоток 9 считывания, и шин 16 коммутации и магнитосвязаны с ними, а также с двумя соответствующими

Q - „ 5

0

0

коммутационными носителями 14. Дополнительные запоминающие носители 13 расположены в местах пересечения соответствующих дополнительных обмоток 5 стирания, дополнительных обмоток tO считывания и шин 16 коммутации и магнитосвязаны с ними . и с двумд соответствующими компенсирующими носителями 15,

Матричный коммутатор работает в двух режимах: в режиме записи маршрута коммутации и режиме передачи коммутируемых сигналов.

Перед началом записи с входа 21 стирания коммутатора поступает импульс на формирователь 11J импульсов тока стирания. При этом все основные и дополнительные запоминающие носители 9 и 10 намагничиваются до насыщения и после окончания переходят в состояние, например, - Brmc))r. Это переводит все ячейки коммутатора на данной строке в состояние О, т.ес закрывает их для передачи коммутируемых сигналов.

Для записи единицы в запоминающий носитель ячейки (открывание ячейки коммутации) одновременно соответствующих входов 18 и 19, коммутатора на формирователи 3 , и & токов записи подаются управляющие импульсы. Амплитуды импульсов тока в записывающих обмотках 2 и 7 таковы, что только суммарное поле (поля записи обмоток записи X и Y совпадают по направлению в основном запоминающем носителе 12) перемагничивает запоминающий магнитный носитель 12 из

0

5

0

состояния -Вг

max

в состояние +Brrnqx.

При этом поле, создаваемое одной обмоткой (2 или 7) записи не перемагничивает запоминающий магнитный носитель 12.

При записи единиц в основные запоминающие носители 12 состояние дополнительных запоминающих носителей 13 не изменяется,

Коммутационные-носители 14 и компенсирующие носители 15 выполнены из магнитного материала, имеющего коэрцитивную силу Н , в 3-4 раза меньшую, чем основные и дополнительные запоминающие носителие Под действием поля смещения, создаваемого запоминающими носителями, коммутационные и компенсирующие магнитные носители 14 и 15 устанавливаются в состояние насыщения, причем их векторы намагни

51

ченности устанавливаются антипараллельно векторам намагниченности соответствующих запоминающих носителей В режиме коммутации на входы 20, 20п формирователей 11 -11П им- пульсов токов коммутации одновременно подаются информационные сигналы Импульсы тока с выходов формирователей 11 4 -11г подаются в шины 16 коммутации и создают импульсное магнитное поле в направлении, перпендикулярном основным и дополнительным запоминающим носителям 12 и 13 ь Под действием этого поля векторы магнитной индукции коммутационных носителей 14 и компенсирующих носителей 15 поворачиваются на угол об и, следовательно, наводится ЭДС в основных и дополнительных обмотках 9 и 10 считывания „ После окончания импульса коммутации под действием полей смещения основных и дополнительных запоминающих носителей 12 и 13, векторы намагниченности коммутационных и компенсирующих магнитных носителей 14 и 15 возвращаются в исходное состояние. В результате на входах усилителей 8 -8W считывания и соответственно на выходах 22 -22 т матричного коммутатора появляются сигналы, определяемые поворотом векторов намагниченности двух коммутационных носителей 14 и двух компенсирующих носителей 15,

-При записи 1 сигнал на входе усилителя считывания пропорционален учетверенному изменению индукции коммутационного носителя, а при записи О равен нулю за счет взаимной ком- пенсации ЭДС, создаваемой в обмотках считывания при изменении индукции коммутационных носителей.

Конструктивное расположение шин коммутации между записывающими носи- телями и соответствующими коммутационными и компенсирующими носителями, а также параллельное соединение этих пин приводит к тому, что создаваемые ими поля Н| в зоне располо- жения запоминающих носителей направлены встречно и компенсируются, а в зоне расположения коммутационных и компенсирующих носителей удваиваются и достигают величины Н«та 2НК„ Это также позволяет снизить уровень межканальных помех.

Таким образом, повышение помеха- устойчивости матричного коммутатора

5

8

« 0 5 д

0

, л

156

за счет снижения, уровня перекрестных помех позволяет расширить область его применения, снизить требования к электронному обрамлению, т.е., создать возможность для широкого использования матричного коммутатора в микропроцессорных системах в качестве межпроцессорного коммутатора высокой надежности, а также в специализированных матричных операционных устройствах свертки цифровых сигналов

Формула изобретения

Матричный коммутатор, содержащий п строк из m обмоток записи X, соединенных в строке последовательно согласно, один вывод каждой строки обмоток записи X соединен с выходом соответствующего формирователя импульсов тока записи X, другой вывод соединен с общей шиной, п строк из m групп обмоток стирания, каждая из которых содержит соединенные последовательно согласно основную и дополнительную обмотки стирания, группы в строке соединены последовательно согласно, один вывод каждой строки обмоток стирания соединен с выходом соответствующего формирователя импульсов тока стирания, другой вывод соединен с общей шиной, m столбцов из п обмоток записи Y, соединенных в столбце последовательно согласно, один вывод каждого столбца обмоток записи Y соединен с выходом соответствующего формирователя импульсов тока записи Y, другой вывод соединен с общей шиной, m усилителей считывания, m столбцов из п групп обмоток считывания, каждая группа содержит основную и дополнительную обмотки считывания, соединенные последовательно встречно, все группы соединены в столбце последовательно встречно, выводы каждого столбца обмоток считывания соединены с входами соответствующего усилителя считывания, п формирователей импульсов тока коммутации, п строк из m групп дискретных запоминающих носителей из магнитного материала, каждая из которых состоит из основного и дополнительного запоминающих носителей, каждый основной запоминающий носитель расположен в местах пересечения соответствующих обмоток записи X и У, и магнитосвязан с ними, с соответствующей основной обмоткой

стирания и, основной обмоткой считывания, каждый дополнительный запоминающий носитель магнитосвязан с соотi

ретствующими дополнительными обмотками стирания и считывания, коммутационные носители из магнитного материала, магнитосвязанные с основными запоминающими носителями, о т л и - , тем, что, с целью повышения помехоустойчивости за счет уменьшения перекрестных помех, в каждую- строку введены 2т компенсирующих носителей дискретного типа из магнит

5

ного материала, две шины коммутации, а коммутационные носители-выполнены дискретными, причем каждый основной запоминающий носитель магнитосвязан с двумя коммутационными носителями и обеими шинами коммутации, одни выводы которых соединены с выходом соответствующего формирователя импульсов тока коммутации, другие выводы подключены к общей шине, а каждый дополнительный запоминающий носитель магнитосвязан с двумя компенсирующими носителями и с обеими шинами коммутации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный коммутатор | 1985 |

|

SU1307577A1 |

| Матричный коммутатор | 1981 |

|

SU1084986A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Устройство управления ферритовыми фазовращателями модульной фазированной антенной решетки | 2018 |

|

RU2698957C1 |

| ДВУХКОМПОНЕНТНЫЙ МАТРИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ МАГНИТНОГО ПОЛЯ | 2004 |

|

RU2290654C2 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| Матричный коммутатор | 1976 |

|

SU597093A1 |

| Устройство для считывания оптической информации | 1979 |

|

SU860135A1 |

| Матричный коммутатор | 1988 |

|

SU1539984A2 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

Изобретение относится к области автоматики и вычислительной технике, в частности, к устройствам для систем электронной коммутации цифровых сигналов, и может быть использовано в качестве межпроцессорного коммутатора с сохранением маршрута коммутации при отключении питания мультипроцессорных вычислительных систем. Целью изобретения является повышение помехоустойчивости, что достигается путем уменьшения перекрестных помех. Это позволяет расширить область применения матричного коммутатора, снизить требования к электронному обрамлению, т.е. создать возможность для широкого использования матричного коммутатора в микропроцессорных системах в качестве межпроцессорного коммутатора высокой надежности, а также в специализированных матричных опера- о ционных устройствах свертки цифровых ® сигналов. 1 ил. (/)

«Л-«

-СИ,

-ов,

| Матричный коммутатор | 1985 |

|

SU1307577A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-07—Публикация

1989-01-09—Подача