Изобретение относится к электронной технике, конкретно к области электронной цифровой коммутационной техники, и может быть использовано для построения наращиваемых интерфейсов параллельного действия в вычислительной технике.

Цель изобретения - расширение частотного диапазона коммутируемых сигналов при обмене в обратном направлении.

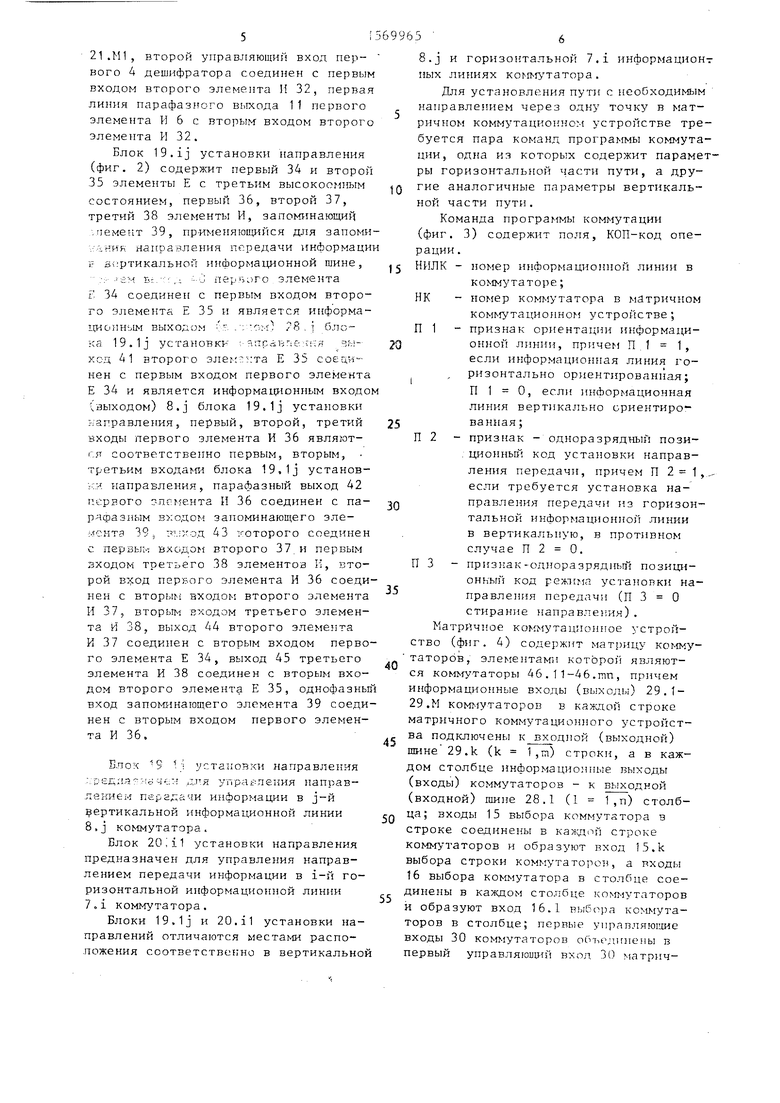

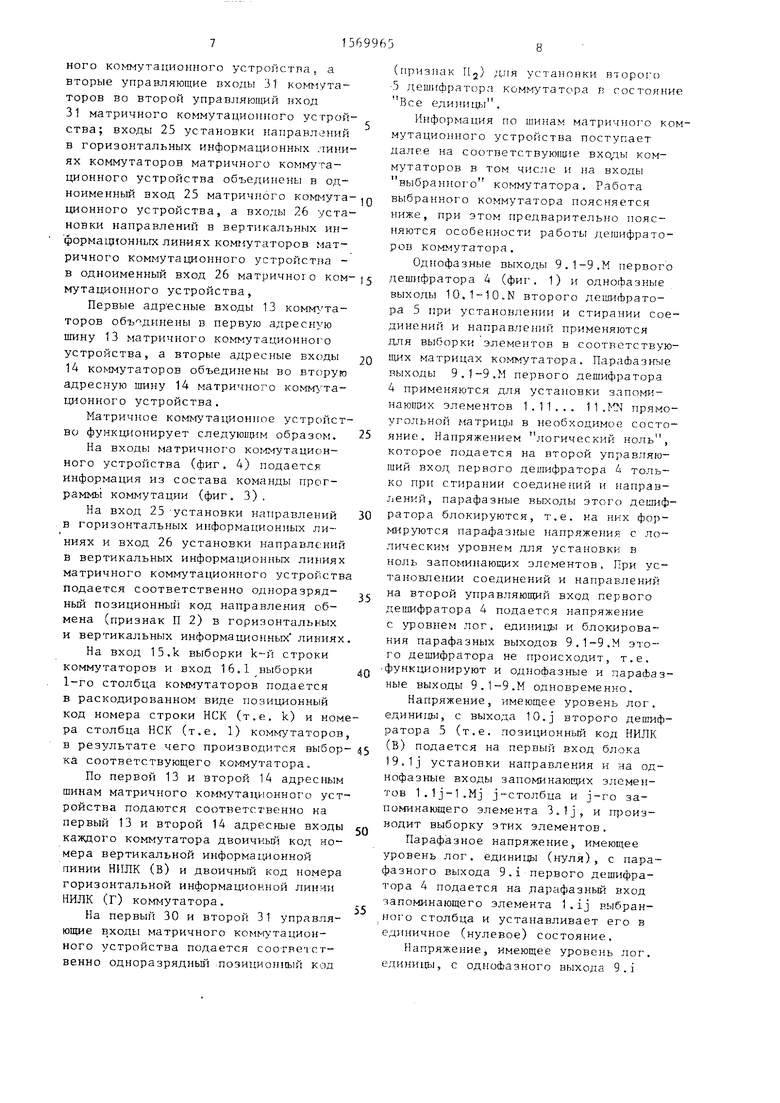

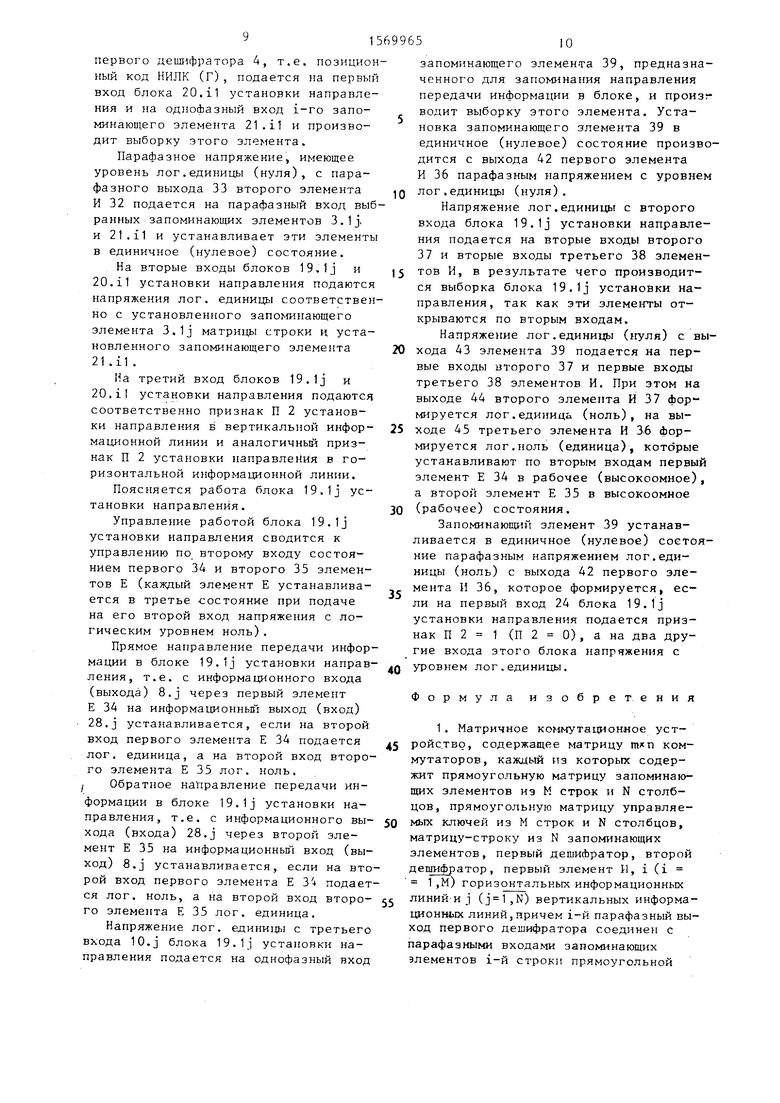

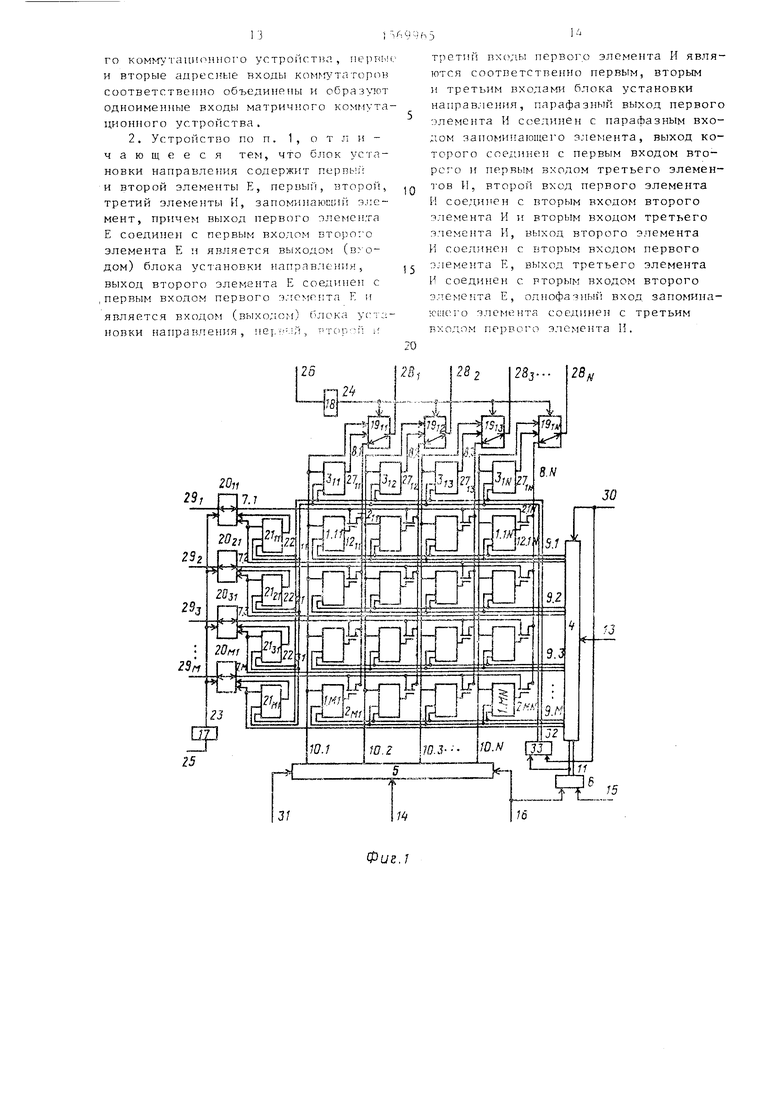

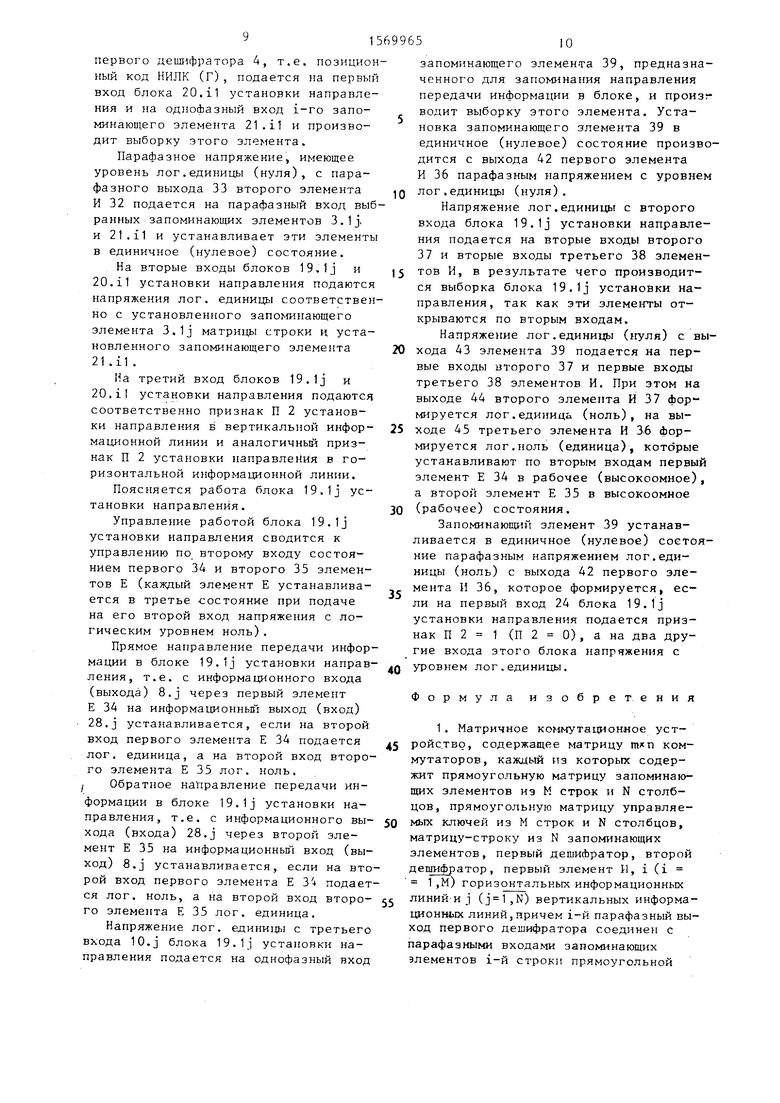

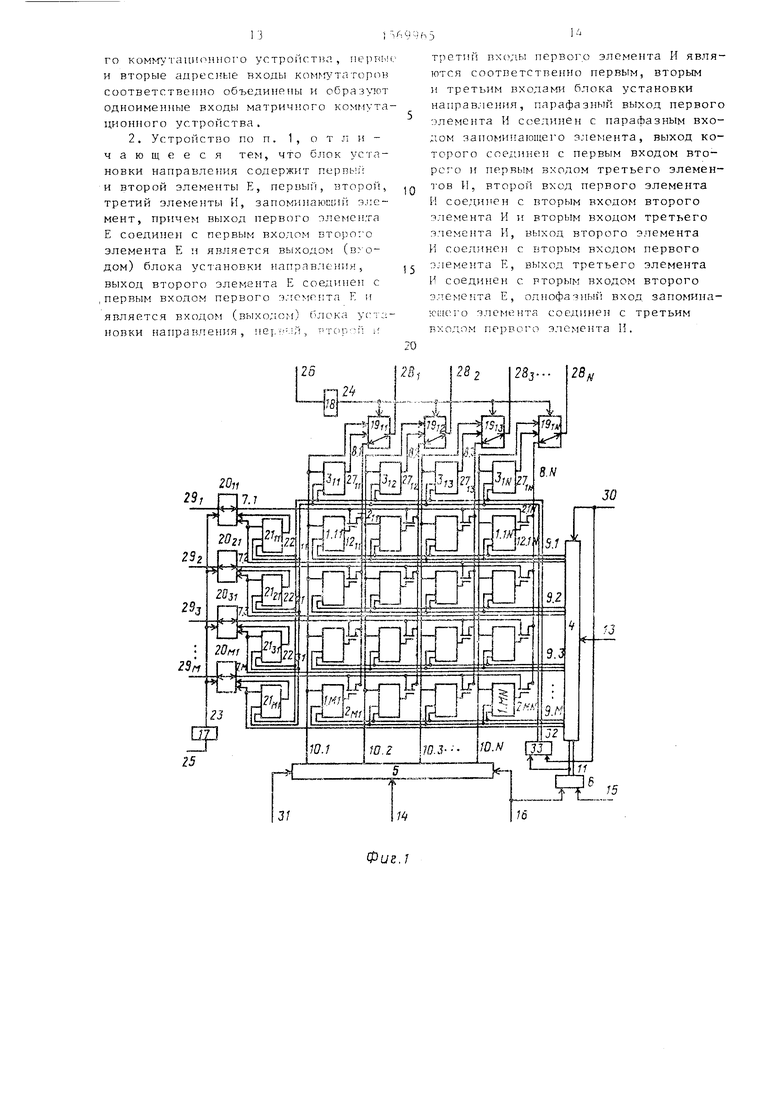

На фиг. 1 приведена схема, иллюстрирующая пример реализации коммутатора, который является основой предлагаемого матричного коммутационного устройства; на фиг. 2 - блок установки направления; на фиг. 3 - Лормат программы коммутации; на Лиг. 4 - схема матричного коммутационного устройства для случая, когда она содержит m«n коммутаторов.

Коммутатор (фиг. 1) содержит прямоугольную матрицу запоминающих элементов 1 . ij (i 1,М; j 1,N), применяющихся для запоминания соедине- ний, содержит прямоугольную матрицу управляемых ключей 2.1J, применяемых для управления соединений, содержит матрицу-строку запоминающих элементов 3.1J для запоминания выбранных путей в вертикальных информационных линиях, первый 4 и второй 5 дешифраторы, первый элемент И 6, а также i горизонтальных информационных линий 7.1-7.М и j вертикальных информационных линий 8.1-8.N, причем 1-й парафазный выход 9.1 первого дешифратора 4 со- цинен с парафазными входами эапошшающих элементов 1.i1-1.iN и применяется для установки этих элементов, j-й выход 10.J второго дешифратора 5 соединен с однофазными входами запоминающих элементов 1.1J-1.MJ однофазным входом j-го запоминающего элемента 3.1J и применяется для вы- борки этих элементов, а парафазный выход 11 первого элемента И 6 соединен с парафазным входом первого дешифратора 4. i-я горизонтальная информационная линия 7.i соединена в пределах i-й строки управляемых ключей 2.i1-2.iN с первыми выходами этих ключей, j-я вертикальная информационная линия 8.j в пределах j-ro столбца управляемых ключей 2.1J-2.MJ с вторыми выходами этих ключей, выход 12.1J каждого из запоминающих элементов 1ij соединен с входом соответствующего ключа 2.1J, информационный вход 13 первого дешифратора 4 и ин- формационный вход 14 второго дешифратора 5 являются соответственно первым и вторым адресными входам коммутатора, первый вход первого элемента И 6 является входом 15 выбора ком- мутатора в строке матрицы коммутаторов, второй вход первого элемента И 6 соединен с первым входом второго дешифратора 5 и является входом 16 выбора коммутатора в столбце матрицы коммутаторов, кроме, того, в состав коммутатора входит первый 17 н второй 18 формирователи (повторители), матрица-строка, элементами которой являются блоки 19.11-19.1N установки направлений, применяющиеся для установки направлений передачи информации в вертикальных информационных линиях коммутатора, матрица-г-столбец, элементами которой являются блоки 20.11- 20.Ml установки направлений, применяющиеся для установки направлений передачи информации в горизонтальных информационных линиях коммутаторов и матрица-столбец, элементами которой являются запоминающие элементы 21.11-21.Ml, применяющиеся для запоминания путей в горизонтальных информационных линиях коммутатора, i-й однофазный выход 9.1 первого дешифратора 4 соединен с однофазным входом 1-го запоминающего элемента 21.11 и первым входом 1-го блока 20.11 установки направления, применяется для выборки этих элементов, выход 22.11 1-го запоминающего элемента 21.11 соединен с вторым входом 1-го блока 20.11 установки направления, выход 23 первого формировател

17соединен с третьими входами блоков 20.11-20.М1 установки направлений, выход 24 второго формирователя

18соединен с третьими входами блоков 19.11-19.IN, вход 25 первого

17 и вход 26 второго 18 формирователей являются входом установки направлений соответственно в горизонтальных 7.1-7.М и вертикальных 8.I-8.N информационных линиях ком1-гутатора, j-й выход 10.J второго дешифратора 5 соединен с первым входом j-ro блока 19.1J установки направления, выход 27.1j j-ro запоминающего элемента 3.1J соединен с вторым входом j-ro блока 19.1J установки направления, j-я вертикальная информационная линия 8 .соединена с четвертым информационным входом (выходом) j-ro блока 19.1J установки направления, вход (выход) 1-го блока 20.11 установки направления является i-м входом (выходом) коммутатора, пятый информационный выход (вход) 28.j блоков 19. 1j является j-м информационным выходом (входом) коммутатора, четвертый информационный вход (выход 29.1 блока 20.11 установки направления является i-м информационным входом (выходом) коммутатора, второй управляющий вход первого дешифратора 4 и второй управляющий вход второго дешифратора 5 являются соответственно первым 30 и вторым 31 управляющими входами комг-гутатора, парафазны выход 33 второго элемента И 32 соединен с парафазными входами запоминающих элементов 3.1 1-3.1N и 21.1121.М1, второй управляющий вход пер- вого 4 дешифратора соединен с первым входом второго элемента И 32, первая линия парафазного выхода 11 первого элемента И 6 с вторым входом второго элемента И 32.

Блок 19.1J установки направления (фиг. 2) содержит первый 34 и второй 35 элементы Е с третьим высокоомиым состоянием, первый 36, второй 37, третий 38 элементы И, запоминающий,

пемеит 39, применяющийся для запоми- мния направления передачи информации F вертикальной информационной шине,

J6M БС ,1 чО перього элемента F 34 соединен с первым входом второго элемента Е 35 и является информационным выходом (. хом) /8.i блока 19.1J установки ;аправпемня выход 41 второго элемента Е 35 соединен с первым входом первого элемента Е 34 и является информационным входом (выходом) 8.J блока 19.1J установки направления, первый, второй, третий входы первого элемента И 36 являются соответственно первым, вторым, третьим входами блока 19.1J установки направления, парафазный выход 42 первого элемента И 36 соединен с па- рафазным входом запоминающего элемента 39, 43 которого соединен с первым входом второго 37 и первым входом третьего 38 элементов И, второй вход первого элемента И 36 соединен с вторым входом второго элемента И 37, вторым входом третьего элемента И 38, выход 44 второго элемента И 37 соединен с вторым входом первого элемента Е 34, выход 45 третьего элемента И 38 соединен с вторым входом второго элементу Е 35, однофазный вход запоминающего элемента 39 соединен с вторым входом первого элемента И 36.

Блок 19 1j установки направления ;редиачначен дня управления направлением передачи информации в j-й вертикальной информационной линии 8.j коммутатора.

Блок 20.11 установки направления предназначен для управления направлением передачи информации в i-й горизонтальной информационной линии 7.1 коммутатора.

Блоки 19.1J и 20.i1 установки направлений отличаются местами расположения соответственно в вертикальной

10

15

20

5

0

5

0

нк

П 1

П 2

8.J и горизонтальной 7.1 ннформационт ных линиях коммутатора.

Для установления пути с необходимым направлением через одну точку в матричном коммутационном устройстве требуется пара команд программы коммутации, одна из которых содержит параметры горизонтальной части пути, а другие аналогичные параметры вертикальной части пути.

Команда программы коммутации (фиг. 3) содержит поля, КОП-код операции.

НИЛК - номер информационной линии в коммутаторе;

-номер коммутатора в матричном коммутационном устройстве;

-признак ориентации информационной линии, причем П 1 1, если информационная линия горизонтально ориентированная;

П 1 0, если информационная линия вертикально ориентированная;

-признак - одноразрядный позиционный код установки направления передачи, причем П 2 1, „ если требуется установка направления передачи из горизонтальной информационной линии

в вертикальную, в противном случае П 2 0.

-признак-одноразрядный позици- оньый код режима установки направления передачи (П 3 О стирание направления).

Матричное коммутационное устройство (фиг. 4) содержит матрицу коммутаторов, элементами которой являются коммутаторы 46.11-46.mn, причем информационные входы (выходы) 29.1- 29.М коммутаторов в каждой строке матричного коммутационного устройст- ва подключены к входной (выходной) шине 29.k (k ) строки, а в каждом столбце информационные выходы (входы) коммутаторов - к выходной (входной) шине 28.1 (1 1,п) столбца; входы 15 выбора коммутатора в строке соединены в каждой строке коммутаторов и образуют вход 15.k выбора строки коммутаторов, а входы 16 выбора коммутатора в столбце соединены в каждом столбце коммутаторов и образуют вход 16.1 выбора коммутаторов в столбце; первые управляющие входы 30 коммутаторов объединены в первый управляющий вход 30 матрнчП 3

0

5

ного коммутационного устройства, а вторые управляющие входы 31 коммутаторов во второй управляющий вход 31 матричного коммутационного устройства; входы 25 установки направлений в горизонтальных информационных линиях коммутаторов матричного коммутационного устройства объединены в одноименный вход 25 матричного коммутационного устройства, а входы 26 установки направлений в вертикальных информационных линиях коммутаторов матричного коммутационного устройства - в одноименный вход 26 матричного коммутационного устройства,

Первые адресные входы 13 коммутаторов объединены в первую адресную шину 13 матричного коммутационного устройства, а вторые адресные входы 14 коммутаторов объединены во вторую адресную шину 14 матричного коммутационного устройства.

Матричное коммутационное устройство функционирует следующим образом.

На входы матричного коммутационного устройства (фиг. 4) подается информация из состава команды программы коммутации (фиг. 3).

На вход 25 установки направлений в горизонтальных информационных линиях и вход 26 установки направлений в вертикальных информационных линиях матричного коммутационного устройства подается соответственно одноразряд- ный позиционный код направления обмена (признак П 2) в горизонтальных и вертикальных информационных линиях.

На вход 15.k выборки k-rt строки коммутаторов и вход 16.1 выборки 1-го столбца коммутаторов подается в раскодированном виде позиционный код номера строки НСК (т.е. k) и номера столбца НСК (т.е. 1) коммутаторов, в результате чего производится выбор- ка соответствующего коммутатора.

По первой 13 и второй 14 адресным шинам матричного коммутационного устройства подаются соответственно на первый 13 и второй 14 адресные входы каждого коммутатора двоичный код номера вертикальной информационной линии ШШК (В) и двоичный код номера горизонтальной информационной линии НИЛК (Г) коммутатора.На первый 30 и второй 31 управляющие входы матричного коммутационного устройства подается соответственно одноразрядный позиционный код

(признак П2) для установки второго 5 дешифратора коммутатора в состояни Все единицы.

Информация по шинам матричного комутационного устройства поступает далее на соответствующие входы коммутаторов в том числе и на входы выбранного коммутатора. Работа выбранного коммутатора поясняется ниже, при этом предварительно поясняются особенности работы дешифраторов коммутатора.

Однофазные выходы 9.1-9.М первого дешифратора 4 (фиг. 1) и однофазные выходы 10.1-10.N второго дешиАрато- ра 5 при установлении и стирании соединений и направлений применяются для выборки элементов в соответствующих матрицах коммутатора. ПараФазные выходы 9.1-9.М первого дешифратора 4 применяются для установки запоминающих элементов 1.11... 11.MN прямоугольной матрицы в необходимое состояние. Напряжением логический ноль, которое подается на второй управляющий вход первого дешифратора 4 только при стирании соединений и направлений, парафазные выходы этого дешифратора блокируются, т.е. на них формируются парафазные напряжения с ло- лическим уровнем для установки в ноль запоминающих элементов. При установлении соединений и направлений на второй управляющий вход первого дешифратора 4 подается напряжение с уровнем лог. единицы и блокирования парафазных выходов 9.1-9.М этого дешифратора не происходит, т.е. функционируют и однофазные и парафазные выходы 9.1-9.М одновременно.

Напряжение, имеющее уровень лог. единицы, с выхода 10.J второго дешифратора 5 (т.е. позиционный код НИЛК (В) подается на первый вход блока 19.1J установки направления и на однофазные входы запоминающих элементов 1.1J-1.MJ j-столбца и j-ro запоминающего элемента 3.1J, и производит выборку этих элементов.

Парафазное напряжение, имеющее уровень лог. единицы (нуля), с пара- фазного выхода 9.1 первого дешифратора 4 подается на парафазный вход запоминающего элемента 1.ij выбран- ого столбца и устанавливает его в единичное (нулевое) состояние.

Напряжение, имеющее уровень лог. единицы, с однофазного выхода 9.1

10

15

20

25

91569965

первого дешифратора 4, т.е. позиционный код НИЛК (Г), подается на первый вход блока 20.11 установки направления и на однофазный вход 1-го запоминающего элемента 21.il и производит выборку этого элемента.

Парафазное напряжение, имеющее уровень лог.единицы (нуля), с пара- фазного выхода 33 второго элемента И 32 подается на парафазный вход выбранных запоминающих элементов 3.1J. и 21.i1 и устанавливает эти элементы в единичное (нулевое) состояние.

На вторые входы блоков 19.1J и 20.11 установки направления подаются напряжения лог. единицы соответственно с установленного запоминающего элемента 3.1J матрицы строки и установленного запоминающего элемента 21.11.

На третий вход блоков 19. 1j и 20.il установки направления подаются соответственно признак П 2 установки направления в вертикальной информационной линии и аналогичный признак П 2 установки направления в горизонтальной информационной линии.

Поясняется работа блока 19.1J установки направления.

Управление работой блока 19.1j установки направления сводится к управлению по второму входу состоянием первого 34 и второго 35 элементов Е (каждый элемент Е устанавливается в третье состояние при подаче на его второй вход напряжения с логическим уровнем ноль).

Прямое направление передачи информации в блоке 19. 1j установки направения, т.е. с информационного входа (выхода) 8.j через первый элемент Е 34 на информационный выход (вход) 28.j устанавливается, если на второй вход первого элемента Е 34 подается ог. единица, а на второй вход второго элемента Е 35 лог. ноль. Обратное направление передачи инормации в блоке 19.1J установки наравления, т.е. с информационного выода (входа) 28.j через второй элеент Е 35 на информационный вход (выод) 8.J устанавливается, если на втоой вход первого элемента Е 34 подаетя лог. ноль, а на второй вход второ- ее о элемента Е 35 лог. единица.

Напряжение лог. единицы с третьего хода 10.j блока 19. 1j установки наравления подается на однофазный вход

30

35

40

45

50

э а (

л н н л у н г

Ф

р му жи щи ц мы ма эл де ли ци хо

па эл

10

15

20

5

965

е

0

5

0

10

запоминающего элемента 39, предназначенного для запоминания направления передачи информации в блоке, и произг водит выборку этого элемента. Установка запоминающего элемента 39 в единичное (нулевое) состояние производится с выхода 42 первого элемента И 36 парафазным напряжением с уровнем лог.единицы (нуля).

Напряжение лог.единицы с второго входа блока 19.1j установки направления подается на вторые входы второго 37 и вторые входы третьего 38 элементов И, в результате чего производится выборка блока 19.1J установки направления, так как эти элементы открываются по вторым входам.

Напряжение лог.единицы (нуля) с выхода 43 элемента 39 подается на первые входы второго 37 и первые входы третьего 38 элементов И. При этом на выходе 44 второго элемента И 37 формируется лог.единица (ноль), на выходе 45 третьего элемента И 3-6 Формируется лог.ноль (единица), устанавливают по вторым входам первый элемент Е 34 в рабочее (высокоомное), а второй элемент Е 35 в высокоомное (рабочее) состояния.

Запоминающий элемент 39 устанавливается в единичное (нулевое) соетоя- ние парафазным напряжением лог.единицы (ноль) с выхода 42 первого элемента И 36, которое формируется, если на первый вход 24 блока 19.1J установки направления подается признак П 2 1 (П 2 0), а на два другие входа этого блока напряжения с уровнем лог.единицы.

Формула изобретения

1. Матричное коммутационлое устройство, содержащее матрицу коммутаторов, каждый из которых содержит прямоугольную матрицу запоминающих элементов из М строк и N столбцов, прямоугольную матрицу управляемых ключей из М строк и N столбцов, матрицу-строку из N запоминающих элементов, первый дешифратор, второй дешифратор, первый элемент И, i (i 1 ,М) горизонтальных информационных линий иj (,N) вертикальных информационных линий,причем i-й парафазный выход первого дешифратора соединен с

парафазными входами запоминающих элементов i-й строки прямоугольной

матрицы, j-й выход второго дешифратора соединен с однофазными входгши запоминающих элементов j-ro столбца прямоугольной матрицы однофазным входом j-ro запоминающего элемента матрицы-строки, парафазный выход первого элемента И соединен с парафазным входом первого дешифратора, i-ная горизонтальнал информационная линия JQ соединена с первыми входами управляемых ключей i-й строки, j-ная вертикальная линия соединена с вторыми входами управляемых ключей j-ro столбца, выход из запоминаю- 15 щих элементов прямоугольной матрицы соединен с входом соответствующего ключа из состава прямоугольной матрицы управляемых ключей, информационный вход первого дешифратора и инфор- 20 запоминающего элемента матрицы-строки мационный вход второго дешифратора соединен с вторым входом j-ro блока

ления матрицы-столбца, выход i-ro запоминающего элемента матрицы-столбца соединен с вторым входом 1-го блока установки направления матрицы- столбца, выход первого формирователя соединен с третьими входами блоков установки направлений матрицы-столбца, выход второго формирователя соединен с третьими входами блоков установки направлений матрицы -строки, вход первого и вход второго Формирователей являются соответственно входом установки направлений в горизонтальных и вертикальных информационных линиях коммутатора, j-й выход второго дешифратора соединен с первым входом j-ro блока установки направления в матрице-строке, выход j-ro

запоминающего элемента матрицы-строки соединен с вторым входом j-ro блока

ления матрицы-столбца, выход i-ro запоминающего элемента матрицы-столбца соединен с вторым входом 1-го блока установки направления матрицы- столбца, выход первого формирователя соединен с третьими входами блоков установки направлений матрицы-столбца, выход второго формирователя соединен с третьими входами блоков установки направлений матрицы -строки, вход первого и вход второго Формирователей являются соответственно входом установки направлений в горизонтальных и вертикальных информационных линиях коммутатора, j-й выход второго дешифратора соединен с первым входом j-ro блока установки направления в матрице-строке, выход j-ro

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Коммутатор | 1987 |

|

SU1434541A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для определения характеристик связности ориентированного графа | 1983 |

|

SU1133596A1 |

| Коммутационное устройство | 1989 |

|

SU1621041A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

Изобретение относится к электронной технике и может быть использовано для построения наращиваемых интерфейсов параллельного действия в вычислительной технике. Цель изобретения - расширение частотного диапазона коммутируемых сигналов в матричном коммутационном устройстве при обмене в обратном направлении - достигается за счет того, что матричное коммутационное устройство представляет собой прямоугольную матрицу коммутаторов размерами M.N, причем для достижения цели в состав каждого коммутатора, содержащего M горизонтальных и N вертикальных информационных линий, прямоугольную матрицу запоминающих элементов размерами M.N, матрицу управляемых ключей размерами M.N, матрицу-строку из N запоминающих элементов, введены первый и второй формирователи, матрица-столбец из M блоков установки направлений таким образом, что каждой горизонтальной информационной линии придан свой блок, матрица-столбец из M запоминающих элементов, матрица-строка из N блоков установки направлений таким образом, что каждой вертикальной информационной линии придан свой блок, в каждой строке матричного коммутационного устройства информационные входы коммутаторов подключены к входной шине строки, а в каждом столбце матричного коммутационного устройства информационные выходы коммутаторов подключены к выходной шине столбца. 3 з.п. ф-лы, 4 ил.

являются соответственно первым и вторым адресными входами коммутатора, первый вход первого элемента И является входом выбора коммутатора в строке матрицы коммутаторов, второй вход первого элемента И соединен с первым входом второго дешифратора и является входом выбора коммутатора в столбце матрицы коммутаторов, информационные входы (выходы) коммутаторов в каждой строке матричного коммутационного устройства подключены к входной (выходной) тине строки, а в каждом столбце информационные выходы (входы) коммутаторов - к вы- ходно.й (входной) шине столбца, входы выбора коммутатора в каждой с-троке объединены и образуют вход выбора соответствующей строки, а входы выбора коммутатора в каждом столбце соединены и образуют вход выбора соответствующего столбца, отличающееся тем, что, с целью расширения частотного диапазона коммутиру емых сигналов при обратном направлении обмена, в состав каждого коммутатора матричного коммутационного устройства дополнительно введены первый и второй формирователи, матрица- строка из N блоков установки направлений, матрица-столбец из М запоминающих элементов и матрица-столбец из М блоков установки иапр ,i лий, второй элемент И, i-й одной ьый выход первого дешифратора соединен с однофазным входом 1-го запоминающего элемента матрицы-столбца и первым входом i-го блока установка направ

5

0

5

0

0

5

установки направления матрицы-строки, j-ная вертикальная информационная линия соединена с информационным входом (выходом) j-ro бло 1 установки направления матрицы-строки, i-ная горизонтальная информационная линия соединена с информационным выходом (входом) i-ro блока установки направления матрицы-столбца, вход ..выход) 1-го блока установки направления является i-м входом (выходом) коммутатора, пятый информационный выход (вход) j-ro блока установки направления матрицы-строки является j-м информационным выходом (входом) коммутатора, второй управляющий вход первого дешифратора и второй управляющий вход второго дешифратора являются соответственно первым и вторым управляющими входами коммутатора, парафазный выход второго элемента И соединен с парафазными входами запоминающих элементов матрицы-строки и запоминающих элементов матрицы- столбца, второй управляющий вход первого дешифратора соединен с первым входом второго элемента И, первая линия парафазного выхода первого элемента И соединена с вторым входом второго элемента И, первые и вторые управляющие входы коммутаторов объединены соответственно с первым и вторым управляющими входами Maip., го коммутационного у. тройства . .Е-Х - ды установки направлений в горизон- тг тьных и вертикальных линиях коммутаторов соответственно объединены и fi .,iovi,;T однои еш П ах иди млтричного коммутационного устройства, первые и вторые адресные входы коммутаторов соответственно объединены и образуют одноименные входы матричного коммутационного устройства.

25

20„

-т/а -7/5/j -Г Уг

р4РШНГг

3„2 3,2Ц 3,327а ГЗп,Ц.

2Эн

третий входы первого элемента И являются соответственно первым, вторым и третьим входами блока установки направления, парафазный выход первого элемента И соединен с парафазным входом запоминающего элемента, выход которого соединен с первым входом второго н первым входом третьего элементов И, второй вход первого элемента И соединен с вторым входом второго элемента И и вторым входом третьего эпемента И, выход второго элемента И соединен с вторым входом первого элемента Е, выход третьего элемента И соединен с вторым входом второго элемента Е, однофазный вход запоминающего элемента соединен с третьим входом первого элемента И.

28

N

30

Фиг./

J

29r M

Фиг.З

16п

| Макаревич О.Б | |||

| и др | |||

| МДП БИС для коммутационных систем телефонии | |||

| Зарубежная электронная техника, 1977, № 15, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-07—Публикация

1988-08-17—Подача