1

(21)4659319/21

(22)06.03.89

(46) 23,04.91, Бнш. fr 15

(72) Д,В. Бородин, 3.F. Поварницына,

ВСН. Богатырев и К„В0 Егоров

(53)621.382(088.8)

(56)Патент СГ1А № 3720848, кл. Н 03 К 17/60, 13,03073о

Авторское свидетельство СССР № 1078616, клс Н 03 К 17/60, 17.12.82.

(54)МНОГОКАНАЛЬНЫЙ КОММУТАТОР

(57)Изобретение относится к импульсной технике и может быть использовано в многоканальных устройствах электронной коммутации Цель изобретения - увеличить быстродействие при сохранении высокой надежности за счет оптимизации зарядного (разрядного) тока емкости нагрузки. Указанная оптимизация достигается использованием в многоканальном коммутаторе блока управления сопротивлением аналогового ключевого КМОП- элемента. Коммутатор содержит в каждом канале инвертор 1, аналоговые ключевые КМОП-элементы 2 и 3, элемент задержки 4, МОП-транзисторы р-типа 9 и 10, МОП-транзисторы п- типа 11 и 12, резисторы 13-16, конденсаторы 17 и 180 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1982 |

|

SU1078616A1 |

| Многоканальный коммутатор | 1989 |

|

SU1723667A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| Ключевой элемент | 1984 |

|

SU1202048A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ (ВАРИАНТЫ) | 2007 |

|

RU2361321C1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| Многоканальный коммутатор аналоговых сигналов | 1982 |

|

SU1034183A1 |

(Л

9 t

:о

sl

tt

ZiI

Изобретение относится к импульсной технике и может использоваться в многоканальных устройствах электронной коммутации

Цель изобретения - увеличение быстродействия устройства при сохранении его высокой надежности за счет оптимизации зарядного (разрядного) тока емкости нагрузки.

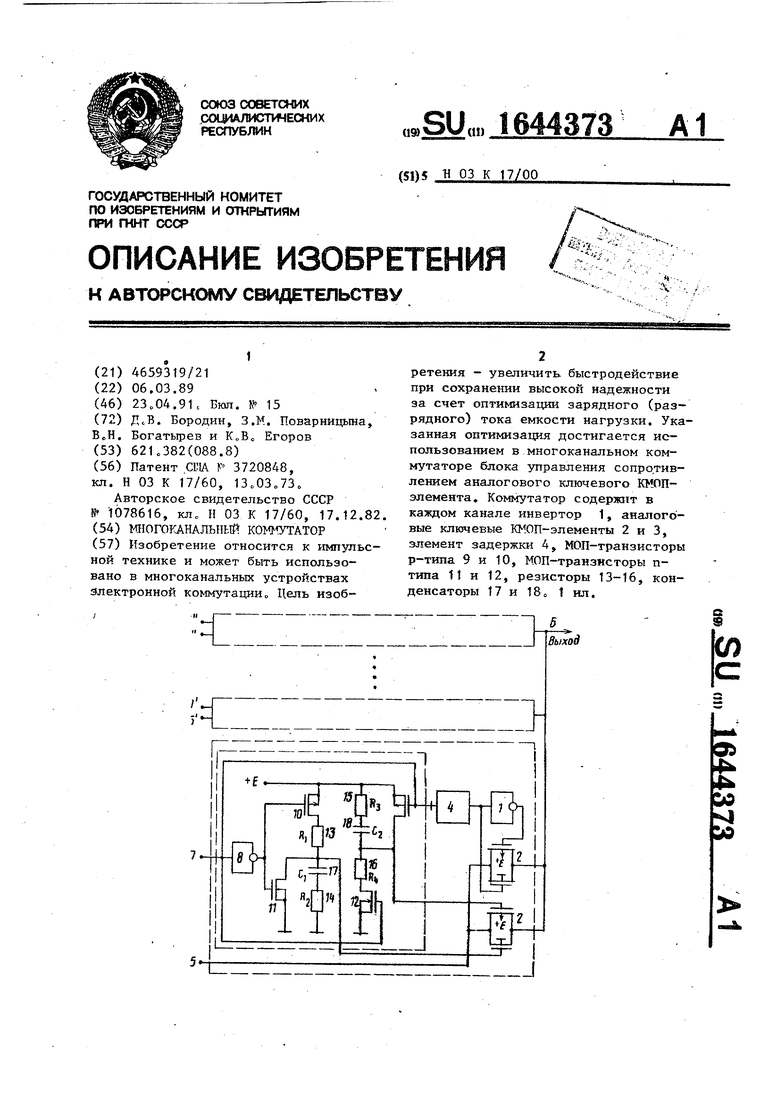

На чертеже приведена функциональная схема многоканального коммутатора.

Коммутатор содержит в каждом канале инвертор 1, первый 2 и второй 3 аналоговые ключевые КМОП-элементы, элемент 4 задержки, аналоговый вход 5, аналоговый выход 6 коммутатора, вход 7 управления и блок управления напряжением на затворах МОП-транзисторов второго аналогового ключевого КМОП-элемента, построенного на инверторе 8, МОП-транзисторах р-типа 9 и 10, МОП-транзисторах п-типа 11 и 12, резисторах 13-16 (сопротивлением R,. R, Р--3 и 4 соответственно) конденсаторах 17 и 18 (емкостью С и С г соответственно),

Устройство работает следующим образом.

Когда на вход 7 управления подан логический О, устройство находится в исходном состоянии: аналоговый ключевой элемент 2 закрыт, транзисторы 9 и 11 открыты, транзисторы 10 и 12 закрыты и тем самым конденсатор 17 разряжен, потенциал обеих обкладок конденсатора 18 равен Е, аналоговый ключевой элемент 8 закрыт„ При подач на вход 7 управления потенциала логи ческой 1 (равного Е) транзисторы 9 и 11 закрываются, транзисторы 10 и 12 открываются и блок управления напряжением на затворах МОП-транзисторов второго аналогового ключевого КМОП-элемента 3 формирует необходимые управляющие воздействия„

В первый момент времени на затвор МОП-транзистора n-типа (р-типа) второго аналогового ключевого КМОП- элемента подается напряжение

I §JL,E/n Е4г/

- R,+ R 2- R,+ Rd E/

. т i,. «- Kjt- «.4 Соотношение величин резисторов R } и R(RjHR({.) выбирается таким, чтобы U, было б олыпе Ur, но меньше Е (соответственно Ug больше 0, но меньше Е - UT). Отношение размеров W/L для МОП-транзисторов п- и р-типа второго

10

44373й

аналогового ключевого элемента 3/W-V, L - длина канала) выбирается соответствующим максимальной мощности в начальный момент времени. Так в начальный момент времени предлагаемая схема обеспечивает необходимый зарядный (разрядный) ток конденсатора нагрузки.

Е предлагаемом коммутаторе с течением времени конденсаторы 17 и 18 заряжаются, и потенциалы, поданные на затворы МОП-транзисторов п- и р- типа второго элемента 3, изменяются

и2 до о

соответствен.с U j до Е и с

но. Следовательно, сопротивление второго аналогового ключевого элемента 3 с течением времени уменьшается. Тем самым конденсатор нагрузки разряжается за существенно меньшее время, чем в схеме прототипа. Поэтому время задержки элемента 4 задержки может быть уменьшено. Тем самым уменьшается и общее время передачи аналогового напряжения коммутатором. В дальнейшем, при подаче на вход 7 управления логического О транзисторы 9 и 11 открываются, транзисторы 10 и 12 закрываются, конденсаторы 17 и 18 разряжаются и схема возвращается в исходное состояние. Для того, чтобы время подготовки к работе было мало, необходимо, чтобы транзисторы 9 и 11 имели малое сопротивление в открытом состоянии.

0

0

Ф о

и з о б

5

рмула изобретения

Многоканальный коммутатор, содержащий в каждом канале элемент задержки, инвертор, первый и второй аналоговые ключевые КМОП-элементы, каждый из которых состоит из МОП-транзистора р-типа и МОП-транзистора n-типа проводимости, подложка которого соединена с общей шиной, исток соединен со стоком МОП-транзистора р-типа и является соответствующим аналоговым входом ключевого элемента, причем входы аналоговых ключевых элементов канала объединены и являются аналоговым входом канала, сток, являющийся аналоговым выходом ключевого элемента, соединен с истоком МОП-транзистора р-типа, подложка которого соединена 5 с шиной источника напряжения, причем выходы всех ключевых КМОП-эле- ментов объединены и являются аналоговым выходом коммутатора, а затвор МОП-транзистора р-типа первого ана

логового ключевого ЮЮП-элемента соединен с выходом инвертора, вход которого соединен с затгором МОП-транзистора n-типа первого аналогового ключевого КМОП-элемента и выходом элемента задержки, вход которого соединен с соответствующим входом управления коммутатора, отличающийся тем, что, С целью увеличения быстродействия при сохранении высокой надежности, в каждый канал введен блок управления напряжением на затворах МОП-транзисторов второго аналогового ключевого КМОП-элемента, вы- полненный на первом резисторе, первый вывод которого подключен к стоку второго МОП-транзистора р-типа, второй вывод - к первой обкладке первого конденсатора, затвору МОП-транзистора n-типа второго аналогового ключевого КМОП-элемента и стоку второго МОП-транзистора n-типа, вторая обкладка первого конденсатора подключена к первому вьюоду второго резистора, второй вывод которого подключен к общей шине, третьем резисторе, пер

10

управления43736

вый вывод которого подключен к шине питания, второй вывод - к первой обкладке второго конденсатора, вто- рая обкладка которого подключена к затвору МОП-транзиСтора р-типа второго аналогового ключевого КМОП- элемента, стоку первого МОП-транзистора р-типа и первому выводу четвертого резистора, второй вывод которого подключен к стоку первого МОП-транзистора n-типа, затвор которого и затвор первого МОП-транзистора р-типа подключены к соответствующей шине

а исток и подложка - к общей шине, исток и подложка первого и второго МОП-транзистора р-типа подключены к шине питания, исток и подложка второго МОП-транзистора n-типа подключены к общей шине, а его затвор и затвор второго МОП- транзистора р-типа - к выходу инвертора, вход которого подключен к соответствующей шине управления, затвор первого МОП-транзистора р-тнпа соединен с входом элемента задержки.

20

25

Авторы

Даты

1991-04-23—Публикация

1989-03-06—Подача