Изобретение относится к электротехнике и может быть использовано в системах автоматического управления тиристорными преобразователями с, 1

Цель изобретения - расширение функциональных возможностей, а также повышение качества трехфазной системы напряжений путем уменьшения асимметрии и повышения стабильности фазовых 2 сдвигов в диапазоне перестройки частоты, повышения стабильности частоты в автоматическом режиме„

На фиго 1 представлена функциональная схема предложенного преобразователя; на фигс 2 - характеристика вход выход блока контроля частоты; на фиг„ 3 - векторные диаграммы напряжений преобразователя фаз с

Устройство для преобразования однофазного напряжения в трехфазное содержит однофазный генератор 1 с управляющим и синхронизирующим входами, логическое устройство 2 с тремя входами,

преобразователь , фаз 3 с двумя входа„ , Ч

ми и шестью выходами, первый 4 и вто- J рой 5 усилители-ограничители, датчик 6 фазового рассогласования, интегрирующий блок 7, стабилизатор 8 фазового сдвига и источник 9 синхронизирующего сигнала, причем управляющий и синхронизирующий входы однофазного генератора 1 подключены соответственно к выходу интегрирующего блока 7 и выходу логического устройства 2 первый и второй входы которого соединены с выходом первого 4 и выходом второго 5 усилителей-ограничителей, вход однофазного генератора 1 соединен с первым выходом преобразователя фаз 3 и входом стабилизатора 8 фазового сдвига, выход которого соединен с вторым входом преобразователя фаз 3, первый выход которого соединен с входом первого усилителя-ограничителя 4 и первым выходом 10 устройства для однофазного преобразования напряжения в трехфазное, второй 11, третий 12, четвертый 13„ пятый 14 и шестой 15 выходы которого

5

J

0

0

соединены с вторым, третьим, четвертым, пятым и шестым выходами преобразователя фаз 3, в У. од интегрирующего блока 7 подключен к выходу датчика 6 фазового рассогласования, первый и второй входы которого соединены с выходом первого 4 и выходом второго 5 усилителей-ограничителей, третий вход логического устройства 2 соединен с входом второго усилителя-ограничителя 5, причем в однофазном генераторе 1, выполненном из дифференциального усилителя 16 постоянного тока, стабилизатора 17 амплитуды, первого 18 и второго 19 конденсаторов, первого 20, второго 21, третьего 22, четвертого 23 и пятого 24 резисторов, стабилизатор 17 амплитуды включен между выходом и инвертирующим входом дифференциального усилителя 16 постоянного тока, к неинвертирующему входу которого подключены одним выводом второй конденсатор 19 и второй резистор 20, второй вывод которого соединен с общей шиной9 между инвертирующим входом дифференциального усилителя 16 постоянного тока и общей шиной включены последовательно соединенные третий 22 и четвертый 23 резисторы, синхронизирующий вход и выход однофазного генератора 1 соединены с первым выводом пятого резистора 24 н выходом дифференциального усилителя 16 постоянного тока, к выходу которого одним выводом подключен первый резистор 20, второй вывод которого соединен с выводом первого конденсатора 18, второй вывод пятого резистора 24 соединен с инвертирующим входом дифференциального усилителя 16 постоянного тока Первый и второй входы логического устройства 2, состоящего из датчика 25 напряжения, триггера 26, первого 27 и второго 28 формирователей узких импульсов, логической схемы И 29 с двумя входами и реле 30 с замыкающим контактом 31 соединены с входами первого 27 и второго 28 фор

мирователей узких импульсов, выхода которых соединены с первым и вторым входами логической схемы И 29, выход которой соединен с первым входом триггера 26, к выходу которого подключено реле 30, один вывод замыкающего контакта 31 которого соединен с третьим входом логического устройства 2 и входом датчика 25 напряжения, а другой вывод соединен с выходом логического устройства 2, при этом однофазнъв генератор 1 включает в се бя также аналоговый перемножитепь 32 третий конденсатор 33, шестой 34, седьмой 35 и восьмой 36 резисторы, причем первый и второй входы и выход аналогового перемножителя 32 подключены соответственно к инвертирующему входу дифференциального усилителя 16 постоянного тока, управляющему входу однофазного генератора 1 и общей точке соединения третьего 22 и четвертого 23 резисторов, третий конденсатор 33 включен между инвертирующим входо дифференциального усилителя 16 постоянного тока и общей шиной, шестой резистор ЗА включен между выходом и инвертирующим входом дифференциального усилителя 16 постоянного тока, седьмой резистор 35 подключен параллельно первому конденсатору 18, свободный вывод которого соединен с общей шиной и свободным Bbroo O Vi второго конденсатора 19, восьмой резистор

36одним выводом подключен к общей точке соединения первого конденсатора 18 и первого резистора 20, а другим - к неинвертирующему входу дифференциального усилителя 16 постоянного тока

Логическое устройство 2 включает в себя также блок 37 контроля частоты и логическую схему ИЛИ 38 с двумя входами, причем вход и выход блока

37контроля частоты соединены с третьим входом логического устройства 2 и первым входом логической схемы ИЛИ 38, второй вход и выход которой подключен к выходу датчика 25 напряжения и второму входу триггера 26, а между источником 9 синхронизирующего сигнала и третьим входом логического устройства 2 дополнительно включен стабилизатор 39 синхросигнала

Преобразователь фаз 3 выполнен из первого 40 и второго 41 сумматоров, первого 42, второго 43 и третьего 44 инверторов, причем первый вход пресб

0

5

разопатсля фаз 3 со диген с первыми входами первого 40 и второго 4 сумматоров , с входом первого инвертора 42 и первым выходом преобразователя фаз 3, второй вход которою соединен с вторым входом первого суьаттора ;tO, выход которого соединен с вторым входом второго сумматора 41, с входом третьего инвертора 44 и пятим выводом 14 преобразователя фаз 3, второй 11, третий 12, четвертый 13 ц шестой 15 выходы которого соединены с выходами первого инвертора 42, второго сумматора М, второго 43 и третьего 44 ин- рертпров, а выход второго сумматора 41 соединен с входом второго инвертора 43 о

стройство работает следующим образом

Однофазньй генератор 1 содержит дифференциальный усилитель 16 постоянного тока, стабилизатор 17 амплитуды, частотно-задающие элементы: конденсаторы 18 и 19, резисторы 20, 21, 34, 35 и 36 и управляемый резистор, выполненный из резисторов 221 и 23 и аналогового перемножитьля

1-у

25

30

Напряжение на выходе аналогового

перемножителя 32 определяется как

U

гг

м

Ей

где Ки - коэффициент передачи множительного устройства 32; напряжение на управляющем входе генератора 1; напряжение на инвертирующем входе дифференциального усилителя 16 постоянного тока. Разность напряжений ( - ределяет величину тока щего через резистор 22, поэтому величина управляемого резистора

UJ2) on- 122, протекаюR,

U 06

х«

и я

(

0

R22/(1 КмЕу

И ).

22

Для обеспечения возбуждения колебаний в генераторе конденсатор 33 выбирается из условия

5

33 + С

)

с

36 + Rio ( ЗФ

+Ј)

К2,

RZO

R

34

Ъ6

),

а частота возникающих колебаний определяется выражением

R2i+Ri6 . R2on . R34 ,

f - - ( Z T У2

r / I/ T TlJ

21

R

70

R

36

18 Ъ19

Отсюда следует, что, изменяя сопротивления резистора Ru, (напряжение управления ЕЧ), можно менять частоту выходного Сигнала, не нарушая при этом условия возбуждения, т.е„ такой генератор является генератором с одним управляемым резистором, в котором при перестройке частоты в рабочем диапазоне амплитуда выходных колеба- ний остается постоянной„

Через резистор 24 поступает синхронизирующий сигнал на инвертирующий вход дифференциального усилителя 16 постоянного тока однофазного генера- тора 1 с

Для уменьшения влияния уровня синхросигнала на амплитуду и форму выходных колебаний однофазного генератора 1 к выходу источника 9 синхронизирующего сигнала подключен стабилизатор 39 синхронизирующего сигнала, который поддерживает амплитуду синхросигнала на постоянном уровне„

При отсутствии напряжения на нсточ пике 9 синхронизирующего сигнала, на выходах датчика 25 напряжения блока 37 контроля частоты и логической схемы ИЛИ 38 присутствуют сигналы с уровнем Г с Триггер 26 устанавливается в такое положение, при котором контакт 31 реле 30 логического устройства 2 разомкнут и интегрирующий блок 7 выдает на выходе постоянное напряжение, определяющее собственную час- тоту однофазного генератора 1 в автономном режиме „

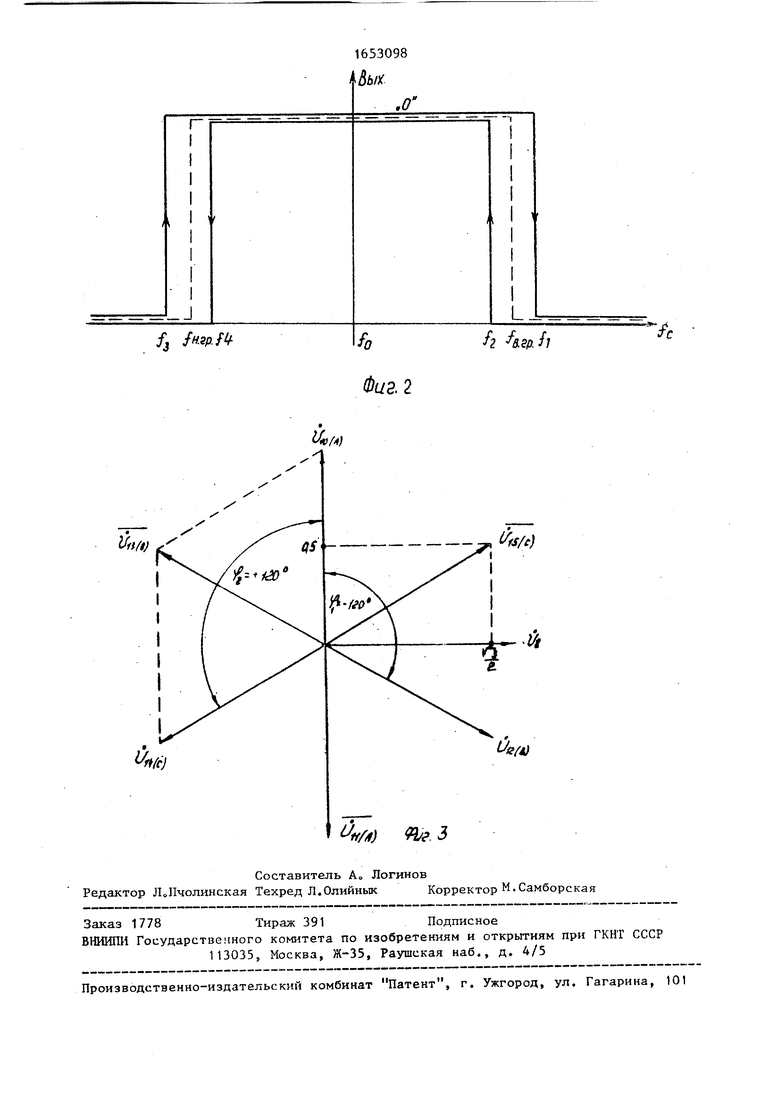

При появлении напряжения на выходе источника 9 синхронизирующего сигнала на выходе датчика 25 напряжения, а следовательно, и на первом входе логической схемы ИЛИ 38 появляется сигнал О, Однако уровень сигнала на втором входе триггера 26 не изменяется до тех пор, пока на втором входе логической схемы ИЛИ 38, т.е„ |на выходе блока 37 контроля частоты, также не появляется сигнал О1 . Это происходит только в том случае, когда частота синхросигнала нахо- дится в допустимых пределах (фиг„2),

Верхний ferp и нижний f граничные пороги срабатывания блока 37 контроля частоты выбираются исходя

5

5

0

5 0

5 Q

из допустимых отклонений частоты синхросигнала от номинального значения Ј0.

При нахождении частоты синхросигнала в допустимых пределах fe.rp fвх5 fHrn на выходе блока 37 контроля частоты присутствует сигнал с уровнем В этом случае с второго входа триггера 26 снимается сигнал 1 и триггер 26 подготавливается к переключению по первому входу„

Первый А и второй 5 усилители-ограничители формируют прямоугольные сигналы из гармонических сигналов, однофазного генератора 1 и источника 9 синхронизирующего сигналас

Формирователи 27 и 28 узких импульсов логического устройства 2 формируют импульсы при переходе через нуль кривых напряжения однофазного генератора 1 и источника 9 синхросигнала,. Сформированные импульсы поступают на первый и второй входы логической схемы И 29 и в момент совпадения триггер 26 переводится в такое состояние, при котором включаются реле 30, переводя интегрирующий блок 7 в режим интегрирования и замыкая замыкающий контакт 31 „

При этом однофазный генератор 1 входит в режим захватывания частоты и работает синхронно на частоте источника 9 синхросигналао Если собственная частота однофазного генератора 1 и источника 9 синхросигнала равны между собой, то фазовый сдвиг между синхронизируемыми напряжениями отсутствует

При неравных частотах появляется фазовый сдвиг между напряжениями однофазного генератора 1 и источника 9 синхронизирующего сигнала, а на выходе датчика 6 фазового рассогласования появляются прямоугольные импульсы, длительность и полярность которых определяется величиной и знаком фазового рассогласования„

Импульсный сигнал, преобразованный интегрирующим блоком 7 в потенциальный, воздействует на управляющий вход однофазного генератора 1 и изменяет его частоту до тех пор,пока фазовый сдвиг не будет равен нулю, при этом собственная частота однофазного генератора 1 становится равной частоте источника 9 синхронизирующего сигнала

При нахождении измеряемой (контролируемой) частоты вблизи граничных

значении f ц гр и в гр блок 37 контроля частоты может легко срабатывать при любой лаже незначительной помехе, вызванной девиацией синхрп- сигнала но частоте„ Повышенна; поме- хоза1.рщенность обеспечивается за счет введения гнстерезисной характеристики (фиго 2) блока 37 контроля частоты,, Изменяя положение частот f,, f2 и f3, Ј4. можно регулировать зону нечувствительности, т„ев ширину гисгерезисной характеристики„

Действительно, если частота синхросигнала f изменяется от номинально- го значения fQ в сторону увеличения, то переключения не происходит до тех пор, пока Јс не превысит значения 1 „ Дальнейшее увеличение частоты Jс f, не изменяет состояния блока 37 конт- роля частоты

Если же частота синхросигнала начинает уменьшаться и опять достигает значения f 1 , то и в этом случае не произойдет обратного переключения бло ка 37 контроля частоты, пока частота синхросигнала не достигнет значения i Аналогично работает блок 37 контроля частоты и при изменении частоты синхросигнала в сторону уменьшения, т.е„ при нахождении Ч„ вблизи нижней граничной частоты

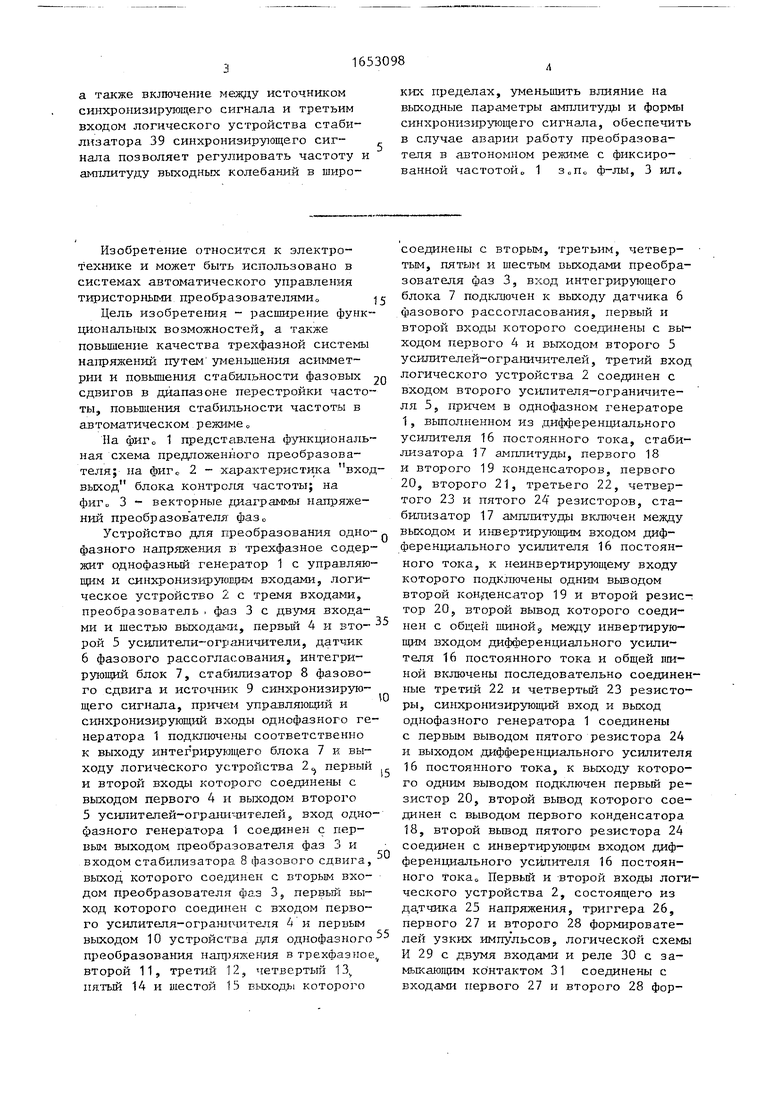

Система трехфазных напряАлшй (фиг„ 3) получается в преобразователе фаз 3 путем геометрического с ммиро- валия в требуемых пропорциях ортогональных синусоидальных напряжений: выходного напряжения однофазного генератора 1 и выходного напряжения стабилизатора 8 фазового сдвига,обес- печиваюцего постоянный фазовый сдвиг (РО u /Z в рабочем диапазоне частот„

С помощью первого сумматора 40, который является инвертирующим, суммируются векторы напряжения Ug и и10/-д) Коэффициент передачи сумматора 40 по первому входу равен 1/2, по второму л|з/2 в результате на выходе сумматора 40 появляется напряжение

1 - Л 14(сГ U о + 2 6 сдвинутое на угол

Ц1, +120 эл о град, по отношению к напряжению и,0(д)с

С помощью второго сумматора 41, который также является инвертирующим, суммируются векторы (ДчИ )- Ко эфуициенты передачи сумматора 41 по первому и второму входам равны единице, поэтому на выходе сумматора 41

полвгпетея мапряи-гние Игз(6| Ь,0( ц( сдвину гпе мл vrnji Ср2 - - i 2d :кт .: р;;д. по отношение к нс.ходному наир/г ению -ТЮ(А)

Tai им образом, на впхо.илх 10, 1 и 1 пре Пратонате.гя ,гии.го на- прякенля в трехфазное формн1,ч:тся сШ Пчотричпая трехфазп,1ч гнсгома напряжений Гд, Ug, U. , а на выхо-. дах 11,13 и 15 - иниертированнан система симметричных .-:них ко- лебанш 11, Uft, Uc ,

Форму л а и з ,i б е т е н и я

1ь Устройство для преобразования однофазного напряжения в трехф з ме, содер.лацее o;;Hoi pa: HLDi генератор с управляюсшм и снзсхронизнр юиагм входами, логическое устройство с тремя входами, преобразователь фаз с двумя входами и шестью выходами, первый и второй усилители-ограничители, датчик фазового рассогласования, инге- rpupyioi tiui блок, стабилизатор фазового сдвига и источник синхронизирчюиего cnrH.uia, П ;ичем управляю ;): и синхронизирующий входы однофазного генератора подключены соответственно к выходу интегрирующего блока и к выходу логического устройства, первьп и второй входы которого соединены соответственно с выходом первого и выходом второго усилителей-ограничителей,выход однофазного генератора соединен с первым входом преоОразлзач еля фаз и с входом стабилизатора фазового сдвига, выход которого соединен с вторым входом преобразователя фаз, nepBLDi выход которого соединен с входом первого усилителя-ограничителя и с первым выходом устройства для преоб разовашш однофазного напряжения в трехфазное, второй, третий, четвер- тый, пятый и шестой выходы которого соединены в свою очередь соответственно с вторым, третьим, четвертым, пятым и шестым выходами преобразователя фаз, вход интегрирующего блока подключен к выходу датчика фазового рассогласования, первый н второй вход которого соединены соответственно с выходом первого и выходом второго усилителей-ограничителей, третий вход логического устройства соединен с входом второго усилителя-ограничителя, причем в однофазном генераторе, выполненном из дифференциального усилителя постоянного тока, стабилизатора амплитуды, первого и второго конденсаторов, первого, второго, третьего, четвертого и пятого резисторов, стабилизатор амплитуды включен между выходом и инвертирующим входом дифференциального усилителя постоянного тока, к неинвертирующему входу которого подключены одним выводом второй конденсатор и второй резистор, второй вывод которого соединен с общей шиной между инвертирующим входом дифференциального усилителя постоянного тока и общей шиной включены последовательно соединенные третий и четвертый резисторы, синхронизирующий вход и выход однофазного генератора соединены соответственно с одним выводом пятого резистора и выходом дифференциального усилителя постоянного тока, к выходу которого одним выводом подключен первый резистор, второй вывод которого соединен с выходом первого конденсатора, при этом в логическом устройстве, выполненном из датчика на пряжения, триггера, первого и второго формирователей узких импульсов, логической схемы И с двумя входами, и рел с контактом, первый и второй входы логического устройства соединены с входами соответственно первого и второго формирователей узких импульсов выходы которых соединены соответственно с первым и вторым входами логической схемы И, выход которой соеди- ненс первым входом триггера, к выходу второго подключено реле, один вывод контакта которого соединен с третьим входом логического устройства и входом датчика напряжения, а другой вы- вод соединен с выходом логического устройства, отличающееся тем, что, с целью расширения функциональных возможностей, а также повышения качества трехфазной системы на- пряжений путем уменьшения асимметрии и повышения стабильности фазовых сдвигов в диапазоне перестройки частоты, повышения стабильности частоты в автономном режиме, в однофазный генератор дополнительно введены аналоговый перемножитель, третий конденсатор, шестой, седьмой и восьмой резисторы, причем первый, второй входы

и выход аналогового перемножйтеля подключены соответственно к инвертирующему входу дифференциального усилителя постоянного тока, управляющему

0 5 0 с о 5 Q

5

входу однофазного генератора и общей точке соединения третьего и четвертого резисторов, третий конденсатор включен между инвертирующим входом дифференциального усилителя постоянного тока и общей шиной, шестой резистор включен между выходом и инвертирующим входом дифференциального усилителя постоянного тока, с которым соединены свободный вывод пятого резистора, седьмой резистор подключен параллельно первому конденсатору, свободный вывод которого соединен с общей ыиной и свободным выводом второго конденсатора, восьмой резистор одним выводом подключен к общей точке соединения первого конденсатора и первого резистора, а другим - к неинвертирующему входу дифференциального усилителя постоянного тока, при этом в логическое устройство дополнительно введены блок контроля частоты и логическая схема ИЛИ с двумя входами, причем вход и выход блока контроля частоты соединены соответственно с третьим входом логического устройства и первым входом логической схемы ИЛИ, второй вход и выход которого подключен соответственно к выходу датчика напряжения и к второму входу триггера, а между источником синхронизирующего сигнала и третьим входом логического устройства дополнительно включен стабилизатор синхросигналас

2„ Устройство по п0 отличающееся тем, что преобразователь фаз выполнен из первого и второго сумматоров, первого, второго и третьего инверторов, причем первый вход преобразователя фаз соединен с первыми входами первого и второго сумматоров, с входом первого инвертора и первым выходом преобразователя фаз, второй вход которого соединен с вторым входом первого сумматора, выход которого соединен с вторым входом второго сумматора, с входом третьего инвертора и пятым выходом преобразователя фаз, второй, третий, четвертый и шестой выходы которого соединены соответственно с выходом первого инвертора, выходом второго сумматора, выходом второго инвертора и выходом третьего инвертора, а выход второго сумматора соединен с входом второго инвертора,,

f3 /H.Spfl+

fo Фиг 2

$г f&yfj

fc

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь однофазного напряжения в трехфазное | 1988 |

|

SU1594665A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1786616A1 |

| Преобразователь однофазного напряжения в трехфазное | 1989 |

|

SU1679586A1 |

| Преобразователь однофазного напряжения в трехфазное | 1987 |

|

SU1432692A1 |

| Высоковольтный стабилизатор с изменяемой полярностью выходного напряжения | 1990 |

|

SU1800563A1 |

| Преобразователь однофазного напряжения в трехфазное | 1987 |

|

SU1450052A1 |

| Устройство передачи и приема информации по двухпроводной линии связи | 1989 |

|

SU1767511A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1775820A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| ФОРМИРОВАТЕЛЬ ТРЕХФАЗНЫХ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2014 |

|

RU2553418C1 |

Изобретение относится к электротехнике и может быть использовано в системах автоматического управления тиристог-ными преобразователями. Цель изобретения - расширение функциональных возможностей, а также повышение качества трехфазной системы напряжений путем уменьшения асимметрии и повышения стабильности фазовых сдвигов в диапазоне перестройки частоты, повышения стабильности частоты я автономном режиме. Устройство содержит соединенные определенным образом однофазный генератор 1, логическое устройство 2, преобразователь 3 фаз, два усилителя-ограничителя 4 и 5, датчик 6 фазового рассогласования, интегрирующий блок 7, стабилизатор 8 фазового сдвига и источник 9 синхронизирующего сигнала,. Введение в однофазный генератор аналогового перемножителя 32, конденсатора 33 и трех резисторов 34, 35 и 36, а в логическое устройство 2 - блока 37 контроля частоты и логического элемента ИЛИ 38, (Л

,,/4

UefD

| Преобразователь однофазного напряжения в трехфазное | 1978 |

|

SU702469A1 |

| , ТрошикинВ.М.Анализ работы трехфазного задающего генератора на интегральных микросхемах - Электротехническая промышленность0 Сер | |||

| Преобразовательная техника, 1979, № 7, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

Авторы

Даты

1991-05-30—Публикация

1989-06-23—Подача