Изобретение относится к электроизмерительной технике и предназначено для измерения RLC-параметров с высокой точностью.

Целью изобретения является расширение функциональных возможностей преобразователя на переменном токе.

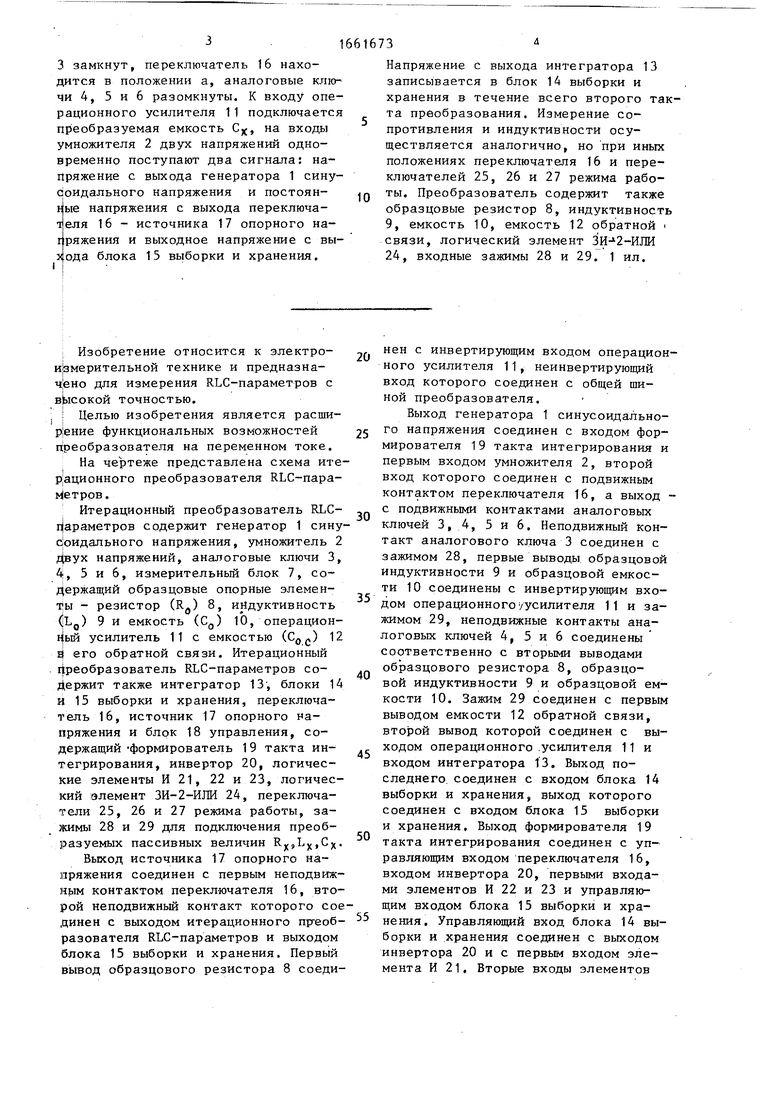

На чертеже представлена схема итерационного преобразователя RLC-napa- Нетров.

Итерационный преобразователь RLC- п|араметров содержит генератор 1 синусоидального напряжения, умножитель 2 двух напряжений, аналоговые ключи 3, 4, 5 и 6, измерительный блок 7, содержащий образцовые опорные элементы - резистор (Rd) 8, индуктивность (L0) 9 и емкость (С0) 10, операцион- н|ый усилитель 11 с емкостью (Сос) 12 в; его обратной связи. Итерационный преобразователь RLC-параметров со- Держит также интегратор 13, блоки 14 И 15 выборки и хранения, переключатель 16, источник 17 опорного напряжения и блок 18 управления, содержащий -формирователь 19 такта интегрирования, инвертор 20, логические элементы И 21, 22 и 23, логический элемент ЗИ-2-ИЛИ 24, переключатели 25, 26 и 27 режима работы, зажимы 28 и 29 для подключения преобразуемых пассивных величин ,CX.

Выход источника 17 опорного напряжения соединен с первым неподвижным контактом переключателя 16, второй неподвижный контакт которого соединен с выходом итерационного пр-еоб- разователя RLC-параметров и выходом блока 15 выборки и хранения. Первый вывод образцового резистора 8 соеди0

5

0

5

0

5

0

5

нен с инвертирующим входом операционного усилителя 11, неинвертирующий вход которого соединен с общей шиной преобразователя.

Выход генератора 1 синусоидального напряжения соединен с входом формирователя 19 такта интегрирования и первым входом умножителя 2, второй вход которого соединен с подвижным контактом переключателя 16, а выход - с подвижными контактами аналоговых ключей 3, 4, 5 и 6. Неподвижный контакт аналогового ключа 3 соединен с зажимом 28, первые выводы образцовой индуктивности 9 и образцовой емкости 10 соединены с инвертирующим входом операционного/усилителя 11 и зажимом 29, неподвижные контакты аналоговых ключей 4, 5 и 6 соединены соответственно с вторыми выводами образцового резистора 8, образцовой индуктивности 9 и образцовой емкости 10. Зажим 29 соединен с первым выводом емкости 12 обратной связи, второй вывод которой соединен с выходом операционного усилителя 11 и входом интегратора 13. Выход последнего соединен с входом блока 14 выборки и хранения, выход которого соединен с входом блока 15 выборки и хранения, Выход формирователя 19 такта интегрирования соединен с управляющим входом переключателя 16, входом инвертора 20, первыми входами элементов И 22 и 23 и управляющим входом блока 15 выборки и хранения. Управляющий вход блока 14 выборки и хранения соединен с выходом инвертора 20 и с первым входом элемента И 21, Вторые входы элементов

И 21, 22 и 23 соединены соответственно с выходами переключателей 25, 26 и 27 режима работы, а выходы - с управляющими входами аналоговых ключей 6, 4 и 5 соответственно. Управляющий вход аналогового ключа 3 соединен с выходом элемента ЗИ-2-ИПИ 24, первый и второй входы которого соединены с выходами формирователя 19 такта интегрирования и переключателя 25 режима работы, третий и четвертый - с выходами инвертора 20 и переключателя 26 режима работы, пятый и шестой - с выходами инвер- тора 20 и переключателя 27 режима работы. Входы переключателей 25, 26 и 27 режима работы соединены с общей шиной преобразователя.

Итерационный преобразователь RLC- параметров работает следующим образом.

В основу принципа действия преобразователя положен итерационный метод коррекции погрешностей. Сущность метода состоит в такой организации процедуры преобразования, при которой (в случае преобразования Cj) результат определяется из равенства произведений значения источника опорного напряжения U0 на электрическое сопротивление измеряемой емкости Су, полученное при заданной частоте СО синусоидального питающего напряжения, и значения U выходного напряжения преобразования на электрическое сопротивление опорной емкости С 1 полученное при той же частоте СО :

о

п .

U Л , tU M

JWL

10

15

20

30

35

U 7.

1

0 W7CQ.Lt

UM 1

И

b C0iCLx

(3)

O.

Во всех режимах работы процедура измерительного преобразования протекает в два такта, причем первому такту условно соответствует положительная полуволна, а второму такту - отрицательная полуволна питающего синусоидального напряжения, выделяемые при помощи формирователя 19.

Режим преобразования С. Переключатели 25, 26, 27 устанавливаются в такие положения, при которых напряжения логического О подаются на соответствующие входы элементов И 22, 23, логической 1 - на вход элемента И 21 .

В первом такте преобразования устанавливаются следующие режимы: на 25 выходе формирователя 19 - напряжение логической 12 в соответствии с прохождением положительной полуволны питающего синусоидального напряжения, на выходе инвертора 20 - напряжение логического О, на выходах элементов И 21,- 22, 23 - О, а на выходе элемента ЗИ-2-ИЖ - 1. При этом начальное напряжение блока 14 выборки и хранения U в течение всего первого такта переписывается в блок 15 выборки и хранения, ключ 3 замкнут, переключатель 16 находится в положении а, а ключи 4, 5 и 6 разомкнуты. К входу операционного усилителя 11 подклю

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель параметров | 1977 |

|

SU702317A1 |

| Цифровой измеритель -параметров | 1978 |

|

SU788036A1 |

| Цифровой измеритель RLc-параметров | 1980 |

|

SU868629A1 |

| Цифровой измеритель -пара-METPOB | 1979 |

|

SU808977A1 |

| Цифровой измеритель напряжения | 1984 |

|

SU1239606A1 |

| Логометрический измерительный преобразователь | 1986 |

|

SU1396074A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2032182C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АКТИВНОЙ И РЕАКТИВНОЙ СОСТАВЛЯЮЩИХ ТОКА | 1990 |

|

RU2018138C1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1987 |

|

SU1597759A1 |

Изобретение относится к электроизмерительной технике и предназначено для измерения RLC-параметров. Цель изобретения - расширение функциональных возможностей - достигается за счет того, что обеспечивается возможность измерения емкости и индуктивности. В режиме измерения емкости переключатели 25, 26, 27 режима работы устанавливаются в такие положения, при которых напряжения логического "0" подаются на соответствующие входы элементов И 22, 23 и логической "1" - на вход элемента И 21. На выходе формирователя 19 такта интегрирования устанавливается напряжение логической "1", на выходе инвертора 20 - напряжение логического "0". Начальное напряжение блока 14 выборки и хранения в течение всего первого такта интегрирования переписывается в блок 15 выборки и хранения, аналоговый ключ 3 замкнут, переключатель 16 находится в положении а, аналоговые ключи 4, 5 и 6 разомкнуты. К входу операционного усилителя 11 подключается преобразуемая емкость CX, на входы умножителя 2 двух напряжений одновременно поступают два сигнала: напряжение с выхода генератора 1 синусоидального напряжения и постоянные напряжения с выхода переключателя 16 - источника 17 опорного напряжения и выходное напряжение с выхода блока 15 выборки и хранения. Напряжение с выхода интегратора 13 записывается в блок 14 выборки и хранения в течение всего второго такта преобразования. Измерение сопротивления и индуктивности осуществляется аналогично, но при иных положениях переключателя 16 и переключателей 25, 26 и 27 режима работы. Преобразователь содержит также образцовые резистор 8, индуктивность 9, емкость 10, емкость 12 обратной связи, логический элемент ЗИ-2-ИЛИ 24, входные зажимы 28 и 29. 1 ил.

п „ ШЬЭСае 0 1/jCOCK Uh 1/jCOC0

или

iSCL JCJC0.

о.с

п

° jCOC.c

В случае преобразования RX(LX) результат определяется из равенства произведений значения U0 на образцовое опорное R0(L0) и значения Utt на измеряемое RyCL), т.е.

U iLlQSiM и l/ibKJac

R

R,

или

1

U,

1

R0 JCOC0|Cn R)t JCOC

о.с

1)

а оа

)

,Q чается преобразуемая емкость С% ,

На входы умножителя 2 одновременно поступают два сигнала: напряжение с выхода генератора 1 (непрерывно), имеющее фиксированное амплитудное

45 значение и синусоидальную форму, и постоянные напряжения с выхода переключателя 16 - ио источника 17 опорного напряжения и выходное напряжение Uft, поступающее с выхода блока 15

50 выборки и хранения. Напряжения UQ и U имеют разные уровни, в соответствии с которыми изменяется и уровень амплитуды синусоидального напряжения на выходе умножителя 2„ U0 и U задают масштаб преобразования. Напряжение далее масштабируется блоком 7 в соответствии со значением измеряемой емкости GX (значение емкости 12 постоянно) . Напряжение синусоидальной

формы на выходе умножителя 2 в те чение действия положительной полу волны питающего синусоидального напряжения интегрируется -при помощи интегратора 13 и фиксируется в нем к моменту окончания такта.

Во втором такте преобразования устанавливаются следующие режимы: на выходе формирователя 19 - напря- сение логического О в соответст- JBHH с прохождением отрицательной полуволны питающего синусоидального напряжения , на выходе инвертора 20 - , Напряжение логической 1, на выхо- де элемента И 21 - 1, на выходах элементов И 22, 23 и элемента ЗИ-2- ЈШИ 24 - напряжение логического О. Jlpn этом напряжение с выхода интегратора 13 записывается в блок 14 выбор,|ки и хранения в течение всего второго iтакта преобразования, ключ 6 замкнут, Ключи 3, 4, 5 разомкнуты, переключатель 16 находится в положении б.

К входу умножителя 2 подключаются Выходное (и) напряжение преобразователя, взятое с блока 15 выборки и Хранения, а к входу операционного усилителя 11 - образцовая опорная ем- ость 10, На интеграторе 13 произ- родится интегрирование синусоидаль- Його напряжения противоположной по- Лярности, взятое уже в масштабе значений напряжения U и образцовой ем

Кости Cfl, Полученное к концу второ- Го такта напряжение фиксируется в 16локе 14 выборки и хранения и принимается за первое улучшенное приближение к искомой величине. В следующем такте это напряжение перепи- сывается в память блока 15 выборки и хранения, и в дальнейшем действия, описанные в первом и во втором тактах преобразования, выполняются поочередно;

В результате после п тактов работы преобразователя в установившемся режиме в соответствии с выражением (1) получают

M«aCOHof§§ + V JOC

§-§;- + V °

(4)

Пм и ПА

- соответственно муЯьти пликатив ная и аддитивная погрешности тракта преобразования

55

Ua - амплитудное значение выходного сигнала генератора 1 синусоидального напряжения. выражения (4) следует

п - U г

и. (5)

п

5 о

5

-. 5

0

5

Режим преобразования RX. Переключатели устанавливаются в такое положение, когда на соответствующие входы элементов И 21 и 23 подается напряжение логического О, а на элемент И 22 - напряжение логической 1V

В первом такте преобразования устанавливаются следующие режимы: на выходе формирователя 19 - логическая 1, на выходе инвертора 20 - логический О, на выходах элементов И 21 и 23 - логический О, на выходе элемента И 22 - логическая 1, на выходе элемента ЗИ-2-ИЛИ 24 - логический О. При этом начальное напряжение блока 14 выборки и хранения U в течение всего первого такта преобразования переписывается в блок 15 выборки и хранения, ключ 4 . замкнут, ключи 3, 5 и 6 разомкнуты, переключатель 16 находится в положении а. К входу умножителя 2 двух напряжений подключается напряжение U , а к входу операционного усилителя 11 - образцовое R0 опорное сопротивление 8. На интеграторе 13 в течение действия положительной полуволны генератора 1 синусоидального напряжения производится интегрирование напряжения, взятое в масштабе значений U0 и RO. К моменту окон- :чания такта преобразования это напряжение фиксируется в интеграто- jpe 13.

i Во втором такте преобразования устанавливаются следующие режимы: на выходе формирователя 19 - напряжение логического О в соответствии с провождением отрицательной полуволны питающего синусоидального напряжения, на выходе инвертора 20 - напряжение логической 1, на выходах элементов И 21, 22 и 23 - логический О, на выходе элемента ЗИ-2-ИЛИ 24 - логическая 1. При этом напряжение с выхода интегратора 13 записывается в блок К выборки и хранения в течение всего второго такта преобразования, ключ 3 замкнут, ключи 4, 5 и 6 разомкнуты, переключатель

16 находится в положении б. К входу умножителя 2 двух напряжений подклю« чается напряжение Ik , а к входу операционного усилителя 11 - преобразуемое сопротивление R.J . После интегрирования на интеграторе 13 напряжение противоположной полярности, полученное к концу второго такта преобразования напряжения, фиксируется блоком 14 выборки и хранения и принимается за первое улучшенное приближение к искомой величине. В следующем такте преобразования это напряжение переписывается в блок 15 выборки и хранения, и в дальнейшем работа преобразователя протекает аналогично описанному.

В результате после п тактов работы преобразователя, в установившемся режиме в соответствии с выражениями (2) и (4) получают

Т - У

R,

(6)

Режим преобразования Ly. Перег ключатели устанавливаются в такое положение, когда на соответствующие входы элементов И 21 и 22 подается напряжение логического О, а на элемент И 23 - напряжение логической -г;

В первом такте преобразования устанавливаются следующие режимы: на выходе формирователя 19 - логическая 1, на выходе инвертора 20 - логический О, на выходах элементов И 21 и 22 - логический О, на выходе элемента И 23 - логическая 1, на выходе элемента ЗИ-2-ИЛИ 24 - логический О .. При этом начальное напряжение блока 14 выборки и хранения Un в течение всего первого такта преобразования переписывается в блок 15 выборки и хранения, ключ 5 замкнут, ключи 3, 4 и 6 разомкнуты, переключатель 16 находится в положении а. К входу умножителя 2 подключается напряжение UQ , а к входу операционного усилителя 11 - образцовая (L0) опорная индуктивность 9. В течение действия положительной полуволны генератора 1 синусоидального напряжения напряжение, взятое в масштабе U0 и L0 интегрируется и фиксируется интегратором 13.

Во втором такте преобразования устанавливаются следующие режимы: на выходе формирователя 19 - логи0

5

0

5

0

5

ческий О, на выходе инвертора 20 - логическая 1 в соответствии с прохождением отрицательной полуволны питающего синусоидального напряжения, на выходах элементов И 21, 22 и 23 - напряжение логического О на выходе элемента ЗИ-2-ИЛИ 24 - логическая 1. При этом напряжение с выхода интегратора 13 переписывается в блок 14 выборки и хране- .ния в течение всего второго такта преобразования, ключ 3 замкнут, ключи 4 , 5 и 6 разомкнуты, переключатель 16 находится в положении б,

К входу умножителя 2 подключается напряжение U, а к входу операционного усилителя - преобразуемая индуктивность L0. После интегрирования на интеграторе 13 напряжение противоположной полярности, полученное к концу второго такта пр.еобразования напряжения, фиксируется в блоке 14 выборки и хранения, принимается за первое улучшенное приближение к искомой величине. В следующем такте преобразования это напряжение переписывается в блок 15 выборки и хранения, и в дальнейшем работа преобразователя протекает аналогично описанному.

В результате после п тактов работы преобразователя, в установившемся режиме в соответствии с выражения(3) и (4) получают

ми

U U L0

(7)

Как видно из выражений (5), (6) и (7), результат преобразования R-, L- и С-параметров не зависит от частоты питающего синусоидального напряжения, а также от систематических погрешностей узлов и блоков преобразователя за исключением источника 17 опорного напряжения и образцовых элементов 8, 9, 10. При этом в отличие от прототипа обеспечивается прямое преобразование измеряемых RLC- параметров в заданном частотном диапазоне.

Обеспечение возможности измерения не только сопротивленияs но и емкости, и индуктивности на переменном токе расширяет функциональные возможности преобразователя.

Формула изобретения

Итерационный преобразователь RLC- параметров, содержащий источник опорного напряжения, выход которого соединен с первым неподвижным контактом Переключателя, второй неподвижный контакт которого соединен с выходом преобразователя, образцовый резистор, Первый вывод которого соединен с инвертирующим входом операционного усилителя, неинвертирующий вход которо- Го соединен с общей шиной преобразователя, четыре аналоговых ключа, ин- Тегратор, первый блок выборки и хранения, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены генератор синусоидального напряжения, умножитель двух напряжений, второй б,лок выборки и хранения, образцовая индуктивность, образцовая емкость, емкость обратной связи и блок управления, содержащий формирователь такта интегрирования, инвертор, три логических элемента И, логический элемент ЗИ-2-ИЛИ и три переключателя режима р аботы, выход генератора синусоидаль- ного напряжения соединен с входом формирователя такта интегрирования И первым входом умножителя, второй вход которого соединен с подвижным f контактом переключателя, а выход - с подвижными контактами четырех аналоговых ключей, неподвижный контакт Первого аналогового ключа соединен с первым входным зажимом, первые выводы образцовой индуктивности и ем- Кости соединены с инвертирующим вхо- дом операционного усилителя и вторым входным зажимом, неподвижные контакты второго, третьего и четверто

0 5 0 0

5

го аналоговых ключей соединены соо ветственно с вторыми выводами образцовых резистора, индуктивности и емкости, второй входной зажим соединен с первым выводом емкости обратной связи, второй вывод которой соединен с выходом операционного усилителя и входом интегратора, выход которого соединен с входом первого блока выборки и хранения, выход формирователя такта интегрирования соединен с управляющим входом переключателя, входом инвертора, первыми входами первого и второго элементов И и управляющим входом второго блока выборки и хранения, выход которого соединен с выходом преобразователя, а вход - с выходом первого блока выборки и хранения, управляющий вход которого соединен с выходом инвертора и с первым входом третьего элемента И, вторые входы первого, второго и третьего элементов И соединены соответственно с выходами первого, второго и третьего переключателей режима работы, а выходы - с управляющими входами второго, третьего и четвертого аналоговых ключей, управляющий вход первого аналогового ключа соединен с выходом элемента ЗИ-2-ИЛИ, первый и второй входы которого соединены с выходами формирователя такта интегрирования и третьего переключателя режима работы, третий и четвертый - с выходами инвертора и первого переключателя режима работы, пятый и шестой - с выходами инвертора и второго переключателя режима работы, входы переключателей режима работы соединены с общей ши- |ной преобразователя.

| Устройство для измерения @ , @ , @ параметров | 1983 |

|

SU1183919A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой омметр | 1982 |

|

SU1046707A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-07-07—Публикация

1989-04-25—Подача